JP5259138B2 - 記憶装置 - Google Patents

記憶装置 Download PDFInfo

- Publication number

- JP5259138B2 JP5259138B2 JP2007211741A JP2007211741A JP5259138B2 JP 5259138 B2 JP5259138 B2 JP 5259138B2 JP 2007211741 A JP2007211741 A JP 2007211741A JP 2007211741 A JP2007211741 A JP 2007211741A JP 5259138 B2 JP5259138 B2 JP 5259138B2

- Authority

- JP

- Japan

- Prior art keywords

- block

- data

- semiconductor memory

- binary

- stored

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 claims description 63

- 230000015654 memory Effects 0.000 claims description 43

- 238000000034 method Methods 0.000 claims description 7

- 239000003990 capacitor Substances 0.000 claims description 5

- 238000007726 management method Methods 0.000 description 29

- 239000007787 solid Substances 0.000 description 19

- 238000010586 diagram Methods 0.000 description 9

- 238000013500 data storage Methods 0.000 description 8

- 238000006243 chemical reaction Methods 0.000 description 4

- 230000010365 information processing Effects 0.000 description 2

- 230000002950 deficient Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

Images

Landscapes

- Techniques For Improving Reliability Of Storages (AREA)

- Memory System (AREA)

- Read Only Memory (AREA)

Description

2 コントローラ

3 揮発性メモリ

4 電源保持用キャパシタ

51 〜54 不揮発性半導体メモリ

61 〜64 不揮発性半導体メモリ

71 〜74 不揮発性半導体メモリ

81 〜84 不揮発性半導体メモリ

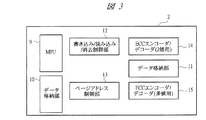

9 MPU

10,11 データ格納部

12 書き込み/読み込み/消去制御部

13 ページアドレス制御部

14,15 ECCエンコーダ/デコーダ

H ホスト

B0〜B5 バス

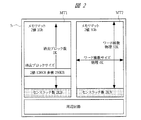

MT1,MT2 メモリマット

BT ブロック管理テーブル

T1 回数管理テーブル

T2 2値/多値テーブル

T3 アドレス変換テーブル

Claims (2)

- 不揮発性半導体メモリで構成されホストからハードディスクドライブ互換制御技術で制御可能に構成された記憶装置であって、

ある電圧レベルのしきい値を複数設定し2ビット以上の多値でデータ書き込みが可能にされた不揮発性半導体メモリセルのメモリアレイで構成された不揮発性半導体メモリと、

揮発性メモリと、

前記ホストから発行されたコマンドに基づいて前記不揮発性半導体メモリの動作指示を行うコントローラと、

電源保持用キャパシタとを備え、

前記不揮発性半導体メモリは、前記多値書き込み可能な不揮発性半導体メモリセルが2値(1ビット)でデータ書き込みが行われるブロックとして制御される領域(以下「2値ブロック」という。)と、前記多値でデータ書き込みが行われるブロックとして制御される領域(以下「多値ブロック」という。)で構成され、ユーザのアクセスが不可とされるシステム領域のデータは前記2値ブロックに格納され、ユーザデータ領域のデータは前記多値ブロックに格納されるように設定されており、

前記多値書き込み可能な不揮発性半導体メモリセルのブロックを2値ブロックとしてデータを格納するか多値ブロックとしてデータを格納するかを示す2値/多値書き込み情報を有したブロック管理テーブルが前記2値ブロックのシステム領域に格納されており、

前記コントローラは、

前記記憶装置の動作時に前記ブロック管理テーブルを前記揮発性メモリに展開する処理と、

前記不揮発性半導体メモリの書き換え耐数に至る前の処理において、ホストから送信されるデータを前記ブロック管理テーブルの2値/多値書き込み情報を参照して前記2値ブロックに格納するデータか前記多値ブロックに格納するデータかを決定し、前記不揮発性半導体メモリにデータを書き込む処理と、

電源遮断が発生したときは、前記電源保持用キャパシタから供給される電源によって、前記揮発性メモリに一時記憶されているユーザデータを前記2値ブロックに書き込む処理とを実行するように構成されてなることを特徴とする記憶装置。 - 請求項1記載の記憶装置において、前記不揮発性半導体メモリのワード線はそれぞれ上位ワード線と下位ワード線で構成され、前記多値ブロックにおいては前記上位ワード線と下位ワード線の両方を使用してデータ格納が行われ、前記2値ブロックにおいては前記上位ワード線のみを使用してデータ格納が行われることを特徴とする記憶装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007211741A JP5259138B2 (ja) | 2007-08-15 | 2007-08-15 | 記憶装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007211741A JP5259138B2 (ja) | 2007-08-15 | 2007-08-15 | 記憶装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009048680A JP2009048680A (ja) | 2009-03-05 |

| JP5259138B2 true JP5259138B2 (ja) | 2013-08-07 |

Family

ID=40500758

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007211741A Expired - Fee Related JP5259138B2 (ja) | 2007-08-15 | 2007-08-15 | 記憶装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5259138B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104919434A (zh) * | 2012-12-07 | 2015-09-16 | 西部数据技术公司 | 用于在固态驱动器中进行较低页数据恢复的系统和方法 |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5612508B2 (ja) | 2010-03-25 | 2014-10-22 | パナソニック株式会社 | 不揮発性メモリコントローラ及び不揮発性記憶装置 |

| JP5533141B2 (ja) * | 2010-03-31 | 2014-06-25 | アイシン・エィ・ダブリュ株式会社 | 書き込み装置、書き込み方法、及び書き込みプログラム |

| JP2012203863A (ja) | 2011-03-28 | 2012-10-22 | Toshiba Corp | メモリシステム |

| JP2015138498A (ja) * | 2014-01-24 | 2015-07-30 | 三菱電機株式会社 | フラッシュメモリの誤り訂正符号化装置および方法 |

| JP6146675B2 (ja) | 2014-06-03 | 2017-06-14 | コニカミノルタ株式会社 | 画像形成装置及びフラッシュメモリの制御方法並びに制御プログラム |

| JP2016004387A (ja) * | 2014-06-16 | 2016-01-12 | 株式会社東芝 | ストレージシステム、メモリコントローラ、および制御方法 |

| JP6493355B2 (ja) * | 2016-10-14 | 2019-04-03 | 京セラドキュメントソリューションズ株式会社 | メモリーシステム及び画像形成装置 |

| JP2018160303A (ja) * | 2017-03-23 | 2018-10-11 | 東芝メモリ株式会社 | 半導体記憶装置 |

| JP7039348B2 (ja) * | 2018-03-20 | 2022-03-22 | キオクシア株式会社 | 書き込み制御装置、ストレージ装置、ネットワークシステム、および書き込み制御方法 |

| KR20230068197A (ko) | 2021-11-10 | 2023-05-17 | 삼성전자주식회사 | 스토리지 장치 및 이의 동작 방법 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11283396A (ja) * | 1998-03-27 | 1999-10-15 | Sony Corp | メモリ装置 |

| JP2000298992A (ja) * | 1999-04-13 | 2000-10-24 | Hitachi Ltd | 多値記憶不揮発性半導体メモリの制御装置 |

| JP2001306393A (ja) * | 2000-04-20 | 2001-11-02 | Mitsubishi Electric Corp | 記憶装置 |

-

2007

- 2007-08-15 JP JP2007211741A patent/JP5259138B2/ja not_active Expired - Fee Related

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104919434A (zh) * | 2012-12-07 | 2015-09-16 | 西部数据技术公司 | 用于在固态驱动器中进行较低页数据恢复的系统和方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2009048680A (ja) | 2009-03-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5259138B2 (ja) | 記憶装置 | |

| US9996274B2 (en) | Flash memory system | |

| US9292428B2 (en) | Memory system | |

| US7974139B2 (en) | Non-volatile memory generating different read voltages | |

| US20160070507A1 (en) | Memory system and method of controlling memory device | |

| US20170091039A1 (en) | Data storage device and operating method thereof | |

| US8694748B2 (en) | Data merging method for non-volatile memory module, and memory controller and memory storage device using the same | |

| KR20080067834A (ko) | 프로그램 방식을 선택할 수 있는 메모리 시스템 | |

| CN115145755B (zh) | 用于重新映射存储器子系统中的不良块的系统和方法 | |

| CN113808656B (zh) | 存储器子系统中的不良生长块管理 | |

| CN111352854B (zh) | 存储装置、控制器及操作存储装置的方法 | |

| US11847065B2 (en) | Memory sub-system management of firmware block record and device block record | |

| US9122583B2 (en) | Memory controller and memory storage device and data writing method | |

| CN115437558A (zh) | 存储器系统中的对角页映射 | |

| US9728264B2 (en) | Nonvolatile memory device, operating method thereof, and data storage device including the same | |

| US11222693B2 (en) | Data management method for memory and memory apparatus using the same | |

| CN117435519B (zh) | 用于减少块转移损失的缓冲器分配 | |

| CN115732003A (zh) | 存储器子系统清理 | |

| US20130286731A1 (en) | Memory device, memory control device, and memory control method | |

| US12062394B2 (en) | Performing data integrity checks to identify defective wordlines | |

| US12299282B2 (en) | Runtime storage capacity reduction avoidance in sequentially-written memory devices | |

| US20250208992A1 (en) | Wordline group-based identification of good memory blocks during a programming operation | |

| US20260037431A1 (en) | Storage device and method of operating the same | |

| US20240192875A1 (en) | Remapping bad blocks in a memory sub-system | |

| CN115079928B (zh) | 跳跃式资料清除方法与资料储存系统 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100203 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120222 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120321 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120518 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20121106 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130205 |

|

| A911 | Transfer of reconsideration by examiner before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20130212 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130402 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130424 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160502 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |