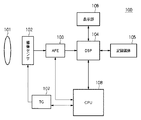

本発明の第1実施形態に係る撮像装置100を、図1を用いて説明する。図1は、本発明の第1実施形態に係る撮像装置100の構成図である。

本実施形態に係る撮像装置100は、電子シャッター機能として、一括電子シャッター機能を採用している。撮像装置100は、次の構成要素を備える。

撮像レンズ101は、被写体の光学像を撮像センサ102の撮像面(画素配列)に形成する。

撮像センサ102は、撮像面(画素配列)に形成された光学像を画像信号に変換する。撮像センサ102は、変換された画像信号を画素配列から読み出して出力する。撮像センサ102は、例えば、CMOSイメージセンサである。

CPU108は、シャッターボタン等の操作部材(図示せず)を介してユーザから指示を受けて、受けた指示に応じて、AFE103、DSP104、TG107を制御する。 AFE(Analog Front End)103は、撮像センサ102から出力されるアナログ画像信号を受ける。AFE103は、CPU108により制御され、受けたアナログ画像信号に対して、A/D変換処理などのアナログ信号処理を行う。例えば、AFE103は、A/D変換器を含み、アナログ画像信号に対してA/D変換処理を行うことにより、デジタル画像信号を生成する。AFE103は、処理後のデジタル画像信号を出力する。

DSP(Disital Signal Processer)104は、AFE103から出力されるデジタル画像信号を受ける。DSP104は、CPU108により制御され、受けたデジタル画像信号に対して、各種の画像処理や圧縮・伸張処理などのデジタル信号処理を行なう。

例えば、DSP104は、デジタル画像信号に対して所定の信号処理を行うことにより、記録用の画像データを生成する。DSP104は、生成した記録用の画像データを記録媒体105に記録する。記録媒体105は、DSP104に着脱可能に接続される。

あるいは、例えば、DSP104は、デジタル画像信号に対して所定の信号処理を行うことにより、表示用の画像信号(アナログ信号)を生成する。DSP104は、生成した表示用の画像信号を表示部106へ供給する。

表示部106は、DSP104から受けた表示用の画像信号や各種メニュー画面などを表示する。

タイミングジェネレータ(TG)107は、CPU108により制御され、所定の駆動信号を生成して、生成した駆動信号を撮像センサ101へ供給する。

次に、撮像センサ102の構成について、図2を用いて説明する。図2は、撮像センサ102の構成図である。

撮像センサ102は、次の構成要素を備える。

画素配列PAでは、複数の画素P11〜P44が行方向及び列方向に配列されている。図2では、画素配列PAが4行4列の画素で構成される場合が例示されている。

読み出し部10は、複数の列共通読み出し回路RC1〜RC4を含む。複数の列共通読み出し回路RC1〜RC4のそれぞれは、列信号線RL1〜RL4を介して画素配列PAにおける各列の画素に接続されている。複数の列共通読み出し回路RC1〜RC4は、画素配列PAから信号を読み出して保持する。

垂直走査回路(駆動部)401は、画素配列PAを駆動する。垂直走査回路401は、TG107から駆動信号を受けて、受けた駆動信号に応じて、所定の制御信号を画素配列PAの各画素に供給する。例えば、垂直走査回路401は、第1のリセット制御信号resp1〜resp4、第2のリセット制御信号resf1〜resf4、転送制御信号tx1〜tx4、選択制御信号sel1〜sel4を、画素配列PAの各画素に供給する。

水平走査回路402は、各列の水平転送スイッチを順次にオンして、複数の列共通読み出し回路RC1〜RC4により保持された各列の信号を順次に出力線OLS,OLN経由で出力アンプ309へ転送する。

出力アンプ309は、転送された信号に基づいて画像信号を生成して出力する。

次に、画素P11〜P44の構成を、図3を用いて説明する。図3は、画素P11の構成図である。以下では、画素P11の構成を例示的に説明するが、他の画素P12〜P44の構成も画素P11の構成と同様である。

画素P11は、次の構成要素を備える。

光電変換部201は、光に応じた電荷(信号)を生成して蓄積する電荷蓄積動作を行う。光電変換部201は、例えば、フォトダイオードである。

第1のリセット部202は、(電荷電圧変換部204と独立して)光電変換部201をリセットする。第1のリセット部202は、例えば、第1のリセットMOSトランジスタであり、垂直走査回路401からアクティブな第1のリセット制御信号resp1がゲートに供給された際にオンして光電変換部201をリセットする。そして、第1のリセット部202は、光電変換部201のリセットを完了することにより、光電変換部201に電荷蓄積動作を開始させる。

転送部203は、活性状態において、光電変換部201で発生した電荷を電荷電圧変換部204へ転送し、非活性状態において、光電変換部201で発生した電荷を電荷電圧変換部204へ転送しない。転送部203は、例えば、転送MOSトランジスタであり、垂直走査回路401からアクティブな転送制御信号tx1がゲートに供給された際にオンする(活性状態になる)ことにより、光電変換部201で発生した電荷を電荷電圧変換部204へ転送する。

電荷電圧変換部(電荷保持部)204は、転送された電荷を保持する。電荷電圧変換部204は、その保持する電荷を電圧に変換する。電荷電圧変換部204は、例えば、フローティングディフュージョンである。

第2のリセット部206は、(光電変換部201と独立して)電荷電圧変換部204をリセットする。第2のリセット部206は、例えば、第2のリセットMOSトランジスタであり、垂直走査回路401からアクティブな第2のリセット制御信号resf1がゲートに供給された際にオンして電荷電圧変換部204をリセットする。

出力部205は、電荷電圧変換部204の電圧に応じた信号を出力する。出力部205は、電荷電圧変換部204がリセットされた状態で、電荷電圧変換部204の電圧に応じたN信号を出力する。出力部205は、光電変換部201の電荷が電荷電圧変換部204へ転送された状態で、電荷電圧変換部204の電圧に応じたS信号を出力する。出力部205は、例えば、増幅MOSトランジスタである。

選択部207は、画素P11を選択状態/非選択状態にする。選択部207は、例えば、選択MOSトランジスタであり、垂直走査回路401からアクティブな選択制御信号sel1がゲートに供給された際にオンして画素P11を選択状態にする。

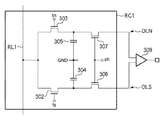

次に、列共通読み出し回路RC1〜RC4の構成を、図4を用いて説明する。図4は、列共通読み出し回路RC1の構成図である。以下では、列共通読み出し回路RC1の構成を例示的に説明するが、他の列共通読み出し回路RC2〜RC4の構成も列共通読み出し回路RC1の構成と同様である。

列共通読み出し回路RC1は、次の構成要素を含む。

S信号転送スイッチ302は、TG107からアクティブな制御信号tsが供給された際にオンすることにより、第1列の画素P11,P21,P31,P41のいずれかから読み出されたS信号をS信号保持容量304へ転送する。

N信号転送スイッチ303は、TG107からアクティブな制御信号tnが供給された際にオンすることにより、第1列の画素P11,P21,P31,P41のいずれかから読み出されたN信号をN信号保持容量305へ転送する。

S信号保持容量304は、TG107からノンアクティブな制御信号tsがS信号転送スイッチ302へ供給されS信号転送スイッチ302がオフすることにより、転送されたS信号を保持し始める。

N信号保持容量305は、TG107からノンアクティブな制御信号tnがN信号転送スイッチ303へ供給されN信号転送スイッチ303がオフすることにより、転送されたN信号を保持し始める。

水平転送スイッチ306は、水平走査回路402からアクティブな水平走査信号phが供給された際にオンすることにより、S信号保持容量304に保持されたS信号をS信号保持容量304から出力線OLSへ転送する。

水平転送スイッチ307は、水平走査回路402からアクティブな水平走査信号phが供給された際にオンすることにより、N信号保持容量305に保持されたN信号をN信号保持容量305から出力線OLNへ転送する。

これにより、出力アンプ309は、出力線OLSにより伝達されたS信号と出力線OLNにより伝達されたN信号との差分をとるCDS処理を行うことにより、画像信号を生成して出力する。

次に、撮像装置100の動作を説明する。

撮像装置100の構成を説明する際に4行4列の画素P11〜P44で構成された画素配列PA(図2参照)を用いたが、撮像装置100の動作を説明する際には、15行25列の画素P1,1〜P15,25で構成された画素配列PAを用いることとする。図5は、15行25列の画素P1,1〜P15,25で構成された画素配列PAを示した図である。

撮像装置100は、静止画撮影モードにおいて、画素配列PAにおける全画素P1,1〜P15,25、すなわち第1の画素群PG1及び第2の画素群PG2の信号から1フレームの静止画用の画像信号を生成する。第1の画素群PG1は、5n+1行目(n:0以上の整数、ここでは、n=0,1,2)の画素である。第1の画素群PG1は、第1行の画素P1,1〜P1,25と、第6行の画素P6,1〜P6,25と、第11行の画素P11,1〜P11,25とを含む。第2の画素群PG2は、第1の画素群PG1以外の行(5n+2行目、5n+3行目、5n+4行目、5n+5行目)の画素である。第2の画素群PG2は、第2〜5行の画素と、第7〜10行の画素と、第12〜15行の画素とを含む。

撮像装置100は、動画撮影モードにおいて、第1の画素群PG1の信号から1フレームの動画用の画像信号を生成する。動画撮影モードでは、画素配列PAから第2の画素群PG2が間引かれて(5行につき1行が読み出し行として選択されて)、第1の画素群PG1から信号が読み出される。

なお、動画撮影と並行して静止画撮影を行うモード(以下、動画/静止画並行撮影モードとする)における撮像装置100の動作は後述する。

次に、動画撮影モードにおける動作について、主に図6を用いて説明する。図6は、動画撮影モードにおける動作を模式的に示した図である。図6では、横軸が時刻を表し、縦軸における横軸より上の部分が光電変換部の動作に関する画素行の位置を表し、縦軸における横軸より下の部分が読み出し部の動作に関する画素行の位置を表す。

図6に示すように、複数の画素P1,1〜P15,25は、第1の蓄積期間群Taで電荷蓄積動作を行う。この第1の蓄積期間群における全ての画素の第1の蓄積期間Ta1〜Ta15は、全部が重なっている。すなわち、画素配列PAの全画素P1,1〜P15,25の光電変換部201における電荷蓄積動作は、一斉に行われる。

なお、蓄積期間名、制御信号名に対する添え字1〜15は、画素行に対応している。

図6に示すリセット動作601は、第1のリセット部202(図3参照)による光電変換部201のリセット動作の完了が、全画素P1,1〜P15,25で同時であることを示している。これについて、図7のタイミングチャートを用いて説明する。図7は、各行の画素における光電変換部201のリセット動作を示すタイミングチャートである。

垂直走査回路401が各行の画素へ供給する第1のリセット制御信号resp1〜resp15は、図7に示すようになる。すなわち、第1のリセット制御信号resp1〜resp15がアクティブなレベルからノンアクティブなレベルへ遷移して各行の画素P1,1〜P15,25のリセット動作が完了するタイミングが同時である。これにより、各行の画素P1,1〜P15,25の光電変換部201は、同時に電荷蓄積動作を開始する。このとき、垂直走査回路401が各行の画素へ供給する転送制御信号tx1〜tx15は、ノンアクティブなレベルに維持されている。これにより、各行の画素P1,1〜P15,25の転送部203は、非活性状態に保たれている。

図6に示す転送動作602,603は、転送部203(図3参照)による光電変換部201の電荷の転送動作が、全画素P1,1〜P15,25で同時に行われることを示している。これについて、図8のタイミングチャートを用いて説明する。図8は、各行の画素における光電変換部201の電荷の転送動作を示すタイミングチャートである。

垂直走査回路401が各行の画素へ供給する転送制御信号tx1〜tx15は、図8に示すようになる。すなわち、転送制御信号tx1〜tx15がノンアクティブなレベルからアクティブなレベルへ遷移して各行の画素P1,1〜P15,25の電荷の転送動作が開始するタイミングが同時である。これにより、各行の画素P1,1〜P15,25の光電変換部201は、同時に電荷蓄積動作を終了する。このとき、垂直走査回路401が各行の画素へ供給する第1のリセット制御信号resp1〜resp15は、ノンアクティブなレベルに維持されている。

従って、図6に示す時刻t1から時刻t2までの時間が第1の蓄積時間Ta1〜Ta15となり、この第1の蓄積時間Ta1〜Ta15の長さを適切に制御することにより、取得する画像信号が適正なレベルとなるように制御することができる。

図6に白い四角で示す第1の読み出し動作604は、列共通読み出し回路RC1〜RC4(図2参照)により第1の画素群PG1(図5参照)のみから信号の読み出し動作が行ごとに順次に行われることを示している。すなわち、垂直走査回路401は、第1行目、第6行目、第11行目を順次に選択する(それ以外の行をスキップする)。列共通読み出し回路RC1〜RC4は、選択された行の画素における電荷電圧変換部204の電圧に応じた信号を出力部205を介して読み出す。

第1の読み出し動作604の枠内に示されたアルファベット(a、b、c、d)は、そこで読み出される画素信号が、どの蓄積期間群に光電変換部201により蓄積されたものかを示している。

例えば、aと記載したものは第1の蓄積期間群Taで光電変換部201により蓄積された信号を示し、bと記載したものは第2の蓄積期間群Tbで光電変換部201により蓄積された信号を示している。cと記載したものは第3の蓄積期間群Tcで光電変換部201により蓄積された信号を示し、dと記載したものは第4の蓄積期間群Tdで光電変換部201により蓄積された信号を示している。

図9に、第1の読み出し動作に関するタイミングチャートを示す。図9では、第1行目の読み出し動作を例示的に示している。

なお、水平転送信号名phに対する添え字1〜15は、画素列に対応している。例えば、ph1は第1列目の列共通読み出し回路RC1に入力される水平転送信号を示し、ph2は第2列目の列共通読み出し回路RC2に入力される水平転送信号を示している。

垂直走査回路401は、第1行目の画素へ供給する選択制御信号sel1をノンアクティブなレベルからアクティブなレベルへ遷移させる。これにより、第1行目の画素P1,1〜P1,25が選択状態になる。このため、第1行目の画素P1,1〜P1,25の出力部205が電荷電圧変換部204の電圧に応じた信号を列信号線RL1〜RL4へ出力する。

次に、TG107は、S信号転送スイッチ302へ供給する制御信号tsをアクティブなレベルにする。これにより、S信号転送スイッチ302がオンして、S信号保持容量304にS信号が記憶される。

その後、垂直走査回路401は、第1行目の画素へ供給する第2のリセット信号resf1をアクティブなレベルにする。これにより、第1行目の画素における第2のリセット部206がオンして、電荷電圧変換部204がリセットされる。その後、垂直走査回路401は、第1行目の画素へ供給する第2のリセット信号resf1をノンアクティブなレベルに戻す。

次に、TG107は、N信号転送スイッチ303へ供給する制御信号tnをアクティブなレベルにする。これにより、N信号転送スイッチ303がオンして、N信号保持容量305にN信号が記憶される。このN信号には、電荷電圧変換部204以降の回路ノイズ成分が含まれている。

各列の水平転送信号ph1〜ph25を順次アクティブにして各列の水平転送スイッチを順次にオンする。これにより、各列のS信号保持容量及びN信号保持容量に保持されたS信号及びN信号を順次に出力アンプ309へ転送する。

出力アンプ309は、S信号とN信号との差分信号に所定のゲインをかけることにより、回路ノイズ成分が除去された画像信号を生成して出力する。

垂直走査回路401は、第1行目の画素へ供給する選択制御信号sel1をアクティブなレベルからノンアクティブなレベルへ遷移させる。これにより、第1行目の画素P1,1〜P1,25が非選択状態になる。

図6に斜線の四角で示す間引き動作605は、列共通読み出し回路RC1〜RC4(図2参照)により第2の画素群PG2(図5参照)から信号が読み出されないことを示している。すなわち、垂直走査回路401は、第2〜5行目、第7〜10行目、第12〜15行目を順次にスキップし、列共通読み出し回路RC1〜RC4は、スキップされた行の画素における電荷電圧変換部204の電圧に応じた信号を読み出さない。

図10に、間引き動作605に関するタイミングチャートを示す。図10では、第3行目の間引き動作605を例示的に示している。

垂直走査回路401は、第3行目の画素へ供給する選択制御信号sel3をノンアクティブなレベルからアクティブなレベルへ遷移させる。これにより、第3行目の画素P3,1〜P3,25が選択状態になる。これにより、第3行目の画素P3,1〜P3,25の出力部205が電荷電圧変換部204の電圧に応じた信号を列信号線RL1〜RL4へ出力する。なお、電荷電圧変換部204は、転送された電荷を保持し続けている。

その後、垂直走査回路401は、第3行目の画素へ供給する第2のリセット信号resf3をアクティブなレベルにする。これにより、第3行目の画素における第2のリセット部206がオンして、電荷電圧変換部204がリセットされる。その後、垂直走査回路401は、第3行目の画素へ供給する第2のリセット信号resf3をノンアクティブなレベルに戻す。

垂直走査回路401は、第3行目の画素へ供給する選択制御信号sel3をアクティブなレベルからノンアクティブなレベルへ遷移させる。これにより、第3行目の画素P3,1〜P3,25が非選択状態になる。

この間引き動作においては、画素の信号を読み出す必要がないため、ts、tn、phといった信号は動かさずにノンアクティブなレベルに固定したままとする。

このように、間引き動作の対象となる行の画素から信号を読み出さないため、1行を間引く動作に必要な時間は1行の画素信号を読み出すのに対して遥かに短い時間で済む。

読み出し部10(図2参照)は、動画撮影を行うことが指示された場合、各フレーム期間において、画素配列PAの一部である第1の画素群PG1の全てから直前のフレーム期間内の蓄積期間群に蓄積された信号における第1の信号を読み出す。

例えば、読み出し部10は、第1のフレーム期間FT1において、第1の画素群PG1の全てから直前のフレーム期間FT0内の第1の蓄積期間群Taで蓄積された信号における第1の信号を読み出す。例えば、読み出し部10は、第2のフレーム期間FT2(第1のフレーム期間以降のフレーム期間)において、第1の画素群PG1の全てから直前のフレーム期間FT1内の第2の蓄積期間群Tbで蓄積された信号における第1の信号を読み出す。

読み出し部10は、第1の信号を、出力アンプ309、及びAFE103経由でDSP104へ供給する。これにより、DSP(生成部)104は、各フレーム期間に読み出された第1の信号から、1フレーム分の動画用の画像信号(画像データ)を生成する。このとき、読み出された第1の信号は行方向(垂直方向)に間引かれたものであるため、そのまま画像を構成すると画像の縦横比が合わないため、DSP104は、列方向(水平方向)の画素情報を補間する処理を行なった上で動画用の画像を構成する。

次に、動画撮影中に静止画を撮影する場合(動画/静止画並行撮影モード)における動作について、主に図11を用いて説明する。図11は、動画/静止画並行撮影モードにおける動作を模式的に示した図である。図11では、横軸が時刻を表し、縦軸における横軸より上の部分が光電変換部の動作に関する画素行の位置を表し、縦軸における横軸より下の部分が読み出し部の動作に関する画素行の位置を表す。以下では、動画モードにおける動作と異なる部分を中心に説明する。

撮像装置100は、既に動画撮影モードで動作しているものとする。

時刻t0において、CPU108は、シャッターボタン等の操作部材(図示せず)を介してユーザから静止画撮影指示を受ける。これにより、CPU108は、動作モードを、動画撮影モードから動画/静止画並行撮影モードへ切り替える。

時刻t2において、全行に対する転送動作602,603が行われるのに対して、時刻t4においては、一部の行に対する部分転送動作1102が行われる。部分転送動作1102は、転送部203(図3参照)による光電変換部201の電荷の転送動作が、第1の画素群PG1で同時に行われ、第2の画素群PG2で行われないことを示している。これについて、図12のタイミングチャートを用いて説明する。図12は、各行の画素における光電変換部201の電荷の転送動作を示すタイミングチャートである。なお、図12では、第1〜7行の画素へ供給される信号が例示的に示されている。

垂直走査回路401が各行の画素へ供給する転送制御信号tx1〜tx15は、図12に示すようになる。すなわち、転送制御信号tx1,tx6,tx11がノンアクティブなレベルからアクティブなレベルへ同時に遷移するとともに、転送制御信号tx2〜tx5,tx7〜tx10,tx12〜tx15がノンアクティブなレベルに維持される。これにより、第1の画素群PG1のみ転送部203が光電変換部201の電荷を電荷電圧変換部204へ転送し、第2の画素群PG2の電荷電圧変換部204は、第1の蓄積期間群Taで蓄積された電荷(信号)を保持し続ける。

図11に破線で囲った白い四角で示す第2の読み出し動作1104は、列共通読み出し回路RC1〜RC4(図2参照)により第2の画素群PG2(図5参照)の一部からも信号の読み出し動作が行ごとに順次に行われることを示している。

すなわち、垂直走査回路401は、第1のフレーム期間FT1において、第2の画素群PG2から5n+2(2、7、12)行目の画素を順次に選択する。列共通読み出し回路RC1〜RC4は、選択された行の画素における電荷電圧変換部204の電圧に応じた信号(第1の蓄積期間群Taで蓄積された信号における第2の信号)を出力部205を介して読み出す。

また、垂直走査回路401は、第2のフレーム期間FT2において、第2の画素群PG2から5n+3(3、8、13)行目の画素を順次に選択する。列共通読み出し回路RC1〜RC4は、選択された行の画素における電荷電圧変換部204の電圧に応じた信号(第1の蓄積期間群Taで蓄積された信号における第2の信号)を出力部205を介して読み出す。

また、垂直走査回路401は、第3のフレーム期間FT3において、第2の画素群PG2から5n+4(4、9、14)行目の画素を順次に選択する。列共通読み出し回路RC1〜RC4は、選択された行の画素における電荷電圧変換部204の電圧に応じた信号(第1の蓄積期間群Taで蓄積された信号における第2の信号)を出力部205を介して読み出す。

また、垂直走査回路401は、第4のフレーム期間FT4において、第2の画素群PG2から5n+5(5、10、15)行目の画素を順次に選択する。列共通読み出し回路RC1〜RC4は、選択された行の画素における電荷電圧変換部204の電圧に応じた信号(第1の蓄積期間群Taで蓄積された信号における第2の信号)を出力部205を介して読み出す。

このように、列共通読み出し回路RC1〜RC4は、連続する複数のフレーム期間FT1〜FT4のそれぞれにおいて、第2の画素群PG2における互いに異なる一部の画素から第1の蓄積期間群Taで蓄積された信号における第2の信号を読み出す。

なお、第2の読み出し動作1104に関するタイミングチャートは、図9と同様になる。

図11に斜線の四角で示す間引き動作1105は、第2の画素群PG2(図5参照)における読み出されない行数(5行に付き3行)が、図6に示す間引き動作605における読み出されない行数(5行に付き4行)に比べて少ない。

図13に、間引き動作1105に関するタイミングチャートを示す。図13では、第3行目の間引き動作1105を例示的に示している。

垂直走査回路401は、第3行目の画素へ供給する選択制御信号sel3をノンアクティブなレベルからアクティブなレベルへ遷移させる。これにより、第3行目の画素P3,1〜P3,25が選択状態になる。これにより、第3行目の画素P3,1〜P3,25の出力部205が電荷電圧変換部204の電圧に応じた信号を列信号線RL1〜RL4へ出力する。なお、電荷電圧変換部204は、第1の蓄積期間群Taで蓄積された電荷(信号)を保持している。

垂直走査回路401は、第3行目の画素へ供給する第2のリセット信号resf3をノンアクティブなレベルに維持する。これにより、電荷電圧変換部204は、リセットされず、第1の蓄積期間群Taで蓄積された電荷(信号)を保持し続ける。

図11に示す第1のフレーム期間FT1中の時刻t3になると、リセット動作601が全画素P1,1〜P15,25で同時に完了する。この際、全画素における転送部203(図3参照)はオフしているため、リセット動作601によって、電荷電圧変換部204に保持されている電荷が破壊されることはない。

このように、読み出し部10(図2参照)は、第1のフレーム期間から始まる連続した複数のフレーム期間のそれぞれにおいて、第2の画素群PG2における互いに異なる一部の画素から第1の蓄積期間群Taで蓄積された信号における第2の信号を読み出す。

例えば、読み出し部10は、第1のフレーム期間FT1において、第2の画素群PG2における5n+2(2、7、12)行目の画素から第1の蓄積期間群Taで蓄積された信号における第2の信号を読み出す。

例えば、読み出し部10は、第2のフレーム期間FT2において、第2の画素群PG2における5n+3(3、8、13)行目の画素から第1の蓄積期間群Taで蓄積された信号における第2の信号を読み出す。

例えば、読み出し部10は、第3のフレーム期間FT3において、第2の画素群PG2における5n+4(4、9、14)行目の画素から第1の蓄積期間群Taで蓄積された信号における第2の信号を読み出す。

例えば、読み出し部10は、第4のフレーム期間FT4において、第2の画素群PG2における5n+5(5、10、15)行目の画素から第1の蓄積期間群Taで蓄積された信号における第2の信号を読み出す。

読み出し部10は、第2の信号を、出力アンプ309、及びAFE103経由でDSP104へ供給する。DSP(生成部)104は、第1のフレーム期間FT1において読み出し部10により読み出された第1の信号と、複数のフレーム期間FT1〜FT4に渡って読み出し部10により読み出された第2の信号とを合成する。これにより、DSP104は、1フレーム分の静止画用の画像信号を生成する。

したがって、各フレーム期間FT0〜FT4が長くなることを抑制しながら、第1の蓄積期間群Taで蓄積された全画素P1,1〜P15,25の信号を用いて1フレーム分の静止画用の画像信号(画像データ)を生成することができる。このため、フレームレートの低下を抑制しながら、蓄積の同時性が向上した空間的な解像度の高い静止画を得ることができる。特に、動く被写体に対しても、静止画のみを撮影する場合(静止画撮影モード)と変らない良好な静止画像を得ることができる。

なお、撮像センサ102の画素配列PAからの読み出し時点で列方向に間引いて読み出すようにしても構わない。

次に、本発明の第2実施形態に係る撮像装置について説明する。以下では、第1実施形態と異なる部分を中心に説明する。

第2実施形態に係る撮像装置は、基本的な構成は第1実施形態と同様であるが、その動作が第1実施形態と異なる。本実施形態では、20行29列の画素P1,1〜P20,29で構成された画素配列PAを用いて撮像装置の動作を説明することとする。図14は、20行29列の画素P1,1〜P20,29で構成された画素配列PAを示した図である。

具体的には、撮像装置は、その動作モードを動画撮影モードから動画/静止画並行撮影モードへ切り替える場合、動画撮影モードである場合よりも、第2の画素群PG2の画素数に対する第1の画素群PG1の画素数の比率を減らす。

例えば、図15に示すように、撮像装置は、その動作モードが動画撮影モードから動画/静止画並行撮影モードへ切り替わった際に、第2の画素群PG2の画素数に対する第1の画素群PG1の画素数の比率を1/5から1/10へ減らす。すなわち、撮像センサ102の読み出し部10は、動画撮影モードにおいて、上記の比率が1/5であり、第1、6、11、16行目の画素から動画用の信号として第1の信号を読み出している。読み出し部10は、その動作モードが動画撮影モードから動画/静止画並行撮影モードへ切り替わった際に、上記の比率が1/5から1/10へ減り、第1、11行目の画素から動画用の信号として第1の信号を読み出している。なお、図15は、動画/静止画並行撮影モードにおける第2の画素群の画素数に対する第1の画素群の画素数の比率を減した場合の動作を模式的に示した図である。

読み出し部10は、第2の画素群PG2の画素数に対する第1の画素群PG1の画素数の比率を減らした場合、その比率を減らさない場合よりも、複数のフレーム期間FT1〜FT4のそれぞれにおいて第2の画素群PG2から信号を読み出す画素数を増やす。これにより、静止画の構成するために使用する全画素の信号が読み出されるまでの時間を短縮することができる。

例えば、図16に示すように、読み出し部10は、上記の比率を1/5のまま減らさなかった場合、複数のフレーム期間FT1〜FT4のそれぞれにおいて、第2の画素群PG2における4行の画素から第2の信号を読み出す。この場合、4フレーム期間で、静止画生成に使用される全画素の信号を取得することができる。

一方、例えば、図15に示すように、読み出し部10は、上記の比率を1/5から1/10へ減らした場合、複数のフレーム期間FT1〜FT4のそれぞれにおいて、第2の画素群PG2における6行の画素から第2の信号を読み出す。この場合、3フレーム期間で、静止画生成に使用される全画素の信号を取得することができる。すなわち、静止画の構成するために使用する全画素の信号が読み出されるまでの時間(3フレーム期間)は、上記の比率を減らした場合(4フレーム期間)より短い。なお、図16は、動画/静止画並行撮影モードにおける第2の画素群の画素数に対する第1の画素群の画素数の比率を減さなかった場合の動作を模式的に示した図である。図16に示す動作は、図示された行の数が異なる点を除けば、図11に示す動作と同様である。

静止画撮影が終了し、再び動画のみの撮影に戻った時点で、動画に使用する画素行数を元に戻せば、動画像における空間的な解像度も再び回復することができる。

次に、本発明の第3実施形態に係る撮像装置について説明する。以下では、第1実施形態と異なる部分を中心に説明する。

本発明の第3実施形態に係る撮像装置は、電子シャッター機能として、スリットローリング電子シャッター機能を採用している。撮像装置100は、次の構成要素を備える。

撮像センサ102の画素配列PAにおける各画素P11i〜P44iは、図17に示すように、第1のリセット部202を含まない。図17は、本発明の第3実施形態に係る撮像装置における画素P11iの構成図である。

画素P11iにおいて光電変換部201をリセットする場合には、信号txと信号resfを同時にアクティブなレベルとすることで、転送部203及び第2のリセット部206を両方オンする。これにより、光電変換部201の電荷が転送部203及び第2のリセット部206を介して電源へ掃出される。なお、図17は、本発明の第3実施形態に係る撮像装置における画素の構成図である。図17では、画素P11iの構成を例示的に説明しているが、他の画素P12i〜P44iの構成も画素P11iの構成と同様である。

図18は、本実施形態における動画撮影モードの動作を模式的に示した図である。横軸は時刻を表し、縦軸は画素行の位置を示している。図18に示すスリットローリング電子シャッターにおいては、光電変換部201のリセットを行単位で順次に行うため、光電変換部の動作と電荷電圧変換部以降の読み出し回路の動作とを分けずに記載している。

垂直走査回路401は、まず画素配列PAの各行の画素における光電変換部201のリセット動作を順次に完了させていく「リセット走査」を行う。これにより、各行の画素における光電変換部201は、順次に電荷蓄積動作を開始する。なお、図18では、便宜的に、各行のリセット走査が完了するタイミングのみを実線で示しており、各行のリセット走査が開始するタイミングの図示を省略している。

次に、垂直走査回路401は、各行のリセット走査完了から蓄積期間分だけ遅れて、光電変換部201に蓄積された電荷を各画素行毎に順次に読み出し始める「読み出し走査」を行う。これにより、各行の画素における光電変換部201は、順次に電荷蓄積動作を終了する。

図18に示す時刻t1が第1行目のリセット走査の完了時刻であり、時刻t2が第1行目の読み出し走査の開始時刻である。時刻t1〜時刻t2の時間が第1行目の画素に対する第1の蓄積期間T1a1となる。時刻t1、t2のそれぞれ所定時間遅延させた時刻で規定される時間が第2行目の画素に対する第1の蓄積期間T1a2となる。他の第3〜15行に対する第1の蓄積期間T1a3〜T1a15に関しても同様に1つ上の行に対して所定時間遅延させた時刻で規定される。

図18に示すように、複数の画素P1,1〜P15,25は、第1の蓄積期間群T1aで電荷蓄積動作を行う。第1の蓄積期間群T1aは、少なくとも隣接する2行に対して一部が重なっている第1の蓄積期間T1a1〜T1a15の集まりである。

図18に示すように、リセット動作1801a,1801bの完了タイミングは、1行前のリセット動作の完了タイミングに対して、1行前の第1の読み出し動作1804又は間引き動作1805が行われた時間だけ遅延して行われる。これにより、第1の蓄積期間群T1aにおける第1の蓄積期間T1a1〜T1a15のそれぞれは、長さが互いに等しい。なお、リセット動作1801aは、第1の読み出し動作1804が行われる行のリセット動作を示し、リセット動作1801bは、間引き動作1805が行われる行のリセット動作を示す。

図21に、リセット動作1801aに関するタイミングチャートを示す。図21では、第7行目のリセット動作1801aを例示的に説明する。

垂直走査回路401は、第7行目の画素へ供給する転送制御信号tx7をアクティブにする。これにより、第7行目の画素における転送部203が光電変換部201の電荷を電荷電圧変換部204へ転送する。

その後、第7行目の画素へ供給する第2のリセット制御信号resf7をアクティブにする。これにより、第7行目の画素における第2のリセット部206が電荷電圧変換部204をリセットする。

垂直走査回路401は、第7行目の画素へ供給する第2のリセット制御信号resf7及び転送制御信号tx7をアクティブにする。これにより、第7行目の画素における光電変換部201がリセットされる。

なお、第7行目のリセット動作1801aは、(破線の波形で示すような)第1行目の第1の読み出し動作1804と並行して行われる(図18参照)。

図22に、リセット動作1801bに関するタイミングチャートを示す。図22では、第9行目のリセット動作1801bを例示的に説明する。

垂直走査回路401は、第9行目の画素へ供給する第2のリセット制御信号resf9及び転送制御信号tx9をアクティブにする。これにより、第9行目の画素における光電変換部201がリセットされる。

なお、第9行目のリセット動作1801bは、(破線の波形で示すような)第3行目の間引き動作1805と並行して行われる(図18参照)。

図18に白い四角で示す第1の読み出し動作1804は、列共通読み出し回路RC1〜RC4(図2参照)により第1の画素群PG1(図5参照)から信号の読み出し動作が行ごとに順次に行われることを示している。すなわち、垂直走査回路401は、第1の画素群PG1から、第1行目、第6行目、第11行目を順次に選択する。列共通読み出し回路RC1〜RC4は、選択された行の画素における電荷電圧変換部204の電圧に応じた信号を出力部205を介して読み出す。

図19に、第1の読み出し動作に関するタイミングチャートを示す。図19では、第1行目の読み出し動作を例示的に示している。本実施形態における第1の読み出し動作は、第1実施形態における第1の読み出し動作と次の点で異なる。

TG107は、S信号転送スイッチ302へ供給する制御信号tsをアクティブなレベルにする。これにより、S信号転送スイッチ302がオンする。垂直走査回路401は、制御信号tsがアクティブな状態で、第1行目の画素へ供給する転送制御信号tx1をアクティブにする。これにより、第1行目の画素における転送部203が光電変換部201の電荷を電荷電圧変換部204へ転送し、出力部205が電荷電圧変換部204の電圧に応じたS信号を列信号線RL1〜RL4へ出力する。S信号転送スイッチ302は、列信号線RL1〜RL4を介して伝達されたS信号をS信号保持容量304に記憶する。

また、各列の水平転送信号ph1〜ph25が順次アクティブにされている期間に、垂直走査回路401は、第1行目の画素へ供給する第2のリセット制御信号resf1及び転送制御信号tx1をアクティブにする。これにより、第1行目の画素における光電変換部201がリセットされる。その後、垂直走査回路401は、第2のリセット制御信号resf1及び転送制御信号tx1をノンアクティブにする。

図18に幅の広い斜線の四角で示す第3の読み出し動作1807は、第2の画素群PG2(図5参照)の一部からダミー的に信号の読み出し動作が行われることを示している。すなわち、垂直走査回路401は、第2の画素群PG2から第2行目、第7行目、第12行目を順次に選択し、列共通読み出し回路RC1〜RC4は、選択された行の画素における電荷電圧変換部204の電圧に応じた信号を出力部205を介してダミー的に読み出す。

本来、動画撮影のみを考えれば、動画に使用する第1の画素群PG1のみの信号を読み出せばよく、それ以外の第2の画素群PG2の一部(2行目、7行目、12行目)を読み出す必要はない。しかし、後述する静止画撮影とのタイミングの辻褄を合わせるために、動画撮影時にも動画に使用しない第2の画素群PG2の一部を読み出す必要がある。

図18に斜線の四角で示す間引き動作1805は、列共通読み出し回路RC1〜RC4(図2参照)により第2の画素群PG2(図5参照)の残りの行から信号が読み出されないことを示している。すなわち、垂直走査回路401は、第3〜5行目、第8〜10行目、第13〜15行目を順次にスキップし、列共通読み出し回路RC1〜RC4は、スキップされた行の画素における電荷電圧変換部204の電圧に応じた信号を読み出さない。

図20に、間引き動作1805に関するタイミングチャートを示す。図20では、第3行目の間引き動作1805を例示的に示している。

垂直走査回路401は、第3行目の画素へ供給する選択制御信号sel3をノンアクティブなレベルからアクティブなレベルへ遷移させる。これにより、第3行目の画素P3,1〜P3,25が選択状態になる。

垂直走査回路401は、第3行目の画素へ供給する転送制御信号tx3をアクティブなレベルにする。これにより、第3行目の画素における転送部203が光電変換部201の電荷を電荷電圧変換部204へ転送する。これにより、電荷電圧変換部204は、第1の蓄積期間T1a3で蓄積された電荷(信号)を保持する。

垂直走査回路401は、第3行目の画素へ供給する選択制御信号sel3をアクティブなレベルからノンアクティブなレベルへ遷移させる。これにより、第3行目の画素P3,1〜P3,25が非選択状態になる。

この間引き動作においては、画素の信号を読み出す必要がないため、ts、tn、phといった信号は動かさずにノンアクティブなレベルに固定したままとする。

このように、画素からの信号を読み出す動作を行わないため、1行を間引く動作に必要な時間は1行の画素信号を読み出すのに対して遥かに短い時間で済む。

他の点は、第1実施形態における動画撮影モードの動作と同様である。

次に、動画/静止画並行撮影モードの動作について、図23を用いて説明する。図23は、動画/静止画並行撮影モードの動作を模式的に示した図である。以下では動画撮影モードの動作と異なる部分を中心に説明する。

動画/静止画並行撮影モードでは、フレーム期間FT12〜FT14において、動画撮影モードと異なるリセット動作2301a,2301bが行われる。リセット動作2301aは、後述の第2の読み出し動作2304が行われる行のリセット動作を示し、リセット動作2301bは、間引き動作2305が行われる行のリセット動作を示す。

図24に、リセット動作2301aに関するタイミングチャートを示す。図24では、第7行目のリセット動作2301aを例示的に説明する。

垂直走査回路401は、第7行目の画素へ供給する第2のリセット制御信号resf7及び転送制御信号tx7をノンアクティブに維持する。これにより、第7行目の画素における電荷電圧変換部204は、リセットされず、第1の蓄積期間T1a7に蓄積された信号を保持し続ける。

なお、第7行目のリセット動作2301aは、(破線の波形で示すような)第1行目の第1の読み出し動作1804と並行して行われる(図23参照)。

図25に、リセット動作2301bに関するタイミングチャートを示す。図25では、第9行目のリセット動作2301bを例示的に説明する。

垂直走査回路401は、第9行目の画素へ供給する第2のリセット制御信号resf9及び転送制御信号tx9をノンアクティブに維持する。これにより、第9行目の画素における電荷電圧変換部204は、リセットされず、第1の蓄積期間T1a9に蓄積された信号を保持し続ける。

また、動画/静止画並行撮影モードでは、第3の読み出し動作1807が行われない代わりに、図23に破線の四角で示す第2の読み出し動作2304が行われる。第2の読み出し動作2304は、列共通読み出し回路RC1〜RC4(図2参照)により第2の画素群PG2(図5参照)の一部から信号の読み出し動作が行ごとに順次に行われることを示している。

すなわち、垂直走査回路401は、第1のフレーム期間FT11において、第2の画素群PG2から5n+2(2、7、12)行目の画素を順次に選択する。列共通読み出し回路RC1〜RC4は、選択された行の画素における電荷電圧変換部204の電圧に応じた信号(第1の蓄積期間群T1aで蓄積された信号における第2の信号)を出力部205を介して読み出す。

また、垂直走査回路401は、第2のフレーム期間FT12において、第2の画素群PG2から5n+3(3、8、13)行目の画素を順次に選択する。列共通読み出し回路RC1〜RC4は、選択された行の画素における電荷電圧変換部204の電圧に応じた信号(第1の蓄積期間群T1aで蓄積された信号における第2の信号)を出力部205を介して読み出す。

また、垂直走査回路401は、第3のフレーム期間FT13において、第2の画素群PG2から5n+4(4、9、14)行目の画素を順次に選択する。列共通読み出し回路RC1〜RC4は、選択された行の画素における電荷電圧変換部204の電圧に応じた信号(第1の蓄積期間群T1aで蓄積された信号における第2の信号)を出力部205を介して読み出す。

また、垂直走査回路401は、第4のフレーム期間FT14において、第2の画素群PG2から5n+5(5、10、15)行目の画素を順次に選択する。列共通読み出し回路RC1〜RC4は、選択された行の画素における電荷電圧変換部204の電圧に応じた信号(第1の蓄積期間群T1aで蓄積された信号における第2の信号)を出力部205を介して読み出す。

列共通読み出し回路RC1〜RC4は、複数のフレーム期間FT11〜FT14のそれぞれにおいて、第2の画素群PG2における互いに異なる一部の画素から第1の蓄積期間群T1aで蓄積された信号における第2の信号を読み出す。

図26に、第2の読み出し動作2304に関するタイミングチャートを示す。図26では、第2行目のリセット動作2304を例示的に説明する。図26では、第2行目の第2の読み出し動作2304を例示的に説明する。動画/静止画並行撮影モードにおける第2の読み出し動作2304は、動画モードにおける第1の読み出し動作(図19参照)と次の点で異なる。

垂直走査回路401は、制御信号tsがアクティブな状態で、第2行目の画素へ供給する転送制御信号tx2をノンアクティブなレベルに維持する。これにより、第2行目の画素における電荷電圧変換部204が第1の蓄積期間T1a2に蓄積された信号を保持し続け、出力部205が電荷電圧変換部204の電圧に応じたS信号を列信号線RL1〜RL4へ出力する。

動画/静止画並行撮影モードでは、動画モードと異なる間引き動作2305が行われる。図27は、間引き動作2305に関するタイミングチャートを示す。図27では、第3行目の間引き動作2305を例示的に説明する。動画/静止画並行撮影モードにおける間引き動作2305は、動画モードにおける間引き動作(図20参照)と次の点で異なる。

垂直走査回路401は、第3行目の画素へ供給する転送制御信号tx3をノンアクティブなレベルに維持する。これにより、第3行目の画素におけるにおける電荷電圧変換部204は、第1の蓄積期間T1a3に蓄積された信号を保持し続ける。

このように、各フレーム期間FT10〜FT14が長くなることを抑制しながら、第1の蓄積期間群T1aで蓄積された全画素P1,1〜P15,25の信号を用いて1フレーム分の静止画用の画像信号(画像データ)を生成することができる。

次に、本発明の第4実施形態に係る撮像装置100iについて、図28を用いて説明する。図28は、本発明の第4実施形態に係る撮像装置100iの構成図である。以下では、第3実施形態と異なる部分を中心に説明する。

撮像装置100iは、AFE103を備えず、撮像センサ102(図1参照)に代えて撮像センサ102iを備える。撮像装置100iでは、AD変換器を撮像センサ102i内に配置するため、AFE103が不要である。

撮像センサ102iは、図29に示すように、画素配列PAの各列に対応したAD(アナログ−ディジタル)変換器を有する、いわゆるカラムAD構成を用いたものである。具体的には、撮像センサ102iの構成は、次の点で第1実施形態と異なる。なお、図29は、本発明の第4実施形態における撮像センサ102iの構成図である。

撮像センサ102iは、読み出し部10i、A/D変換部20i、記憶部30i、制御部40i、及びLVDS部2905を含む。

読み出し部10iは、複数の列共通読み出し回路RC1i〜RC4iを含む。複数の列共通読み出し回路RC1〜RC4のそれぞれは、図30に示すように、その内部構成が第1実施形態と異なる。列共通読み出し回路RC1は、水平転送スイッチ306、307を含まない。列共通読み出し回路RC1におけるS信号保持容量304及びN信号保持容量305に保持された信号は、それぞれ、A/D変換部20iへ出力される。なお、図30は、本発明の第4実施形態における列共通読み出し回路RC1の構成図である。

図29に示すA/D変換部20iは、複数の列A/D変換器ADC1i〜ADC4iを含む。複数の列A/D変換器ADC1i〜ADC4iは、複数の列共通読み出し回路RC1i〜RC4iから出力された信号(S信号、N信号)を受ける。複数の列A/D変換器ADC1i〜ADC4iのそれぞれは、受けた信号(アナログ信号)をA/D変換して、変換した信号(デジタル信号)を記憶部30iへ供給する。

なお、A/D変換の方式としては、三角波を掃印するランプ型、逐次比較(Successive Approximation)型などがあるが、画素からのアナログ信号をディジタル信号に変換できるものならどのようなタイプのものでもよい。

記憶部30iは、メモリ(RAM)2903を含む。メモリ2903は、A/D変換部20iによりA/D変換された信号を一時的に記憶する。

制御部40iは、メモリ制御部2904を含む。メモリ制御部2904は、メモリ2903へ供給される信号の記憶動作と、メモリ2903からLVDS部2905への画素信号の読み出し動作とを制御する。

LVDS部2905は、メモリ2903から読み出された画素信号(S信号、N信号)をシリアライズした後、S信号とN信号との差動信号に生成する。LVDS部2905は、生成した差動信号を出力端子から後段(DSP104)へ出力する。

このように撮像センサ内で画素信号をディジタル信号化して出力する場合、シリアル化して出力した方が、端子数の観点から有利である。

また、列A/D変換器の後段に容量の大きなメモリを有する場合、1行分の画素信号をメモリまで並列に処理できるため、それ以降の信号転送速度に制約されずメモリまでの信号読み出し速度を非常に高速化することができる。このため、画素信号の読み出しにおいて間引き動作をする必要がなくなる。

図31に、本実施形態における動画撮影モードの動作を模式的に示す。図31では、横軸が時刻を表し、縦軸における上段の部分が光電変換部201からメモリ2903までの信号の読み出し動作に関する画素行の位置を表し、縦軸における下段の部分がメモリ2903から信号の出力動作を表す。

図31に示すように、第1の蓄積期間群T2aは、少なくとも隣接する2行に対して同じ長さの一部が重なっている第1の蓄積期間T2a1〜T2a15の集まりである。すなわち、リセット動作3101の完了タイミングは、1行前のリセット動作の完了タイミングに対して、1行前の第1の読み出し動作3102が行われた時間だけ遅延して行われる。これにより、第1の蓄積期間群T2aにおける第1の蓄積期間T2a1〜T2a15のそれぞれは、長さが互いに等しい。その遅延の長さは、間引き動作1805が行われないため、一定の長さ(第1の読み出し動作3102の時間)になっている。

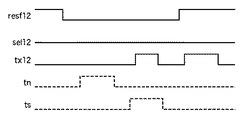

図33に、リセット動作3101に関するタイミングチャートを示す。図33では、第12行目のリセット動作3101を例示的に説明する。

垂直走査回路401は、第12行目の画素へ供給する第2のリセット制御信号resf12をアクティブなレベルからノンアクティブなレベルへ遷移させる。これにより、第12行目の画素における第2のリセット部206がオフして、電荷電圧変換部204のリセットが解除される。

そして、垂直走査回路401は、第12行目の画素へ供給する第2のリセット制御信号resf12及び転送制御信号tx12をアクティブにする。これにより、第12行目の画素における光電変換部201がリセットされる。その後、垂直走査回路401は、第2のリセット制御信号resf1をアクティブなレベルに維持するとともに、転送制御信号tx1をノンアクティブにする。

なお、第12行目のリセット動作3101は、(破線の波形で示すような)第1行目の第1の読み出し動作3102と並行して行われる(図31参照)。

図32に、第1の読み出し動作3102に関するタイミングチャートを示す。図32では、第1行目の読み出し動作を例示的に示している。本実施形態における第1の読み出し動作は、第3実施形態における第1の読み出し動作(図19参照)と次の点で異なる。

垂直走査回路401は、第1行目の画素へ供給する第2のリセット制御信号resf1をアクティブなレベルからノンアクティブなレベルへ遷移させる。これにより、第1行目の画素における第2のリセット部206がオフして、電荷電圧変換部204のリセットが解除される。

TG107は、N信号転送スイッチ303へ供給する制御信号tnをアクティブなレベルにする。これにより、N信号転送スイッチ303がオンする。これにより、第1行目の画素における出力部205が電荷電圧変換部204の電圧に応じたN信号を列信号線RL1〜RL4へ出力する。N信号転送スイッチ303は、列信号線RL1〜RL4を介して伝達されたN信号をN信号保持容量305に記憶する。TG107は、制御信号tnをノンアクティブなレベルにする。

その後、TG107は、S信号転送スイッチ302へ供給する制御信号tsをアクティブなレベルにする。これにより、S信号転送スイッチ302がオンする。垂直走査回路401は、制御信号tsがアクティブな状態で、第1行目の画素へ供給する転送制御信号tx1をアクティブにする。これにより、第1行目の画素における転送部203が光電変換部201の電荷を電荷電圧変換部204へ転送し、出力部205が電荷電圧変換部204の電圧に応じたS信号を列信号線RL1〜RL4へ出力する。S信号転送スイッチ302は、列信号線RL1〜RL4を介して伝達されたS信号をS信号保持容量304に記憶する。

また、各列の水平転送信号ph1〜ph25が順次アクティブにされている期間に、垂直走査回路401は、第1行目の画素へ供給する第2のリセット制御信号resf1及び転送制御信号tx1をアクティブにする。これにより、第1行目の画素における光電変換部201がリセットされる。その後、垂直走査回路401は、第2のリセット制御信号resf1をアクティブなレベルに維持するとともに、転送制御信号tx1をノンアクティブにする。

図31に示す出力動作3103は、メモリ制御部2904により制御されて、メモリ2903に格納されている信号がLVDS部2905及び出力端子を介してDSP104へ出力される動作を1行分単位で示している。

枠内のアルファベット(a〜d)は信号がどの蓄積期間群T2a〜T2dで蓄積されたかを示し、数字(1〜15)はどの画素行の信号であるかを示している。例えば、a1と記載した枠は、第1の蓄積期間T2aにおいて1行目に蓄積された信号を出力していることを示す。

このように、制御部40iは、各フレーム期間において、第1の画素群PG1(5n+1行目)の全てに対する直前のフレーム期間内の蓄積期間群(T2a〜T2d)で蓄積された信号における第1の信号を更新するように、メモリ2903を制御する。そして、制御部40iは、更新した第1の信号をメモリ2903から読み出す。

例えば、動画撮影モードでは、第1のフレーム期間FT21において、第1の画素群PG1(5n+1行目)により直前のフレーム期間FT0内の第1の蓄積期間群T2aで蓄積された第1の信号a1,a6,a11をメモリ2903から読み出す。

例えば、動画撮影モードでは、第2のフレーム期間FT22において、第1の画素群PG1(5n+1行目)により直前のフレーム期間FT1内の第2の蓄積期間群T2bで蓄積された第1の信号b1,b6,b11をメモリ2903から読み出す。

LVDS部2905は、メモリ2903から制御部40iにより読み出された第1の信号を出力端子経由でDSP104へ供給する。これにより、DSP(生成部)104は、各フレーム期間に読み出された第1の信号から、1フレーム分の動画用の画像信号(画像データ)を生成する。

次に、動画/静止画並行撮影モードの動作について、図34を用いて説明する。図34は、動画/静止画並行撮影モードの動作を模式的に示した図である。以下では動画撮影モードの動作と異なる部分を中心に説明する。

図34に斜線の四角で示す第4の読み出し動作3402は、列共通読み出し回路RC1i〜RC4i(図29参照)により第2の画素群PG2(図5参照)から信号が読み出されるがメモリ2903に記憶されないことを示している。すなわち、メモリ制御部2904は、第2〜5行目、第7〜10行目、第12〜15行目の信号を順次にスキップし、スキップされた行の画素の信号をメモリ2903に記憶させない。

これにより、第2のフレーム期間FT22では、メモリ2903において、動画に使用しない第2の画素群PG2(5n+1行目以外の行)の信号が更新されない。メモリ2903は、第2の画素群PG2により第1の蓄積期間群T2aで蓄積された信号を保持し続ける。一方、メモリ2903において、動画に使用する第1の画素群G1(5n+1行目)の信号は更新される。

同様に、第3のフレーム期間FT23、第4のフレーム期間FT24でも、メモリ2903において、動画に使用しない第2の画素群PG2(5n+1行目以外の行)の信号が更新されない。メモリ2903は、第2の画素群PG2により第1の蓄積期間群T2aで蓄積された信号を保持し続ける。

また、メモリ制御部2904は、メモリ2903に保持された第2の画素群PG2(図5参照)の一部の信号を読み出す。

すなわち、メモリ制御部2904は、第1のフレーム期間FT21において、第2の画素群PG2から5n+2(2、7、12)行目の画素の信号(第1の蓄積期間群T2aで蓄積された信号における第2の信号)を選択して読み出す。なお、メモリ制御部2904が、第1のフレーム期間FT21において、第1の画素群PG1から画素の信号(第1の蓄積期間群T2aで蓄積された信号における第1の信号)を選択して読み出す点は、動画モードと同様である。

また、メモリ制御部2904は、第2のフレーム期間FT22において、第2の画素群PG2から5n+3(3、8、13)行目の画素の信号(第1の蓄積期間群T2aで蓄積された信号における第2の信号)を選択して読み出す。

また、メモリ制御部2904は、第3のフレーム期間FT23において、第2の画素群PG2から5n+4(4、9、14)行目の画素の信号(第1の蓄積期間群T2aで蓄積された信号における第2の信号)を選択して読み出す。

また、メモリ制御部2904は、第4のフレーム期間FT24において、第2の画素群PG2から5n+5(5、10、15)行目の画素の信号(第1の蓄積期間群T2aで蓄積された信号における第2の信号)を選択して読み出す。

このように、メモリ制御部2904は、連続する複数のフレーム期間FT21〜FT24のそれぞれにおいて、第2の画素群PG2における互いに異なる一部の画素から第1の蓄積期間群T2aで蓄積された信号における第2の信号を読み出す。LVDS部2905は、メモリ制御部2904により読み出された第1の信号及び第2の信号を出力端子経由でDSP104へ供給する。DSP(生成部)104は、第1のフレーム期間FT21においてメモリ制御部2904により読み出された第1の信号と、複数のフレーム期間FT21〜FT24においてメモリ制御部2904により読み出された第2の信号とを合成する。これにより、DSP104は、1フレーム分の静止画用の画像信号を生成する。

本実施形態によれば、動画に使用せず静止画のみに使用する画素の信号を一時的に保持する記憶手段がディジタル値で保持するメモリになることにより、大容量のメモリを比較的容易に構成することができる。

また、画素から読み出された信号をディジタルのメモリに保持させるので、アナログのメモリにおける問題(微小な欠陥に起因したリーク電流等)を回避できる。

なお、本実施形態では動画に使用する画素と使用しない画素との区別を行単位でのみ行ったが、ディジタルのメモリを使用していることで、列方向(水平方向)でも区別してもよい。これにより、データをフレームごとに更新する行と更新しない行とをより細かく制御することができ、より効率的な静止画用のデータの転送が可能となる。

また、N信号を先に読み出してからS信号を読み出すことが出来、リセットノイズも除去できる。この場合、画質を容易に向上できる。