本発明は、液晶パネルを備える液晶装置に関し、特に、液晶パネルの製造上の特性ばらつきを吸収する液晶装置とその液晶装置の製造方法に関するものである。

近年、強誘電性液晶素子などに代表されるメモリ性液晶パネルが盛んに研究開発され、低消費電力の特徴を生かして表示装置や液晶シャッター等に用いられている。しかし、強誘電性液晶素子の動作は、温度に対して敏感であり、また、湿度の影響を受けることから、湿度を考慮した温度補償を行う液晶装置が開示されている(例えば特許文献1参照)。

この特許文献1に開示されている従来の液晶装置の概略を図12、図13に基づいて説明する。図12において液晶装置101は、メモリ性液晶パネル120と温度センサー103と駆動回路110とによって構成される。ここで、メモリ性液晶パネル120は、スメクチック相を示す強誘電性液晶素子であるが、構造は後述する。温度センサー103は、温度情報としての温度検出信号T1を出力して駆動回路110に供給する。駆動回路110は、制御回路111と電源回路112と走査電極駆動回路113と信号電極駆動回路114によって構成される。制御回路111は、温度センサー103からの温度検出信号T1を入力し、制御信号S1、S2、S3を出力する。

電源回路112は、制御回路111からの制御信号S3を入力し、極性の異なる複数の出力電圧Voutを出力する。走査電極駆動回路113は、メモリ性液晶パネル120の走査電極を駆動する回路であり、出力電圧Voutと制御信号S1を入力して走査電極駆動電圧Vcomを出力する。信号電極駆動回路114は、メモリ性液晶パネル120の信号電極を駆動する回路であり、出力電圧Voutと制御信号S2を入力して信号電極駆動電圧Vsegを出力する。メモリ性液晶パネル120は、駆動回路110からの走査電極駆動電圧Vcomと信号電極駆動電圧Vsegを入力して駆動される。

ここで、駆動回路110の制御回路111は、温度センサー103からの温度検出信号T1を入力して、温度が所定温度以上の時は、メモリ性液晶パネル120に供給する駆動電圧のパルス幅を温度上昇に沿って短くし、メモリ性液晶パネル120の温度特性を補償する。また、温度が所定温度以下の時は、湿度の影響を考慮して所定温度でのパルス幅を継続するか、又は温度低下に沿ってパルス幅を短くしてメモリ性液晶パネル120の動作マージンを高める駆動を行う。

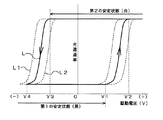

次に図13に基づいて、特許文献1に示される従来の液晶装置の具体的な動作の一例を説明する。図13において、X軸は検出された温度を示し、Y軸は駆動電圧(すなわち走査電極駆動電圧Vcomと信号電極駆動電圧Vsegの合成駆動電圧)のパルス幅を示している。

ここで、所定温度Tは第1の温度補償範囲と第2の温度補償範囲の境目となる温度であり、メモリ性液晶パネル120の特性から0℃以下に設定されている。そして、検出された温度が所定温度Tより高い場合は、図示するように第1の温度補償範囲となり、また、検出された温度が所定温度T(約−2℃)より低い場合は、図示するように第2の温度補償範囲となる。

ここで、温度センサー103によって検出された温度が第1の温度補償範囲である場合、駆動電圧は、液晶の温度特性に基づいて低温側から高温側に向かってパルス幅が減少す

るので、所定温度Tでパルス幅は最大(約5500μS)となる。この第1の温度補償範囲におけるパルス幅の値は、制御回路111に記憶されている第1の温度補償範囲におけるパルス幅の変換テーブル(図示せず)を参照して変化量が決められている。そして、このパルス幅の増減カーブは、第1の温度補償範囲(すなわち、+60℃〜所定温度T)におけるメモリ性液晶パネル120の閾値の温度特性に基づいて決定されており、このパルス幅の増減カーブによって、第1の温度補償範囲でのメモリ性液晶パネル120の表示動作を補償し、温度に対して安定した動作を実現する。

また、温度センサー103によって検出された温度が第2の温度補償範囲である場合、駆動電圧のパルス幅は、所定温度Tで最大となったパルス幅とほぼ同一のパルス幅となる。この第2の温度補償範囲におけるパルス幅の値は、制御回路111に記憶されている第2の温度補償範囲におけるパルス幅の変換テーブル(図示せず)を参照して決められている。この第2の温度補償範囲でのパルス幅が、所定温度Tでのパルス幅とほぼ同一である理由は、強誘電性液晶素子の閾値の湿度特性に基づくものであり、低温度低湿度の条件で閾値が低下した場合でも、一定の動作マージンを確保することを目的としている。

次に公知ではあるが本発明を理解する助けとなるので、強誘電性液晶素子などに代表されるメモリ性液晶パネルの構成と動作について以下説明する。

まず、強誘電性液晶素子を用いたメモリ性液晶パネルの構造を図14に基づいて説明する。図14(a)はメモリ性液晶パネルの偏光板配置の構成を模式的に示した平面図であり、液晶パネル120は、クロスニコルに合わせた偏光板121a、121bの間に、偏光板121aの偏光軸Cと偏光板121bの偏光軸Dのどちらか一方と、液晶分子の第1の安定状態(矢印E)もしくは、第2の安定状態(矢印F)のときの分子長軸方向のどちらかとが、ほぼ平行になるように液晶層122を配置する。ここで、図14(a)においては、偏光板121aの偏光軸Cと第1の安定状態(矢印E)のときの分子長軸方向が、ほぼ平行になるように配置されている。

次に図14(b)は、液晶パネル120の構造を模式的に示した断面図である。図14(b)において、液晶パネル120は、少なくとも二つの安定状態を持つメモリ性液晶である液晶層122を挟持する一対のガラス基板123a、123bから構成される。また、このガラス基板123aと123bはシール材126によって固着されている。そして、ガラス基板123a、123bの対向面には駆動電極としての複数の走査電極124と、信号電極125が設けられており、その上に配向膜127a、127bが蒸着されている。

さらに一方のガラス基板123aの外側には、前述した如く、液晶層122の液晶分子の第1もしくは第2の安定状態の時の分子長軸方向が平行になるように第1の偏光板121aが設けられており、他方のガラス基板123bの外側には、第1の偏光板121aの偏光軸と90度異なるようにして第2の偏光板121bが設けられている。

次に、図14(a)、図14(b)で示した液晶パネル120の動作を説明する。図15は、液晶パネル120の駆動電圧に対する光透過率L(実線)の変化を示している。ここで、強誘電性液晶のスイッチング、つまり一方の安定状態から他方の安定状態への転移は、駆動電圧のパルス幅値とパルス高値との積の値が閾値以上の値となる電圧を強誘電性液晶に印加した場合にのみ起こる。図15において、液晶パネル120は駆動電圧の極性の違いによって、第1の安定状態(非透過(黒)表示)か、第2の安定状態(透過(白)表示)かのいずれかが選択される。

ここで、駆動電圧をプラス方向に増加させたとき、光透過率Lが変化し始める電圧値を

V1、光透過率Lの変化が飽和する電圧値をV2とする。次に駆動電圧を減少させ、さらに逆極性のマイナス方向に電圧を増加させて光透過率Lが減少し始める電圧値をV3、光透過率Lの変化が飽和する電圧値をV4とする。このように液晶パネル120は、強誘電性液晶分子の閾値以上の駆動電圧(すなわちV2以上のプラス印加電圧)が印加された場合に第2の安定状態が選択され、また、強誘電性液晶分子の逆極性の閾値以上の駆動電圧(すなわちV4以上のマイナス印加電圧)が印加された場合は、第1の安定状態が選択される。そして、その後、駆動電圧が0Vになってもメモリ性効果によって、それぞれの安定状態は維持される。

この結果、図14(a)に示すように偏光板121a、121bを配置すると、第2の安定状態で白表示(透過状態)、第1の安定状態で黒表示(非透過状態)となる。尚、偏光板121a、121bの配置を変えることにより、第2の安定状態で黒表示(非透過状態)、第1の安定状態で白表示(透過状態)とすることも出来る。

ここで、強誘電性液晶素子を用いた液晶パネル120の閾値は、ガラス基板123aと123bのギャップの僅かな違い等によって大きく影響を受けるので、製造上のばらつきによって閾値(V2及びV4)がそれぞれ異なる液晶パネルが製造されることになる。すなわち、図15において、液晶パネル120の閾値がマイナス方向にずれると光透過率特性は、光透過率L1(破線)のように図面上左側にシフトし、また、液晶パネル120の閾値がプラス方向にずれると、光透過率L2(破線)のように図面上右側にシフトする。

そして、このように閾値のばらついた液晶パネルを標準的な駆動波形で駆動すると、一方の安定状態から他方の安定状態へ転移するための動作マージンが低下して、表示不良を起こすパネルが発生し問題である。しかし、高精度なギャップ管理には限界があり、製造コストも増大する。また、液晶パネルの閾値を厳しく管理して、規格内のパネルのみを良品にすると、歩留まりが著しく低下して量産が困難となる。このため、強誘電性液晶素子に代表されるメモリ性液晶パネルは、低消費電力であるという優れた特徴があるが、液晶パネルの特性ばらつきの問題を解決しなければ、製品の安定した量産化は困難である。

特開2007−248984号公報(第9頁、第1図)

しかしながら、特許文献1の従来の液晶装置は、液晶パネルの動作を補償するために変換テーブルを備え、湿度特性を考慮した温度補償を実現しているが、液晶パネルの製造上のばらつきによって閾値がばらつく問題に関して考慮されておらず、製造上の特性ばらつきを補正し、吸収するための方策は、開示も示唆もされていない。すなわち、駆動電圧のパルス幅等を調整する変換テーブルは従来の液晶装置では一つのみであるので、温度変化等に対しての補償は出来るが、閾値のばらつきに応じて駆動電圧を調整して液晶パネルの動作マージンの低下を防ぐことは出来ない。

本発明の目的は上記課題を解決し、液晶パネルの製造上の特性ばらつきを吸収して動作マージンを確保し、歩留まり低下を改善する液晶装置とその液晶装置の製造方法を提供することである。

上記課題を解決するために、本発明の液晶装置とその液晶装置の製造方法は、下記記載の構成と製造方法を採用する。

本発明の液晶装置の製造方法は、液晶パネルと、この液晶パネルに駆動電圧を印加するための駆動回路と、この駆動回路を制御する制御手段と、駆動回路と制御手段とを電気的に接続する回路基板とを備えた液晶装置の製造方法であって、温度情報によって駆動電圧を変化させる変換テーブルを複数有し、複数の外部端子を備えた駆動回路を用意する工程と、複数の出力信号を出力する制御手段を用意する工程と、回路基板は、駆動回路と接続するための複数の駆動回路側電極と、制御手段と接続するための複数の制御手段側電極とを備え、駆動回路側電極と制御手段側電極とを接続する電極パターンが、それぞれ異なる複数種類の前記回路基板を用意する工程と、液晶パネルの固有の特性を検出する工程と、検出された液晶パネルの固有の特性に基づいて、異なる複数種類の回路基板から、一つの種類の回路基板を選択し、複数の変換テーブルのうちの一つの変換テーブルのみが機能するように、選択された回路基板で駆動回路と制御手段とを電気的に接続する工程を備えたことを特徴とする。

また、駆動回路側電極と制御手段側電極とを接続する電極パターンが、それぞれ異なる複数種類の回路基板とは、接続されている駆動回路側電極と、制御手段側電極との組み合わせが、それぞれの異なる回路基板であることを特徴とする。

また、駆動回路側電極と制御手段側電極とを接続する電極パターンが、それぞれ異なる複数種類の回路基板とは、駆動回路側電極と制御手段側電極とを接続する複数の配線のうち、一部の配線が切断されており、その切断されている位置が異なる回路基板であることを特徴とする。

また、変換テーブルを選択する切替信号と駆動回路に供給する電源との電極パターンが形成された選択手段を、駆動回路とこの駆動回路を制御する外部の制御手段との間に配設する工程を有することを特徴とする。

また、選択手段には、切替信号と電源の電極パターンが隣接して形成されていることを特徴とする。

また、選択手段に液晶パネルの固有の特性に応じて切替信号と電源とを接続するか否か

を選択する工程を有することを特徴とする。

また、切替信号の接続に応じて複数の変換テーブルのうちの一つの変換テーブルを選択する切替手段を駆動回路が有することを特徴とする。

また、外部端子を選択手段に隣接する駆動回路の片側に配設されていることを特徴とする。

また、少なくとも二つの安定状態を有するメモリ性液晶パネルを搭載する工程を有することを特徴とする。

また、選択手段は回路基板であることを特徴とする。

上記の如く本発明によれば、液晶装置内に駆動電圧を変化させる複数の変換テーブルを備えているので、液晶パネルの特性ばらつきに応じて複数の変換テーブルの中から一つの変換テーブルを選択することが出来る。これにより、液晶パネルに製造上の特性ばらつきがあっても、最適な駆動電圧を出力できるので、その特性ばらつきを吸収して動作マージンが高く信頼性に優れた液晶装置とその製造方法を提供することが出来る。

また、液晶装置とシステム側とを電気的に接続する選択手段によって複数の変換テーブルの中から一つの変換テーブルを選択するので、ばらつきを調整し吸収するための特別な切り替え手段が不要であり、部品点数が少なく取り扱いが容易な液晶装置を提供することが出来る。

また、液晶装置側に、特性ばらつきに対応する複数の変換テーブルが用意されているので、液晶装置単独で液晶パネルの特性ばらつきを吸収することが出来る。このために、システム側からの特性ばらつきに対する制御や調整が不要であり、システム側の制御が簡素化されると共に、システムに液晶装置を搭載する製造ラインの組み立て工程や検査工程を簡素化することが出来る。

以下図面により本発明の実施の形態を詳述する。

[第1の実施形態の液晶装置の回路構成の説明]

まず、本発明の液晶装置に係わる回路構成の概略を説明する。図1は本発明の第1の実施形態の液晶装置の回路構成の概略を示す回路ブロック図である。図1において、1は本発明の液晶装置であり、液晶パネル10と駆動回路としての駆動IC20を備えている。30は選択手段としてのフレキシブルプリント基板(以下、FPCと略す)である。本実施形態ではFPCを使用したが、電極パターンが形成できれば、いかなる回路基板を用いても構わない。60は液晶装置1を外部から制御する制御手段としての制御部である。ここで、FPC30は、液晶装置1の駆動IC20と制御部60の間に配設して、制御部60からの電源や各種の情報を駆動IC20に伝達する機能を有している。

次に駆動IC20の内部構成と外部端子の接続を説明する。駆動IC20は、一例として4個の変換テーブル21a〜21d(以下、LUT21a〜21dと略す)と、切替手段としてのセレクト回路22と、電源回路23と、出力回路24とを備えている。また、25a〜25fは複数の外部端子であり、FPC30の電極にそれぞれ接続され、FPC30を介して制御部60の電源や信号線と電気的に接続される。

ここで、外部端子25aは、FPC30を介して制御部60からの電源VDDに接続し、駆動IC20に電源VDDを供給する。また、外部端子25cは、FPC30を介して制御部60からの電源VSSに接続し、駆動IC20に電源VSSを供給する。また、外部端子25bと25dは、FPC30の電極パターンに接続されて切替信号LT0、LT1として駆動IC20に入力する。この切替信号LT0、LT1は、FPC30の内部で一例として破線で示すように電源VSSに接続されるが、接続は4通りあり、詳細は後述する。また、外部端子25eは、駆動IC20の内部で電源VDDに接続し、FPC30に接続される。また、外部端子25fは、FPC30を介して制御部60からのシリアル信号SIに接続し、駆動IC20の内部のLUT21a〜21dと出力回路24にシリアル信号SIを供給する。図示していないが、このシリアル信号SIの他に制御信号として、イネーブル信号等がある。

また、駆動IC20の内部の4個のLUT21a〜LUT21dは、シリアル信号SIを入力して、それぞれ異なるパルス幅信号P1a〜P1dを出力する。尚、LUT21a〜21dは、不揮発性メモリやROM等により構成され、シリアル信号SIによって伝達される温度情報に応じて、パルス幅信号P1a〜P1dを出力する。

また、セレクト回路22は、LUT21a〜LUT21dからのパルス幅信号P1a〜P1dと、外部端子25b、25dからの切替信号LT0、LT1を入力し、切替信号LT0、LT1の論理に基づいてLUT21a〜LUT21dの中から一つのLUTのみを選択して、選択パルス幅信号P2を出力する。

また、電源回路23は、図示しないが電源VDDとVSSを入力し、コンデンサ等のチャージポンプ式の昇圧回路により、液晶パネル10を駆動するための電源±VS、±VD、±VHを出力する。また、出力回路24は、選択パルス幅信号P2とシリアル信号SIと電源±VS、±VD、±VHを入力して、液晶パネル10に、セグメント駆動電圧VSEGとコモン駆動電圧VCOMを出力する。

また、制御部60は、内部にシステムの全体を制御するマイクロコンピュータ61(以下、マイコン61と略す)と電源回路62、温度センサー63等を備えており、前述したように、FPC30を介して液晶装置1の駆動IC20に、電源VDD、VSSとシリアル信号SIを供給する。

[第1の実施形態の液晶装置の機械的な構成の説明]

次に、本発明の液晶装置の機械的な構成の概略を図2の模式的な外形図に基づいて説明する。図2において、液晶装置1の液晶パネル10は、少なくとも二つの安定状態を持つメモリ性液晶である液晶層(図示せず)を挟持する一対のガラス基板11a、11bを有している。そして、ガラス基板11a、11bの対向面には駆動電極としての複数の走査電極と信号電極(図示せず)が設けられており、表示エリア12には、マトリクス状の画素13が配置され、様々な情報を表示することが出来る。尚、液晶パネル10の構造は、図14の従来例で示した液晶パネルと同様であるので詳細な説明は省略する。また、液晶パネル10の画素はマトリクス状の配置には限定されず、例えば、7セグメントや固有の模様などでも良い。

また、駆動IC20は、液晶パネル10の一方のガラス基板11b上に実装され、駆動IC20から出力される複数のコモン駆動電圧VCOMとセグメント駆動電圧VSEGは、ガラス基板11b上に形成される透明電極(図示せず)を介して走査電極と信号電極に接続される。

また、FPC30は、一方の端部に複数の電極31a〜31gが形成され、液晶パネル10のガラス基板11bの透明電極(図示せず)に導電性接着剤(図示せず)等によって固着される。また、FPC30の他方の端部には複数の電極32a〜32eが形成され、制御部60の電極(図示せず)と導電性接着剤(図示せず)等によって固着される。これにより、FPC30を介して、液晶装置1の液晶パネル10と外部の制御部60とは、電気的機械的に結合される。

また、駆動IC20の外部端子25a〜25fは、FPC30の電極31a〜31gに隣接して駆動IC20の片側に並んで配設される。これにより、駆動IC20の外部端子25a〜25fとFPC30の電極31a〜31gは、最短距離のパターンで配線することが出来る。

また、制御部60はプリント基板等によって構成され、マイコン61、電源回路62、温度センサー63等が実装される。このように、液晶装置1の駆動回路20と制御部60との間にFPC30が配設されることで、制御部60からの電源や信号は、FPC30を介して液晶装置1の駆動IC20に供給される。尚、FPC30の配線に関しての詳細は後述する。

[第1の実施形態の液晶装置のFPCの説明]

次に、FPC30の配線の一例について図3に基づいて説明する。FPC30は、4通りの電極パターンが形成された4種類のFPCによって成り、図3(a)〜図3(d)は、その4種類のFPC30a〜30dを示している。

図3(a)において、FPC30aの駆動IC20側の電極31a〜31gは、図示するように、それぞれ駆動IC20の電源と信号線に接続され、電極31bは電源VDD、電極31cは切替信号LT0、電極31dは電源VSS、電極31eは切替信号LT1、電極31fは電源VDD、電極31gはシリアル信号SIに接続される。尚、電極31aは、ダミー電極である。

また、制御部60側の電極32a〜32eは、それぞれ制御部60の電源と信号線に接続され、電極32aは電源VDD、電極32cは電源VSS、電極32eはシリアル信号SIに接続される。尚、電極32bと32dはダミー電極である。

このような電極の配置がなされているので、駆動IC20側の電極31bと制御部60側の電極32aは、電源VDDとして電極パターンPT1によって電気的に接続される。また同様に、電極31dと電極32cは、電源VSSとして電極パターンPT2によって電気的に接続される。また同様に、電極31gと電極32eは、シリアル信号SIとして電極パターンPT3によって電気的に接続される。そして、これらの電極パターンPT1、PT2、PT3は、4種類のFPC30a〜30dにおいてすべて共通である。

また、図3(a)で示すように、FPC30aの電極31c(切替信号LT0)は、電源VDDである電極パターンPT1に接続される。これにより、切替信号LT0は電源VDDが供給されてその信号レベルは論理“1”となる。また、電極31e(切替信号LT1)は、電源VDDである電極31fと電極パターンPT4によって接続される。これにより、切替信号LT1は電源VDDが供給されてその信号レベルは論理“1”となる。この結果、図3(a)で示すFPC30aの切替信号LT0とLT1の論理は、切替信号LT0を下位ビット、LT1を上位ビットとする2進数の切替信号LTとして表現するならば、切替信号LT=“11”となる。

また、図3(b)で示すように、FPC30bの電極31c(切替信号LT0)は、電

源VSSである電極パターンPT2に接続される。これにより、切替信号LT0は電源VSSが供給されてその信号レベルは論理“0”となる。また、電極31e(切替信号LT1)は、電源VDDである電極31fと電極パターンPT4によって接続される。これにより、切替信号LT1は電源VDDが供給されてその信号レベルは論理“1”となる。この結果、図3(b)で示すFPC30bの切替信号LT0とLT1の論理は、切替信号LT0を下位ビット、LT1を上位ビットとする2進数の切替信号LTとして表現するならば、切替信号LT=“10”となる。

また、図3(c)で示すように、FPC30cの電極31c(切替信号LT0)は、電源VDDである電極パターンPT1に接続される。これにより、切替信号LT0は電源VDDが供給されてその信号レベルは論理“1”となる。また、電極31e(切替信号LT1)は、電源VSSである電極パターンPT2に接続される。これにより、切替信号LT1は電源VSSが供給されてその信号レベルは論理“0”となる。この結果、図3(c)で示すFPC30cの切替信号LT0とLT1の論理は、切替信号LT0を下位ビット、LT1を上位ビットとする2進数の切替信号LTとして表現するならば、切替信号LT=“01”となる。

また、図3(d)で示すように、FPC30dの電極31c(切替信号LT0)は、電源VSSである電極パターンPT2に接続される。これにより、切替信号LT0は電源VSSが供給されてその信号レベルは論理“0”となる。また、電極31e(切替信号LT1)は、電源VSSである電極パターンPT2に接続される。これにより、切替信号LT1は電源VSSが供給されてその信号レベルは論理“0”となる。この結果、図3(d)で示すFPC30dの切替信号LT0とLT1の論理は、切替信号LT0を下位ビット、LT1を上位ビットとする2進数の切替信号LTとして表現するならば、切替信号LT=“00”となる。

このように、切替信号LT0とLT1の電極パターンが異なる4種類のFPC30a〜30dを製造し用意することによって、このFPC30a〜30dのいずれかを選択して液晶パネル10に固着することで、駆動IC20に入力する切替信号LT0、LT1の論理を任意に決定することが出来る。

また、FPC30a〜30dの電極パターンの配置は、図示するように切替信号LT0、LT1と電源VDD、電源VSSは隣り合って隣接して形成されている。これにより、切替信号LT0、LT1を電源VDD又はVSSに接続する電極パターンが最短になると共に、FPCは片面電極パターンで製造でき、FPCの製造が簡単でコストも安いという利点がある。尚、FPCの電極数や信号線の種類、及び形状等は、一例であるので限定されるものではない。

[第1の実施形態の液晶装置の動作の説明]

次に、本発明の液晶装置の動作を図1と図4に基づいて説明する。図1において、液晶パネル10に所定の情報を表示する場合、制御部60のマイコン61は、表示情報をシリアルデータに変換してシリアル信号SIとして出力する。液晶装置1の駆動IC20は、FPC30を介して表示情報であるシリアル信号SIを入力すると、内蔵の出力回路24に表示情報が伝達され、この表示情報に応じて液晶パネル10の画素をON、又はOFFするためのセグメント駆動電圧VSEGとコモン駆動電圧VCOMを出力する。尚、セグメント駆動電圧VSEGとコモン駆動電圧VCOMの波形は、電源回路23からの電源±VS、±VD、±VHを合成して生成するが、駆動電圧の波形の詳細は後述する。

また、制御部60のマイコン61は、温度センサー63から信号を入力し、周囲の温度情報としてシリアルデータに変換してシリアル信号SIとして出力する。すなわち、シリ

アル信号SIは、液晶パネル10に表示する表示情報と共に、周囲の温度情報も駆動IC20に伝達する。詳しくは、シリアル信号SIは、シリアルデータであり、先頭からのビット列が表示制御や温度情報を表すコマンドビットで構成され、その後のビット列が表示情報のデータビットで構成される。

駆動IC20は、FPC30を介して温度情報であるシリアル信号SIを入力すると、シリアル信号SIは複数のLUT21a〜21dに伝達され、各LUT21a〜21dから、入力された温度情報に対応したパルス幅信号P1a〜P1dが出力する。

ここで、LUT21a〜21dの出力である温度変化に対するパルス幅信号P1a〜P1dの変移の一例を図4に基づいて説明する。図4において、X軸はパルス幅信号P1a〜P1dを表すパルス幅であり、単位はμSである。また、Y軸はシリアル信号SIによって入力される周囲の温度情報である。

ここで、パルス幅信号P1a〜P1dは、温度が低くなるに従ってパルス幅が長くなるが、これは、液晶パネル10の閾値が温度低下によって上昇するので、その閾値の変化を補正するためである。すなわち前述したように、メモリ性液晶は、駆動電圧のパルス幅値とパルス高値との積の値が閾値を越えたときに一方の安定状態から他方の安定状態へ転移するので、閾値の上昇を補正するには駆動電圧のパルス幅を閾値の上昇に応じて長く設定すれば良い。

また、第1のLUT21aの出力のパルス幅信号P1aは、図示するようにパルス幅が最も長い信号である。このパルス幅によって液晶パネル10が駆動されると、パルス幅値とパルス高値との積の値は最も大きくなるので、LUT21aは液晶パネル10の固有の特性である閾値が最も高くばらついた場合に選択される。また、第4のLUT21dの出力のパルス幅信号P1dは、図示するようにパルス幅が最も短い信号である。このパルス幅によって液晶パネル10が駆動されると、パルス幅値とパルス高値との積の値は最も小さくなるので、LUT21dは液晶パネル10の固有の特性である閾値が最も低くばらついた場合に選択される。

同様に、パルス幅信号P1bを出力する第2のLUT21bは、液晶パネル10の閾値がやや高くばらついた場合に選択され、パルス幅信号P1cを出力する第3のLUT21cは、液晶パネル10の閾値がやや低くばらついた場合に選択される。このように、液晶パネル10の閾値のばらつきに応じて、LUTを切り替えて駆動電圧のパルス幅を選択することで、閾値のばらつきを吸収して、動作不良となる液晶パネル10を削減し、歩留まりを向上させることが出来る。

次に図1のセレクト回路22は、LUT21a〜21dからのパルス幅信号P1a〜P1dを入力して、切替信号LT0とLT1の論理に応じてLUT21a〜21dのいずれか一つのLUTのみを選択し、選択パルス幅信号P2を出力する。ここで、切替信号LT0を下位ビット、LT1を上位ビットとする2進数の切替信号LTとして表現するならば、例えば、切替信号LT=“11”のとき、セレクト回路22はLUT21aから出力されるパルス幅信号P1aを選択し、選択パルス幅信号P2として出力する。

また、切替信号LT=“10”のとき、セレクト回路22はLUT21bから出力されるパルス幅信号P1bを選択し、選択パルス幅信号P2として出力する。また、切替信号LT=“01”のとき、セレクト回路22はLUT21cから出力されるパルス幅信号P1cを選択し、選択パルス幅信号P2として出力する。また、切替信号LT=“00”のとき、セレクト回路22はLUT21dから出力されるパルス幅信号P1dを選択し、選択パルス幅信号P2として出力する。すなわち、切替信号LT0とLT1によって複数の

LUT21a〜21dの中から一つのLUTが選択されて動作し、他のLUTは無効となって動作しない。

ここで、切替信号LT0とLT1の論理は前述したように、図3で示したFPC30の電極パターンの配線によって決定されるので、予め液晶パネル10の閾値を測定し、液晶パネル10の固有の特性である閾値に応じてFPC30a〜30dを選択して接続するならば、駆動IC20は液晶パネル10の閾値に応じたLUTを選択し、閾値に適した選択パルス幅信号P2を出力することが出来る。

次に出力回路24は、選択パルス幅信号P2を入力して駆動電圧のパルス幅を決定し、シリアル信号SIからの表示情報に基づいて電源±VS、±VD、±VHを順次切り替えて、液晶パネル10にセグメント駆動電圧VSEGとコモン駆動電圧VCOMを出力する。

[第1の実施形態の液晶装置の駆動波形の説明]

次に、液晶パネル10を駆動するセグメント駆動電圧VSEGとコモン駆動電圧VCOMの駆動波形を図5〜図7に基づいて説明する。図5は、液晶パネル10の閾値に合わせて第1のLUT21aが選択された場合において、液晶パネル10の固有の画素に印加される所定温度での駆動波形を示している。そして、図5(a)は、画素を白表示とする駆動波形であり、図5(b)は、画素を黒表示とする駆動波形である。尚、この駆動波形はセグメント駆動電圧VSEGとコモン駆動電圧VCOMの合成駆動波形として示している。

図5(a)と図5(b)において、駆動波形は表示データを書き込む期間の前に、液晶パネル10を一方の安定状態にリセットするためのリセット期間Rsを備えている。このリセット期間Rsは、+VSと−VSの双極性パルスを印加する。尚、+VSと−VSは図15で示した閾値(すなわちV2とV4)より充分に高い電圧が選択される。このリセット期間Rsの駆動電圧がリセットパルスと定義される。このリセットパルスの印加によって、液晶パネル10は図15で示した第1の安定状態(黒表示)にリセットされるが、リセットパルスを反転させることによって第2の安定状態(白表示)にリセットすることも出来る。

次にリセット期間Rsが終了すると、駆動波形は各画素に表示データを書き込むセレクト期間Sctに移行する。セレクト期間Sctは、選択した画素に表示データを書き込む選択期間Seと、他の画素に表示データを書き込む非選択期間NSeを備えている。

ここで、図5(a)に示す白表示の場合には、表示状態をリセット期間Rsによる黒表示から白表示に切り替えるので、液晶パネル10の閾値以上の電圧である±VSの双極性パルスが印加される。また、図5(b)に示す黒表示の場合には、リセット期間Rsによる黒表示から切り替える必要がないので、閾値以下の電圧である±VDの双極性パルスが印加される。また、選択期間Seに続いて、閾値以下の電圧である±VHの双極性パルスが印加される非選択期間NSeが走査の終了まで継続される。尚、すべての期間で双極性パルスを印加する理由は、液晶を交流化駆動するためである。

また、図5(a)の選択期間Seの±VSのパルス幅T1は、変換テーブルである第1のLUT21aが選択されたことによるパルス幅信号P1aに基づいたパルス幅である。例えば、周囲温度が20℃のときは、図4に示すように、そのパルス幅は他のLUTの中で最も長くT1=約1750μSである。尚、パルス幅T1は、リセット期間Rsや非選択期間NSeにおいても同じパルス幅が印加される。

このように、第1のLUT21aが選択されることで、駆動波形は最も長いパルス幅T1となる。これにより、黒表示を白表示に切り替える選択期間Seの駆動電圧は、パルス幅値とパルス高値との積の値が最も大きくなり、液晶パネル10の閾値が製造上のばらつきで最も高い値にシフトしても、その閾値に合った駆動波形を印加することが出来る。尚、駆動波形のそれぞれの電圧値は、一例として、VSが約4.8V、VDが約3.6V、VHが約1.2Vである。

次に図6は、液晶パネル10の閾値に合わせて第2のLUT21bが選択された場合において、液晶パネル10の固有の画素に印加される所定温度での駆動波形を示している。そして、図6(a)は画素を白表示とする駆動波形であり、図6(b)は画素を黒表示とする駆動波形である。尚、この駆動波形は図5と同様に合成駆動波形である。

ここで、図6(a)と図6(b)は図5(a)と図5(b)と同様に、リセット期間Rs、選択期間Se、非選択期間NSeを有しており、その駆動波形の基本は同じである。そして唯一異なる点は、そのパルス幅であり、選択期間Seの±VSのパルス幅T2は、第2のLUT21bが選択されたことによるパルス幅信号P1bに基づいたパルス幅である。例えば、周囲温度が20℃のときは、図4に示すように、そのパルス幅はT1より短くてT2=約1600μSである。尚、パルス幅T2は、リセット期間Rsや非選択期間NSeにおいても同じパルス幅が印加される。

このように、第2のLUT21bが選択されることで、黒表示を白表示に切り替える選択期間Seの駆動電圧であるパルス幅値とパルス高値との積の値は、LUT21aの選択時より小さくなる。これにより、液晶パネル10の閾値が製造上のばらつきで、やや高い値にシフトした場合に、その閾値に適した駆動電圧を印加することが出来る。

次に図7は、液晶パネル10の閾値に合わせて第4のLUT21dが選択された場合において、液晶パネル10の固有の画素に印加される所定温度での駆動波形を示している。そして、図7(a)は画素を白表示とする駆動波形であり、図7(b)は画素を黒表示とする駆動波形である。尚、この駆動波形は図5と同様に合成駆動波形である。

ここで、図7(a)と図7(b)は図5(a)と図5(b)と同様に、リセット期間Rs、選択期間Se、非選択期間NSeを有しており、その駆動波形の基本は同じである。そして唯一異なる点は、そのパルス幅であり、選択期間Seの±VSのパルス幅T4は、LUT21dが選択されたことによるパルス幅信号P1dに基づいたパルス幅である。例えば、周囲温度が20℃のときは、図4に示すように、そのパルス幅は最も短くてT4=約1300μSである。尚、パルス幅T4は、リセット期間Rsや非選択期間NSeにおいても同じパルス幅が印加される。なお、図5、図6、図7において、パルス幅が短くなるにしたがって、パルス間の0Vとなる期間を長くし、リセット期間Rs、選択期間Se、非選択期間NSeのそれぞれの期間を同じ長さとしているが、0Vとなる期間は一定として、パルス幅が短くなるにしたがって、それぞれの期間の長さを短くしても構わない。

このように、第4のLUT21dが選択されることで、黒表示を白表示に切り替える選択期間Seの駆動電圧であるパルス幅値とパルス高値との積の値は、他のLUT21a〜LUT21cの選択時より最も小さくなる。これにより、液晶パネル10の閾値が製造上のばらつきで、最も低い値にシフトした場合に、その閾値に適した駆動電圧を印加することが出来る。

尚、第3のLUT21cが選択された場合の駆動波形は省略するが、LUT21cが選択された場合のパルス幅をパルス幅T3とするならば、そのパルス幅T3はパルス幅信号P1cに基づいたパルス幅であり、周囲温度が20℃のとき図4に示すように、T3=約

1450μSである。また、パルス幅信号P1a〜P1dの値は一例であり、組み込まれる液晶パネルの特性に応じて最適なパルス幅が設定される。

[第1の実施形態の液晶装置の製造方法の工程順の説明]

次に第1の実施形態の液晶装置の製造工程は、まず、液晶パネル10に複数のLUTと外部端子を備えた駆動IC20を実装する。次に液晶パネル10を駆動し、所定温度での液晶パネル10の閾値を測定する。次に測定した閾値に基づいてLUTを選択する切替信号LT0、LT1の論理を決定する。次に切替信号LT0、LT1の論理に基づいて、予め用意したFPC30a〜FPC30dの中から一つのFPCを選択する。次に選択したFPCを液晶パネル10に固着して駆動IC20の外部端子と接続し、一つのLUTを選択する。次に表示テストを行い液晶装置が完成する。

ここで、FPCの選択と液晶パネルへの固着工程を図8によって説明する。図8において、FPCは前述したように、切替信号LT0とLT1が電源VDD又は電源VSSと接続するか否かで、4通りの論理を有する4種類のFPC30a〜30dを製造し、予め用意する。そして、液晶パネル10の閾値のばらつきに応じて、最も適応するFPCを用意したFPC30a〜30bの中から選択し、液晶パネル10のガラス基板11bに導電性接着剤等(図示せず)によって固着する。これにより、特別な切り替え手段等を用意しなくても、閾値のばらつきを吸収出来るので、特性が揃った液晶装置を量産することが出来る。

以上のように本発明によれば、液晶装置に低消費電力が特徴のメモリ性液晶パネルを用いる場合、製造上のばらつきで液晶パネルの閾値がばらついて表示動作が不安定になり、歩留まりが低下するという問題があるが、その特性ばらつきに応じて駆動ICに内蔵する複数の変換テーブルの中から一つの変換テーブルを選択することで、特性ばらつきを吸収する液晶装置を提供することが出来る。

また、その変換テーブルの選択は、液晶装置とシステム側である制御部とを電気的に接続するFPCを選択することで実現できるので、液晶装置の組み立て工程が簡素化されると共に、変換テーブルを切り替えるための余分な部品等を設ける必要が無く、部品点数が少なく小型で取り扱いが容易な液晶装置を提供することが出来る。

また、液晶パネルの特性ばらつきの吸収を液晶装置側単独で実現できるので、液晶装置を搭載するシステム側では、液晶装置のばらつきを考慮する必要が無い。これにより、シンプルな制御で液晶装置を制御し駆動できるので、システム側の構成や制御プログラムが容易になり、液晶装置を搭載するシステム側においても大きな効果を得ることが出来る。

[第2の実施形態の液晶装置の回路構成の説明]

次に、本発明の液晶装置に係わる第2の実施形態の回路構成の概略を説明する。図9は本発明の第2の実施形態の液晶装置の概略を示す回路ブロック図である。尚、第2の実施形態回路ブロック図は第1の実施形態で説明した回路ブロック図(図1)と大部分が共通であるので、同一要素には同一番号を付し重複する説明は省略する。

図9において、本発明の第2の実施形態である液晶装置1は、第1の実施形態と同様に液晶パネル10と駆動回路としての駆動IC20を備えている。また、40は選択手段としてのFPCである。また、60は液晶装置1を外部から制御する制御手段としての制御部である。ここで、FPC40は、液晶装置1の駆動IC20と制御部60の間に配設して、制御部60からの電源や各種の情報を伝達する機能を有している。また、液晶パネル10、外部の制御部60の構成は第1の実施形態と同一であるので説明は省略する。

また、駆動IC20についても基本構成は第1の実施形態と同様であるが、異なる点はプルアップ抵抗R1、R2を内蔵していることである。ここで、プルアップ抵抗R1は、一方の端子を切替信号LT0に接続し、他方の端子を電源VDDに接続して、切替信号LT0がFPC40側でオープンである場合、その電位を電源VDDと同電位にしている。また、プルアップ抵抗R2は、一方の端子を切替信号LT1に接続し、他方の端子を電源VDDに接続して、切替信号LT1がFPC40側でオープンである場合、その電位を電源VDDと同電位にしている。このように、第2の実施形態は、切替信号LT0とLT1をプルアップ抵抗R1、R2によって電源VDDと同電位にしていることが特徴である。

[第2の実施形態の液晶装置のFPCの説明]

次に、FPC40の配線について図10に基づいて説明する。FPC40は、第1の実施形態と同様に4通りの電極パターンが形成された4種類のFPCによって成り、図10(a)〜図10(d)は、その4種類のFPC40a〜40dを示している。

図10(a)において、FPC40aの駆動IC20側の電極41a〜41gは、図示するように、それぞれ駆動IC20の電源と信号線に接続され、電極41bは電源VDD、電極41cは切替信号LT0、電極41dは電源VSS、電極41eは切替信号LT1、電極41gはシリアル信号SIに接続される。尚、電極41aと41fは、ダミー電極である。

また、制御部60側の電極42a〜42eは、それぞれ制御部60の電源と信号線に接続され、電極42aは電源VDD、電極42cは電源VSS、電極42eはシリアル信号SIに接続される。尚、電極42bと42dはダミー電極である。

このような電極の配置がなされているので、駆動IC20側の電極41bと制御部60側の電極42aは、電源VDDとして電極パターンPT5によって電気的に接続される。また同様に、電極41dと電極42cは、電源VSSとして電極パターンPT6によって電気的に接続される。また同様に、電極41gと電極42eは、シリアル信号SIとして電極パターンPT7によって電気的に接続される。そして、これらの電極パターンPT5、PT6、PT7は、4種類のFPC40a〜40dにおいてすべて共通である。

また、図10(a)で示すように、FPC40aの電極41c(切替信号LT0)は、どのパターンにも接続されずオープンである。これにより、切替信号LT0は電源VDDにプルアップされているのでその信号レベルは論理“1”となる。また同様に、電極41e(切替信号LT1)も、どのパターンにも接続されずオープンである。これにより、切替信号LT1は電源VDDにプルアップされているのでその信号レベルは論理“1”となる。この結果、図10(a)で示すFPC40aの切替信号LT0とLT1の論理は、切替信号LT0を下位ビット、LT1を上位ビットとする2進数の切替信号LTとして表現するならば、切替信号LT=“11”となる。

また、図10(b)で示すように、FPC40bの電極41c(切替信号LT0)は、電源VSSである電極パターンPT6に接続される。これにより、切替信号LT0は電源VSSが供給されてその信号レベルは論理“0”となる。また、電極41e(切替信号LT1)は、どのパターンにも接続されずオープンである。これにより、切替信号LT1は電源VDDにプルアップされているのでその信号レベルは論理“1”となる。この結果、図10(b)で示すFPC40bの切替信号LT0とLT1の論理は、切替信号LT0を下位ビット、LT1を上位ビットとする2進数の切替信号LTとして表現するならば、切替信号LT=“10”となる。

また、図10(c)で示すように、FPC40cの電極41c(切替信号LT0)は、どのパターンにも接続されずオープンである。これにより、切替信号LT0は電源VDDにプルアップされているのでその信号レベルは論理“1”となる。また、電極41e(切替信号LT1)は、電源VSSである電極パターンPT6に接続される。これにより、切替信号LT1は電源VSSが供給されてその信号レベルは論理“0”となる。この結果、図10(c)で示すFPC40cの切替信号LT0とLT1の論理は、切替信号LT0を下位ビット、LT1を上位ビットとする2進数の切替信号LTとして表現するならば、切替信号LT=“01”となる。

また、図10(d)で示すように、FPC40dの電極41c(切替信号LT0)は、電源VSSである電極パターンPT6に接続される。これにより、切替信号LT0の信号レベルは論理“0”となる。また、電極41e(切替信号LT1)は、電源VSSである電極パターンPT6に接続される。これにより、切替信号LT1の信号レベルは論理“0”となる。この結果、図10(d)で示すFPC40dの切替信号LT0とLT1の論理は、切替信号LT0を下位ビット、LT1を上位ビットとする2進数の切替信号LTとして表現するならば、切替信号LT=“00”となる。

このように、切替信号LT0とLT1の電極パターンが異なる4種類のFPC40a〜40dを製造し用意することによって、このFPC40a〜40dのいずれかを選択して液晶パネル10に固着することで、駆動IC20に入力する切替信号LT0、LT1の論理を任意に選ぶことが出来る。

これにより、第2の実施形態の液晶装置は、第1の実施形態と同様に、製造上のばらつきで液晶パネルの閾値がばらつくことに対応して、FPC40a〜40dのいずれかを選択して液晶装置に固着し完成させることで、その閾値の特性ばらつきに応じて内蔵する複数の変換テーブルの中から一つの変換テーブルを選択することが出来るので、液晶パネルの特性ばらつきの影響が抑制されて不良品の発生を大きく減少させることが出来る。

また、第2の実施形態においては、切替信号LT0、LT1が電源VSSに接続された場合、プルアップ抵抗R1、R2を通って僅かに電流が流れるが、プルアップ抵抗R1、R2の抵抗値を高く設定すれば、その電流はほぼ無視することが出来る。また、プルアップ抵抗R1、R2は、駆動IC20に内蔵されるので、部品点数を増やさずに第2の実施形態を実現できる。また、第2の実施形態のFPC40a〜40cの電極パターンは、第1の実施形態のFPC30a〜30cの電極パターンと比較してシンプルであるので、FPCの製造が容易となる。

また、FPC40a〜40dの電極パターンの配置は、切替信号LT0、LT1と電源VSSは隣り合って隣接して形成されている。これにより、切替信号LT0、LT1を電源VSSに接続する電極パターンが最短になると共に、FPCは片面電極パターンで製造でき、FPCの製造が簡単でコストも安いという利点がある。尚、第2の実施形態の液晶装置の製造方法の工程順は、第1の実施形態と同様であるので説明は省略する。

[第3の実施形態の液晶装置のFPCの説明]

次に、本発明の液晶装置に係わる第3の実施形態の概略を説明する。第3の実施形態は、プルアップ抵抗R1、R2を有する第2の実施形態に対してFPCのみが異なるだけであるので、FPCについてのみ図11に基づいて説明する。図11において、50は第3の実施形態の液晶装置に用いられるFPCである。FPC50の駆動IC20側の電極51a〜51gは、図示するように、それぞれ駆動IC20側の電源と信号線に接続され、電極51bは電源VDD、電極51cは切替信号LT0、電極51dは電源VSS、電極

51eは切替信号LT1、電極51gはシリアル信号SIに接続される。尚、電極51aと51fは、ダミー電極である。

また、制御部60側の電極52a〜52eは、それぞれ制御部60の電源と信号線に接続され、電極52aは電源VDD、電極52cは電源VSS、電極52eはシリアル信号SIに接続される。尚、電極52bと52dはダミー電極である。

このような電極の配置がなされているので、駆動IC20側の電極51bと制御部60側の電極52aは、電源VDDとして電極パターンPT8によって電気的に接続される。また同様に、電極51dと電極52cは、電源VSSとして電極パターンPT9によって電気的に接続される。また同様に、電極51gと電極52eは、シリアル信号SIとして電極パターンPT10によって電気的に接続される。

また、電極51c(切替信号LT0)は、電源VSSである電極パターンPT9に接続されて、切替信号LT0の信号レベルは論理“0”となる。また同様に、電極51e(切替信号LT1)も、電源VSSである電極パターンPT9に接続されて、切替信号LT1の信号レベルは論理“0”となる。この結果、図11で示すFPC50の切替信号LT0とLT1の論理は、切替信号LT0を下位ビット、LT1を上位ビットとする2進数の切替信号LTとして表現するならば、切替信号LT=“00”となる。

また、電極51c(切替信号LT0)からの電極パターンは、電源VSSである電極パターンPT9との接続点付近(破線の円形で示す)に切断ポイントH0を有している。また同様に、電極51e(切替信号LT1)からの電極パターンは、電源VSSである電極パターンPT9との接続点付近(破線の円形で示す)に切断ポイントH1を有している。この切断ポイントH0、H1での電極パターンは、その部分が図示するように僅かに細くなると良い。これは、この切断ポイントH0、H1は、穴開け機等によって略円形の穴が開けられて、その部分の電極パターンが切断されるからである。

すなわち、FPC50の切断ポイントH0、H1の位置に穴が開けられることによって、電極51cと51eの電極パターンは、電源VSSと電気的に分離されることになる。例えば、切断ポイントH0に穴が開けられると、電極51c(切替信号LT0)の電極パターンは、電源VSSの電極パターンPT9と電気的に切断されるので、オープン状態となる。これにより、切替信号LT0は電源VDDにプルアップされているのでその信号レベルは論理“1”となる。この結果、切替信号LT0とLT1の論理は、切替信号LT0を下位ビット、LT1を上位ビットとする2進数の切替信号LTとして表現するならば、切替信号LT=“01”となる。

また、切断ポイントH1に穴が開けられると、電極51e(切替信号LT1)の電極パターンは、電源VSSの電極パターンPT9と電気的に切断されるので、オープン状態となる。これにより、切替信号LT1は電源VDDにプルアップされているのでその信号レベルは論理“1”となる。この結果、切替信号LT0とLT1の論理は、切替信号LT0を下位ビット、LT1を上位ビットとする2進数の切替信号LTとして表現するならば、切替信号LT=“10”となる。

また、切断ポイントH0、H1の両方に穴が開けられるならば、電極51cと電極51eの両方はオープン状態となるので、切替信号LT0、LT1は共に論理“1”となる。この結果、切替信号LT0とLT1の論理は、切替信号LT0を下位ビット、LT1を上位ビットとする2進数の切替信号LTとして表現するならば、切替信号LT=“11”となる。

このように、切替信号LT0、LT1をどのような論理に設定するかに応じて、切断ポイントH0とH1に穴を開けるか否かを決定し実施するならば、1種類のFPC50によって切替信号LT0、LT1の論理が異なるFPCを製造し用意することが出来る。

[第3の実施形態の液晶装置の製造方法の工程順の説明]

次に第3の実施形態の液晶装置の製造工程は、まず、液晶パネル10に駆動IC20を実装して液晶パネル10を駆動し、所定温度での液晶パネル10の閾値を測定する。次に測定した閾値に基づいてLUTを選択する切替信号LT0、LT1の論理を決定する。次に切替信号LT0、LT1の論理に基づいて、FPC50の切断ポイントH0とH1の穴開けを実施する。次に穴開けが実施されたFPC50を導電性接着剤等によって液晶パネル10のガラス基板11b(図2参照)に固着して駆動IC20の外部端子に接続し、一つのLUTを選択する。次に表示テストを行い液晶装置が完成する。

以上のように、本発明の第3の実施形態によれば、液晶パネルの特性ばらつきに応じて1種類のFPCに僅かな加工を実施するだけで、液晶パネルの特性ばらつきを吸収出来るので、第1及び第2の実施形態の液晶装置と同様な効果を得ることが出来る。また、LUTを切り替えるためのFPCは、1種類だけ用意すれば良いので、FPCの製造や管理が簡単であり、簡素化された製造工程で液晶装置を製造することが出来る。

尚、本発明の実施形態において、液晶パネル10の特性のばらつきに応じて選択するLUTは4個としているが、この数に限定されず、液晶パネル10の特性のばらつきに応じて選択できるLUTは、例えば、2個であっても6個であっても、その数は任意で良い。また、そのLUTの数に応じて、切替信号の本数も増減することはもちろんであり、例えば、LUTが2個であるならば、切替信号は1本で良い。

また、本発明の実施形態において、LUTは温度変化に応じて駆動波形のパルス幅を変化させているが、これに限定されず、温度変化に応じて駆動波形のパルス高値を変化させても、同様な特性を得ることが出来る。この場合、複数のLUTは駆動波形のパルス幅を異ならせるのではなく、駆動波形のパルス高値を異ならせて切り替える方法でも良い。

また、本発明の実施形態において、液晶パネル10の閾値のばらつきに応じて複数のLUTの中から一つのLUTを選択しているが、LUTの選択は閾値のばらつきに限定されるものではなく、液晶の応答特性のばらつき、温度特性のばらつき等、他の特性のばらつきに応じた切り替えでも、本発明は適応される。

また、本発明の実施形態において、液晶装置に搭載する液晶パネルは、強誘電性液晶素子を代表とするメモリ性液晶パネルを前提としたが、これに限定されず、通常のネマティック液晶などによる液晶パネルを用いた液晶装置にも適応される。また、本発明の実施形態で示したブロック図や外形図等は、これに限定されるものではなく、本発明の要旨を満たすものであれば、任意に変更してよい。

本発明の第1の実施形態の液晶装置の回路的な概略構成を示す回路ブロック図である。

本発明の第1の実施形態の液晶装置の機械的な概略構成を示す外形図である。

本発明の第1の実施形態の液晶装置のFPCの電極パターンの一例を示す説明図である。

本発明の第1の実施形態の液晶装置の変換テーブルのデータの一例を示すグラフである。

本発明の第1の実施形態の液晶装置において第1のLUTが選択された場合の駆動電圧波形である。

本発明の第1の実施形態の液晶装置において第2のLUTが選択された場合の駆動電圧波形である。

本発明の第1の実施形態の液晶装置において第4のLUTが選択された場合の駆動電圧波形である。

本発明の第1の実施形態の液晶装置においてFPCの選択と液晶パネルへの固着工程を説明する説明図である。

本発明の第2の実施形態の液晶装置の電気的な概略構成を示す回路ブロック図である。

本発明の第2の実施形態の液晶装置のFPCの電極パターンの一例を示す説明図である。

本発明の第3の実施形態の液晶装置のFPCの電極パターンの一例を示す説明図である。

従来の液晶装置の概略を示す回路ブロック図である。

従来の液晶装置の動作を説明する変換テーブルのグラフである。

従来のメモリ性液晶パネルの構造を示す説明図である。

従来のメモリ性液晶パネルの光透過率特性を示す説明図である。

符号の説明

1 液晶装置

10 液晶パネル

11a、11b ガラス基板

12 表示エリア

13 画素

20 駆動IC

21a〜21d 変換テーブル(LUT)

22 セレクト回路

23、62 電源回路

24 出力回路

25a〜25f 外部端子

30、30a〜30d、40、40a〜40d、50 フレキシブルプリント基板(FPC)

31a〜31g、32a〜32e、41a〜41g、42a〜42e、51a〜51g、52a〜52e 電極

60 制御部

61 マイコン

63 温度センサー

P1a〜P1d パルス幅信号

P2 選択パルス幅信号

SI シリアル信号

LT0、LT1 切替信号

VSEG セグメント駆動電圧

VCOM コモン駆動電圧

PT1〜PT10 電極パターン

H0、H1 切断ポイント

±VS、±VD、±VH、VDD、VSS 電源