JP5138611B2 - 接合用の隣接収納部を有する半導体相互接続、及び形成方法 - Google Patents

接合用の隣接収納部を有する半導体相互接続、及び形成方法 Download PDFInfo

- Publication number

- JP5138611B2 JP5138611B2 JP2008552305A JP2008552305A JP5138611B2 JP 5138611 B2 JP5138611 B2 JP 5138611B2 JP 2008552305 A JP2008552305 A JP 2008552305A JP 2008552305 A JP2008552305 A JP 2008552305A JP 5138611 B2 JP5138611 B2 JP 5138611B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- dielectric layer

- opening

- dielectric

- forming

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 66

- 238000000034 method Methods 0.000 title claims description 25

- 229910052751 metal Inorganic materials 0.000 claims description 64

- 239000002184 metal Substances 0.000 claims description 64

- 239000000758 substrate Substances 0.000 claims description 23

- 238000005530 etching Methods 0.000 claims description 17

- 230000004888 barrier function Effects 0.000 claims description 14

- 239000000463 material Substances 0.000 claims description 13

- 230000001590 oxidative effect Effects 0.000 claims description 7

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 claims description 2

- 229910052715 tantalum Inorganic materials 0.000 claims description 2

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 claims description 2

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 claims description 2

- 239000004020 conductor Substances 0.000 claims 2

- 239000010410 layer Substances 0.000 description 142

- 235000012431 wafers Nutrition 0.000 description 21

- 230000008569 process Effects 0.000 description 13

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 9

- 229910052799 carbon Inorganic materials 0.000 description 9

- 230000015572 biosynthetic process Effects 0.000 description 7

- 239000013626 chemical specie Substances 0.000 description 7

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 5

- 239000003989 dielectric material Substances 0.000 description 5

- 229910052760 oxygen Inorganic materials 0.000 description 5

- 239000001301 oxygen Substances 0.000 description 5

- 230000008901 benefit Effects 0.000 description 4

- 230000004048 modification Effects 0.000 description 4

- 238000012986 modification Methods 0.000 description 4

- 229910052802 copper Inorganic materials 0.000 description 3

- 239000010949 copper Substances 0.000 description 3

- 230000007797 corrosion Effects 0.000 description 3

- 238000005260 corrosion Methods 0.000 description 3

- 238000005516 engineering process Methods 0.000 description 3

- UGFAIRIUMAVXCW-UHFFFAOYSA-N Carbon monoxide Chemical compound [O+]#[C-] UGFAIRIUMAVXCW-UHFFFAOYSA-N 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 2

- 229910002091 carbon monoxide Inorganic materials 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000009713 electroplating Methods 0.000 description 2

- 239000007789 gas Substances 0.000 description 2

- 238000001465 metallisation Methods 0.000 description 2

- 239000003607 modifier Substances 0.000 description 2

- 238000001020 plasma etching Methods 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 125000006850 spacer group Chemical group 0.000 description 2

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- 239000011247 coating layer Substances 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- UBHZUDXTHNMNLD-UHFFFAOYSA-N dimethylsilane Chemical compound C[SiH2]C UBHZUDXTHNMNLD-UHFFFAOYSA-N 0.000 description 1

- NBVXSUQYWXRMNV-UHFFFAOYSA-N fluoromethane Chemical compound FC NBVXSUQYWXRMNV-UHFFFAOYSA-N 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 239000010931 gold Substances 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- UIUXUFNYAYAMOE-UHFFFAOYSA-N methylsilane Chemical compound [SiH3]C UIUXUFNYAYAMOE-UHFFFAOYSA-N 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 238000005240 physical vapour deposition Methods 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- PQDJYEQOELDLCP-UHFFFAOYSA-N trimethylsilane Chemical compound C[SiH](C)C PQDJYEQOELDLCP-UHFFFAOYSA-N 0.000 description 1

- 229940094989 trimethylsilane Drugs 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76885—By forming conductive members before deposition of protective insulating material, e.g. pillars, studs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/11—Manufacturing methods

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L24/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L24/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/50—Multistep manufacturing processes of assemblies consisting of devices, each device being of a type provided for in group H01L27/00 or H01L29/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/11—Manufacturing methods

- H01L2224/114—Manufacturing methods by blanket deposition of the material of the bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/11—Manufacturing methods

- H01L2224/116—Manufacturing methods by patterning a pre-deposited material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/1302—Disposition

- H01L2224/13021—Disposition the bump connector being disposed in a recess of the surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

- H01L2224/812—Applying energy for connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

- H01L2224/818—Bonding techniques

- H01L2224/81801—Soldering or alloying

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06513—Bump or bump-like direct electrical connections between devices, e.g. flip-chip connection, solder bumps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L24/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01013—Aluminum [Al]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01019—Potassium [K]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01022—Titanium [Ti]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01032—Germanium [Ge]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01047—Silver [Ag]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01049—Indium [In]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01051—Antimony [Sb]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01072—Hafnium [Hf]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01073—Tantalum [Ta]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01074—Tungsten [W]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01078—Platinum [Pt]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01082—Lead [Pb]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/013—Alloys

- H01L2924/014—Solder alloys

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/049—Nitrides composed of metals from groups of the periodic table

- H01L2924/0494—4th Group

- H01L2924/04941—TiN

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/102—Material of the semiconductor or solid state bodies

- H01L2924/1025—Semiconducting materials

- H01L2924/1026—Compound semiconductors

- H01L2924/1032—III-V

- H01L2924/10329—Gallium arsenide [GaAs]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/1901—Structure

- H01L2924/1904—Component type

- H01L2924/19043—Component type being a resistor

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Wire Bonding (AREA)

Description

Claims (3)

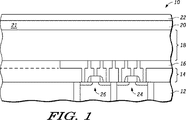

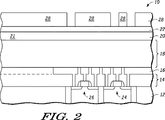

- 被覆素子層を有した基板を設ける工程と、

複数の素子を基板の内部かつ前記被覆素子層の内部に形成する工程と、

一つ以上の相互接続層を前記被覆素子層の上に形成する工程と、

誘電体層を、前記一つ以上の相互接続層の内の最上部にある相互接続層の上面を取り囲むように形成する工程と、

開口部を前記誘電体層の中に形成する工程であって、前記開口部を誘電体層の中に形成する結果、前記誘電体層には前記開口部が形成されるとともに、開口部の側壁の一部分に沿って前記誘電体層の改質部分が形成される、前記開口部を誘電体層の中に形成する工程と、

前記開口部に導電材料を充填する工程と、

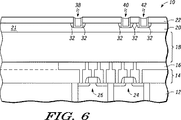

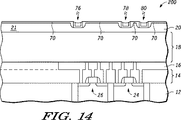

前記誘電体層の露出部分を除去して、誘電体層よりも上に延びる導電材料の突出パッドを形成する工程と、

前記誘電体層の改質部分を除去することによって前記誘電体層に収納開口部を突出パッドに隣接して形成する工程とを備える、半導体デバイスの製造方法。 - 前記開口部を形成する工程では更に、

パターニング済みマスク層を誘電体層上の絶縁キャップ層の上に設ける工程と、

誘電体層及び絶縁キャップ層をエッチングする工程と、

パターニング済みマスク層をプラズマ雰囲気中の酸化性化学種に曝露して除去する工程と、

前記収納開口部のサイズを制御すべく前記誘電体層の改質部分の大きさを決定するために、パターニング済みマスク層の除去を制御する工程とを備える、請求項1記載の方法。 - 基板と、

基板の上の素子層と、

基板及び素子層の内部に形成される複数の素子と、

素子層の上の一つ以上の相互接続層と、

一つ以上の相互接続層の内の最上部にある相互接続層の上面を取り囲む誘電体層と、

前記誘電体層に設けられた開口部と、

前記開口部に設けられるとともに前記誘電体層の上面を越えて上方に延びる突出パッドとを備え、

前記突出パッドは、収納開口部をもって前記誘電体層から分離されているとともに、バリア層であって前記突出パッドの側壁を画定し、かつタンタル、窒化タンタル、窒化チタン、またはこれらの材料の組み合わせからなるバリア層と前記バリア層の内部に設けられた金属層とからなる、半導体デバイス。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/339,132 | 2006-01-25 | ||

| US11/339,132 US7579258B2 (en) | 2006-01-25 | 2006-01-25 | Semiconductor interconnect having adjacent reservoir for bonding and method for formation |

| PCT/US2006/061737 WO2007100404A2 (en) | 2006-01-25 | 2006-12-07 | Semiconductor interconnect having adjacent reservoir for bonding and method for formation |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009524932A JP2009524932A (ja) | 2009-07-02 |

| JP2009524932A5 JP2009524932A5 (ja) | 2010-02-04 |

| JP5138611B2 true JP5138611B2 (ja) | 2013-02-06 |

Family

ID=38284743

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008552305A Active JP5138611B2 (ja) | 2006-01-25 | 2006-12-07 | 接合用の隣接収納部を有する半導体相互接続、及び形成方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US7579258B2 (ja) |

| JP (1) | JP5138611B2 (ja) |

| CN (1) | CN101496166B (ja) |

| TW (1) | TWI415216B (ja) |

| WO (1) | WO2007100404A2 (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8134235B2 (en) | 2007-04-23 | 2012-03-13 | Taiwan Semiconductor Manufacturing Co., Ltd. | Three-dimensional semiconductor device |

| US8053900B2 (en) * | 2008-10-21 | 2011-11-08 | Taiwan Semiconductor Manufacturing Company, Ltd. | Through-substrate vias (TSVs) electrically connected to a bond pad design with reduced dishing effect |

| US8796822B2 (en) * | 2011-10-07 | 2014-08-05 | Freescale Semiconductor, Inc. | Stacked semiconductor devices |

| JP2016018879A (ja) * | 2014-07-08 | 2016-02-01 | 株式会社東芝 | 半導体装置および半導体装置の製造方法 |

| US10636767B2 (en) * | 2016-02-29 | 2020-04-28 | Invensas Corporation | Correction die for wafer/die stack |

| GB2589329B (en) * | 2019-11-26 | 2022-02-09 | Plessey Semiconductors Ltd | Substrate bonding |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07112041B2 (ja) * | 1986-12-03 | 1995-11-29 | シャープ株式会社 | 半導体装置の製造方法 |

| JPH04258125A (ja) * | 1991-02-13 | 1992-09-14 | Nec Corp | 半導体装置 |

| US5739579A (en) * | 1992-06-29 | 1998-04-14 | Intel Corporation | Method for forming interconnections for semiconductor fabrication and semiconductor device having such interconnections |

| US6097096A (en) * | 1997-07-11 | 2000-08-01 | Advanced Micro Devices | Metal attachment method and structure for attaching substrates at low temperatures |

| US6232219B1 (en) * | 1998-05-20 | 2001-05-15 | Micron Technology, Inc. | Self-limiting method of reducing contamination in a contact opening, method of making contacts and semiconductor devices therewith, and resulting structures |

| JP2002026056A (ja) * | 2000-07-12 | 2002-01-25 | Sony Corp | 半田バンプの形成方法及び半導体装置の製造方法 |

| DE10118422B4 (de) * | 2001-04-12 | 2007-07-12 | Infineon Technologies Ag | Verfahren zur Herstellung einer strukturierten metallhaltigen Schicht auf einem Halbleiterwafer |

| JP3735547B2 (ja) * | 2001-08-29 | 2006-01-18 | 株式会社東芝 | 半導体装置及びその製造方法 |

| US6887769B2 (en) * | 2002-02-06 | 2005-05-03 | Intel Corporation | Dielectric recess for wafer-to-wafer and die-to-die metal bonding and method of fabricating the same |

| US6962835B2 (en) * | 2003-02-07 | 2005-11-08 | Ziptronix, Inc. | Method for room temperature metal direct bonding |

| US7307005B2 (en) * | 2004-06-30 | 2007-12-11 | Intel Corporation | Wafer bonding with highly compliant plate having filler material enclosed hollow core |

| EP1732116B1 (en) * | 2005-06-08 | 2017-02-01 | Imec | Methods for bonding and micro-electronic devices produced according to such methods |

-

2006

- 2006-01-25 US US11/339,132 patent/US7579258B2/en active Active

- 2006-03-06 US US11/368,720 patent/US7514340B2/en active Active

- 2006-12-07 JP JP2008552305A patent/JP5138611B2/ja active Active

- 2006-12-07 CN CN2006800518156A patent/CN101496166B/zh active Active

- 2006-12-07 WO PCT/US2006/061737 patent/WO2007100404A2/en active Application Filing

- 2006-12-20 TW TW095147984A patent/TWI415216B/zh active

Also Published As

| Publication number | Publication date |

|---|---|

| TW200746358A (en) | 2007-12-16 |

| JP2009524932A (ja) | 2009-07-02 |

| CN101496166B (zh) | 2010-11-03 |

| US7514340B2 (en) | 2009-04-07 |

| WO2007100404A2 (en) | 2007-09-07 |

| WO2007100404A3 (en) | 2008-10-09 |

| TWI415216B (zh) | 2013-11-11 |

| CN101496166A (zh) | 2009-07-29 |

| US20070170584A1 (en) | 2007-07-26 |

| US7579258B2 (en) | 2009-08-25 |

| US20070170585A1 (en) | 2007-07-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TWI406381B (zh) | 半導體裝置及其形成方法 | |

| US11011421B2 (en) | Semiconductor device having voids and method of forming same | |

| US8252659B2 (en) | Method for producing interconnect structures for integrated circuits | |

| US9633929B2 (en) | TSV formation | |

| JP5497756B2 (ja) | 半導体素子の製造方法および半導体素子 | |

| US20130105968A1 (en) | TSV Backside Processing Using Copper Damascene Interconnect Technology | |

| US20080026579A1 (en) | Copper damascene process | |

| JP5138611B2 (ja) | 接合用の隣接収納部を有する半導体相互接続、及び形成方法 | |

| CN109686657B (zh) | 晶圆间键合结构的形成方法、晶圆的键合方法 | |

| CN107305840B (zh) | 一种半导体器件及其制造方法和电子装置 | |

| JP3781729B2 (ja) | 半導体装置の製造方法 | |

| US8445376B2 (en) | Post-etching treatment process for copper interconnecting wires | |

| US8563432B2 (en) | Method for forming through silicon via structure | |

| CN112736054B (zh) | 半导体元件及其制备方法 | |

| US11315904B2 (en) | Semiconductor assembly and method of manufacturing the same | |

| JP2004119872A (ja) | 半導体装置の製造方法 | |

| US7528059B2 (en) | Method for reducing polish-induced damage in a contact structure by forming a capping layer | |

| JP2008041804A (ja) | 半導体装置及びその製造方法 | |

| JP2015228473A (ja) | 半導体装置およびその製造方法 | |

| TWI559414B (zh) | 基底穿孔製程 | |

| KR101128725B1 (ko) | 반도체 장치의 제조방법 | |

| KR20120034988A (ko) | 반도체 소자의 콘택 및 그 형성 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091207 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20091207 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20111124 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111129 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120224 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121023 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121114 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 5138611 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151122 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |