JP5111758B2 - 薄膜トランジスタ - Google Patents

薄膜トランジスタ Download PDFInfo

- Publication number

- JP5111758B2 JP5111758B2 JP2005364933A JP2005364933A JP5111758B2 JP 5111758 B2 JP5111758 B2 JP 5111758B2 JP 2005364933 A JP2005364933 A JP 2005364933A JP 2005364933 A JP2005364933 A JP 2005364933A JP 5111758 B2 JP5111758 B2 JP 5111758B2

- Authority

- JP

- Japan

- Prior art keywords

- gate electrode

- electrode

- opening

- thin film

- film transistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6729—Thin-film transistors [TFT] characterised by the electrodes

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/1368—Active matrix addressed cells in which the switching element is a three-electrode device

Landscapes

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Mathematical Physics (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- General Physics & Mathematics (AREA)

- Optics & Photonics (AREA)

- Thin Film Transistor (AREA)

- Electrodes Of Semiconductors (AREA)

Description

上記従来技術では、リーク電流の低減が図られるとはいえ、表示電極電位のレベルシフトの問題についてはなんら提案や改善策が示されていない。したがって、レベルシフトの問題をリーク電流の低減と同時に解決する技術が望まれる。更に、大型液晶TVの本格的市場参入を実現するためにはHDTVに代表される画面の大型化&高精細化が必須であり、これを実現するためにはTFTのオン電流を高めることが不可欠である。すなわちリーク電流の低減&オン電流増大&浮遊容量低減の3つを最適化することが必須になる。

前記ゲート電極上にゲート絶縁膜を介して配置された半導体層と、

前記半導体層上に配置されたソース及びドレイン電極を含み、

前記ソース及びドレイン電極のいずれか一方が中央に配置され、他方がそれを囲むように同心円状に配置され、

前記同心円状に配置されたソース及びドレイン電極間にチャネル領域を有し、

前記ゲート電極開口部の外径は前記ソース又はドレイン電極の外径より小さく、かつ前記ゲート電極開口部の外径が前記ソース又はドレイン電極の外径内に納まるように配置されている

ことを特徴とする薄膜トランジスタである。

チャネル幅W対チャネル長L比(W/L)が、約4.5以上であり、

S'への充電能力指標Fが、約50以下である薄膜トランジスタである。

式1 S'=π×((D+L)/2)×((D+L)/2)−π×(d/2)×(d/2)

式中、DはTFTのソース電極外径、LはTFTのチャネル長、dはゲート電極開口径を意味する。(図4A 参照)

本発明では、D=d+4とした。4の意味は食刻工程の合せ精度、加工精度を勘案した数字であり、同心円の外径差2μmを意味する。

式2 W/L=π×(D/L+1)

式3 F=S'÷(W/L)

含むことを特徴とする表示装置である。

前記ゲート電極に円形状のゲート電極開口部を形成する工程、

前記開口部が形成されたゲート電極上に、ゲート絶縁膜を介して半導体層を形成する工程、

前記半導体層上にフォトレジストを形成する工程、

前記ゲート電極をマスクとして、前記基板底部から背面露光を行い、円形状の遮光膜を有するフォトマスクを介して、前記フォトレジスト上部より正面露光を行うことにより前記フォトレジストを感光させる工程、

前記背面及び正面露光により感光されたフォトレジストを現像除去した後、残存するリング形状のフォトレジストをマスクとして半導体層をエッチングして、リング形状の半導体層形成する工程、

を含むことを特徴とする薄膜トランジスタの製造方法である。

前記ゲート電極に円形状のゲート電極開口部を形成する工程、

前記開口部が形成されたゲート電極上に、ゲート絶縁膜を介して半導体層を形成する工程、

前記半導体層上にフォトレジストを形成する工程、

中央部に円形開口を有する遮光膜が形成されたフォトマスクを介して、前記フォトレジスト上部より正面露光を行い前記フォトレジストを感光させる工程、

前記正面露光により感光されたフォトレジストを現像除去した後、残存するリング形状のフォトレジストをマスクとして半導体層をエッチングして、リング形状の半導体層を形成する工程、

を含むことを特徴とする薄膜トランジスタの製造方法である。

本実施例の薄膜トランジスタは、チャネル長Lが5μm、チャネル幅Wが47μm、W/Lが9.4、及び実効Cgs面積S'が380μm2として作製される。

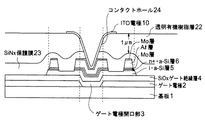

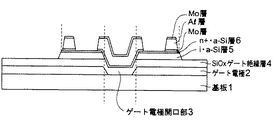

2 ゲート電極・配線

3 ゲート電極開口部

4 ゲート絶縁層

5 i・a-Si:H層

6 n+・a-Si:H層

7 ドレイン電極

8 ソース電極

9 保護膜

10 ITO電極

11 チャネル領域

13,13' フォトレジスト

14,14' フォトマスク

15,15' 遮光膜

16 円形状フォトレジスト

16' リング形状フォトレジスト

17 円形状a-Si島

17' リング形状a-Si島

18 リング形状a-Si島内径開口部

19 コンタクトホール

20 ゲート配線接続端子

21 信号線接続端子

22 透明有機樹脂層

23 SiNx保護膜

24 コンタクトホール

Claims (8)

- 基板上に配置された円形状のゲート電極開口部を有するゲート電極と、

前記ゲート電極上にゲート絶縁膜を介して配置された半導体層と、

前記半導体層上に配置されたソース及びドレイン電極を含み、

前記ソース電極が前記ゲート電極開口部の中央に配置され、前記ドレイン電極が前記ソース電極を囲むように同心円状に配置され、

前記同心円状に配置されたソース及びドレイン電極間にチャネル領域を有し、

前記ゲート電極開口部の外径は前記中央に配置されたソース電極の外径より小さく、かつ前記ゲート電極開口部の外径が前記ソース又はドレイン電極の外径内に納まるように配置されて、

前記半導体層は、前記ゲート電極開口部に対応する半導体層開口部を有することを特徴とする薄膜トランジスタ。 - 前記ゲート電極開口部は前記ソース又はドレイン電極に対して同軸上に配置されることを特徴とする請求項1に記載の薄膜トランジスタ。

- 前記薄膜トランジスタの実効Cgs面積S’が、150πμm2以下であり、

チャネル幅W対チャネル長L比(W/L)が、4.5以上であり、

実効Cgs面積S’への充電能力指標Fが、50以下である

ことを特徴とする請求項1に記載の薄膜トランジスタ。 - 前記実効Cgs面積S’はπ×((ソース電極外径D+L)/2)×((D+L)/2)−π×(ゲート電極開口径d/2)×(d/2)なる式より、前記チャネル幅W対チャネル長L比(W/L)はπ×(D/L+1)なる式より、及び前記実効Cgs面積S’への充電能力指標FはS’÷(W/L)なる式より算出される

ことを特徴とする請求項3に記載の薄膜トランジスタ。 - 表示セルがマトリクス状に配置された表示装置であって、前記表示セルが請求項1に記載の薄膜トランジスタを含む

ことを特徴とする表示装置。 - 基板上にゲート電極を形成する工程、

前記ゲート電極に円形状のゲート電極開口部を形成する工程、

前記開口部が形成されたゲート電極上に、ゲート絶縁膜を介して半導体層を形成する工程、

前記半導体層上にフォトレジストを形成する工程、

前記ゲート電極をマスクとして、前記基板底部から背面露光を行い、円形状の遮光膜を有するフォトマスクを介して、前記フォトレジスト上部より正面露光を行うことにより前記フォトレジストを感光させる工程、

前記背面及び正面露光により感光されたフォトレジストを現像除去した後、残存するリング形状のフォトレジストをマスクとして半導体層をエッチングして、リング形状の半導体層を形成する工程、

前記半導体層上にソース電極がゲート電極開口部の中央に配置され、ドレイン電極がソース電極を囲むように同心円状にソース及びドレイン電極を形成する工程、

を含むことを特徴とする薄膜トランジスタの製造方法。 - 前記フォトマスクの遮光膜は、前記ゲート電極に形成された前記ゲート電極開口部に対して同軸上に配置される

ことを特徴とする請求項6に記載の薄膜トランジスタの製造方法。 - 基板上にゲート電極を形成する工程、

前記ゲート電極に円形状のゲート電極開口部を形成する工程、

前記開口部が形成されたゲート電極上に、ゲート絶縁膜を介して半導体層を形成する工程、

前記半導体層上にフォトレジストを形成する工程、

中央部に円形開口を有する遮光膜が形成されたフォトマスクを介して、前記フォトレジスト上部より正面露光を行い前記フォトレジストを感光させる工程、

前記正面露光により感光されたフォトレジストを現像除去した後、残存するリング形状のフォトレジストをマスクとして半導体層をエッチングして、リング形状の半導体層を形成する工程、

前記半導体層上にソース電極がゲート電極開口部の中央に配置され、ドレイン電極がソース電極を囲むように同心円状にソース及びドレイン電極を形成する工程、

を含むことを特徴とする薄膜トランジスタの製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005364933A JP5111758B2 (ja) | 2005-12-19 | 2005-12-19 | 薄膜トランジスタ |

| KR1020060030539A KR101201330B1 (ko) | 2005-12-19 | 2006-04-04 | 박막트랜지스터 및 그의 제조방법 및 이를 이용한액정표시장치 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005364933A JP5111758B2 (ja) | 2005-12-19 | 2005-12-19 | 薄膜トランジスタ |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007173307A JP2007173307A (ja) | 2007-07-05 |

| JP2007173307A5 JP2007173307A5 (ja) | 2009-02-05 |

| JP5111758B2 true JP5111758B2 (ja) | 2013-01-09 |

Family

ID=38299504

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005364933A Expired - Fee Related JP5111758B2 (ja) | 2005-12-19 | 2005-12-19 | 薄膜トランジスタ |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JP5111758B2 (ja) |

| KR (1) | KR101201330B1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11621280B2 (en) * | 2015-11-05 | 2023-04-04 | Innolux Corporation | Display device |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101865546B1 (ko) * | 2009-10-16 | 2018-06-11 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 액정 표시 장치 및 액정 표시 장치를 포함한 전자 기기 |

| WO2011048923A1 (en) * | 2009-10-21 | 2011-04-28 | Semiconductor Energy Laboratory Co., Ltd. | E-book reader |

| KR102223581B1 (ko) * | 2009-10-21 | 2021-03-04 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 아날로그 회로 및 반도체 장치 |

| KR101773641B1 (ko) | 2010-01-22 | 2017-09-12 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| KR101638200B1 (ko) * | 2010-04-13 | 2016-07-08 | 파나소닉 주식회사 | 유기 반도체 장치 및 유기 반도체 장치의 제조 방법 |

| KR102101167B1 (ko) * | 2012-02-03 | 2020-04-16 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| TWI493724B (zh) | 2012-03-01 | 2015-07-21 | E Ink Holdings Inc | 半導體元件 |

| CN102790056B (zh) * | 2012-08-13 | 2014-12-10 | 京东方科技集团股份有限公司 | 阵列基板及其制作方法、goa单元制作方法及显示装置 |

| CN108447871B (zh) | 2018-03-13 | 2020-12-25 | 深圳市华星光电半导体显示技术有限公司 | 像素单元及其制作方法、显示装置 |

| KR102576214B1 (ko) | 2018-06-28 | 2023-09-07 | 삼성디스플레이 주식회사 | 배선 기판 및 이를 포함하는 표시 장치 |

| US12525591B2 (en) | 2019-12-30 | 2026-01-13 | Lg Display Co., Ltd. | Thin film transistor and display panel using the same |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6482674A (en) * | 1987-09-25 | 1989-03-28 | Casio Computer Co Ltd | Thin film transistor |

| KR100896167B1 (ko) * | 2002-04-24 | 2009-05-11 | 이 잉크 코포레이션 | 전자 표시장치 |

| JP2004087682A (ja) * | 2002-08-26 | 2004-03-18 | Chi Mei Electronics Corp | 薄膜トランジスタ、画像表示素子および画像表示装置 |

| JP4887646B2 (ja) * | 2005-03-31 | 2012-02-29 | 凸版印刷株式会社 | 薄膜トランジスタ装置及びその製造方法並びに薄膜トランジスタアレイ及び薄膜トランジスタディスプレイ |

| JP5116251B2 (ja) * | 2005-05-20 | 2013-01-09 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

-

2005

- 2005-12-19 JP JP2005364933A patent/JP5111758B2/ja not_active Expired - Fee Related

-

2006

- 2006-04-04 KR KR1020060030539A patent/KR101201330B1/ko not_active Expired - Fee Related

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11621280B2 (en) * | 2015-11-05 | 2023-04-04 | Innolux Corporation | Display device |

| US20240395828A1 (en) * | 2015-11-05 | 2024-11-28 | Innolux Corporation | Display device |

Also Published As

| Publication number | Publication date |

|---|---|

| KR101201330B1 (ko) | 2012-11-14 |

| JP2007173307A (ja) | 2007-07-05 |

| KR20070065187A (ko) | 2007-06-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6541294B1 (en) | Semiconductor device and manufacturing method thereof | |

| US8928044B2 (en) | Display device, switching circuit and field effect transistor | |

| US8420413B2 (en) | Method for manufacturing pixel structure | |

| US8362526B2 (en) | Liquid crystal display device and fabricating method thereof | |

| US20100133541A1 (en) | Thin film transistor array substrate, its manufacturing method, and liquid crystal display device | |

| JP5243686B2 (ja) | 薄膜トランジスタ | |

| US6570631B2 (en) | Black matrix in liquid crystal display and method of fabricating the same | |

| JPWO2011027650A1 (ja) | 半導体装置、アクティブマトリクス基板、及び表示装置 | |

| US20080197356A1 (en) | Thin film transistor substrate and method of manufacturing the same | |

| US8289491B2 (en) | Liquid crystal display device with shield lines on data lines and thin film transistor components | |

| JP5111758B2 (ja) | 薄膜トランジスタ | |

| US8698148B2 (en) | Display devices and fabrication methods thereof | |

| US7768012B2 (en) | LCD pixel array structure | |

| JP2003347556A (ja) | 薄膜トランジスタ平面ディスプレイパネル及びその製造方法 | |

| GB2530223A (en) | Method for manufacturing thin film transistor array substrate | |

| EP2261733A1 (en) | Pixel designs of improving the aperture ratio in an LCD | |

| CN100448012C (zh) | 显示装置的薄膜晶体管基板及其制造方法 | |

| US7329901B2 (en) | Thin-film semiconductor device, electro-optical device, and electronic apparatus | |

| CN111357107A (zh) | Tft基板、esd保护电路及tft基板的制作方法 | |

| US20130106679A1 (en) | Lcd panel and method of manufacturing the same | |

| CN100464240C (zh) | 液晶显示器用阵列基板及其制造方法 | |

| US8664703B2 (en) | Display device having a shield | |

| US20080308808A1 (en) | Thin film transistor array substrate and method for fabricating same | |

| KR20030058614A (ko) | 액정표시장치의 제조방법 | |

| KR20070054914A (ko) | 박막 트랜지스터 기판 및 그 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081212 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20081212 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20101018 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101027 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110127 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110907 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120514 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120727 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120911 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121010 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151019 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5111758 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |