JP5073749B2 - 数値制御型オシレータ(nco)出力クロック位相平滑化 - Google Patents

数値制御型オシレータ(nco)出力クロック位相平滑化 Download PDFInfo

- Publication number

- JP5073749B2 JP5073749B2 JP2009529327A JP2009529327A JP5073749B2 JP 5073749 B2 JP5073749 B2 JP 5073749B2 JP 2009529327 A JP2009529327 A JP 2009529327A JP 2009529327 A JP2009529327 A JP 2009529327A JP 5073749 B2 JP5073749 B2 JP 5073749B2

- Authority

- JP

- Japan

- Prior art keywords

- clock

- phase

- nco

- phase error

- input

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/156—Arrangements in which a continuous pulse train is transformed into a train having a desired pattern

- H03K5/1565—Arrangements in which a continuous pulse train is transformed into a train having a desired pattern the output pulses having a constant duty cycle

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/099—Details of the phase-locked loop concerning mainly the controlled oscillator of the loop

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/02—Digital function generators

- G06F1/025—Digital function generators for functions having two-valued amplitude, e.g. Walsh functions

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/13—Arrangements having a single output and transforming input signals into pulses delivered at desired time intervals

- H03K5/133—Arrangements having a single output and transforming input signals into pulses delivered at desired time intervals using a chain of active delay devices

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/0805—Details of the phase-locked loop the loop being adapted to provide an additional control signal for use outside the loop

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/081—Details of the phase-locked loop provided with an additional controlled phase shifter

- H03L7/0812—Details of the phase-locked loop provided with an additional controlled phase shifter and where no voltage or current controlled oscillator is used

- H03L7/0816—Details of the phase-locked loop provided with an additional controlled phase shifter and where no voltage or current controlled oscillator is used the controlled phase shifter and the frequency- or phase-detection arrangement being connected to a common input

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K2005/00013—Delay, i.e. output pulse is delayed after input pulse and pulse length of output pulse is dependent on pulse length of input pulse

- H03K2005/00019—Variable delay

- H03K2005/00026—Variable delay controlled by an analog electrical signal, e.g. obtained after conversion by a D/A converter

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Nonlinear Science (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Stabilization Of Oscillater, Synchronisation, Frequency Synthesizers (AREA)

Description

本発明の実施例は、LCDディスプレイ(例えば、テレビジョンディスプレイ)などのイメージングシステムと関連するハードウエア又はコンピュータ上で稼動するソフトウエア上で実現させることが可能である。該コンピュータシステムは、パソコン、ノートブックコンピュータ、サーバコンピュータ、メインフレーム、ネットワーク型コンピュータ、ワークステーション等とすることが可能である。このソフトウエアプログラムは、NCOクロック位相平滑化を与えるべく動作可能である。1実施例においては、該コンピュータシステムは、バスに結合されているプロセッサ、及び該バスに結合されているメモリ格納部を包含している。該メモリ格納部は、揮発性又は非揮発性とすることが可能であり、且つ着脱自在な格納媒体を包含することが可能である。該コンピュータは、又、ディスプレイ、データ入力及び出力用設備等を包含することが可能である。

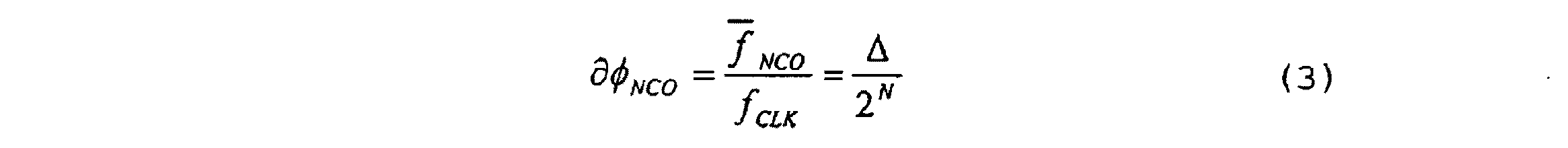

本発明の実施例は、最小のジッタを示す一次クロックから二次クロックを派生する目的のためのNCOクロックを実現する。特に、本発明の実施例は、従来のNCOクロック出力によって発生される離散化によって発生されるジッタと比較した場合にNCOクロックの出力上のジッタを減少させることが可能である。

Claims (17)

- 位相平滑化システムであって、

入力クロックに基づく選択可能周波数において複数個のNCOクロックパルスを生成するように構成されており、前記複数個のNCOクロックパルスのエッジが前記入力クロックのエッジに整合されている、数値制御型オシレータ(NCO)と、

前記NCOへ結合されており、前記複数個のNCOクロックパルスの各々に対して対応する位相エラーを生成するように構成されている、位相エラー計算モジュールと、

前記位相エラー計算モジュールへ結合されており、前記選択可能周波数において出力クロックを発生するために前記対応する位相エラーに従って前記複数個のNCOクロックパルスの各々を調節するように構成されているクロック位相選択可能遅延であって、前記出力クロックのエッジが、理想的な出力位相を一層近接して近似するべく位相調節されており且つ前記入力クロックの前記エッジと必ずしも整合する必要がない、クロック位相選択可能遅延と、

を含み、

前記クロック位相選択可能遅延が、

L個のバッファの第1のストリングを有し、前記入力クロックを受け取り且つ前記入力クロックをL個の等しい位相へロックするように構成されている遅延ロックループ(DLL)と、

L個のバッファの第2のストリングを有し、前記複数個のNCOクロックパルスを受け取り且つ前記入力クロックの前記L個の等しい位相を発生するように構成されている電圧制御型遅延線(VCDL)と、

前記対応する位相エラーを受け取り且つ前記複数個のNCOクロックパルスの内の対応するNCOクロックパルスへ適用される前記対応する位相エラーに基づいて適宜の位相遅延を選択するように構成されているマルチプレクサと、

を含み、

L個のバッファの前記第2のストリングに印加される制御電圧がL個のバッファの前記第1のストリングに印加される制御電圧と等しい、

位相平滑化システム。 - 請求項1に記載の位相平滑化システムであって、

前記NCOが、

前記入力クロックを受け取り且つ前記入力クロックのエッジにおいて蓄積された値を与えるように構成されているアキュムレータを含む、

位相平滑化システム。 - 請求項2に記載の位相平滑化システムであって、

前記NCOが、更に、

前記アキュムレータへ結合されており、前記アキュムレータ内の値を周波数制御入力に継続的に加算するように構成されている加算ブロックを含む、

位相平滑化システム。 - 請求項3に記載の位相平滑化システムであって、

前記加算ブロックが、前記入力クロックの前記エッジにおいて前記周波数制御入力を前記蓄積された値に加算し且つ前記アキュムレータ内に格納するために次の前に蓄積された値を発生するように構成されている、位相平滑化システム。 - 請求項2に記載の位相平滑化システムであって、

前記アキュムレータが、前記複数個のNCOクロックパルスの内の1個のNCOクロックパルスを出力するように構成されている、位相平滑化システム。 - 請求項2に記載の位相平滑化システムであって、

前記位相エラー計算モジュールが、前記選択可能周波数において理想的なNCOクロックと比較される前記アキュムレータによって発生されるNCOクロックパルスの位相エラーを決定するように構成されており、前記位相エラーが前記アキュムレータ内の前記蓄積された値のフラクショナルビットに基づいている、位相平滑化システム。 - 請求項1に記載の位相平滑化システムであって、

前記DLLが、

前記第1のストリングに結合されており、前記Lに等しい位相が入力クロック周期に等しく無い場合に差エラーを計算するように構成されている位相周波数検知器(PFD)と、

前記ストリングを前記入力クロックへロックするために前記差エラーを補正するために前記PFDへ結合されているチャージポンプと、

を含む、位相平滑化システム。 - 位相平滑化システムであって、

入力クロックを受け取り且つ前記入力クロックのエッジにおいて蓄積された値を供給するように構成されており、選択可能周波数においてNCOクロックのNCOクロックパルスを生成する、アキュムレータと、

前記アキュムレータへ結合されており、前記アキュムレータ内に格納するために次の蓄積された値を発生するために前記蓄積された値を周波数制御入力に加算するように攻勢されている、加算ブロックと、

前記アキュムレータへ結合されており、前記NCOクロックパルスに対する位相エラーを発生するように構成されている、位相エラー計算モジュールと、

前記位相エラー計算モジュールへ結合されており、前記選択可能周波数において出力クロックの出力クロックパルスを発生するために前記位相エラーに従って前記NCOクロックパルスを調節するように構成されているクロック位相選択可能遅延であって、前記出力クロックのエッジが理想的な出力位相を一層近接して近似するように位相調節されており且つ前記入力クロックの前記エッジに必ずしも整合する必要がない、クロック位相選択可能遅延と、

を含み、

前記クロック位相選択可能遅延が、

L個のバッファの第1のストリングを有し、前記入力クロックを受け取り且つ前記入力クロックをL個の等しい位相へロックするように構成されている遅延ロックループ(DLL)と、

L個のバッファの第2のストリングを有し、前記NCOクロックパルスを受け取り且つ前記入力クロックの前記L個の等しい位相を発生するように構成されている電圧制御型遅延線(VCDL)と、

前記位相エラーを受け取り且つ前記出力クロックとして前記NCOクロックパルスへ印加される前記位相エラーに基づいて適宜の位相遅延を選択するように構成されているマルチプレクサと、

を含み、

L個のバッファの前記第2のストリングに印加される制御電圧がL個のバッファの前記第1のストリングに印加される制御電圧と等しい、

位相平滑化システム。 - 請求項8に記載の位相平滑化システムであって、

前記位相エラー計算モジュールが前記蓄積された値のフラクショナルビットに基づいて前記位相エラーを決定するように構成されている、位相平滑化システム。 - 請求項8に記載の位相平滑化システムであって、

前記アキュムレータが前記蓄積された値の1個のビットに基づいて前記NCOクロックパルスを生成する、位相平滑化システム。 - 位相平滑化を提供する方法であって、

入力クロックに基づく選択可能周波数において複数個のNCOクロックパルスを生成し、前記複数個のNCOクロックパルスの前端が前記入力クロックの前端に整合しており、

前記選択可能周波数の理想的なNCOクロックと比較された場合に前記複数個のNCOクロックパルスの各々に対する対応する位相エラーを決定し、

前記選択可能周波数において出力クロックを発生するために前記対応する位相エラーを前記複数個のNCOクロックパルスの各々へ適用し、前記出力クロックの前記前端が前記理想的なNCOクロックの理想的な位相に一層近接して近似するように位相調節されており且つ前記入力クロックの前記前端と必ずしも整合する必要がない、

ことを含み、

前記対応する位相エラーを適用することが、

前記入力クロックのL個の等しい位相に対応するL個のタップ点を含む第1の遅延線を形成し、

前記NCOクロックパルスのL個の等しい位相に対応するL個のタップ点を含む第2の遅延線を形成し、

前記NCOクロックパルスへ適宜の位相遅延を適用するために前記対応する位相エラーに基づいて前記第2の遅延線の適宜のタップ点を選択する、

ことを含み、

前記第1及び第2の遅延線が同じ制御電圧で制御される、

方法。 - 請求項11に記載の方法であって、

前記複数個のNCOクロックパルスを生成することが、

前記入力クロックの前端において、蓄積された値を周波数制御入力に加算して次の蓄積された値を発生し、

前記次の蓄積された値を格納する、

ことを含む、方法。 - 請求項12に記載の方法であって、更に、

前記複数個のNCOクロックパルスの内の1個のNCOクロックパルスを発生する、

ことを含む、方法。 - 請求項12に記載の方法であって、

前記対応する位相エラーを決定することが、

前記蓄積された値のフラクショナルビットに基づいてNCOクロックパルスの正規化された位相エラーを決定し、

1から前記正規化された位相エラーを減算することにより前記対応する位相エラーを発生するために前記正規化された位相エラーを補償する、

ことを含む、方法。 - 請求項11に記載の方法であって、更に、

前記入力クロックを受け取り、

前記入力クロックをL個の等しい位相へロックする、

ことを含む、方法。 - 請求項11に記載の方法であって、更に、

前記出力クロックとして前記適宜の位相遅延を具備する前記NCOクロックパルスを出力する、

ことを含む、方法。 - 請求項11に記載の方法であって、

前記適宜のタップ点を選択することが、

前記L個のタップ点を提供する電圧制御型遅延線(VCDL)の全てのバッファが同一の値である場合に前記適宜のタップ点を選択する、

ことを含む、方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/523,123 | 2006-09-18 | ||

| US11/523,123 US7826582B2 (en) | 2006-09-18 | 2006-09-18 | Numerically controlled oscillator (NCO) output clock phase smoothing |

| PCT/US2007/078688 WO2008036613A1 (en) | 2006-09-18 | 2007-09-18 | Numerically controlled oscillator (nco) output clock phase smoothing |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010504068A JP2010504068A (ja) | 2010-02-04 |

| JP5073749B2 true JP5073749B2 (ja) | 2012-11-14 |

Family

ID=39188588

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009529327A Active JP5073749B2 (ja) | 2006-09-18 | 2007-09-18 | 数値制御型オシレータ(nco)出力クロック位相平滑化 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7826582B2 (ja) |

| JP (1) | JP5073749B2 (ja) |

| KR (1) | KR20090067182A (ja) |

| TW (1) | TWI441455B (ja) |

| WO (1) | WO2008036613A1 (ja) |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7907028B1 (en) | 2008-02-19 | 2011-03-15 | Marvell International, Ltd. | Jitter compensated numerically controlled oscillator |

| US8082462B1 (en) * | 2008-11-13 | 2011-12-20 | Xilinx, Inc. | Direct synthesis of audio clock from a video clock via phase interpolation of a dithered pulse |

| DE102011077399A1 (de) * | 2010-06-10 | 2012-05-10 | Continental Teves Ag & Co. Ohg | Geschwindigkeitssensor mit Costas-Schleife |

| CN102468845B (zh) * | 2010-10-29 | 2013-10-16 | 鼎桥通信技术有限公司 | 一种消除数控振荡器的频率偏移的方法 |

| DE102011003738B4 (de) | 2011-02-08 | 2018-12-27 | Robert Bosch Gmbh | Verfahren und Vorrichtung zur Verringerung von Signalflankenjitter in einem Ausgangssignal eines numerisch kontrollierten Oszillators |

| US9024699B2 (en) | 2013-01-21 | 2015-05-05 | Apple Inc. | Numerically-controlled oscillator |

| KR101982492B1 (ko) | 2013-01-25 | 2019-05-27 | 삼성전자 주식회사 | 듀티 코드를 주기 코드에 정규화하여 클락 신호 생성 방법과 장치들 |

| US9563227B2 (en) * | 2013-02-06 | 2017-02-07 | Nvidia Corporation | Approach to clock frequency modulation of a fixed frequency clock source |

| US9287884B2 (en) * | 2013-02-21 | 2016-03-15 | Microchip Technology Incorporated | Enhanced numerical controlled oscillator |

| US10061444B2 (en) * | 2013-07-31 | 2018-08-28 | Apple Inc. | Self capacitance touch sensing |

| US9590602B2 (en) * | 2014-06-13 | 2017-03-07 | Stmicroelectronics International N.V. | System and method for a pulse generator |

| US9577648B2 (en) | 2014-12-31 | 2017-02-21 | Semtech Corporation | Semiconductor device and method for accurate clock domain synchronization over a wide frequency range |

| US10156135B2 (en) | 2015-04-08 | 2018-12-18 | Halliburton Energy Services, Inc. | Phase compensated fixed-point numerically controlled oscillator for downhole logging |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5365182A (en) | 1993-06-22 | 1994-11-15 | Motorola, Inc. | Method and apparatus for low power clock generation for high speed applications |

| US6424185B1 (en) | 1998-05-22 | 2002-07-23 | National Semiconductor Corporation | NCO based frequency synthesizer with jitter modulation |

| US6650721B1 (en) | 1999-08-05 | 2003-11-18 | Agere Systems Inc. | Phase locked loop with numerically controlled oscillator divider in feedback loop |

| US6429693B1 (en) * | 2000-06-30 | 2002-08-06 | Texas Instruments Incorporated | Digital fractional phase detector |

| DE10033109C2 (de) * | 2000-07-07 | 2002-06-20 | Infineon Technologies Ag | Taktsignalgenerator |

| US6983032B2 (en) * | 2001-08-28 | 2006-01-03 | Texas Instruments Incorporated | Digital timing recovery method for communication receivers |

| US7839178B2 (en) * | 2002-08-20 | 2010-11-23 | Seagate Technology Llc | High speed digital phase/frequency comparator for phase locked loops |

| JP3863522B2 (ja) * | 2003-12-25 | 2006-12-27 | Necエレクトロニクス株式会社 | ディジタルvco、vco回路、pll回路、情報記録装置及び同期クロック信号生成方法 |

| US7643595B2 (en) * | 2004-09-13 | 2010-01-05 | Nortel Networks Limited | Method and apparatus for synchronizing clock timing between network elements |

| KR100644127B1 (ko) * | 2005-01-03 | 2006-11-10 | 학교법인 포항공과대학교 | 무한의 위상 이동 기능을 가지는 전압 제어 지연 라인을기반으로 하는 듀얼 루프 디엘엘 |

| US7102403B2 (en) * | 2005-02-03 | 2006-09-05 | Mediatek Incorporation | Clock recovering circuit utilizing a delay locked loop for generating an output clock locked to an analog input signal and related method thereof |

| US7271634B1 (en) * | 2005-09-16 | 2007-09-18 | Advanced Micro Devices, Inc. | Delay-locked loop having a plurality of lock modes |

| US7323915B2 (en) * | 2006-01-19 | 2008-01-29 | Honeywell International, Inc. | Delay locked loop with selectable delay |

| US7570725B1 (en) * | 2006-03-07 | 2009-08-04 | Marvell International Ltd. | Numerically controlled oscillator |

-

2006

- 2006-09-18 US US11/523,123 patent/US7826582B2/en active Active

-

2007

- 2007-09-18 WO PCT/US2007/078688 patent/WO2008036613A1/en not_active Ceased

- 2007-09-18 KR KR1020097007839A patent/KR20090067182A/ko not_active Withdrawn

- 2007-09-18 JP JP2009529327A patent/JP5073749B2/ja active Active

- 2007-09-19 TW TW096134782A patent/TWI441455B/zh active

Also Published As

| Publication number | Publication date |

|---|---|

| TW200838148A (en) | 2008-09-16 |

| US7826582B2 (en) | 2010-11-02 |

| WO2008036613A1 (en) | 2008-03-27 |

| JP2010504068A (ja) | 2010-02-04 |

| US20080069284A1 (en) | 2008-03-20 |

| TWI441455B (zh) | 2014-06-11 |

| KR20090067182A (ko) | 2009-06-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5073749B2 (ja) | 数値制御型オシレータ(nco)出力クロック位相平滑化 | |

| CN100409572C (zh) | 频率转换器及其使用方法 | |

| US9735787B2 (en) | Frequency synthesizer with dynamic phase and pulse-width control | |

| US7800451B2 (en) | Frequency adjustment for clock generator | |

| WO2010036449A2 (en) | Method and apparatus for counter-based clock signal adaptation | |

| US8184762B2 (en) | Digital phase lock loop with multi-phase master clock | |

| US6779010B2 (en) | Accumulator with programmable full-scale range | |

| US8664990B2 (en) | Coherent phase locked loop | |

| US7071787B2 (en) | Method and apparatus for the reduction of phase noise | |

| JP4198068B2 (ja) | デジタル周波数変換のための方法および装置 | |

| US12308850B2 (en) | Low jitter clock multiplier circuit and method with arbitrary frequency acquisition | |

| US8443023B2 (en) | Frequency synthesis rational division | |

| US20050093583A1 (en) | Fixed frequency clock output having a variable high frequency input clock and an unrelated fixed frequency reference signal | |

| CN1951014A (zh) | 用于可编程时钟发生器的设备和方法 | |

| JP2017169189A (ja) | スペクトラム拡散クロック発生回路 | |

| KR20050016309A (ko) | 디지털 주파수 전환을 위한 방법 및 장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100909 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120412 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120424 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120627 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120814 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120822 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5073749 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150831 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |