JP5010239B2 - 補償付き増幅器 - Google Patents

補償付き増幅器 Download PDFInfo

- Publication number

- JP5010239B2 JP5010239B2 JP2006299309A JP2006299309A JP5010239B2 JP 5010239 B2 JP5010239 B2 JP 5010239B2 JP 2006299309 A JP2006299309 A JP 2006299309A JP 2006299309 A JP2006299309 A JP 2006299309A JP 5010239 B2 JP5010239 B2 JP 5010239B2

- Authority

- JP

- Japan

- Prior art keywords

- amplifier

- input

- output

- capacitor

- amplifiers

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000003990 capacitor Substances 0.000 claims description 62

- 238000013500 data storage Methods 0.000 description 18

- 238000010586 diagram Methods 0.000 description 16

- 238000012545 processing Methods 0.000 description 12

- 238000000034 method Methods 0.000 description 9

- 230000003287 optical effect Effects 0.000 description 7

- 230000006870 function Effects 0.000 description 6

- 230000003071 parasitic effect Effects 0.000 description 6

- 230000008569 process Effects 0.000 description 6

- 230000003321 amplification Effects 0.000 description 5

- 238000003199 nucleic acid amplification method Methods 0.000 description 5

- 238000004364 calculation method Methods 0.000 description 4

- 230000001413 cellular effect Effects 0.000 description 4

- 238000004891 communication Methods 0.000 description 3

- 230000004044 response Effects 0.000 description 2

- 230000003044 adaptive effect Effects 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012552 review Methods 0.000 description 1

- 230000035945 sensitivity Effects 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F1/00—Details of amplifiers with only discharge tubes, only semiconductor devices or only unspecified devices as amplifying elements

- H03F1/42—Modifications of amplifiers to extend the bandwidth

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F1/00—Details of amplifiers with only discharge tubes, only semiconductor devices or only unspecified devices as amplifying elements

- H03F1/26—Modifications of amplifiers to reduce influence of noise generated by amplifying elements

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/005—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements using switched capacitors, e.g. dynamic amplifiers; using switched capacitors as resistors in differential amplifiers

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2200/00—Indexing scheme relating to amplifiers

- H03F2200/18—Indexing scheme relating to amplifiers the bias of the gate of a FET being controlled by a control signal

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2200/00—Indexing scheme relating to amplifiers

- H03F2200/36—Indexing scheme relating to amplifiers the amplifier comprising means for increasing the bandwidth

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Amplifiers (AREA)

Description

Claims (6)

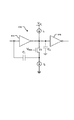

- (i)入力信号を受けるように構成された入力及び(ii)電圧源からの供給電圧を受けるように構成された出力を有する第1の増幅器と、

前記第1の増幅器の前記出力に接続する入力を有する第2の増幅器と、

第1端及び第2端を有する第1のキャパシタであって、該第1のキャパシタの該第1端は前記第1の増幅器の前記入力に接続する、該第1のキャパシタと、

第1端及び第2端を有する第2のキャパシタであって、該第2のキャパシタの該第1端は前記第1の増幅器の前記出力に接続する、該第2のキャパシタと、

第1端及び第2端を有する抵抗であって、該抵抗の該第1端は第1の電圧源に接続されており、該抵抗の該第2端は前記第2のキャパシタの前記第2端に接続されている、該抵抗と、

制御端子、前記抵抗の前記第2端及び前記第2のキャパシタの前記第2端に接続する第1の端子、並びに、前記第1のキャパシタの前記第2端に接続する第2の端子を有する第1のトランジスタと、

入力及び出力を有する電流源であって、該電流源の該入力は前記第1のキャパシタの前記第2端及び前記第1のトランジスタの前記第2の端子に接続されており、該電流源の該出力は電圧基準に接続されている、該電流源と、

を備え、

前記第1のトランジスタは、前記第1のキャパシタと前記第1の増幅器の出力との間に接続されている、増幅器システム。 - 前記第1の増幅器の前記出力と第2の電圧源との間に接続された別の電流源を更に備える、請求項1に記載の増幅器システム。

- 前記第1及び第2の増幅器が、演算トランスコンダクタンス増幅器を含む、請求項1に記載の増幅器システム。

- 前記第1のキャパシタの前記第1端は、前記第1の増幅器の前記入力に直接接続されている、請求項1に記載の増幅器システム。

- 前記第1のキャパシタは、前記第1の増幅器の前記入力と前記電圧基準との間に接続されている、請求項1に記載の増幅器システム。

- 前記第1の電圧源の電圧が前記第2の電圧源の電圧と異なる、請求項2に記載の増幅器システム。

Applications Claiming Priority (8)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/264,921 US7202733B1 (en) | 2005-11-02 | 2005-11-02 | Transconductance amplifiers with compensation |

| US11/264921 | 2005-11-02 | ||

| US79928206P | 2006-05-10 | 2006-05-10 | |

| US60/799282 | 2006-05-10 | ||

| US82087806P | 2006-07-31 | 2006-07-31 | |

| US60/820878 | 2006-07-31 | ||

| US11/503436 | 2006-08-11 | ||

| US11/503,436 US7459972B2 (en) | 2005-11-02 | 2006-08-11 | Amplifiers with compensation |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007129720A JP2007129720A (ja) | 2007-05-24 |

| JP2007129720A5 JP2007129720A5 (ja) | 2009-12-17 |

| JP5010239B2 true JP5010239B2 (ja) | 2012-08-29 |

Family

ID=37593827

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006299309A Active JP5010239B2 (ja) | 2005-11-02 | 2006-11-02 | 補償付き増幅器 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US7459972B2 (ja) |

| EP (1) | EP1783894B1 (ja) |

| JP (1) | JP5010239B2 (ja) |

| SG (1) | SG131904A1 (ja) |

| TW (1) | TWI426704B (ja) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7551024B2 (en) * | 2001-03-13 | 2009-06-23 | Marvell World Trade Ltd. | Nested transimpedance amplifier |

| US7558014B1 (en) | 2004-06-24 | 2009-07-07 | Marvell International Ltd. | Programmable high pass amplifier for perpendicular recording systems |

| JP5407264B2 (ja) * | 2008-10-09 | 2014-02-05 | ソニー株式会社 | 固体撮像素子およびカメラシステム |

| US8385016B1 (en) * | 2009-11-04 | 2013-02-26 | Marvell International, Inc. | Asymmetric correction circuit |

| EP3145216B1 (en) * | 2015-09-17 | 2018-11-14 | Nxp B.V. | Amplifier system |

| JP2017079397A (ja) * | 2015-10-20 | 2017-04-27 | 株式会社東芝 | 増幅回路 |

| US9667351B2 (en) | 2015-10-30 | 2017-05-30 | Avago Technologies General Ip (Singapore) Pte. Ltd. | Simultaneous bandwidth extension at high gain and peaking reduction at minimum gain for wideband, variable gain, linear optical receivers |

| US10469037B2 (en) | 2017-04-19 | 2019-11-05 | Mediatek Inc. | Multi-stage amplifier circuit with zero and pole inserted by compensation circuits |

| US10224887B2 (en) | 2017-08-04 | 2019-03-05 | Analog Devices, Inc. | Variable gain-bandwidth transimpedance amplifier |

| CN109428563B (zh) * | 2017-08-25 | 2022-11-22 | 瑞昱半导体股份有限公司 | 阻抗校正装置及其方法 |

| TWI641213B (zh) * | 2017-09-05 | 2018-11-11 | 瑞昱半導體股份有限公司 | 放大器與其重置方法 |

| CN109474241B (zh) * | 2017-09-08 | 2022-09-27 | 瑞昱半导体股份有限公司 | 放大器与其重置方法 |

| CN111478671B (zh) * | 2020-04-13 | 2023-04-14 | 电子科技大学 | 一种应用于Sub-GHz频段的新型低噪声放大器 |

| EP3945672A1 (en) * | 2020-07-31 | 2022-02-02 | NXP USA, Inc. | Error amplifier circuits for dc-dc converters, dc-dc converters and controllers |

Family Cites Families (31)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3079568A (en) * | 1959-02-09 | 1963-02-26 | Acf Ind Inc | Broad band amplifier |

| US3605031A (en) * | 1969-09-04 | 1971-09-14 | Blonder Tongue Lab | Wide-band low-distortion alternating current amplifier |

| US4185249A (en) * | 1978-08-23 | 1980-01-22 | Hewlett-Packard Company | Bipolar signal to current converter |

| US4405899A (en) * | 1979-03-01 | 1983-09-20 | Motorola, Inc. | High pass filter and method of making same |

| NL8002666A (nl) * | 1980-05-09 | 1981-12-01 | Philips Nv | Operationele versterker. |

| NL8204024A (nl) * | 1982-10-19 | 1984-05-16 | Philips Nv | Operationele versterker. |

| US4559502A (en) * | 1984-04-19 | 1985-12-17 | Signetics Corporation | Multi-stage amplifier with capacitive nesting for frequency compensation |

| JPH0767052B2 (ja) * | 1985-10-24 | 1995-07-19 | 日本電気株式会社 | 位相補償回路 |

| US5121075A (en) * | 1991-03-04 | 1992-06-09 | Hewlett-Packard Co. | Precision programmable attenuator |

| DE69429212D1 (de) * | 1993-06-21 | 2002-01-10 | Koninkl Philips Electronics Nv | Verstärkungsanordnung mit Vielweg-Millernullunterdrückung |

| AUPN204295A0 (en) * | 1995-03-29 | 1995-04-27 | Hildebrandt, William James | Amplifying circuit |

| EP0777318B1 (en) * | 1995-11-30 | 2003-03-12 | STMicroelectronics S.r.l. | Frequency self-compensated operational amplifier |

| US6002299A (en) * | 1997-06-10 | 1999-12-14 | Cirrus Logic, Inc. | High-order multipath operational amplifier with dynamic offset reduction, controlled saturation current limiting, and current feedback for enhanced conditional stability |

| EP0913926B1 (en) * | 1997-10-31 | 2004-03-03 | STMicroelectronics S.r.l. | Integrated power amplifier which allows parallel connections |

| US6114907A (en) * | 1998-12-08 | 2000-09-05 | National Semiconductor Corporation | Amplifier with dynamic compensation and method |

| US6208206B1 (en) * | 1999-02-11 | 2001-03-27 | The Hong Kong University Of Science And Technology | Frequency compensation techniques for low-power multistage amplifiers |

| JP2000261265A (ja) * | 1999-03-10 | 2000-09-22 | Toshiba Microelectronics Corp | 帰還型可変利得増幅回路 |

| US6400301B1 (en) * | 2000-09-07 | 2002-06-04 | Texas Instruments Incorporated | amplifying signals in switched capacitor environments |

| US6340916B1 (en) * | 2000-09-21 | 2002-01-22 | Telecommunications Laboratories, Chunghwa Telecom Co., Ltd. | Ransimpedance amplifier circuit |

| US6407640B1 (en) * | 2000-09-22 | 2002-06-18 | Qualcomm, Incorporated | Two-stage LNA with good linearity |

| US6624704B1 (en) * | 2001-10-25 | 2003-09-23 | National Semiconductor Corporation | High speed high current gain operational amplifier |

| US6882226B2 (en) * | 2002-05-16 | 2005-04-19 | Integrant Technologies Inc. | Broadband variable gain amplifier with high linearity and variable gain characteristic |

| US6842068B2 (en) * | 2003-02-27 | 2005-01-11 | Semiconductor Components Industries, L.L.C. | Power management method and structure |

| US6930544B2 (en) * | 2003-03-07 | 2005-08-16 | Matsushita Electric Industrial Co., Ltd. | Filter |

| US7002409B1 (en) * | 2004-02-11 | 2006-02-21 | Marvell International Ltd. | Compensation circuit for amplifiers having multiple stages |

| US7324035B2 (en) * | 2004-05-13 | 2008-01-29 | University Of Florida Research Foundation, Inc. | Amplifier with pulse coded output and remote signal reconstruction from the pulse output |

| TWI237441B (en) * | 2004-11-25 | 2005-08-01 | Himax Tech Inc | Operational amplifier with frequency compensation circuit |

| US7202746B1 (en) * | 2004-12-14 | 2007-04-10 | Cirrus Logic, Inc. | Multiple-stage operational amplifier and methods and systems utilizing the same |

| US7199656B1 (en) | 2005-11-02 | 2007-04-03 | Marvell World Trade International | Amplifiers with compensation |

| US7202733B1 (en) | 2005-11-02 | 2007-04-10 | Marvell International Ltd. | Transconductance amplifiers with compensation |

| US7161420B1 (en) | 2005-11-02 | 2007-01-09 | Marvell World Trade Ltd. | Amplifiers with compensation |

-

2006

- 2006-08-11 US US11/503,436 patent/US7459972B2/en active Active

- 2006-10-25 EP EP06022343.5A patent/EP1783894B1/en active Active

- 2006-10-30 SG SG200607353-0A patent/SG131904A1/en unknown

- 2006-10-31 TW TW095140239A patent/TWI426704B/zh not_active IP Right Cessation

- 2006-11-02 JP JP2006299309A patent/JP5010239B2/ja active Active

-

2008

- 2008-12-02 US US12/326,197 patent/US7737777B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20070109057A1 (en) | 2007-05-17 |

| US7459972B2 (en) | 2008-12-02 |

| TW200729699A (en) | 2007-08-01 |

| JP2007129720A (ja) | 2007-05-24 |

| US7737777B2 (en) | 2010-06-15 |

| EP1783894B1 (en) | 2019-03-20 |

| SG131904A1 (en) | 2007-05-28 |

| EP1783894A3 (en) | 2008-07-02 |

| US20090140803A1 (en) | 2009-06-04 |

| EP1783894A2 (en) | 2007-05-09 |

| TWI426704B (zh) | 2014-02-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5010239B2 (ja) | 補償付き増幅器 | |

| US7202733B1 (en) | Transconductance amplifiers with compensation | |

| EP1783898B1 (en) | High-bandwidth high-gain amplifier | |

| TWI416864B (zh) | 崁套式互阻抗放大器 | |

| EP1783899B1 (en) | High-bandwidth high-gain amplifier | |

| TWI433452B (zh) | 崁套式互阻抗放大器 | |

| US7696820B1 (en) | Increasing amplifier bandwidth by positive capacitive feedback | |

| US7468633B1 (en) | Multi-amplifier circuit | |

| US7323930B2 (en) | Amplifiers with compensation | |

| US7589649B1 (en) | Apparatus, method, and system for correction of baseline wander | |

| US7843247B1 (en) | Method and apparatus for controlled voltage level shifting | |

| US7525347B1 (en) | Differential peak detector | |

| JP2007129719A (ja) | 補償付き増幅器 | |

| US7199656B1 (en) | Amplifiers with compensation | |

| EP2495872B1 (en) | Two-stage class AB operational amplifier | |

| US7289381B1 (en) | Programmable boosting and charge neutralization | |

| US7852123B1 (en) | Reset-free comparator with built-in reference |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091029 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20091029 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110209 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110215 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110412 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110906 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111115 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120522 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120601 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5010239 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150608 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R371 | Transfer withdrawn |

Free format text: JAPANESE INTERMEDIATE CODE: R371 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R360 | Written notification for declining of transfer of rights |

Free format text: JAPANESE INTERMEDIATE CODE: R360 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R360 | Written notification for declining of transfer of rights |

Free format text: JAPANESE INTERMEDIATE CODE: R360 |

|

| R371 | Transfer withdrawn |

Free format text: JAPANESE INTERMEDIATE CODE: R371 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R360 | Written notification for declining of transfer of rights |

Free format text: JAPANESE INTERMEDIATE CODE: R360 |

|

| R370 | Written measure of declining of transfer procedure |

Free format text: JAPANESE INTERMEDIATE CODE: R370 |

|

| R360 | Written notification for declining of transfer of rights |

Free format text: JAPANESE INTERMEDIATE CODE: R360 |

|

| R371 | Transfer withdrawn |

Free format text: JAPANESE INTERMEDIATE CODE: R371 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |