JP4971069B2 - Fet増幅回路 - Google Patents

Fet増幅回路 Download PDFInfo

- Publication number

- JP4971069B2 JP4971069B2 JP2007204915A JP2007204915A JP4971069B2 JP 4971069 B2 JP4971069 B2 JP 4971069B2 JP 2007204915 A JP2007204915 A JP 2007204915A JP 2007204915 A JP2007204915 A JP 2007204915A JP 4971069 B2 JP4971069 B2 JP 4971069B2

- Authority

- JP

- Japan

- Prior art keywords

- fet

- bias

- source

- current

- gate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Amplifiers (AREA)

Description

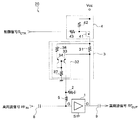

図1に示すFET増幅回路は、制御信号SCTRがローレベル(オン)のとき、電流供給回路3の動作がオンになる。まず、制御信号SCTRがローレベルになると、電源スイッチ4のトランジスタ45のエミッタ電位が制御信号SCTRの入力端子よりも電位が高くなり、トランジスタ45にベース電流が流れる。また、このベース電流に応じた電流がトランジスタ45のエミッタコレクタ間に流れる。すなわち、トランジスタ45のエミッタコレクタ間の抵抗値が下がり、ショートに近い状態となる。なお、このときトランジスタ44のコレクタエミッタ間には電流が流れない。すなわち、トランジスタ44のエミッタコレクタ間の抵抗値は開放に近い状態となる。

次に、図1に示すFET増幅回路10は、制御信号SCTRがハイレベル(オフ)のとき、電流供給回路3の動作がオフになる。制御信号SCTRがハイレベルになると、電源スイッチ4のトランジスタ44のエミッタ電位が制御信号SCTRの入力端子よりも電位が低くなり、トランジスタ44にベース電流が流れる。また、このベース電流に応じた電流がトランジスタ44のエミッタコレクタ間に流れる。すなわち、トランジスタ44のエミッタコレクタ間の抵抗値が下がり、ショートに近い状態となる。なお、このときトランジスタ45のコレクタエミッタ間には電流が流れない。すなわち、トランジスタ45のコレクタエミッタ間は開放状態(又はそれに近い状態)になる。

Claims (2)

- ソースが接地されたFET増幅素子と、

FET増幅素子のゲートソース間に並列に接続されたバイアス抵抗と、

FET増幅素子のドレイン又はソースに直列に接続されFET増幅素子のドレインソース間電流を検出するモニタ素子と、ゲート側に接続されたバイアス抵抗端子に接続されモニタ素子により検出されるドレインソース間電流が定電流化するバイアス電圧がFET増幅素子のゲートソース間に印加されるようバイアス抵抗に電流を供給する電流供給源と、を含む電流回路と、

所定のタイミングでオンオフが切り替わる制御信号に応じて電流回路の動作のオンオフを切り替える電源スイッチと、

を備え、

制御信号がオンのときに、FET増幅素子がゲートに入力された高周波信号を増幅してドレインから出力するFET増幅回路であって、

ゲート側に接続されたバイアス抵抗端子と所定の電源との間に直列に接続されたキャパシタと電圧印加スイッチとを含み、制御信号がオンのときに電圧印加スイッチがオンし、これにより所定の電源からバイアス抵抗にキャパシタを介して過渡電流を流してFET増幅素子のゲートソース間のバイアス電圧を上げるバイアス急昇圧回路と、

バイアス抵抗に並列に接続された電圧降下スイッチを含み、制御信号がオフのときに電圧降下スイッチがオンし、これによりFET増幅素子のゲートソース間のバイアス電圧を下げるバイアス急降圧回路と、

を備えることを特徴とするFET増幅回路。 - 請求項1に記載のFET増幅回路において、

前記キャパシタと前記電圧印加スイッチとの間の経路に一端が接続され、他端が接地された抵抗を備えることを特徴とするFET増幅回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007204915A JP4971069B2 (ja) | 2007-08-07 | 2007-08-07 | Fet増幅回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007204915A JP4971069B2 (ja) | 2007-08-07 | 2007-08-07 | Fet増幅回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009044281A JP2009044281A (ja) | 2009-02-26 |

| JP4971069B2 true JP4971069B2 (ja) | 2012-07-11 |

Family

ID=40444573

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007204915A Active JP4971069B2 (ja) | 2007-08-07 | 2007-08-07 | Fet増幅回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4971069B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9680425B2 (en) | 2013-08-29 | 2017-06-13 | Telefonaktiebolaget L M Ericsson (Publ) | Driver circuit and associated power amplifier assembly, radio base station and method |

| US10924064B2 (en) * | 2017-02-22 | 2021-02-16 | Sumitomo Electric Industries, Ltd. | Bias circuit |

| JPWO2024202353A1 (ja) * | 2023-03-29 | 2024-10-03 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6130344Y2 (ja) * | 1980-01-21 | 1986-09-05 | ||

| JPH07162241A (ja) * | 1993-12-06 | 1995-06-23 | Nec Corp | マイクロ波帯出力レベル自動制御回路 |

| JP2001284974A (ja) * | 2000-03-30 | 2001-10-12 | Nec Corp | Fet増幅器 |

-

2007

- 2007-08-07 JP JP2007204915A patent/JP4971069B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2009044281A (ja) | 2009-02-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9614440B2 (en) | Power supply device and semiconductor integrated circuit device | |

| JP5854372B2 (ja) | 電力増幅モジュール | |

| CN101999207B (zh) | 补偿功率放大器中的非线性电容效应 | |

| JP5939404B2 (ja) | 無線周波数増幅回路及び電力増幅モジュール | |

| US9148097B2 (en) | Electronic system—radio frequency power amplifier and method for dynamic adjusting bias point | |

| US6424225B1 (en) | Power amplifier circuit for providing constant bias current over a wide temperature range | |

| US8598953B2 (en) | System and method for pre-charging a current mirror | |

| US20110032037A1 (en) | Power amplifier bias circuit having controllable current profile | |

| US9024689B2 (en) | Electronic system—radio frequency power amplifier and method for self-adjusting bias point | |

| US20140112414A1 (en) | Power amplifier and the related power amplifying method | |

| CN114070215A (zh) | 功率放大器、功率放大器系统及其操作方法 | |

| US8688061B2 (en) | System and method for biasing a power amplifier | |

| JP4971069B2 (ja) | Fet増幅回路 | |

| CN108900167B (zh) | 阻抗补偿电路及功率放大补偿电路 | |

| US20140327482A1 (en) | Radio frequency power amplifier with no reference voltage for biasing and electronic system | |

| CN104617886B (zh) | 一种用于改善功率放大器开关谱的功率控制方法及其电路 | |

| US10608592B2 (en) | Linear amplifier having higher efficiency for envelope tracking modulator | |

| JP2006093896A (ja) | E級増幅器、及びeer変調増幅装置 | |

| EP3168988B1 (en) | Amplifier system and method for controlling amplifier | |

| CN113612458A (zh) | 一种可控制偏置电路及功率放大器 | |

| EP1542357B1 (en) | A power amplifier module and a time division multiple access radio | |

| KR100654644B1 (ko) | 최적화된 전력 효율을 갖는 전력 증폭기 | |

| JP2008165686A (ja) | 可変レギュレータ及びこの可変レギュレータを用いた電力増幅装置 | |

| JP2007201698A (ja) | 高周波電力増幅器 | |

| JPH1032434A (ja) | 電力増幅回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100806 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110819 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110830 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111027 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120403 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120405 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150413 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4971069 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |