JP4919084B2 - シーケンス制御回路 - Google Patents

シーケンス制御回路 Download PDFInfo

- Publication number

- JP4919084B2 JP4919084B2 JP2007314290A JP2007314290A JP4919084B2 JP 4919084 B2 JP4919084 B2 JP 4919084B2 JP 2007314290 A JP2007314290 A JP 2007314290A JP 2007314290 A JP2007314290 A JP 2007314290A JP 4919084 B2 JP4919084 B2 JP 4919084B2

- Authority

- JP

- Japan

- Prior art keywords

- program counter

- signal

- counter signal

- indicating

- outputs

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Programmable Controllers (AREA)

- Testing Of Individual Semiconductor Devices (AREA)

- Tests Of Electronic Circuits (AREA)

Description

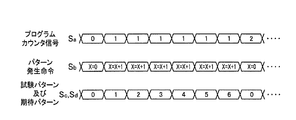

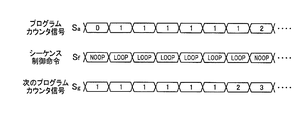

御回路300は、プログラムカウンタ「2」において、「NOOP(改行)」を実行して、プログラムカウンタを「3」に進める。以上のような動作により、シーケンス制御回路300から出力されるプログラムカウンタ信号Saは「0」「1」「1」「1」「1」「1」「1」「2」・・・となる(図8参照)。

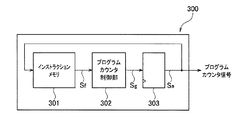

ス制御命令Sfに応じて次回のプログラムカウンタ信号Sgを出力するものである。フリップフロップ303は、プログラムカウンタ信号Saを出力すると共に、次回のプログラムカウンタ信号Sgを保持するものである。このフリップフロップ303は、初期値「0」を記憶しており、初期的には「0」のプログラムカウンタ信号Saをシーケンス制御回路300内のインストラクションメモリ301及び外部のインストラクションメモリ400に出力することとなる。

え、インストラクションメモリとプログラムカウンタ制御部とをパイプライン処理にて動作させる。

換えた場合、所定条件成立時に書き換えた内容を元に戻すため、次回、新たにシーケンス制御回路を作動させる場合に、書き換え後の状態のままとならず、次回のシーケンス制御回路の作動時においても適切にプログラムカウンタ信号を出力することができる。

」を示すプログラムカウンタ信号Sj1が出力されると、これを入力し(図1参照)、「NOOP」を示すシーケンス制御命令Sl1を第3フリップフロップ33に出力する。

るものである。さらに、ジャンプ制御回路41は、第2所定条件成立時(所定条件成立時)には、書き換えた内容を元に戻す復帰信号Ss2をデュアルポートメモリ11のライトイネーブルに出力するものである。

示すように、「NOOP」を示すシーケンス制御命令Sl1を出力する。そして、第2フリップフロップ32は、シーケンス制御命令Sl1を入力して保持する。

、ループカウンタ42からカウンタ信号Snを読み込む。そして、シーケンス制御命令Sl3が「LOOP」を示し、ループカウンタ42の値が「0」となっていないため、第2フリップフロップ32からのジャンプアドレス信号Sp2を選択する旨の選択信号Sqをセレクタ44に送信する。これにより、セレクタ44は、「1」を示すジャンプアドレス信号Sp2を信号Srとしてデュアルポートメモリ11のライトデータに出力することとなる。

トラクションメモリ20は、「1」を示すジャンプアドレス信号Sp1を第2フリップフロップ32に出力する。そして、第2フリップフロップ32は、時刻t4において入力した「1」を示すジャンプアドレス信号Sp2をセレクタ44に出力する。また、第3フリップフロップ33は、時刻t4において入力した「LOOP」を示すシーケンス制御命令Sl3を出力する。

モリ11のライトデータに出力することとなる。

力する。これにより、例えば、ループサイクルの終了にあわせてループを抜けるように、カウンタ信号出力部10から出力される次回のプログラムカウンタ信号Sj1を書き換えることができる。従って、出力したプログラムカウンタ信号Sj1を自ら入力し、入力したプログラムカウンタ信号Sj1のカウント値に応じて次回のプログラムカウンタ信号Sj1を出力するカウンタ信号出力部10を備えつつも、適切なループサイクルを実現することができる。

それぞれのシーケンス制御命令Sl1のうち1つを選択して出力するセレクタを設ける。このような構成の場合、プログラムカウンタ信号Sj1を例えば10bitの信号とし、複数のインストラクションメモリ20は10bitのうち下位9bitの信号を処理するものとする。上位1bitの信号はセレクタに直接入力され、セレクタは上位1bitの信号に基づいて、第3フリップフロップ33から出力されたそれぞれのシーケンス制御命令Sl1のうち1つを選択して出力する。

10 カウンタ信号出力部

11 デュアルポートメモリ

12 セレクタ

20 インストラクションメモリ

31〜33,50フリップフロップ

40 プログラムカウンタ制御部

41 ジャンプ制御回路

42 ループカウンタ

43 加算器

44 セレクタ

Claims (3)

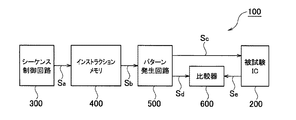

- アドレスを示すカウント値の情報を有したプログラムカウンタ信号を出力すると共に、出力した前記プログラムカウンタ信号を自ら入力し、入力したプログラムカウンタ信号のカウント値に応じて次回のプログラムカウンタ信号を出力するカウンタ信号出力手段と、

前記カウンタ信号出力手段からプログラムカウンタ信号を入力し、入力したプログラムカウンタ信号のカウント値に応じて、シーケンス制御命令を出力するインストラクションメモリと、

前記シーケンス制御命令を入力し、入力したシーケンス制御命令に応じて、前記カウンタ信号出力手段が出力する次回のプログラムカウンタ信号のカウント値を書き換えるプログラムカウンタ制御部と、を備え、

前記インストラクションメモリと前記プログラムカウンタ制御部とをパイプライン処理にて動作させ、

前記インストラクションメモリは、プログラムカウンタ信号によってアクセスされたアドレスにループを示すシーケンス制御命令を記憶している場合、ループを示すシーケンス制御命令を出力すると共に、回路構成に応じたループ回数を示すループ信号を出力し、

前記プログラムカウンタ制御部は、前記ループ信号を入力した後、所定タイミング毎に、前記ループ信号が示すループ回数をカウントダウンしていき、カウントダウン終了時にプログラムカウンタ信号のカウント値を書き換える書き換え信号を前記カウンタ信号出力手段に出力する

ことを特徴とするシーケンス制御回路。 - 前記プログラムカウンタ制御部は、次回のプログラムカウンタ信号のカウント値を書き換えた場合、所定条件成立時に書き換えた内容を元に戻す復帰信号を出力する

ことを特徴とする請求項1に記載のシーケンス制御回路。 - 前記プログラムカウンタ制御部は、今回のプログラムカウンタ信号と前回のプログラムカウンタ信号とを入力し、今回のプログラムカウンタ信号が示すカウント値から、前回のプログラムカウンタ信号が示すカウント値を減算した値が1となったときに、前記所定条件が成立したと判断して復帰信号を出力する

ことを特徴とする請求項2に記載のシーケンス制御回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007314290A JP4919084B2 (ja) | 2007-12-05 | 2007-12-05 | シーケンス制御回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007314290A JP4919084B2 (ja) | 2007-12-05 | 2007-12-05 | シーケンス制御回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009140122A JP2009140122A (ja) | 2009-06-25 |

| JP4919084B2 true JP4919084B2 (ja) | 2012-04-18 |

Family

ID=40870686

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007314290A Active JP4919084B2 (ja) | 2007-12-05 | 2007-12-05 | シーケンス制御回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4919084B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5233852B2 (ja) | 2009-06-11 | 2013-07-10 | アイシン・エィ・ダブリュ株式会社 | 電磁弁装置 |

| KR20120136474A (ko) | 2011-06-09 | 2012-12-20 | 삼성전자주식회사 | 반도체 테스트 장치 및 그 테스트 방법 |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002342076A (ja) * | 2001-05-18 | 2002-11-29 | Sharp Corp | パイプライン制御方式 |

| JP2003256237A (ja) * | 2002-02-27 | 2003-09-10 | Toshiba Corp | 割り込み発生装置、割り込み発生方法および割り込み発生プログラム |

-

2007

- 2007-12-05 JP JP2007314290A patent/JP4919084B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2009140122A (ja) | 2009-06-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US5966723A (en) | Serial programming mode for non-volatile memory | |

| US8195839B2 (en) | Apparatus and method for producing identifiers regardless of mixed device type in a serial interconnection | |

| JPS6239780B2 (ja) | ||

| US4670879A (en) | Pattern generator | |

| KR100498508B1 (ko) | 데이터 전송시간을 감소시키는 듀얼 버퍼링(Dualbuffering) 메모리 시스템 및 이에 대한 제어방법 | |

| US4759021A (en) | Test pattern generator | |

| US8464008B1 (en) | Command cancellation channel for read-modify-write operation in a memory | |

| JP4919084B2 (ja) | シーケンス制御回路 | |

| US9436466B2 (en) | Blank bit and processor instructions employing the blank bit | |

| US9916878B2 (en) | Methods and systems for parallel column twist interleaving | |

| JPS62226306A (ja) | プログラマブルシ−ケンサ | |

| JPH10319095A (ja) | 半導体テスト装置 | |

| JP2006313090A (ja) | 半導体集積回路及びそのバーインテスト方法 | |

| JP5032137B2 (ja) | 半導体記憶装置 | |

| US7345496B2 (en) | Semiconductor apparatus and test execution method for semiconductor apparatus | |

| KR100632338B1 (ko) | 반도체 장치 및 그 시험 방법 | |

| KR20060019609A (ko) | 시험 장치, 및 프로그램 | |

| JP2568268B2 (ja) | データ列発生回路及びその回路を用いたメモリテスト装置 | |

| EP0142562A1 (en) | Pipeline system for microprogram control unit | |

| JP2001282324A (ja) | シーケンス制御回路 | |

| JP2007058450A (ja) | 半導体集積回路 | |

| KR102724459B1 (ko) | 데이터 입출력 유닛, 전자 장치 및 그 제어 방법들 | |

| JP2010085177A (ja) | 半導体試験装置 | |

| US20010021973A1 (en) | Processor | |

| JPWO2008026273A1 (ja) | Dmaコントローラ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100924 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20111014 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111020 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111212 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120105 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120118 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4919084 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150210 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20180210 Year of fee payment: 6 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20180210 Year of fee payment: 6 |

|

| S201 | Request for registration of exclusive licence |

Free format text: JAPANESE INTERMEDIATE CODE: R314201 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20180210 Year of fee payment: 6 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |