JP4891682B2 - 液晶表示装置及びその駆動方法 - Google Patents

液晶表示装置及びその駆動方法 Download PDFInfo

- Publication number

- JP4891682B2 JP4891682B2 JP2006195304A JP2006195304A JP4891682B2 JP 4891682 B2 JP4891682 B2 JP 4891682B2 JP 2006195304 A JP2006195304 A JP 2006195304A JP 2006195304 A JP2006195304 A JP 2006195304A JP 4891682 B2 JP4891682 B2 JP 4891682B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- voltage

- pixel

- liquid crystal

- gate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3685—Details of drivers for data electrodes

- G09G3/3688—Details of drivers for data electrodes suitable for active matrices only

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

- G09G3/3659—Control of matrices with row and column drivers using an active matrix the addressing of the pixel involving the control of two or more scan electrodes or two or more data electrodes, e.g. pixel voltage dependant on signal of two data electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0439—Pixel structures

- G09G2300/0443—Pixel structures with several sub-pixels for the same colour in a pixel, not specifically used to display gradations

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0439—Pixel structures

- G09G2300/0443—Pixel structures with several sub-pixels for the same colour in a pixel, not specifically used to display gradations

- G09G2300/0447—Pixel structures with several sub-pixels for the same colour in a pixel, not specifically used to display gradations for multi-domain technique to improve the viewing angle in a liquid crystal display, such as multi-vertical alignment [MVA]

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0876—Supplementary capacities in pixels having special driving circuits and electrodes instead of being connected to common electrode or ground; Use of additional capacitively coupled compensation electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0202—Addressing of scan or signal lines

- G09G2310/0205—Simultaneous scanning of several lines in flat panels

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0202—Addressing of scan or signal lines

- G09G2310/0213—Addressing of scan or signal lines controlling the sequence of the scanning lines with respect to the patterns to be displayed, e.g. to save power

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/06—Details of flat display driving waveforms

- G09G2310/061—Details of flat display driving waveforms for resetting or blanking

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/08—Details of timing specific for flat panels, other than clock recovery

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0247—Flicker reduction other than flicker reduction circuits used for single beam cathode-ray tubes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0261—Improving the quality of display appearance in the context of movement of objects on the screen or movement of the observer relative to the screen

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/06—Adjustment of display parameters

- G09G2320/068—Adjustment of display parameters for control of viewing angle adjustment

Description

垂直配向モード液晶表示装置で広視野角を実現するための手段としては、電場生成電極に切開部を形成する方法と電場生成電極上に突起を形成する方法などがある。切開部と突起で液晶分子の傾斜方向を決めることができるので、これらを使用して液晶分子の傾斜方向を多様な方向に分散させることで基準視野角を広めることができる。

側面視認性を改善するために1つの画素を2つの副画素に分割し、2つの副画素を容量性結合させた後、一方の副画素には直接電圧を印加し、他方の副画素には容量性結合による電圧下降を起こして2つの副画素の電圧を異ならせることで透過率を異ならせる方法が提示された。

前記インパルシブデータ電圧は前記第2副画素電極に印加できる。

前記インパルシブデータ電圧は前記第1及び第2正規映像データ電圧より小さくてもよい。

M個の束の映像情報を受けて各M個の束の第1及び第2正規映像データに変換し、1つの束のインパルシブデータを生成して前記第1及び第2正規映像データ及び前記インパルシブデータを前記データ駆動部に伝送する信号制御部をさらに含むことができる。

互いに異なる第1及び第2階調電圧集合を生成し、前記第1及び第2階調電圧集合から前記第1及び第2正規映像データ電圧を各々選択して、前記第1及び第2副画素電極に各々印加することができる。

前記インパルシブデータ電圧は複数の画素行の第2副画素電極に同時に印加できる。

前記第1及び第2正規映像データ電圧は各々複数の画素行の第1及び第2副画素電極に交互であって順に印加することができる。

前記第2番目M個の画素行の第2副画素電極に前記インパルシブデータ電圧を印加した後、前記第1番目M個の画素行の第1及び第2副画素電極に印加された前記第1及び第2正規映像データ電圧の極性と異なる所定の先充電電圧を前記データ線に印加することができる。

前記ゲート駆動部は複数の水平周期の間に前記第2ゲート線に前記ゲートオン電圧を複数回印加することができる。

前記ゲート駆動部は複数の画素行の第2ゲート線に前記ゲートオン電圧を同時に印加することができる。

第1番目画素行の第1及び第2副画素電極に前記第1番目画素行の第1及び第2正規映像データ電圧が各々印加された後、第2画素行の第1及び第2副画素電極に前記第2画素行の第1正規映像データ電圧及び前記インパルシブデータ電圧を各々印加することができる。

図面において多様な層及び領域を明確に表現するために厚さを拡大して示した。明細書全体にわたって類似する部分については同一図面符号を付けた。層、膜、領域、板などの部分が他の部分の“上”にあるとする時、これは他の部分の“直上”にある場合だけでなく、その中間に他の部分がある場合も含む。反対に、ある部分が他の部分の“直上”にあるとする時には中間に他の部分がないことを意味する。

図1は本発明の1つの実施例による液晶表示装置のブロック図であり、図2は本発明の1つの実施例による液晶表示装置の1つの画素に対する等価回路図である。

図1に示したように、本発明の1つの実施例による液晶表示装置は液晶表示板組立体300及び、これと接続されたゲート駆動部400及びデータ駆動部500、データ駆動部500に接続された階調電圧生成部800、そしてこれらを制御する信号制御部600を含む。

信号線Gi、Djはゲート信号(“走査信号”とも言う)を伝達する複数のゲート線Giとデータ信号を伝達する複数のデータ線Djを含む。ゲート線はほぼ行方向に延びて互いにほぼ平行であり、データ線はほぼ列方向に延びて互いにほぼ平行である。

スイッチング素子Qは下部表示板100に設けられている薄膜トランジスタなどの三端子素子であって、その制御端子はゲート線Giと接続されており、入力端子はデータ線Djと接続されており、出力端子は液晶キャパシタCLC及びストレージキャパシタCSTと接続されている。

再び図1を参照すれば、階調電圧生成部800は画素PXの透過率と関する2つの階調電圧集合(または基準階調電圧集合)を生成する。2つの(基準)階調電圧集合は互いに異なるガンマ曲線に基づいて生成され、各(基準)階調電圧集合は共通電圧Vcomに対して正の値を有するものと負の値を有するものを含む。しかし、2つの(基準)階調電圧集合の代わりに1つの(基準)階調電圧集合のみを生成することもできる。

データ駆動部500は液晶表示板組立体300のデータ線Djと接続されており、階調電圧生成部800からの2つの階調電圧集合のうちの1つを選択し、選択された階調電圧集合に属する1つの階調電圧をデータ信号としてデータ線Djに印加する。しかし、階調電圧生成部800が全ての階調に対応する電圧を全て提供する必要はなく、決められた数の基準階調電圧のみを提供するように構成することが可能であり、この場合データ駆動部500は基準階調電圧を分圧して全体階調に対する階調電圧を生成し、この中からデータ信号を選択するように構成できる。

このような駆動装置400、500、600、800の各々は少なくとも1つの集積回路チップの形態で液晶表示板組立体300上に直接装着されたり、可撓性印刷回路膜(図示せず)上に装着されてTCP(tape carrier package)の形態で液晶表示板組立体300に付着するように構成でき、別途の印刷回路基板(図示せず)上に装着することも可能である。これとは異なって、これら駆動装置400、500、600、800を複数の駆動回路形態で集積して液晶表示板組立体300に実装するように構成することもできる。また、駆動装置400、500、600、800は単一チップに集積する必要はなく、これらのうちの少なくとも1つまたはこれらを構成する少なくとも1つの回路素子を単一チップの外側に構成することができる。

図3は本発明の1つの実施例による液晶表示装置の駆動信号を示したタイミング図であり、図4は図3に示した駆動信号によって表示される画像を1つのフレームの間に表示した概略図である。

データ制御信号CONT2は1つの画素行の出力映像信号DATの伝送開始を知らせる水平同期開始信号STHと、液晶表示板組立体300にデータ信号を印加することを命令するロード信号LOAD及びデータクロック信号HCLKを含む。データ制御信号CONT2はまた共通電圧Vcomに対するデータ信号の電圧極性(以下、“共通電圧に対するデータ信号の電圧極性”を“データ信号の極性”と言う)を反転させる反転信号RVSをさらに含む。

階調電圧生成部800が2つの階調電圧集合を生成する場合、正規映像データとインパルシブデータの階調値は同一であり、正規映像データとインパルシブデータに対して互いに異なる階調電圧集合がそれぞれ対応し、各階調に対する階調電圧は互いに異なる場合がある。正規映像データが示すガンマ曲線は液晶表示装置の特性によって決められ、インパルシブデータが示すガンマ曲線は正規映像データが示すガンマ曲線に比べて低い輝度を示す。場合によってはインパルシブデータが示すガンマ曲線が全ての階調に対してブラックを示したり、任意の一定の輝度を示したりする。

画素PXに印加されたデータ電圧Vdと共通電圧Vcomの差は液晶キャパシタCLCの充電電圧、つまり、画素電圧として示される。液晶分子は画素電圧の大きさによってその配列を異ならせ、それによって液晶層3を通過する光の偏光が変化する。このような偏光の変化は液晶表示板組立体300に付着された偏光子によって光の透過率変化で示される。

1つのフレームが終われば、次のフレームが始まり、各画素PXに印加されるデータ電圧Vdの極性が直前フレームにおける極性と反対になるように、データ駆動部500に印加される反転信号RVSの状態を制御することができる(“フレーム反転”)。この時、1つのフレーム内でも反転信号RVSの特性によって1つのデータ線を通じて流れる正規映像データ電圧Nの極性を変えることができる(例えば:行反転、点反転)。これと異なって、一束の画素に印加される正規映像データ電圧Nの極性を互いに異なるように構成することもできる(例えば:列反転、点反転)。インパルシブデータ電圧Iの極性も反転信号RVSによって変わるが、図3と異なって任意の極性になってもよい。

このように正規映像及びインパルシブ映像を表示することによってブラリングを防止することができ、インパルシブ駆動のための周波数の増加が相対的に少なくて画素電圧の充電率を高めることができる。

シフトレジスター部510は複数のシフトレジスターを含み、各シフトレジスターは決められた量の映像データDATを全部シフトさせた後、シフトクロック信号(図示せず)を次の段のシフトレジスターに送って、1つの画素行の映像データDATがシフトレジスター部510のシフトレジスターに順にシフトされる。

デジタル−アナログ変換器530は階調電圧生成部800から階調電圧Vgmの入力を受けて反転信号RVSによって共通電圧Vcomに対して正の値を有する階調電圧と負の値を有する階調電圧のうちの各映像データDATに対応するいずれか1つを選択する。そして、デジタル−アナログ変換器530は選択された階調電圧を当該アナログデータ電圧に変換する。

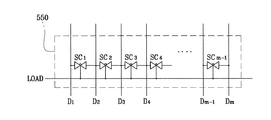

チャージシェアリング部550は、既に説明したように、制御端子にロード信号LOADに印加されるトランスミッションゲートから構成されている。図7に示したように、ロード信号LOADが高レベルを維持する間にトランスミッションゲートSC1-SCm-1は導通状態になって全てのデータ線D1-Dmが互いに接続される。したがって、全てのデータ線D1-Dmの電圧状態は所定の電圧レベルV1に均一となる。つまり、チャージシェアリングが行われる。その後、ロード信号LOADが高レベルから低レベルに変われば、下降エッジ時にトランスミッションゲートSC1-SCm-1の制御端子に低レベルが印加されて、全てのトランスミッションゲートSC1-SCm-1は導通状態から非導通状態に変わり、映像データDATに対応する当該データ電圧がデータ線D1-Dmを通じて伝達される。

この時、データ線に正常データ電圧やブラックデータ電圧が印加される前にデータ駆動部500はロード信号LOADに同期して全てのデータ線を接続するチャージシェアリングを実施する。次に、図5を参照して、このようなデータ駆動部500の動作についてさらに詳細に説明する。

データ駆動部500は、図5に示したように、シフトレジスター部510、ラッチ520、デジタル−アナログ変換器530、バッファー540、そしてチャージシェアリング部550を備える。チャージシェアリング部550は、図6に示したように、隣接したデータ線の間に接続された複数のスイッチング素子SC1,SC2,…,SCm-1を含む。各スイッチング素子SC1,SC2,…,SCm-1は制御端子及び反転制御端子を有しているトランスミッションゲートであり、制御端子にロード信号LOADが印加される。

デジタル−アナログ変換器530は階調電圧生成部800から階調電圧Vgmの入力を受けて反転信号RVSによって共通電圧Vcomに対して正の値を有する階調電圧と負の値を有する階調電圧のうちのいずれか1つを選択する。そして、選択された階調電圧の中で各映像データDATに対応する階調電圧を選択し、デジタル映像データDATを当該アナログデータ電圧に変換する。

チャージシェアリング部550は、既に説明したように、制御端子にロード信号LOADに印加されるトランスミッションゲートから構成されている。図7に示したように、ロード信号LOADが高レベルを維持する間に、トランスミッションゲートSC1-SCm-1は導通状態になって、全てのデータ線D1-Dmが互いに接続される。したがって、全てのデータ線D1-Dmの電圧状態は所定の電圧レベルV1に均一となる。つまり、チャージシェアリングが行われる。その後、ロード信号LOADが高レベルから低レベルに変われば、つまり、下降エッジ時にトランスミッションゲートSC1-SCm-1の制御端子に低レベルが印加されて、全てのトランスミッションゲートSC1-SCm-1は導通状態から非導通状態に変わり、映像データDATに対応する当該データ電圧がデータ線D1-Dmを通じて伝達される。

図8は本発明の他の実施例による液晶表示装置の2つの副画素に対する等価回路図である。

図1に示すように、本発明の他の実施例による液晶表示装置も液晶表示板組立体300、ゲート駆動部400、データ駆動部500、階調電圧生成部800、そして信号制御部600を含む。

信号線はゲート信号(“走査信号”とも言う)を伝達する複数のゲート線(図示せず)とデータ信号を伝達する複数のデータ線(図示せず)を含む。ゲート線はほぼ行方向に延びた互いにほぼ平行であり、データ線はほぼ列方向に延びて互いにほぼ平行である。

液晶キャパシタCLCa/CLCbは下部表示板100の副画素電極PEa/PEbと上部表示板200の共通電極CEを2つの端子とし、副画素電極PEa/PEbと共通電極CEの間の液晶層3は誘電体として機能する。一対の副画素電極PEa、PEbは互いに分離されており、1つの画素電極PEを構成する。共通電極CEは上部表示板200の前面に形成されていて共通電圧Vcomの印加を受ける。液晶層3は負の誘電率異方性を有し、液晶層3の液晶分子は電場がない状態でその長軸が2つの表示板の表面に対して垂直または水平をなすように配向されていてもよい。

階調電圧生成部800は画素PXの透過率と関する少なくとも2つの階調電圧集合(または基準階調電圧集合)を生成する。少なくとも2つの(基準)階調電圧集合は互いに異なるガンマ曲線に基づいて生成され、各(基準)階調電圧集合は共通電圧Vcomに対して正の値を有するものと負の値を有するものを含む。しかし、少なくとも2つの(基準)階調電圧集合の代わりに1つの(基準)階調電圧集合のみを生成することもできる。

信号制御部600は外部のグラフィック制御機から入力映像信号R、G、B及びその表示を制御する入力制御信号を受信する。

信号制御部600は入力映像信号R、G、Bと入力制御信号に基づいて入力映像信号R、G、Bを液晶表示板組立体300及びデータ駆動部500の動作条件に合わせて適切に処理し、ゲート制御信号CONT1及びデータ制御信号CONT2などを生成した後、ゲート制御信号CONT1をゲート駆動部400に出力して、データ制御信号CONT2と処理した映像信号DATをデータ駆動部500に出力する。出力映像信号DATは入力映像信号R、G、Bに基づいて作った正規映像データとインパルシブ駆動のためのインパルシブデータを含む。

データ制御信号CONT2は1つの束の副画素に対する映像データの伝送開始を知らせる水平同期開始信号STHと、液晶表示板組立体300にデータ信号を印加することを命令するロード信号LOAD、データクロック信号HCLK及び反転信号RVSを含む。

ゲート駆動部400は信号制御部600からのゲート制御信号CONT1によってゲートオン電圧Vonをゲート線に印加して、このゲート線に接続されたスイッチング素子を導通させる。その結果、データ線に印加されたデータ信号が導通したスイッチング素子を通じて当該副画素PXa、PXbに印加される。

1水平周期(“1H”とも言う)を単位としてこのような過程を繰り返すことによって、全ての副画素PXa、PXbにデータ電圧Vdを印加して1つのフレームの正規映像及びインパルシブ映像を表示する。

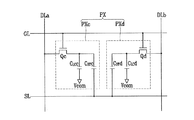

図9は本発明の他の実施例による液晶表示装置の1つの画素に対する等価回路図である。

各画素PXは一対の副画素PXa、PXbを含み、各副画素PXa/PXbは各々当該ゲート線GLa/GLb及びデータ線DLに接続されているスイッチング素子Qa/Qbと、これに接続された液晶キャパシタCLCa/CLCb、そしてスイッチング素子Qa/Qb及び維持電極線SLに接続されているストレージキャパシタCSTa/CSTbを含む。

液晶キャパシタCLCa/CLCbの補助的な役割を果たすストレージキャパシタCSTa/CSTbは、下部表示板100に設けられた維持電極線SLと画素電極PEが絶縁体を間に挟んで重合して構成され、維持電極線SLには共通電圧Vcomなどの所定の電圧が印加される。しかし、ストレージキャパシタCSTa、CSTbは副画素電極PEa、PEbが絶縁体を媒介として直上の前段ゲート線と重合するように構成してもよい。

次に、このような液晶表示装置の動作について図10及び図11を参照して詳細に説明する。

図10は図9に示した画素を含む液晶表示装置の駆動信号を示したタイミング図であり、図11は図10に示した駆動信号によって表示される画像を1つのフレームの間に表示した概略図である。

信号制御部600はM個の束の入力映像信号R、G、Bを受けて各M個の束の正規映像データNa、Nbに変換し、1つの束のインパルシブデータIを生成してM個の束の入力映像信号R、G、Bが入力される時間と実質的に同一な時間の間に(2M+1)個の束の出力映像信号DATを出力する(Mは自然数)。したがって、水平同期開始信号STHの周波数は水平同期信号Hsyncの周波数の(2M+1)/M倍である。また、出力映像信号DATが同期されるデータクロック信号HCLKの周波数は入力映像信号R、G、Bが同期されるメインクロックMCLKの周波数の(2M+1)/M倍であり得る。例えば、図10にはMを3として示した。

階調電圧生成部800で1つの階調電圧集合を作って、正規映像データNa、Nbを互いに異ならせて各画素PXa、PXbに互いに異なる電圧を印加することができる。しかし、正規映像データNa、Nbは同一でありながら2つの副画素PXa、PXbに対する階調電圧集合を別に作り、これを交互にデータ駆動部500に提供することができ、また、データ駆動部500でこれを交互に選択することによって、2つの副画素PXa、PXbに互いに異なる電圧を印加することもできる。但し、この時、2つの副画素PXa、PXbの合成ガンマ曲線が正面での基準ガンマ曲線に近く映像信号を補正したり、階調電圧集合を作ることが好ましい。例えば、正面での合成ガンマ曲線は、この液晶表示板組立体に最も適するように決められた正面での基準ガンマ曲線と一致するようにし、側面での合成ガンマ曲線は正面での基準ガンマ曲線と最も近くする。

図10に示したように、データ駆動部500は第1〜第6水平周期の間に第1〜第3番目画素行の各副画素PXa、PXbに対するデータ電圧Vdを1Hごとに順に当該データ線DLに印加する。

第7水平周期TIでゲート駆動部400はゲート信号gkb、gk+1b、gk+2bを各々k〜(k+2)番目画素行の副画素PXbに接続されたゲート線GLbに同時に印加して、このゲート線GLbに接続されたスイッチング素子Qbを導通させる。その結果、データ線DLに印加されたインパルシブデータIに対応するデータ電圧Vdが導通したたスイッチング素子Qbを通じて当該画素PXbに印加される。

このようにインパルシブ映像を2つの副画素PXa、PXbのうちのいずれか1つに表示し、他の副画素には正規映像を表示することによって、ブラリングを防止しながら輝度低下を減らすことができる。また、複数行の副画素にインパルシブ映像を同時に表示することで、インパルシブ駆動のための周波数の増加が相対的に少ないので画素電圧の充電率を高めることができる。

以下では図9に示した画素を有する液晶表示装置におけるインパルシブ映像を表示するための他の駆動方法について図12を参照して詳細に説明する。

図12は本発明の他の実施例による液晶表示装置の駆動信号の他の例を示したタイミング図である。

図12に示したように、データ駆動部500は第1〜第6水平周期の間に第1〜第3番目画素行の各副画素PXa、PXbに対する正極性のデータ電圧を1Hごとに順に当該データ線DLに印加する。

第7水平周期でゲート駆動部400はゲート信号gkb、gk+1b、gk+2bを各々k〜(k+2)番目画素行の副画素PXbに接続されたゲート線GLbに同時に印加して、このゲート線GLbに接続されたスイッチング素子Qbを導通させる。その結果、データ線DLに印加されたインパルシブデータIに対応するデータ電圧Vdが導通したスイッチング素子Qbを通じて当該画素PXbに印加される。

図10及び図11に示した液晶表示装置の多くの特徴が図12に示した液晶表示装置にも適用できる。

図13は本発明の他の実施例による液晶表示装置の駆動信号の他の例を示したタイミング図である。

信号制御部600は入力映像信号R、G、Bを副画素PXa、PXbに対する正規映像データに変換するが、インパルシブデータは別途に作らない。

データ駆動部500は、図5〜図7を参照して既に説明したように、一定の時間の間にデータ駆動部500の全ての出力端子を内部で互いに接続するチャージシェアリング機能を有している。データ駆動部500からのデータ電圧のうちのその半分が正極性で、残り半分は負極性であれば、全体データ線DLのうちの半分は正極性のデータ電圧が充電され、残り半分は負極性のデータ電圧が充電される。したがって、データ駆動部500が全ての出力端子を接続すれば、データ線DLの電荷が互いに再配列されながら、データ駆動部500の出力端子には正極性と負極性の中間値であるほぼ共通電圧Vcomのレベルを有する電荷共有電圧Iがかかる。

図13に示すように、1H区間はロード信号LOADがローレベルであるデータ電圧出力区間とハイレバルであるチャージシェアリング区間に分けられる。

ゲート駆動部400は副画素PXaに接続されているゲート線GLaにゲートオン電圧Vonを印加して、データ線DLに印加されたデータ電圧Naを当該副画素PXaに印加する。

再び、ゲート駆動部400は副画素PXbに接続されているゲート線GLbにゲートオン電圧Vonを印加してデータ線DLに印加されたデータ電圧Nbを当該副画素PXbに印加する。

これと同時に、ゲート駆動部400は所定の画素行(例えば、k番目画素行)の副画素PXbに接続されているゲート線GLbにゲートオン電圧Vonを印加して当該副画素PXbに電荷共有電圧Iを印加させる。

図13に示したように、複数の水平周期の間に1つの画素行の副画素PXbに電荷共有電圧Iを印加したり、複数の画素行の副画素PXbに電荷共有電圧Iを同時に印加したりすることができる。その結果、電荷共有区間が短くても電荷共有電圧Iを副画素PXbに十分に充電することができる。

このように本実施例によれば、別途のインパルシブデータを生成せずデータ駆動部500の出力端子で電荷共有を通じてインパルシブ映像のための電圧を供給するので、信号制御部600及びデータ駆動部500の動作が簡単で、階調電圧生成部800が別途の階調電圧集合を作る必要がない。また、データ電圧の極性が行反転または点反転である場合、データ線DLが共通電圧Vonレベルに十分に充電されているので、画素電圧の充電率も高めることができる。

以下では図8に示した2つの副画素が互いに同一の時間に互いに異なるデータ線を通じて別個のデータ電圧の印加を受ける本発明の他の実施例による液晶表示装置について図14を参照して詳細に説明する。

図14に示すように、本実施例による液晶表示装置は複数のゲート線GL、複数対のデータ線DLa、DLb及び複数の維持電極線SLを含む信号線と、これに接続された複数の画素PXを含む。

各スイッチング素子Qc/Qdもまた、下部表示板100に備えられている薄膜トランジスタなどの3端子素子で、その制御端子はゲート線GLと接続されており、入力端子はデータ線DLa/DLbと接続されており、出力端子は液晶キャパシタCLCc/CLCd及びストレージキャパシタCSTc/CSTdと接続されている。

次に、このような液晶表示装置の動作に対して図15を参照して詳細に説明する。

図15は図14に示した画素を含む液晶表示装置の駆動信号を示したタイミング図である。

階調電圧生成部800で1つの階調電圧集合を作って、正規映像データNa、Nbを互いに異ならせて各画素PXa、PXbに互いに異なる電圧を印加することができる。2つの副画素PXa、PXbの合成ガンマ曲線が正面での基準ガンマ曲線に近く映像信号を補正したり、階調電圧集合を作ったりすることが好ましい。例えば、正面での合成ガンマ曲線は、この液晶表示板組立体に最も適するように決められた正面での基準ガンマ曲線と一致させ、側面での合成ガンマ曲線が正面での基準ガンマ曲線と最も近くなるようにする。

ゲート駆動部400は第1番目画素行の副画素PXa、PXbに接続されているゲート線GLにゲート信号g1を印加して、このゲート線GLに接続されているスイッチング素子Qa、Qbを同時に導通させる。その結果、データ線DLa、DLbに各々印加されているデータ電圧Vda、Vdbが導通したスイッチング素子Qa、Qbを通じて当該副画素PXa、PXbに各々印加される。

ゲート駆動部400はk番目画素行の副画素PXa、PXbに接続されているゲート線GLにゲート信号gkを印加して、このゲート線GLに接続されているスイッチング素子Qa、Qbを同時に導通させる。その結果、データ線DLa、DLbに各々印加されているデータ電圧Vda、Vdbが導通したスイッチング素子Qa、Qbを通じて当該副画素PXa、PXbに各々印加される。

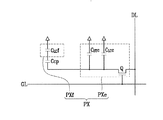

以下では図8に示した2つの副画素のうちの1つの副画素のみスイッチング素子を通じてデータ電圧の印加を受けて、他の1つの副画素は容量性結合されている本発明の他の実施例による液晶表示装置について図16を参照して詳細に説明する。

図16に示すように、本実施例による液晶表示装置は複数のゲート線GLと複数のデータ線DLを含む信号線と、これに接続されている複数の画素PXを含む。

各画素PXは一対の第1及び第2副画素PXe、PXfと2つの副画素PXe、PXfとの間に接続されている結合キャパシタCcpを含む。

スイッチング素子Qはまた下部表示板100に設けられている薄膜トランジスタなどの3端子素子で、その制御端子はゲート線GLと接続されており、入力端子はデータ線DLと接続されており、出力端子は液晶キャパシタCLCe、ストレージキャパシタCSTe及び結合キャパシタCcpと接続されている。

ストレージキャパシタCSTeに共通電圧Vcomが印加され、キャパシタCLCe、CSTe、CLCf、Ccpと、その静電容量を同一図面符号で示すと、第1液晶キャパシタCLCeに充電された電圧Veと第2液晶キャパシタCLCfに充電された電圧Vfは次のような関係を有する。

Ccp/(Ccp+CLCf)の値が1より小さいために第2液晶キャパシタCLCfに充電された電圧Vfは第1液晶キャパシタCLCeに充電された電圧Veに比べて常に小さい。この関係はストレージキャパシタCSTeに印加された電圧が共通電圧Vcomでなくても同様に成立する。

次に、このような液晶表示装置の動作について図17を参照して詳細に説明する。

図17は図16に示した画素を含む液晶表示装置の駆動信号を示したタイミング図である。

データ駆動部500は1つの画素行の出力映像信号DATを受信し、各出力映像信号DATに対応する階調電圧を選択することによって出力映像信号DATをアナログデータ電圧Vdに変換した後、これを当該データ線DLに印加する。

ゲート駆動部400は第1番目画素行のゲート線GLにゲート信号g1を印加して、このゲート線GLに接続されているスイッチング素子Qを導通させる。その結果、データ線DLに印加されているデータ電圧Vdが導通したスイッチング素子Qを通じて当該副画素PXaに印加される。

ゲート駆動部400はk番目画素行のゲート線GLにゲート信号gkを印加して、このゲート線GLに接続されているスイッチング素子Qを導通させる。その結果、データ線DLに印加されているデータ電圧Vdが導通したスイッチング素子Qを通じて当該副画素PXaに印加される。

本発明によれば、複数の画素行にインパルシブ映像を同時に表示することによってインパルシブ映像を表示するための駆動時間を相対的に減らすことができるので、画素電圧の充電率を高めることができ、その結果、充電率不足によるフリッカー発生を最小化することができる。また、インパルシブ映像を1つの副画素に表示し、他の副画素に正規映像を表示することによってブラリングを防止しながら、輝度低下を減らすことができる。

100 下部表示板

191 画素電極

200 上部表示板

230、CF 色フィルター

270 共通電極

300 液晶表示板組立体

400 ゲート駆動部

500 データ駆動部

510 シフトレジスター部

520 ラッチ

530 デジタル−アナログ変換機

540 バッファー

550 チャージシェアリング部

600 信号制御部

800 階調電圧生成部

Gi ゲート線

Dj データ線

CLC 液晶キャパシタ

CST ストレージキャパシタ

CE 共通電極

CONT1 ゲート制御信号

CONT2 データ制御信号

CPV ゲートクロック信号

CR、CS キャリー信号

DAT 映像信号

DE データイネーブル信号

DOUT データ線の電圧

HCLK データクロック信号

Hsync 水平同期信号

I インパルシブデータ電圧

LOAD ロード信号

MCLK メインクロック信号

N 正規映像データ電圧

Na、Nb 正規映像データ

OE 出力イネーブル信号

OIE インパルシブデータ用波形

OEN 正規映像データ用波形

P1 正規映像データ用パルス

P2インパルシブデータ用パルス

PE 画素電極

PEa、PEb 副画素電極

PX 画素

PXa、PXb 副画素

Q スイッチング素子

RVS 反転信号

SL 維持電極線

STV 走査開始信号

Vcom 共通電圧

Vd アナログデータ電圧

Ve 第1液晶キャパシターの電圧

Vf 第2液晶キャパシターの電圧

Vg ゲート信号

Vgm 階調電圧

Von ゲートオン電圧

Voff ゲートオフ電圧

Vsync 垂直同期信号

Claims (10)

- ゲートオン電圧を伝達する複数のゲート線と、

第1及び第2正規映像データ電圧とインパルシブデータ電圧を伝達する複数のデータ線と、

前記ゲート線及び前記データ線に接続されており、第1及び第2副画素電極を含む複数の画素と、

前記ゲート線に接続されて前記ゲートオン電圧を印加するゲート駆動部と、

前記データ線に接続されて前記第1及び第2正規映像データ電圧と前記インパルシブデータ電圧を印加するデータ駆動部と、

を含み、

前記第1副画素電極と前記第2副画素電極に各々印加される前記第1及び第2正規映像データ電圧は1つの映像情報から得られて互いに異なり、

前記インパルシブデータ電圧は、前記第1及び第2副画素電極のうちのいずれか1つに1フレームに1回ずつ印加され、

前記インパルシブデータ電圧は、前記インパルシブデータ電圧が印加される副画素電極に関する正規映像データ電圧以下である液晶表示装置。 - 前記第1正規映像データ電圧は前記第2正規映像データ電圧より大きく、前記第1副画素電極の面積は前記第2副画素電極の面積より小さい、請求項1に記載の液晶表示装置。

- M個の画素行において表示される映像情報を受けて、M個の画素行上に存在する前記第1副画素電極に対する第1正規映像データ及び前記M個の画素行上に存在する前記第2副画素電極に対する第2正規映像データに変換し、他のM個の画素行上に存在する前記インパルシブデータ電圧が印加される副画素電極に対する1つのインパルシブデータを生成して前記第1及び第2正規映像データ及び前記インパルシブデータを前記データ駆動部に伝送する信号制御部をさらに含み(Mは自然数)、

前記データ駆動部は、前記第1正規映像データ、前記第2正規映像データ、及び前記インパルシブデータを、前記第1及び第2正規映像データ電圧と前記インパルシブデータ電圧に変換し、変換した前記第1及び第2正規映像データ電圧と前記インパルシブデータ電圧を印加する、請求項1に記載の液晶表示装置。 - 前記第1及び第2副画素電極に各々接続されている第1及び第2スイッチング素子をさらに含み、

前記ゲート線は前記第1及び第2スイッチング素子に各々接続されている第1及び第2ゲート線を含む、請求項1に記載の液晶表示装置。 - 前記第1及び第2副画素電極に各々接続されている第1及び第2スイッチング素子をさらに含み、

前記データ線は前記第1及び第2スイッチング素子に各々接続されている第1及び第2データ線を含む、請求項1に記載の液晶表示装置。 - 第1及び第2副画素電極を含む複数の画素を含む液晶表示装置の駆動方法であって、

前記第1及び第2副画素電極に第1及び第2正規映像データ電圧を各々印加する段階と、

前記第1及び第2副画素電極のうちのいずれか1つにインパルシブデータ電圧を1フレームに1回ずつ印加する段階と、

を含み、前記第1及び第2正規映像データ電圧は、1つの映像情報から得られるとともに互いに異なり、

前記インパルシブデータ電圧は、前記インパルシブデータ電圧が印加される副画素電極に関する正規映像データ電圧以下であることを特徴とする液晶表示装置の駆動方法。 - M個の画素行において表示される映像情報を受けて、M個の画素行上に存在する前記第1副画素電極に対する第1正規映像データ及び前記M個の画素行上に存在する前記第2副画素電極に対する第2正規映像データに変換し、他のM個の画素行上に存在する前記インパルシブデータ電圧が印加される副画素電極に対する1つのインパルシブデータを生成する段階と、

前記第1及び第2正規映像データと前記インパルシブデータを前記第1及び第2正規映像データ電圧と前記インパルシブデータ電圧に各々変換する段階と、

をさらに含み(Mは自然数)、

前記第1及び第2正規映像データ電圧を各々印加する段階は、前記変換された前記第1及び第2正規映像データ電圧を印加し、

前記インパルシブデータ電圧を1フレームに1回ずつ印加する段階は、前記変換された前記インパルシブデータ電圧を印加する、

請求項6に記載の液晶表示装置の駆動方法。 - 前記第1及び第2正規映像データ電圧を各々印加する段階は、

互いに異なる第1及び第2階調電圧集合を生成する段階と、

前記第1及び第2階調電圧集合から前記第1及び第2正規映像データ電圧を各々選択する段階と、

を含む、請求項6に記載の液晶表示装置の駆動方法。 - 前記第1及び第2正規映像データ電圧を各々印加する段階は、M個の画素行上に存在する第1及び第2副画素電極の各副画素電極に、前記各副画素電極に関する第1又は第2正規映像データ電圧を交互であって順に印加する第1の印加段階を含み、

前記インパルシブデータ電圧を1フレームに1回ずつ印加する段階は、前記第1の印加段階に続いて、別のM個の画素行上に存在する第2副画素電極に前記インパルシブデータ電圧を印加する第2の印加段階を含む(Mは自然数)、請求項6に記載の液晶表示装置の駆動方法。 - 前記第1及び第2正規映像データ電圧を各々印加する段階は、第1の画素行上に存在する第1副画素電極に当該副画素電極に関する第1正規データ電圧を、前記第1の画素行上に存在する第2副画素電極に当該副画素電極に関する第2正規映像データ電圧を順に印加する第3の印加段階を含み、

前記インパルシブデータ電圧を1フレームに1回ずつ印加する段階は、前記第3の印加段階に続いて、第1の画素行と異なる第2の画素行上に存在する第1副画素電極に当該副画素電極に関する第1正規映像データ電圧を、前記第2の画素行上に存在する第2副画素電極に前記インパルシブデータ電圧を順に印加する第4の印加段階を含む、請求項6に記載の液晶表示装置の駆動方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR10-2005-0064781 | 2005-07-18 | ||

| KR1020050064781A KR101152123B1 (ko) | 2005-07-18 | 2005-07-18 | 액정 표시 장치 및 그 구동 방법 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007025691A JP2007025691A (ja) | 2007-02-01 |

| JP2007025691A5 JP2007025691A5 (ja) | 2009-07-02 |

| JP4891682B2 true JP4891682B2 (ja) | 2012-03-07 |

Family

ID=37074137

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006195304A Expired - Fee Related JP4891682B2 (ja) | 2005-07-18 | 2006-07-18 | 液晶表示装置及びその駆動方法 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US20070013643A1 (ja) |

| EP (1) | EP1746569B1 (ja) |

| JP (1) | JP4891682B2 (ja) |

| KR (1) | KR101152123B1 (ja) |

| CN (1) | CN1901020B (ja) |

| AT (1) | ATE400866T1 (ja) |

| DE (1) | DE602006001697D1 (ja) |

| TW (1) | TWI417825B (ja) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101237208B1 (ko) * | 2005-08-02 | 2013-02-25 | 엘지디스플레이 주식회사 | 데이터 공급 방법, 액정표시장치 및 그 구동 방법 |

| US8259046B2 (en) * | 2006-07-14 | 2012-09-04 | Sharp Kabushiki Kaisha | Active matrix substrate and display device having the same |

| KR101369883B1 (ko) * | 2007-02-26 | 2014-03-25 | 삼성디스플레이 주식회사 | 액정 표시 장치 |

| KR101340999B1 (ko) * | 2007-04-24 | 2013-12-13 | 엘지디스플레이 주식회사 | 액정표시장치 및 이의 구동방법 |

| TWI405014B (zh) * | 2007-07-26 | 2013-08-11 | Au Optronics Corp | 液晶顯示器及其驅動方法 |

| CN101561601B (zh) * | 2008-04-14 | 2012-05-30 | 北京京东方光电科技有限公司 | 液晶显示器的驱动方法及驱动装置 |

| CN101581858B (zh) * | 2008-05-16 | 2012-02-08 | 群康科技(深圳)有限公司 | 垂直配向型液晶显示装置及其驱动方法 |

| TWI408649B (zh) * | 2008-05-23 | 2013-09-11 | Innolux Corp | 垂直配向型液晶顯示裝置及其驅動方法 |

| US8432344B2 (en) * | 2008-05-27 | 2013-04-30 | Samsung Display Co., Ltd. | Liquid crystal display |

| KR101503660B1 (ko) * | 2009-01-16 | 2015-03-18 | 삼성디스플레이 주식회사 | 표시패널, 이의 구동 방법 및 이를 수행하기 위한 표시장치 |

| TWI406248B (zh) * | 2009-06-02 | 2013-08-21 | Sitronix Technology Corp | 液晶點反轉之驅動方法 |

| TWI416493B (zh) * | 2009-12-07 | 2013-11-21 | Innolux Corp | 液晶顯示器 |

| US8547418B2 (en) * | 2010-07-19 | 2013-10-01 | Broadcom Corporation | Method and system for processing and displaying video in three dimensions using a liquid crystal display |

| TWI524324B (zh) * | 2014-01-28 | 2016-03-01 | 友達光電股份有限公司 | 液晶顯示器 |

| CN106023918B (zh) * | 2016-06-30 | 2018-10-30 | 深圳市华星光电技术有限公司 | 液晶显示器及其数据驱动器 |

Family Cites Families (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0497126A (ja) * | 1990-08-16 | 1992-03-30 | Internatl Business Mach Corp <Ibm> | 液晶表示装置 |

| EP0715753A1 (en) * | 1994-06-09 | 1996-06-12 | Koninklijke Philips Electronics N.V. | Display device |

| JP3160493B2 (ja) * | 1995-06-19 | 2001-04-25 | キヤノン株式会社 | 液晶表示装置 |

| US6061045A (en) | 1995-06-19 | 2000-05-09 | Canon Kabushiki Kaisha | Liquid crystal display apparatus and method of driving same |

| JP3229250B2 (ja) * | 1997-09-12 | 2001-11-19 | インターナショナル・ビジネス・マシーンズ・コーポレーション | 液晶表示装置における画像表示方法及び液晶表示装置 |

| JP3734629B2 (ja) * | 1998-10-15 | 2006-01-11 | インターナショナル・ビジネス・マシーンズ・コーポレーション | 表示装置 |

| JP4519251B2 (ja) * | 1999-10-13 | 2010-08-04 | シャープ株式会社 | 液晶表示装置およびその制御方法 |

| JP2002229505A (ja) * | 2001-01-31 | 2002-08-16 | Nec Corp | 表示装置 |

| JP2003215535A (ja) * | 2001-03-30 | 2003-07-30 | Matsushita Electric Ind Co Ltd | 液晶表示装置 |

| JP4602608B2 (ja) * | 2001-08-28 | 2010-12-22 | 株式会社日立製作所 | 表示装置 |

| US7161576B2 (en) * | 2001-07-23 | 2007-01-09 | Hitachi, Ltd. | Matrix-type display device |

| JP3913040B2 (ja) * | 2001-11-08 | 2007-05-09 | 東芝松下ディスプレイテクノロジー株式会社 | 液晶表示装置の駆動方法および液晶表示装置 |

| JP3653506B2 (ja) * | 2002-03-20 | 2005-05-25 | 株式会社日立製作所 | 表示装置及びその駆動方法 |

| JP2003280600A (ja) * | 2002-03-20 | 2003-10-02 | Hitachi Ltd | 表示装置およびその駆動方法 |

| JP4143323B2 (ja) * | 2002-04-15 | 2008-09-03 | Nec液晶テクノロジー株式会社 | 液晶表示装置 |

| JP4342200B2 (ja) * | 2002-06-06 | 2009-10-14 | シャープ株式会社 | 液晶表示装置 |

| JP2004012872A (ja) * | 2002-06-07 | 2004-01-15 | Nec Electronics Corp | 表示装置及びその駆動方法 |

| KR100895303B1 (ko) * | 2002-07-05 | 2009-05-07 | 삼성전자주식회사 | 액정 표시 장치 및 그 구동 방법 |

| EP1600928A4 (en) * | 2003-02-03 | 2006-10-11 | Sharp Kk | LIQUID CRYSTAL DISPLAY |

| KR100997974B1 (ko) * | 2003-12-03 | 2010-12-02 | 삼성전자주식회사 | 액정 표시 장치 및 그 구동 방법 |

| JP4265788B2 (ja) * | 2003-12-05 | 2009-05-20 | シャープ株式会社 | 液晶表示装置 |

| JP4292068B2 (ja) * | 2003-12-11 | 2009-07-08 | 株式会社日立ハイテクノロジーズ | 走査電子顕微鏡 |

| JP4191136B2 (ja) * | 2004-03-15 | 2008-12-03 | シャープ株式会社 | 液晶表示装置およびその駆動方法 |

| JP4642031B2 (ja) * | 2004-11-05 | 2011-03-02 | シャープ株式会社 | 液晶表示装置およびその駆動方法 |

-

2005

- 2005-07-18 KR KR1020050064781A patent/KR101152123B1/ko active IP Right Grant

-

2006

- 2006-07-07 TW TW095124832A patent/TWI417825B/zh not_active IP Right Cessation

- 2006-07-11 EP EP06116944A patent/EP1746569B1/en not_active Not-in-force

- 2006-07-11 DE DE602006001697T patent/DE602006001697D1/de active Active

- 2006-07-11 AT AT06116944T patent/ATE400866T1/de not_active IP Right Cessation

- 2006-07-17 CN CN2006100993310A patent/CN1901020B/zh not_active Expired - Fee Related

- 2006-07-18 JP JP2006195304A patent/JP4891682B2/ja not_active Expired - Fee Related

- 2006-07-18 US US11/489,296 patent/US20070013643A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| CN1901020A (zh) | 2007-01-24 |

| TWI417825B (zh) | 2013-12-01 |

| DE602006001697D1 (de) | 2008-08-21 |

| EP1746569A1 (en) | 2007-01-24 |

| US20070013643A1 (en) | 2007-01-18 |

| EP1746569B1 (en) | 2008-07-09 |

| KR101152123B1 (ko) | 2012-06-15 |

| KR20070010304A (ko) | 2007-01-24 |

| ATE400866T1 (de) | 2008-07-15 |

| JP2007025691A (ja) | 2007-02-01 |

| CN1901020B (zh) | 2010-09-01 |

| TW200710790A (en) | 2007-03-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4891682B2 (ja) | 液晶表示装置及びその駆動方法 | |

| JP5419321B2 (ja) | 表示装置 | |

| TWI447687B (zh) | 液晶顯示器 | |

| US8174515B2 (en) | Method of driving a display panel and display apparatus for performing the method | |

| CN101334972B (zh) | 液晶显示器及其驱动方法 | |

| KR101318367B1 (ko) | 표시장치 및 이의 구동방법 | |

| KR20060089829A (ko) | 표시 장치 및 그 구동 방법 | |

| KR20110017751A (ko) | 액정표시장치와 그 도트 인버젼 제어방법 | |

| US20210217373A1 (en) | Method for driving pixel matrix and display device | |

| JP5302492B2 (ja) | インパルシブ駆動液晶表示装置及びその駆動方法 | |

| WO2010125716A1 (ja) | 表示装置および表示装置の駆動方法 | |

| KR20070063168A (ko) | 액정 표시 장치 및 그 구동 방법 | |

| KR20060082104A (ko) | 액정 표시 장치 및 그 구동 방법 | |

| KR100956343B1 (ko) | 액정 표시 장치 및 그 구동 방법 | |

| JP2007034294A (ja) | 液晶表示装置 | |

| KR20070010524A (ko) | 액정 표시 장치 및 그 구동 방법 | |

| KR101359924B1 (ko) | 표시 장치 | |

| KR102169963B1 (ko) | 액정표시장치 및 이의 도트 인버전 제어방법 | |

| KR20070027374A (ko) | 표시 장치의 구동 장치 | |

| KR20080046979A (ko) | 액정 표시 장치 | |

| KR20080007785A (ko) | 액정 표시 장치 | |

| KR20080097796A (ko) | 액정 표시 장치 | |

| KR20070101502A (ko) | 액정 표시 장치 | |

| KR20070070639A (ko) | 표시 장치의 구동 장치 | |

| KR20070025251A (ko) | 표시 장치의 구동 장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090519 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090519 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100427 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110927 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111116 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20111116 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20111206 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111216 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4891682 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141222 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141222 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141222 Year of fee payment: 3 |

|

| R371 | Transfer withdrawn |

Free format text: JAPANESE INTERMEDIATE CODE: R371 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |