JP4869552B2 - 符号乗算処理を実行する方法及び装置 - Google Patents

符号乗算処理を実行する方法及び装置 Download PDFInfo

- Publication number

- JP4869552B2 JP4869552B2 JP2003425712A JP2003425712A JP4869552B2 JP 4869552 B2 JP4869552 B2 JP 4869552B2 JP 2003425712 A JP2003425712 A JP 2003425712A JP 2003425712 A JP2003425712 A JP 2003425712A JP 4869552 B2 JP4869552 B2 JP 4869552B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- operand

- instruction

- packed

- sign

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F7/00—Methods or arrangements for processing data by operating upon the order or content of the data handled

- G06F7/38—Methods or arrangements for performing computations using exclusively denominational number representation, e.g. using binary, ternary, decimal representation

- G06F7/48—Methods or arrangements for performing computations using exclusively denominational number representation, e.g. using binary, ternary, decimal representation using non-contact-making devices, e.g. tube, solid state device; using unspecified devices

- G06F7/52—Multiplying; Dividing

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/3017—Runtime instruction translation, e.g. macros

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F15/00—Digital computers in general; Data processing equipment in general

- G06F15/76—Architectures of general purpose stored program computers

- G06F15/80—Architectures of general purpose stored program computers comprising an array of processing units with common control, e.g. single instruction multiple data processors

- G06F15/8007—Architectures of general purpose stored program computers comprising an array of processing units with common control, e.g. single instruction multiple data processors single instruction multiple data [SIMD] multiprocessors

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F7/00—Methods or arrangements for processing data by operating upon the order or content of the data handled

- G06F7/38—Methods or arrangements for performing computations using exclusively denominational number representation, e.g. using binary, ternary, decimal representation

- G06F7/48—Methods or arrangements for performing computations using exclusively denominational number representation, e.g. using binary, ternary, decimal representation using non-contact-making devices, e.g. tube, solid state device; using unspecified devices

- G06F7/52—Multiplying; Dividing

- G06F7/523—Multiplying only

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F7/00—Methods or arrangements for processing data by operating upon the order or content of the data handled

- G06F7/38—Methods or arrangements for performing computations using exclusively denominational number representation, e.g. using binary, ternary, decimal representation

- G06F7/48—Methods or arrangements for performing computations using exclusively denominational number representation, e.g. using binary, ternary, decimal representation using non-contact-making devices, e.g. tube, solid state device; using unspecified devices

- G06F7/544—Methods or arrangements for performing computations using exclusively denominational number representation, e.g. using binary, ternary, decimal representation using non-contact-making devices, e.g. tube, solid state device; using unspecified devices for evaluating functions by calculation

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30003—Arrangements for executing specific machine instructions

- G06F9/30007—Arrangements for executing specific machine instructions to perform operations on data operands

- G06F9/3001—Arithmetic instructions

- G06F9/30014—Arithmetic instructions with variable precision

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30003—Arrangements for executing specific machine instructions

- G06F9/30007—Arrangements for executing specific machine instructions to perform operations on data operands

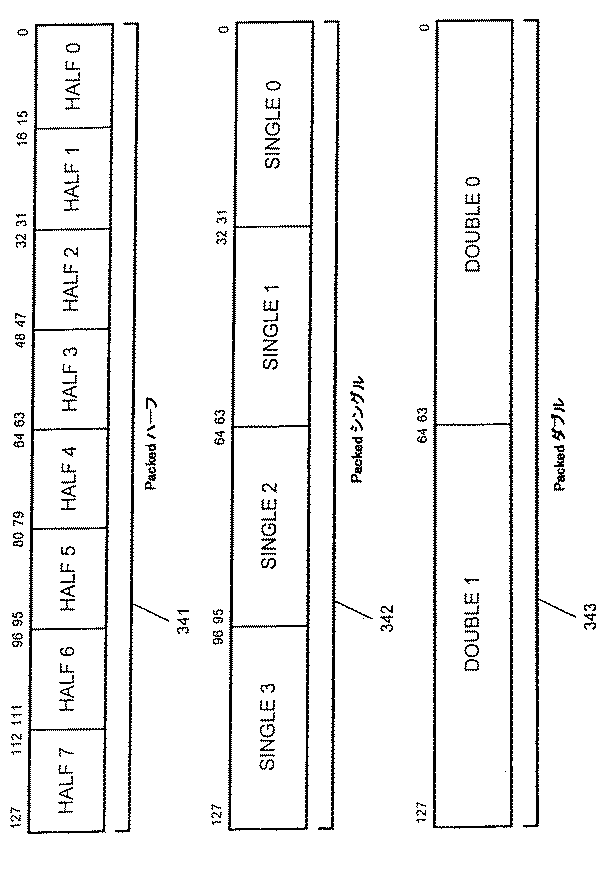

- G06F9/30036—Instructions to perform operations on packed data, e.g. vector, tile or matrix operations

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3885—Concurrent instruction execution, e.g. pipeline or look ahead using a plurality of independent parallel functional units

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3885—Concurrent instruction execution, e.g. pipeline or look ahead using a plurality of independent parallel functional units

- G06F9/3887—Concurrent instruction execution, e.g. pipeline or look ahead using a plurality of independent parallel functional units controlled by a single instruction for multiple data lanes [SIMD]

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2207/00—Indexing scheme relating to methods or arrangements for processing data by operating upon the order or content of the data handled

- G06F2207/38—Indexing scheme relating to groups G06F7/38 - G06F7/575

- G06F2207/3804—Details

- G06F2207/3808—Details concerning the type of numbers or the way they are handled

- G06F2207/3812—Devices capable of handling different types of numbers

- G06F2207/382—Reconfigurable for different fixed word lengths

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2207/00—Indexing scheme relating to methods or arrangements for processing data by operating upon the order or content of the data handled

- G06F2207/38—Indexing scheme relating to groups G06F7/38 - G06F7/575

- G06F2207/3804—Details

- G06F2207/3808—Details concerning the type of numbers or the way they are handled

- G06F2207/3828—Multigauge devices, i.e. capable of handling packed numbers without unpacking them

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- Software Systems (AREA)

- General Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- Mathematical Analysis (AREA)

- Computational Mathematics (AREA)

- Mathematical Optimization (AREA)

- Pure & Applied Mathematics (AREA)

- Computing Systems (AREA)

- Mathematical Physics (AREA)

- Computer Hardware Design (AREA)

- Executing Machine-Instructions (AREA)

- Advance Control (AREA)

- Complex Calculations (AREA)

Description

(Compact Flash)カードコントロール149、液晶(LCD)コントロール150、DMA(Direct Memory Access)コントローラ151、及び代替バスマスタインタフェース152を含む他の様々なシステム装置と通信するためのバス141に接続される。一実施例では、データ処理システム140はまた、I/Oバス153を介し様々なI/O装置と通信するためのI/Oブリッジ154を備える。このようなI/O装置は、以下に限定されるものではないが、例えば、UART(Universal Asynchronous Receiver/Transmitter)155、USB156、ブルートゥース無線UART157、及びI/O拡張インタフェース158から構成されてもよい。

ここで、アレイB1014とC1022の補正係数が、アップダウンランプ(updown ramp)

d1=SIGN(d)×(MAX(0, ABS(d)−MAX(0, 2×(ABS(d)−strength))))

により計算される。

d2=clipd1((A−D)/4, d1/2)

により計算される。

B’=clip(B+d1) C’=clip(C−d1)

補正される。

A’=A−d2 D’=D+d2

補正される。

最大値=MAX(V1 V2 V3 V4 V5 V6 V7 V8)

最小値=MIN(V1 V2 V3 V4 V5 V6 V7 V8)

特徴付けされる。

a3,0=(2×V3−5×V4+5×V5−2×V6)/8

a3,1=(2×V1−5×V2+5×V3−2×V4)/8

a3,2=(2×V5−5×V6+5×V7−2×V8)/8

a3,0’=SIGN(a3,0)×MIN(ABS(a3,0), ABS(a3,1), ABS(a3,2))

d=CLIP(5×(a3,0’−a3,0)/8, 0, ((V4−V5)/2×δ(ABS(a3,0)<量子化係数))

計算される。ただし、δ()は、真の場合には1、偽の場合には0と評価する。

m<1の場合、ABS(V1−V0)<QPのとき、pm=V0とし、そうでないときpm=V1とする。

102、166、200 プロセッサ

104、167 キャッシュ

106、145、164 レジスタファイル

108、142、162 実行ユニット

109、143,163 命令セット

110 プロセッサバス

112 グラフィックス/ビデオカード

114 AGPインターコネクト

116 メモリコントローラハブ(MCH)

118 メモリインタフェース

120 メモリ

122 専用ハブインタフェースバス

124 データ記憶装置

126 無線送信機

128 フラッシュBIOS

130 I/Oコントローラハブ(ICH)

134 ネットワークコントローラ

141 バス

144、165 デコーダ

146 SDRAMコントロール

147 SRAMコントロール

148 バーストフラッシュメモリインタフェース

149 PCMCIA/CFカードコントロール

150 LCDコントロール

151 DMAコントロール

152 代替バスマスタインタフェース

153 I/Oバス

154 I/Oブリッジ

155 UART

156 USB

157 ブルートゥースUART

158 I/O拡張インタフェース

159 処理コア

161 SIMDコプロセッサ

168 I/Oシステム

169 無線インタフェース

201 フロントエンド

202 高速スケジューラ

203 アウト・オブ・オーダーエンジン

204 低速/通常浮動小数点スケジューラ

206 シンプル浮動小数点スケジューラ

211 実行ブロック

212、214 アドレス生成ユニット(AGU)

216、218 高速ALU

220 低速ALU

222 浮動小数点ALU

224 浮動小数点移動ユニット

226 命令プリフェッチャ

228 命令デコーダ

230 トレースキャッシュ

232 マイクロコードROM

234 uopキュー

430 符号計算論理

600、650 回路

606、608 2−入力(2:1)マルチプレクサ(mux)

614 加算器

618 3−入力(3:1)マルチプレクサ(mux)

624 ゼロ検出回路

628 論理NORゲート

920 絶対値計算論理

Claims (4)

- 格納領域と、

該格納領域に接続される実行リソースと、

を有するプロセッサを含む装置であって、

前記実行リソースは、第1オペランドと第2オペランドとを含む第1命令を実行し、該第1命令に応答して、前記第2オペランドが正の値である場合には前記第1オペランドの値を、前記第2オペランドがゼロの値である場合にはゼロの値を、前記第2オペランドが負の値である場合には前記第1オペランドの反対の符号の値を有する結果を前記格納領域に格納することを特徴とする装置。 - Packedデータ要素を格納できるレジスタファイルと、

前記レジスタファイルに接続され、複数のPackedデータ命令に応答して前記レジスタファイルに値を格納する実行ユニットと、

を有するプロセッサであって、

前記実行ユニットは、複数の結果データ要素から構成される結果を前記レジスタファイルに格納することにより前記複数のPackedデータ命令の第1命令に応答し、

前記複数の結果データ要素の各々は、複数の第1ソースデータ要素と複数の第2ソースデータ要素の各自の値に対して、前記複数の第2ソースデータ要素の対応する第2ソースデータ要素の「1」,「0」又は「−1」の符号の値と乗算された前記複数の第1ソースデータ要素の対応する第1ソースデータ要素に等しいことを特徴とするプロセッサ。 - フロントエンドによって、第1オペランド符号と第1オペランド量を有する第1オペランドと第2オペランド符号と第2オペランド量を有する第2オペランドとを特定する命令をフェッチするステップと、

実行ユニットを使用して、入力された前記第2オペランドが正であるか判断し、そのとき前記命令に応答して前記第1オペランドを結果として格納し、前記第2オペランドが負であるか判断し、そのとき前記第1オペランドと「−1」との積に等しい値を前記命令の結果として格納し、前記第2オペランドがゼロであるか判断し、そのときゼロを前記命令の結果として格納するステップと、

を有することを特徴とする方法。 - 第1Packedデータ命令と、複数の第1ソースデータ要素から構成される第1Packedデータと、複数の第2ソースデータ要素から構成される第2Packedデータとを格納するメモリと、

前記第1Packedデータ命令を実行し、複数の結果Packedデータ要素から構成される結果Packedデータをプロセッサ格納領域に格納するプロセッサと、

を有するシステムであって、

前記複数の第2ソースデータ要素の非ゼロ要素に対応する前記複数の結果Packedデータ要素のそれぞれは、前記複数の第1ソースデータ要素と前記複数の第2ソースデータ要素との対応する要素の双方の符号により決定される符号と、前記複数の第2ソースデータ要素の対応する要素のすべての非ゼロの値に対する前記複数の第1Packedデータ要素の対応する要素の大きさとを有することを特徴とするシステム。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US610929 | 2003-06-30 | ||

| US10/610,929 US7539714B2 (en) | 2003-06-30 | 2003-06-30 | Method, apparatus, and instruction for performing a sign operation that multiplies |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005025719A JP2005025719A (ja) | 2005-01-27 |

| JP2005025719A5 JP2005025719A5 (ja) | 2007-02-01 |

| JP4869552B2 true JP4869552B2 (ja) | 2012-02-08 |

Family

ID=33452633

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003425712A Expired - Fee Related JP4869552B2 (ja) | 2003-06-30 | 2003-12-22 | 符号乗算処理を実行する方法及び装置 |

Country Status (10)

| Country | Link |

|---|---|

| US (1) | US7539714B2 (ja) |

| EP (2) | EP2284694B1 (ja) |

| JP (1) | JP4869552B2 (ja) |

| KR (1) | KR100841131B1 (ja) |

| CN (1) | CN1577249B (ja) |

| BR (2) | BR0306094A (ja) |

| MX (1) | MXPA03011899A (ja) |

| RU (1) | RU2275677C2 (ja) |

| SG (1) | SG144700A1 (ja) |

| TW (1) | TWI305882B (ja) |

Families Citing this family (33)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7424501B2 (en) | 2003-06-30 | 2008-09-09 | Intel Corporation | Nonlinear filtering and deblocking applications utilizing SIMD sign and absolute value operations |

| CN101421935B (zh) * | 2004-09-20 | 2011-05-25 | Divx公司 | 视频去块滤波器 |

| US7475103B2 (en) | 2005-03-17 | 2009-01-06 | Qualcomm Incorporated | Efficient check node message transform approximation for LDPC decoder |

| WO2007049150A2 (en) * | 2005-09-28 | 2007-05-03 | Arc International (Uk) Limited | Architecture for microprocessor-based systems including simd processing unit and associated systems and methods |

| US20080071851A1 (en) * | 2006-09-20 | 2008-03-20 | Ronen Zohar | Instruction and logic for performing a dot-product operation |

| US9069547B2 (en) * | 2006-09-22 | 2015-06-30 | Intel Corporation | Instruction and logic for processing text strings |

| US20090113174A1 (en) * | 2007-10-31 | 2009-04-30 | Texas Instruments Incorporated | Sign Operation Instructions and Circuitry |

| US8515052B2 (en) | 2007-12-17 | 2013-08-20 | Wai Wu | Parallel signal processing system and method |

| US8041927B2 (en) * | 2008-04-16 | 2011-10-18 | Nec Corporation | Processor apparatus and method of processing multiple data by single instructions |

| WO2010047344A1 (ja) * | 2008-10-24 | 2010-04-29 | シャープ株式会社 | 表示装置および表示装置の駆動方法 |

| US9747105B2 (en) * | 2009-12-17 | 2017-08-29 | Intel Corporation | Method and apparatus for performing a shift and exclusive or operation in a single instruction |

| US9003170B2 (en) * | 2009-12-22 | 2015-04-07 | Intel Corporation | Bit range isolation instructions, methods, and apparatus |

| WO2012009540A1 (en) * | 2010-07-14 | 2012-01-19 | Ntt Docomo, Inc. | Low-complexity intra prediction for video coding |

| RU2467377C1 (ru) * | 2011-04-19 | 2012-11-20 | ОАО "Концерн "Моринформсистема-Агат" | Способ и устройство умножения чисел в коде "1 из 4" |

| RU2461867C1 (ru) * | 2011-06-23 | 2012-09-20 | Российская Федерация, от имени которой выступает Государственная корпорация по атомной энергии "Росатом" - Госкорпорация "Росатом" | Реконфигурируемый вычислительный конвейер |

| US9507593B2 (en) * | 2011-12-23 | 2016-11-29 | Intel Corporation | Instruction for element offset calculation in a multi-dimensional array |

| US9710266B2 (en) | 2012-03-15 | 2017-07-18 | International Business Machines Corporation | Instruction to compute the distance to a specified memory boundary |

| US9715383B2 (en) | 2012-03-15 | 2017-07-25 | International Business Machines Corporation | Vector find element equal instruction |

| US9459867B2 (en) | 2012-03-15 | 2016-10-04 | International Business Machines Corporation | Instruction to load data up to a specified memory boundary indicated by the instruction |

| US9459868B2 (en) | 2012-03-15 | 2016-10-04 | International Business Machines Corporation | Instruction to load data up to a dynamically determined memory boundary |

| US9501276B2 (en) * | 2012-12-31 | 2016-11-22 | Intel Corporation | Instructions and logic to vectorize conditional loops |

| US9207941B2 (en) * | 2013-03-15 | 2015-12-08 | Intel Corporation | Systems, apparatuses, and methods for reducing the number of short integer multiplications |

| CN103995475B (zh) * | 2014-05-16 | 2016-05-18 | 北京航空航天大学 | 一种柔性嵌入式被测设备模拟器 |

| US20160125263A1 (en) | 2014-11-03 | 2016-05-05 | Texas Instruments Incorporated | Method to compute sliding window block sum using instruction based selective horizontal addition in vector processor |

| US20160188341A1 (en) * | 2014-12-24 | 2016-06-30 | Elmoustapha Ould-Ahmed-Vall | Apparatus and method for fused add-add instructions |

| US10346944B2 (en) | 2017-04-09 | 2019-07-09 | Intel Corporation | Machine learning sparse computation mechanism |

| CN108733347B (zh) * | 2017-04-20 | 2021-01-29 | 杭州海康威视数字技术股份有限公司 | 一种数据处理方法及装置 |

| RU2653310C1 (ru) * | 2017-05-24 | 2018-05-07 | федеральное государственное бюджетное образовательное учреждение высшего образования "Воронежский государственный университет" (ФГБОУ ВО "ВГУ") | Устройство для умножения числа по модулю на константу |

| CN107729989B (zh) * | 2017-07-20 | 2020-12-29 | 安徽寒武纪信息科技有限公司 | 一种用于执行人工神经网络正向运算的装置及方法 |

| RU2666285C1 (ru) * | 2017-10-06 | 2018-09-06 | Федеральное государственное бюджетное образовательное учреждение высшего образования "Вятский государственный университет" (ВятГУ) | Способ организации выполнения операции умножения двух чисел в модулярно-логарифмическом формате представления с плавающей точкой на гибридных многоядерных процессорах |

| KR102704647B1 (ko) * | 2017-10-12 | 2024-09-10 | 삼성전자주식회사 | 전자 장치 및 그 제어 방법 |

| KR102894225B1 (ko) * | 2020-04-07 | 2025-12-03 | 삼성전자 주식회사 | 뉴럴 네트워크 연산 수행을 위한 뉴럴 네트워크 장치, 뉴럴 네트워크 장치의 동작 방법 및 뉴럴 네트워크 장치를 포함하는 애플리케이션 프로세서 |

| US11614920B2 (en) * | 2020-05-07 | 2023-03-28 | Meta Platforms, Inc. | Bypassing zero-value multiplications in a hardware multiplier |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR1398092A (fr) * | 1964-03-26 | 1965-05-07 | Saint Gobain | Nouveau circuit électronique de commutation |

| FR1509926A (fr) * | 1966-03-21 | 1968-01-19 | Saint Gobain Techn Nouvelles | Circuit multiplicateur scalaire |

| JPS6297060A (ja) * | 1985-10-23 | 1987-05-06 | Mitsubishi Electric Corp | デイジタルシグナルプロセツサ |

| SU1309020A1 (ru) * | 1985-12-23 | 1987-05-07 | Горьковский Исследовательский Физико-Технический Институт При Горьковском Государственном Университете Им.Н.И.Лобачевского | Устройство дл умножени |

| JPS63310023A (ja) * | 1987-06-11 | 1988-12-19 | Matsushita Electric Ind Co Ltd | 符号付固定小数点乗算装置 |

| NL9001608A (nl) * | 1990-07-16 | 1992-02-17 | Philips Nv | Ontvanger voor meerwaardige digitale signalen. |

| JPH04155503A (ja) * | 1990-10-19 | 1992-05-28 | Matsushita Electric Ind Co Ltd | ニューロ制御装置 |

| US5128890A (en) * | 1991-05-06 | 1992-07-07 | Motorola, Inc. | Apparatus for performing multiplications with reduced power and a method therefor |

| US5349545A (en) * | 1992-11-24 | 1994-09-20 | Intel Corporation | Arithmetic logic unit dequantization |

| US6023489A (en) * | 1995-05-24 | 2000-02-08 | Leica Geosystems Inc. | Method and apparatus for code synchronization in a global positioning system receiver |

| EP0847552B1 (en) * | 1995-08-31 | 2002-10-30 | Intel Corporation | An apparatus for performing multiply-add operations on packed data |

| US6038583A (en) * | 1997-10-23 | 2000-03-14 | Advanced Micro Devices, Inc. | Method and apparatus for simultaneously multiplying two or more independent pairs of operands and calculating a rounded products |

| US6490607B1 (en) * | 1998-01-28 | 2002-12-03 | Advanced Micro Devices, Inc. | Shared FP and SIMD 3D multiplier |

| US6243803B1 (en) * | 1998-03-31 | 2001-06-05 | Intel Corporation | Method and apparatus for computing a packed absolute differences with plurality of sign bits using SIMD add circuitry |

| US6351293B1 (en) * | 1998-05-18 | 2002-02-26 | Sarnoff Corporation | Decision directed phase detector |

| US6292814B1 (en) * | 1998-06-26 | 2001-09-18 | Hitachi America, Ltd. | Methods and apparatus for implementing a sign function |

| US6397240B1 (en) * | 1999-02-18 | 2002-05-28 | Agere Systems Guardian Corp. | Programmable accelerator for a programmable processor system |

-

2003

- 2003-06-30 US US10/610,929 patent/US7539714B2/en not_active Expired - Lifetime

- 2003-10-13 TW TW092128278A patent/TWI305882B/zh not_active IP Right Cessation

- 2003-12-17 SG SG200307424-2A patent/SG144700A1/en unknown

- 2003-12-18 MX MXPA03011899A patent/MXPA03011899A/es not_active Application Discontinuation

- 2003-12-22 JP JP2003425712A patent/JP4869552B2/ja not_active Expired - Fee Related

- 2003-12-25 RU RU2003137709/09A patent/RU2275677C2/ru not_active IP Right Cessation

- 2003-12-25 CN CN2003101130822A patent/CN1577249B/zh not_active Expired - Fee Related

- 2003-12-29 EP EP10184624.4A patent/EP2284694B1/en not_active Expired - Lifetime

- 2003-12-29 BR BR0306094-2A patent/BR0306094A/pt not_active IP Right Cessation

- 2003-12-29 EP EP03258226A patent/EP1496432A3/en not_active Ceased

- 2003-12-29 BR BRPI0306094-2A patent/BRPI0306094B1/pt unknown

- 2003-12-30 KR KR1020030099839A patent/KR100841131B1/ko not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20040267858A1 (en) | 2004-12-30 |

| EP2284694B1 (en) | 2013-05-15 |

| CN1577249B (zh) | 2010-04-14 |

| RU2003137709A (ru) | 2005-06-10 |

| JP2005025719A (ja) | 2005-01-27 |

| RU2275677C2 (ru) | 2006-04-27 |

| TW200500878A (en) | 2005-01-01 |

| EP1496432A3 (en) | 2007-12-12 |

| BRPI0306094B1 (pt) | 2017-06-27 |

| MXPA03011899A (es) | 2005-01-13 |

| TWI305882B (en) | 2009-02-01 |

| EP1496432A2 (en) | 2005-01-12 |

| SG144700A1 (en) | 2008-08-28 |

| US7539714B2 (en) | 2009-05-26 |

| KR20050005729A (ko) | 2005-01-14 |

| KR100841131B1 (ko) | 2008-06-24 |

| BR0306094A (pt) | 2005-05-17 |

| EP2284694A1 (en) | 2011-02-16 |

| CN1577249A (zh) | 2005-02-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4869552B2 (ja) | 符号乗算処理を実行する方法及び装置 | |

| US10474466B2 (en) | SIMD sign operation | |

| JP4480997B2 (ja) | Simd整数乗算上位丸めシフト | |

| CN107741842B (zh) | 用于执行点积运算的指令和逻辑 | |

| CN102103487B (zh) | 用于在单个指令中执行移位和异或运算的方法和装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061213 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061213 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20091102 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091110 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100210 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101026 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110126 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20111025 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111116 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141125 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |