JP4786178B2 - 薄膜層の特性を変化させるプロセス、及び前記プロセスを適用する基板 - Google Patents

薄膜層の特性を変化させるプロセス、及び前記プロセスを適用する基板 Download PDFInfo

- Publication number

- JP4786178B2 JP4786178B2 JP2004507374A JP2004507374A JP4786178B2 JP 4786178 B2 JP4786178 B2 JP 4786178B2 JP 2004507374 A JP2004507374 A JP 2004507374A JP 2004507374 A JP2004507374 A JP 2004507374A JP 4786178 B2 JP4786178 B2 JP 4786178B2

- Authority

- JP

- Japan

- Prior art keywords

- thin film

- film layer

- surface area

- support

- specific surface

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/322—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to modify their internal properties, e.g. to produce internal imperfections

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B81—MICROSTRUCTURAL TECHNOLOGY

- B81C—PROCESSES OR APPARATUS SPECIALLY ADAPTED FOR THE MANUFACTURE OR TREATMENT OF MICROSTRUCTURAL DEVICES OR SYSTEMS

- B81C1/00—Manufacture or treatment of devices or systems in or on a substrate

- B81C1/00349—Creating layers of material on a substrate

- B81C1/0038—Processes for creating layers of materials not provided for in groups B81C1/00357 - B81C1/00373

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B81—MICROSTRUCTURAL TECHNOLOGY

- B81C—PROCESSES OR APPARATUS SPECIALLY ADAPTED FOR THE MANUFACTURE OR TREATMENT OF MICROSTRUCTURAL DEVICES OR SYSTEMS

- B81C1/00—Manufacture or treatment of devices or systems in or on a substrate

- B81C1/00642—Manufacture or treatment of devices or systems in or on a substrate for improving the physical properties of a device

- B81C1/00714—Treatment for improving the physical properties not provided for in groups B81C1/0065 - B81C1/00706

-

- C—CHEMISTRY; METALLURGY

- C30—CRYSTAL GROWTH

- C30B—SINGLE-CRYSTAL GROWTH; UNIDIRECTIONAL SOLIDIFICATION OF EUTECTIC MATERIAL OR UNIDIRECTIONAL DEMIXING OF EUTECTOID MATERIAL; REFINING BY ZONE-MELTING OF MATERIAL; PRODUCTION OF A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; SINGLE CRYSTALS OR HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; AFTER-TREATMENT OF SINGLE CRYSTALS OR A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; APPARATUS THEREFOR

- C30B25/00—Single-crystal growth by chemical reaction of reactive gases, e.g. chemical vapour-deposition growth

- C30B25/02—Epitaxial-layer growth

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02367—Substrates

- H01L21/0237—Materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02367—Substrates

- H01L21/0237—Materials

- H01L21/02373—Group 14 semiconducting materials

- H01L21/02381—Silicon, silicon germanium, germanium

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02436—Intermediate layers between substrates and deposited layers

- H01L21/02439—Materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02436—Intermediate layers between substrates and deposited layers

- H01L21/02439—Materials

- H01L21/02455—Group 13/15 materials

- H01L21/02463—Arsenides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02436—Intermediate layers between substrates and deposited layers

- H01L21/02494—Structure

- H01L21/02513—Microstructure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02538—Group 13/15 materials

- H01L21/02543—Phosphides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02538—Group 13/15 materials

- H01L21/02546—Arsenides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02587—Structure

- H01L21/0259—Microstructure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02656—Special treatments

- H01L21/02658—Pretreatments

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N30/00—Piezoelectric or electrostrictive devices

- H10N30/01—Manufacture or treatment

- H10N30/08—Shaping or machining of piezoelectric or electrostrictive bodies

- H10N30/082—Shaping or machining of piezoelectric or electrostrictive bodies by etching, e.g. lithography

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N60/00—Superconducting devices

- H10N60/01—Manufacture or treatment

- H10N60/0268—Manufacture or treatment of devices comprising copper oxide

- H10N60/0296—Processes for depositing or forming superconductor layers

- H10N60/0576—Processes for depositing or forming superconductor layers characterised by the substrate

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y40/00—Manufacture or treatment of nanostructures

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S977/00—Nanotechnology

- Y10S977/70—Nanostructure

- Y10S977/701—Integrated with dissimilar structures on a common substrate

- Y10S977/72—On an electrically conducting, semi-conducting, or semi-insulating substrate

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S977/00—Nanotechnology

- Y10S977/70—Nanostructure

- Y10S977/811—Of specified metal oxide composition, e.g. conducting or semiconducting compositions such as ITO, ZnOx

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S977/00—Nanotechnology

- Y10S977/70—Nanostructure

- Y10S977/813—Of specified inorganic semiconductor composition, e.g. periodic table group IV-VI compositions

- Y10S977/825—Heterojunction formed between semiconductor materials that differ in that they belong to different periodic table groups

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S977/00—Nanotechnology

- Y10S977/70—Nanostructure

- Y10S977/832—Nanostructure having specified property, e.g. lattice-constant, thermal expansion coefficient

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/24—Structurally defined web or sheet [e.g., overall dimension, etc.]

- Y10T428/24802—Discontinuous or differential coating, impregnation or bond [e.g., artwork, printing, retouched photograph, etc.]

Description

−Siの基板の表面をポーラス化することによって、高比表面積を有する2つのポーラス層が形成される。このうち、表面層は、多孔率が低く、一方、表面層と基板との間に挿入された後者の層は多孔率の増大をみせる。

−上記の結果得られた基板の表面を若干酸化(最大でも単層)することによって、クリスタリット(微結晶)を機械的に安定化させる。

−Siの薄膜層のエピタキシーの直前に、成長構造における基板を還元する。

−Siの薄膜層上にSiGeの層を格子不整に成長させる。

−高比表面積を有するナノ構造化サポート上に少なくとも1つの薄膜層を形成すること、及び

−ナノ構造化サポートを処理して、サポート内に内部歪みを発生させて、少なくとも前記薄膜層の平面内にその変形を引き起こすことによって、薄膜層の対応する変形を確実にして薄膜層の特性を変化させることからなる。

−金属又は半金属をベースとした高比表面積を有するナノ構造物。

−例えばポーラスシリコンなど高比表面積を有する半導体ナノ構造物、又はIV型、IV−IV型、III−V型、II−VI型などその他の半導体ナノ構造物。

−TiO2(アナターゼ、ルチル)、Al2O3、ZnOなどをベースとした高比表面積を有するナノ構造化誘電体。

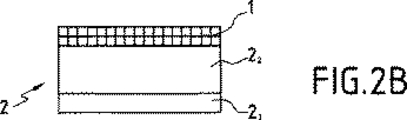

−薄膜層1は、変形後、基板(ナノ構造化サポートおよび薄膜層)が過剰に曲がらないようにするため、ナノ構造化サポート2よりも十分薄い厚さでなければならない。

−薄膜層は、構造上の欠陥から変形が生じても実質的に弾性が保たれるよう、十分薄い厚さでなければならない。

・以下のような半導体

−IV−IV型:Si、Ge、SixGe1−x、SiC、SixGeyC1−x−y

−III−V型:GaxAl1−xAs、GaxIn1−xAs、AlxIn1−xAs、GaxIn1−xAsyP1−y、GaxAl1−xP、GaxAl1−xN、GaxIn1−xN、GaxIn1−xSb、GaxAl1−xSb、(GaxIn1−x)1−yTlyAs、(GaxIn1−x)1−yTlyP

−II−VI型:ZnxCd1−xTeySe1−y、CdxHg1−xTe

・YbaCuOなどの超半導体

・以下のような磁性体

−鉄、コバルト、ニッケル、それらの合金、一部の希土類などの強磁性体

−常磁性体

Claims (16)

- マイクロエレクトロニクス、ナノエレクトロニクス、又はマイクロテクノロジー、ナノテクノロジーの各分野で利用される基板(3)を形成するサポート(2)の表面上に形成される薄膜層(1)の特性を変化させるプロセスであって、

−高比表面積を有するナノ構造化サポート(2)上に少なくとも1つの薄膜層(1)を形成すること、及び

−前記高比表面積を有するナノ構造化サポート(2)を処理して、前記サポート内に内部歪みを発生させて、少なくとも前記薄膜層の平面内にその変形を引き起こすことによって、前記薄膜層の対応する変形を確実にして前記薄膜層の特性を変化させることからなることを特徴とするプロセス。 - 前記高比表面積を有するナノ構造化サポート(2)を化学的に処理して、そのナノ構造の膨張又は収縮に対応する変形を保証することからなることを特徴とする請求項1記載のプロセス。

- 高比表面積を有するナノ構造化サポート(2)を、金属、半導体、又は誘電体をベースとした様々なナノ構造物の中から選択することからなることを特徴とする請求項1記載のプロセス。

- 前記高比表面積を有するナノ構造化サポート(2)の処理後、前記薄膜層(1)上に結晶質のエピタキシャル成長を発生させることからなることを特徴とする請求項1又は2記載のプロセス。

- 前記高比表面積を有するナノ構造化サポート(2)の処理後に、前記薄膜層(1)上のエピタキシャル成長によって形成される前記結晶質の格子定数に対応する格子定数を有することが可能な薄膜層(1)を選択することからなることを特徴とする請求項4記載のプロセス。

- 前記高比表面積を有するナノ構造化サポート(2)上に予め歪ませた又は予め歪ませていない薄膜層(1)を形成することからなることを特徴とする請求項5記載のプロセス。

- 前記高比表面積を有するナノ構造化サポート(2)上に、少なくとも1つの中間層(21)を、前記薄膜層(1)と前記高比表面積を有するナノ構造化サポート(2)との間に形成することからなることを特徴とする請求項1記載のプロセス。

- 前記薄膜層(1)上に、半導体材料又は超半導体材料から選択した結晶質の前記エピタキシャル成長を形成することからなることを特徴とする請求項4、5、7のいずれか1項に記載のプロセス。

- 前記高比表面積を有するナノ構造化サポート(2)上に、圧電特性を有する材料から構成される薄膜層(1)を形成することからなることを特徴とする請求項1〜3のいずれか1項に記載のプロセス。

- 前記薄膜層(1)でリソグラフィー工程を実施して圧電領域(z)を実現することからなることを特徴とする請求項9記載のプロセス。

- 前記薄膜層において電荷がみられるように、前記高比表面積を有するナノ構造化サポート(2)を変形させることからなることを特徴とする請求項9又は10記載のプロセス。

- マイクロエレクトロニクス、ナノエレクトロニクス、又はマイクロテクノロジー、ナノテクノロジー用の基板であって、

高比表面積を有するナノ構造化サポート(2)によって形成される基板であり、

前記高比表面積を有するナノ構造化サポート(2)が、後続の処理で変形し、その表面上に前記サポートに対応して変形する少なくとも1つの薄膜層(1)が形成されることを特徴とする基板。 - 前記薄膜層(1)に形成された半導体結晶質又は超半導体結晶質のエピタキシャル層(4)を備えることを特徴とする請求項12記載の基板。

- 前記薄膜層(1)が圧電材料から構成されることを特徴とする請求項12記載の基板。

- 光電子素子の製造への請求項12記載の基板の適用。

- 電子部品の製造への請求項12記載の基板の適用。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| FR02/05731 | 2002-05-07 | ||

| FR0205731A FR2839505B1 (fr) | 2002-05-07 | 2002-05-07 | Procede pour modifier les proprietes d'une couche mince et substrat faisant application du procede |

| PCT/FR2003/001423 WO2003099707A2 (fr) | 2002-05-07 | 2003-05-07 | Procede pour modifier les proprietes d'une couche mince et substrat faisant application du procede |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010094004A Division JP2010212705A (ja) | 2002-05-07 | 2010-04-15 | 薄膜層の特性を変化させるプロセス、及び前記プロセスを適用する基板 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005528987A JP2005528987A (ja) | 2005-09-29 |

| JP2005528987A5 JP2005528987A5 (ja) | 2011-07-07 |

| JP4786178B2 true JP4786178B2 (ja) | 2011-10-05 |

Family

ID=29286361

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004507374A Expired - Lifetime JP4786178B2 (ja) | 2002-05-07 | 2003-05-07 | 薄膜層の特性を変化させるプロセス、及び前記プロセスを適用する基板 |

| JP2010094004A Pending JP2010212705A (ja) | 2002-05-07 | 2010-04-15 | 薄膜層の特性を変化させるプロセス、及び前記プロセスを適用する基板 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010094004A Pending JP2010212705A (ja) | 2002-05-07 | 2010-04-15 | 薄膜層の特性を変化させるプロセス、及び前記プロセスを適用する基板 |

Country Status (7)

| Country | Link |

|---|---|

| US (2) | US7553369B2 (ja) |

| EP (1) | EP1501757B1 (ja) |

| JP (2) | JP4786178B2 (ja) |

| KR (1) | KR100855784B1 (ja) |

| AU (1) | AU2003263225A1 (ja) |

| FR (1) | FR2839505B1 (ja) |

| WO (1) | WO2003099707A2 (ja) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2839505B1 (fr) * | 2002-05-07 | 2005-07-15 | Univ Claude Bernard Lyon | Procede pour modifier les proprietes d'une couche mince et substrat faisant application du procede |

| FR2857155B1 (fr) | 2003-07-01 | 2005-10-21 | St Microelectronics Sa | Procede de fabrication de couches contraintes de silicium ou d'un alliage de silicium-germanium |

| RU2267832C1 (ru) * | 2004-11-17 | 2006-01-10 | Александр Викторович Принц | Способ изготовления микро- и наноприборов на локальных подложках |

| EP1874986B1 (en) * | 2005-04-25 | 2013-01-23 | Smoltek AB | Controlled growth of a nanostructure on a substrate, and electron emission devices based on the same |

| US7777291B2 (en) | 2005-08-26 | 2010-08-17 | Smoltek Ab | Integrated circuits having interconnects and heat dissipators based on nanostructures |

| FR2903810B1 (fr) * | 2006-07-13 | 2008-10-10 | Commissariat Energie Atomique | Procede de nanostructuration de la surface d'un substrat |

| EP2197782B1 (en) | 2007-09-12 | 2020-03-04 | Smoltek AB | Connecting and bonding adjacent layers with nanostructures |

| WO2009108101A1 (en) | 2008-02-25 | 2009-09-03 | Smoltek Ab | Deposition and selective removal of conducting helplayer for nanostructure processing |

| DE102010046215B4 (de) | 2010-09-21 | 2019-01-03 | Infineon Technologies Austria Ag | Halbleiterkörper mit verspanntem Bereich, Elektronisches Bauelement und ein Verfahren zum Erzeugen des Halbleiterkörpers. |

| US10032870B2 (en) * | 2015-03-12 | 2018-07-24 | Globalfoundries Inc. | Low defect III-V semiconductor template on porous silicon |

Family Cites Families (40)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3607269A (en) * | 1968-04-01 | 1971-09-21 | Polaroid Corp | Image-receiving elements and photographic processes employing same |

| DE2934426A1 (de) * | 1979-08-25 | 1981-03-26 | Rudi Ing.(grad.) 6700 Ludwigshafen Schmitt | Messgeraet zur quantitativen bestimmung einer komponente einer gasmischung |

| US4758534A (en) * | 1985-11-13 | 1988-07-19 | Bell Communications Research, Inc. | Process for producing porous refractory metal layers embedded in semiconductor devices |

| US4728591A (en) * | 1986-03-07 | 1988-03-01 | Trustees Of Boston University | Self-assembled nanometer lithographic masks and templates and method for parallel fabrication of nanometer scale multi-device structures |

| US5238729A (en) * | 1991-04-05 | 1993-08-24 | Minnesota Mining And Manufacturing Company | Sensors based on nanosstructured composite films |

| JPH04318922A (ja) * | 1991-04-17 | 1992-11-10 | Sumitomo Electric Ind Ltd | 化合物半導体結晶の成長方法 |

| JP3089732B2 (ja) * | 1991-09-24 | 2000-09-18 | 住友電気工業株式会社 | 化合物半導体のエピタキシャル成長方法 |

| FR2689912A1 (fr) * | 1992-04-14 | 1993-10-15 | Centre Nat Rech Scient | Procédé de réalisation d'un réseau de discontinuités à une ou deux dimensions à la surface d'un substrat cristallin ou dans une structure complexe comportant un tel substrat. |

| US5374472A (en) * | 1992-11-03 | 1994-12-20 | The Regents, University Of California | Ferromagnetic thin films |

| US5352651A (en) * | 1992-12-23 | 1994-10-04 | Minnesota Mining And Manufacturing Company | Nanostructured imaging transfer element |

| US5338430A (en) * | 1992-12-23 | 1994-08-16 | Minnesota Mining And Manufacturing Company | Nanostructured electrode membranes |

| US5459016A (en) * | 1993-12-16 | 1995-10-17 | Minnesota Mining And Manufacturing Company | Nanostructured thermal transfer donor element |

| JP3250721B2 (ja) * | 1995-12-12 | 2002-01-28 | キヤノン株式会社 | Soi基板の製造方法 |

| JP3541690B2 (ja) * | 1998-09-11 | 2004-07-14 | 松下電器産業株式会社 | 発光素子の製造方法 |

| US6834149B1 (en) * | 1999-02-09 | 2004-12-21 | Xoetronics, Llc | Optically confined birefringent chalcopyrite heterostructure devices and operating methods |

| US6372364B1 (en) * | 1999-08-18 | 2002-04-16 | Microcoating Technologies, Inc. | Nanostructure coatings |

| JP2001223165A (ja) * | 2000-02-10 | 2001-08-17 | Hitachi Cable Ltd | 窒化物半導体及びその製造方法 |

| US6365059B1 (en) * | 2000-04-28 | 2002-04-02 | Alexander Pechenik | Method for making a nano-stamp and for forming, with the stamp, nano-size elements on a substrate |

| US20040195202A1 (en) * | 2000-04-28 | 2004-10-07 | Alexander Pechenik | Method for making a nano-stamp and for forming, with the stamp, nano-size elements on a substrate |

| US6787198B2 (en) * | 2000-07-28 | 2004-09-07 | Ekc Technology, Inc. | Hydrothermal treatment of nanostructured films |

| US6541392B2 (en) * | 2000-09-15 | 2003-04-01 | Technology Ventures, L.L.C. | Method for fabricating three dimensional anisotropic thin films |

| EP1333935A4 (en) * | 2000-10-17 | 2008-04-02 | Nanogram Corp | PREPARATION OF A COAT BY REACTIVE DEPOSITION |

| KR100831751B1 (ko) * | 2000-11-30 | 2008-05-23 | 노쓰 캐롤라이나 스테이트 유니버시티 | M'n 물의 제조 방법 및 장치 |

| US6913697B2 (en) * | 2001-02-14 | 2005-07-05 | Science & Technology Corporation @ Unm | Nanostructured separation and analysis devices for biological membranes |

| US20040033942A1 (en) * | 2001-03-13 | 2004-02-19 | Jackson Jennifer L | Transriotion factors |

| US6992321B2 (en) * | 2001-07-13 | 2006-01-31 | Motorola, Inc. | Structure and method for fabricating semiconductor structures and devices utilizing piezoelectric materials |

| DE10204895B4 (de) * | 2002-02-06 | 2004-07-29 | Diehl Munitionssysteme Gmbh & Co. Kg | Verfahren zur Herstellung von Reaktivstoffen |

| JP2003282464A (ja) * | 2002-03-27 | 2003-10-03 | Seiko Epson Corp | 半導体基板およびその製造方法 |

| US6946410B2 (en) * | 2002-04-05 | 2005-09-20 | E. I. Du Pont De Nemours And Company | Method for providing nano-structures of uniform length |

| US6853075B2 (en) * | 2003-01-28 | 2005-02-08 | Wayne State University | Self-assembled nanobump array stuctures and a method to fabricate such structures |

| FR2839505B1 (fr) * | 2002-05-07 | 2005-07-15 | Univ Claude Bernard Lyon | Procede pour modifier les proprietes d'une couche mince et substrat faisant application du procede |

| US6869671B1 (en) * | 2002-06-03 | 2005-03-22 | University Of Notre Dame | Enabling nanostructured materials via multilayer thin film precursor and applications to biosensors |

| US6858521B2 (en) * | 2002-12-31 | 2005-02-22 | Samsung Electronics Co., Ltd. | Method for fabricating spaced-apart nanostructures |

| US7135728B2 (en) * | 2002-09-30 | 2006-11-14 | Nanosys, Inc. | Large-area nanoenabled macroelectronic substrates and uses therefor |

| US7067867B2 (en) * | 2002-09-30 | 2006-06-27 | Nanosys, Inc. | Large-area nonenabled macroelectronic substrates and uses therefor |

| CN1742358A (zh) * | 2002-11-20 | 2006-03-01 | 瑞威欧公司 | 在基板上制造多层器件的方法和系统 |

| US7132678B2 (en) * | 2003-03-21 | 2006-11-07 | International Business Machines Corporation | Electronic device including a self-assembled monolayer, and a method of fabricating the same |

| US7115910B2 (en) * | 2003-05-05 | 2006-10-03 | Banpil Photonics, Inc. | Multicolor photodiode array and method of manufacturing thereof |

| US7019391B2 (en) * | 2004-04-06 | 2006-03-28 | Bao Tran | NANO IC packaging |

| DE102007038851A1 (de) * | 2007-08-16 | 2009-02-19 | Schott Ag | Verfahren zur Herstellung von monokristallinen Metall- oder Halbmetallkörpern |

-

2002

- 2002-05-07 FR FR0205731A patent/FR2839505B1/fr not_active Expired - Lifetime

-

2003

- 2003-05-07 WO PCT/FR2003/001423 patent/WO2003099707A2/fr active Application Filing

- 2003-05-07 US US10/512,077 patent/US7553369B2/en not_active Expired - Lifetime

- 2003-05-07 AU AU2003263225A patent/AU2003263225A1/en not_active Abandoned

- 2003-05-07 EP EP03755160.3A patent/EP1501757B1/fr not_active Expired - Lifetime

- 2003-05-07 JP JP2004507374A patent/JP4786178B2/ja not_active Expired - Lifetime

- 2003-05-07 KR KR1020047017951A patent/KR100855784B1/ko active IP Right Grant

-

2009

- 2009-05-22 US US12/470,540 patent/US9102518B2/en active Active

-

2010

- 2010-04-15 JP JP2010094004A patent/JP2010212705A/ja active Pending

Also Published As

| Publication number | Publication date |

|---|---|

| FR2839505A1 (fr) | 2003-11-14 |

| EP1501757A2 (fr) | 2005-02-02 |

| US9102518B2 (en) | 2015-08-11 |

| US20050229837A1 (en) | 2005-10-20 |

| JP2010212705A (ja) | 2010-09-24 |

| AU2003263225A1 (en) | 2003-12-12 |

| US7553369B2 (en) | 2009-06-30 |

| WO2003099707A3 (fr) | 2004-04-08 |

| FR2839505B1 (fr) | 2005-07-15 |

| JP2005528987A (ja) | 2005-09-29 |

| KR20050007530A (ko) | 2005-01-19 |

| WO2003099707A2 (fr) | 2003-12-04 |

| US20090226680A1 (en) | 2009-09-10 |

| EP1501757B1 (fr) | 2017-08-16 |

| KR100855784B1 (ko) | 2008-09-01 |

| AU2003263225A8 (en) | 2003-12-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2010212705A (ja) | 薄膜層の特性を変化させるプロセス、及び前記プロセスを適用する基板 | |

| Golod et al. | Fabrication of conducting GeSi/Si micro-and nanotubes and helical microcoils | |

| US7696105B2 (en) | Method for producing catalyst-free single crystal silicon nanowires, nanowires produced by the method and nanodevice comprising the nanowires | |

| US20060009003A1 (en) | Methods for nanowire growth | |

| JP4954853B2 (ja) | 2つの固体材料の分子接着界面における結晶欠陥および/または応力場の顕在化プロセス | |

| KR101401580B1 (ko) | 기판 벽개 방법 | |

| JP2005528987A5 (ja) | ||

| US9647063B2 (en) | Nanoscale chemical templating with oxygen reactive materials | |

| CN104756229B (zh) | 用于生产半导体结构的方法 | |

| US20130264687A1 (en) | Method for producing columnar structure | |

| JP2017028318A (ja) | エピタキシャル固体半導体ヘテロ構造及びその製造方法 | |

| JP4046175B2 (ja) | 微細構造素子の作製方法 | |

| US7084075B2 (en) | Method for producing a layer on a substrate | |

| JP4854180B2 (ja) | InSbナノ細線構造の作製方法 | |

| US20230052052A1 (en) | Monocrystalline nickel-titanium films on single crystal silicon substrates using seed layers | |

| JP4235709B2 (ja) | 半導体基板表面の微細ファセット形状作製方法 | |

| JP3950970B2 (ja) | Sn単結晶薄膜の製造方法 | |

| JPH113988A (ja) | 超微細突起構造体およびその製造方法 | |

| KR20220102739A (ko) | 반도체 나노막대의 형성방법, 반도체 디바이스 및 그 제조방법 | |

| JPH0927451A (ja) | 化合物半導体基板の製造方法 | |

| JPH09106949A (ja) | 化合物半導体基板及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060328 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090324 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20090624 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091015 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20091215 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100610 |

|

| A524 | Written submission of copy of amendment under article 19 pct |

Free format text: JAPANESE INTERMEDIATE CODE: A524 Effective date: 20110524 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110713 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4786178 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140722 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |