CN1742358A - 在基板上制造多层器件的方法和系统 - Google Patents

在基板上制造多层器件的方法和系统 Download PDFInfo

- Publication number

- CN1742358A CN1742358A CNA2003801090448A CN200380109044A CN1742358A CN 1742358 A CN1742358 A CN 1742358A CN A2003801090448 A CNA2003801090448 A CN A2003801090448A CN 200380109044 A CN200380109044 A CN 200380109044A CN 1742358 A CN1742358 A CN 1742358A

- Authority

- CN

- China

- Prior art keywords

- semiconductor layer

- layer

- bonded areas

- bonding

- crystal grain

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L22/00—Testing or measuring during manufacture or treatment; Reliability measurements, i.e. testing of parts without further processing to modify the parts as such; Structural arrangements therefor

- H01L22/20—Sequence of activities consisting of a plurality of measurements, corrections, marking or sorting steps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B81—MICROSTRUCTURAL TECHNOLOGY

- B81C—PROCESSES OR APPARATUS SPECIALLY ADAPTED FOR THE MANUFACTURE OR TREATMENT OF MICROSTRUCTURAL DEVICES OR SYSTEMS

- B81C99/00—Subject matter not provided for in other groups of this subclass

- B81C99/0035—Testing

- B81C99/0045—End test of the packaged device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L22/00—Testing or measuring during manufacture or treatment; Reliability measurements, i.e. testing of parts without further processing to modify the parts as such; Structural arrangements therefor

- H01L22/10—Measuring as part of the manufacturing process

- H01L22/14—Measuring as part of the manufacturing process for electrical parameters, e.g. resistance, deep-levels, CV, diffusions by electrical means

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/013—Alloys

- H01L2924/014—Solder alloys

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1305—Bipolar Junction Transistor [BJT]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1306—Field-effect transistor [FET]

- H01L2924/13091—Metal-Oxide-Semiconductor Field-Effect Transistor [MOSFET]

Abstract

本发明公开一种用于在整体基板上制造多层器件的方法和系统。多层微机电与微流体器件被制造于具有预定弱粘结区域及强粘结区域的层体的基板上,而器件解构层位于弱粘结区域处或在弱粘结区域上。还公开了在基板上制造具有预定弱粘结区域及强粘结区域的多层集成电路。任意层数可粘结与堆栈,以便在基板上产生预定器件器件。本发明还揭示了建立穿过基板的边缘互联体与通路以形成层体和层体上器件互联的方法。

Description

相关申请的交叉参考

本申请根据35U.S.C.§119(e)要求2002年11月20日提交的美国临时专利申请No.60/428,125的优先权,该申请结合在此作为参考。

技术领域

本发明有关于在基板上制造多层有源器件的方法和系统,特别是关于一种在半导体基板上制造垂直集成电路、微机电器件和微流体器件。

背景技术

对于更快速而更便宜的集成电路的需求持续增加。莫尔定律推测每平方英时的晶体管数量会以每年双倍的比率成长。然而,当传统的二维空间(或平面)的芯片制造方法已达到极限,为了要实现莫尔定律的预言,势必要革新技术以扩展芯片制造的新领域。

直至目前为止,大部分所遭遇到对更密集的集成电路的需求来自于在制造于相对平面结构上持续缩小的有源器件。即,二维芯片制造已然是为半导体制造的普遍方法。大多数的半导体设备被制造在一个平面的单晶半导体基板中。而此方式对于垂直积设到三维空间实非常有限。

当濒临二维芯片制造空间的极限时,效能上的主要突破将往三维空间芯片制造发展(即,在z方向上的芯片制造)。

将微器件垂直积设或堆栈到同一封装内,是一种减小封装体积、增加电路密度、节省基板空间、以及增加效能和功能性的相当吸引人的方法。缩减内部芯片的延迟与耗电量为堆栈积设的两种优势。如果这些器件变薄并且堆栈在彼此的顶部上,在成本与电路密度方面的优势将巨幅增加。而在IC(集成电路)和MEMS(微机电系统)两制程中,硅晶片第三维空间绝大部分尚未开发。

目前产业上所用的二维器件垂直堆栈的方法,一般为芯片-标度法且需仰赖磨的动作来使晶片变薄。大多数的方法仰赖利用通孔、堆栈母子芯片、或打线粘结的互联方式。目前的方法皆具有关于封装大小、成本、可靠度、和产量冲击的限制。尽管困难,堆栈器件以达成三维空间的整合被发现是可行的,尤其是在结合微机电系统(MEMS)和应用导向集成电路(ASIC)控制器的方面。堆栈个别芯片的高密度内存封装已被发现许多特定的应用。

IBM的美国专利No.6,355,501揭示了一种制造三维集成电路总成的方法,主要关于芯片规模。其中揭示的总成是由在绝缘体上的三维堆栈硅(SOI)芯片所组成,并揭示了一种形成此种集成电路总成的方法。每一个SOI芯片包括一个取置部(handler)来对第一金属化图案作机械接触以与一半导体器件做电气接触。该金属化图案依次接触设置在半导体设备的一相反表面上的第二个金属化图案。在此揭示的方法包括步骤有:a)使一基板在其一第一表面上具有一第三金属化图案;b)藉使SOI芯片的第二金属化图案与基板的第三金属化的图案电气接触,使基板第一表面的其中一SOI芯片在基板的第一表面对齐;c)从该SOI芯片移除取置部,暴露出SOI芯片的第一金属化图案;d)使第二个SOI芯片和第一SOI芯片对齐,让第二SOI芯片的第二金属化图案与第一SOI芯片被暴露出的第一金属化图案电气接触;以及e)反复的步骤c)和d)来一个叠在一个上地装设后续SOI芯片。然而,此参考资料揭示的方法可碍于成本昂贵而功能有限。

在上述美国专利No.6,355,501中所揭示的方法的关键缺点在于其申请人所强调的在一个晶片规模上形成三维电路导致低生产率。此外,对准每个芯片被视为是妨碍晶片规模堆栈的重要问题。每个芯片的堆栈步骤包括对准欲彼此粘结的层体。必须具有透明的粘着物和窗口才能够光学地存取在两个欲相粘结的表面上的对准标记。此外,取置部对于对准标记必须是可通透的。其它的缺点与后续的重复方法步骤的数量有关。依照其中的描述,为达到堆栈层体间的电气接触,当它被堆栈而且对齐的时候,各层体间进行一个焊料回流步骤。在再回流之后,芯片堆栈是边缘粘结的。又,在后来的层可被粘结之前,取置部一定要以粘除(用激光或其它的热气)、抛光、及其它的准备步骤移除。最后,过量基板以磨除或者蚀去来移除。

这些不利条件导致成本和功能性有关的缺点。伴随磨除的费用损失、繁琐的后续步骤、防碍晶片规模堆栈的芯片规模,而之中晶片规模众所皆知可减少成本,欲克服在晶片上的产量问题于是回归到芯片规模的问题上、层数限制造成较多数量的堆栈,堆栈一定要在其它的堆栈上堆栈、由于后续堆栈量与互联有关使得整体的产量减少、多重再回流流量可损及其它的层。而功能性的不利条件包括:缺乏诊断、缺乏互联变化性、有限的互联空间、大型堆栈有限的可寻址性,特别是内存堆栈、没有整合噪声屏蔽的能力、没有整合散热的能力、没有接地平面的能力、及层体数量之限。

美国加利福尼亚州欧文的Irvine Sensors公司以及IBM公司已采用实施一种三维封装。不连续的晶粒利用边缘隆起方法被堆栈及互联。已知良品晶粒(KGD)被变薄。晶粒边缘的焊料泵在用于对齐及互联连堆栈的晶粒。一晶粒是放在一个环氧基树脂矩阵中。环氧基树脂帮助对齐不同尺寸的晶粒,而且被用为互联表面。个体堆栈和晶粒的互联以及KGD的需求,导致这是一种非常贵的制造方法。

另一个已知采用三维封装的是Cubic Memory公司,该公司通过施用布置在整个晶片上的数层聚硫亚氨绝缘体层的金的互联路径,制造出高密度堆栈内存模块。然而,堆栈与垂直互联仍然在一个个别的芯片规模上。

又另一种已采行的三维封装实施例是由美国加利福尼亚州圣约瑟的Tessera公司与英特尔公司一同针对芯片-规模所开发,通过透过微球栅数组将芯片粘着到适应性基板上的堆栈封装,而z向折叠在它本身之上的芯片加载带。

Ziptronix公司显然地正在发展晶片规模堆栈的IC。其着眼于挑战对准、压力管理、热管理、高密度、以及生产率。

如同上面所举例说明,可行的垂直积设方法尚有各种不同的缺陷。一种基本缺陷来自于生产率损失。当今市场上所有器件堆栈方式均为晶粒-规模。准备个别的晶粒、对齐、堆栈、乃至于连接。如此的方法很贵,且堆栈的产量损失是为层体中每个器件的混合产量损失。便宜的器件有时可容忍增加的产量损失,像是SRAM堆栈等。但是当在堆栈较贵的器件时,解决手段为使用一已知良品晶粒(KGD)。KGD意指,经烧入和测试的各未包装晶粒。此外,堆栈需要在每层完成后经电气测试。此处理过程所须费用非常贵,且主要应用已经被限制在高阶的使用者,像是军队和卫星技术。

另一传统垂直积设的不利条件肇于晶粒规模的技术有限。除了Ziptronix尚未达到市场的方式外,所有的方法都是堆栈器件于一晶粒规模上。晶片规模制造显著的经济优势以这些技术是完全作不到的。处理和测试个别晶粒的高费用限制这些方法用于高阶应用。

在整个传统制造程序中形成电路的另一已知问题是支撑在一个基板上的取置部的需求。在进行处理的时候,基板须提供机械性支撑和热稳定度。被处理的基板因而必须足够厚以抵抗恶劣的处理环境,包括高压、温度、以及化学与能量暴露。而如果寻求活性的薄膜器件则需要更进一步的处理。

在一个足够厚的基板上形成电路或其它的结构来抵抗处理后采取一种处理方式,即以机械的方法移除基板的厚度。机械的方法,诸如切断或研磨等,浪费整体的资源和人力。切断或磨除的材料通常不可回收,即使是可回收的,在重复使用之前一定需要历经更进一步的处理。此外,变薄的基板通常受制于抛光或其它的方法来平滑表面。其它的技术包括在器件制造之前在基板上形成一蚀刻停止层结构。然而,基板典型上仍然在一选择的蚀刻步骤之前被磨除机械式移除,该步骤一般蚀刻基板到蚀刻停止层。所有的这些技术造成时间和资源的浪费,以及令人挂心的品质控制。

要形成薄膜器件的另一种技术利用离子植入方法。离子植入的一种普遍利用是形成数层薄的半导体材料。举例来说,此方法被揭示在专利申请EP 01045448和WO 00/024059中,两者皆名为“通过氢离子植入分离方法制造SOI晶片的方法及以该方法生产的SOI晶片”,而且在本申请中两者都作为参考。离子,尤其像是氢离子或氦离子,在氧化硅晶片的顶面植入。离子在顶表面植入一个深度。其后,可从整体硅基板分层出一薄层体,一般受制于高温(大约500℃以上)处理下。此薄层接着可被托承在一缘体层和一基板上,而微电子或其它的结构可被其上形成。然而,微电子一定要在分层薄层之后来形成,因为离子植入对微电子是有害地影响。特别是薄层可被弄歪,器件可被离子植入而损害,或器件可在分层期间被损害。

Bruel等的专利申请WO 98/33209,取名为“在特定半导体中包含一个被保护的离子区域以及涉及离子植入的获得薄膜的方法”,其中揭示了提供包括一个金属氧化物半导体(MOS)的薄膜的方法。大体上,一个MOS晶体管形成于半导体基板的表面上。晶体管的区域是被屏蔽的,且周围的区域是以离子植入来界定一预期断裂线(即,在该处微泡由离子植入步骤产生)。为了要分开上面有晶体管的薄膜,在微泡附近的预期断裂线着手断开的动作,且透过晶体管下面的晶平面(即,没有微泡存在)传播。可想而知在其上具有晶体管的薄膜利用专利申请WO98/33209的揭示是可行的,不过,因为基板材料的晶形结构势必使得破碎的动作极接近晶体管,而使得晶体管受到断开传播的不理想压力的影响。

Aspar等的美国专利No.6,103,597,名称为“获得半导体材料薄膜的方法”,主要揭示了使一其中具有微电子或其它结构的薄膜基板受到离子撞击的内容。气体的微泡在形成定义薄膜厚度的深度形成。然而,可在基板上被形成的多种微电子和结构需要一个后续的韧化步骤,以修理损害或其它分散到所述元件的缺点。因此,薄膜层被揭示为一种可被导致沿着微泡线破碎的热处理而可从底下的基板材料分离。

Sakaguchi等的名称为“基板及相关制造方法”的美国专利No.6,221,738以及名称为“生产半导体对象的方法”的美国专利No.6,100,166揭示粘结渗透的半导体层,两者在此处均被作为参考。其中揭示粘结渗透层的力量较弱,如此促进应用一外部力量的移除。美国专利No.6,100,166揭示一个层体可以一剥除方向的力量移除。然而,这两个参考专利案中所揭示的在整个层体界面间利用微弱的渗透分离物理作用。这可对整体伤及其中间的结构完整性以及任何形成在渗透的半导体材料上的半导体设备。

Henley等的名为“前制半导体程序植入和后制程序薄膜分离”的美国专利No.6,184,111在本申请中作为参考。其揭示了在一个硅水表面下的一经选择的深度利用一压力层。器件被形成在压力层上面。通常依晶片直径改变剂量而在相同的能阶进行植入。受控的断开传播开始分离压力层上面的一层,包括其上任何的器件。注意形成压力层的方法可损害其上面形成的器件,如此一般尚需之后的修理韧化步骤。因此,在传统的离子植入和分层方法中,在其上包括影微电子或其它结构的薄膜是不可在不弄歪或损害该薄半导体层的情况下植入离子的。

因此,考虑当前电路处理的不利条件,一种避免不利条件和传统方法的缺点而在一个芯片上或在一个晶片规模上提供三维空间的集成电路将会是令人想要的。

因此,本发明的一个基本目标在于提供一个最低成本的三维空间集成电路。

本发明更进一步的目的是提供一多层基板来制造一有用器件。

本发明的另一目的是提供为垂直集成器件增加生产率的方法与系统。

本发明的又另一目的是提供分类垂直集成器件的方法与系统。

阅读下列各项描述并伴随附图,本发明上述和其后所说明的目的和优势可被明了。

发明内容

前面所讨论及其它的问题、公知不利条件、及本发明所预达成的目的,将通过本发明所揭示的一些方法和器件来克服与解决。

在某一方面中,发明是制造垂直微机电器件的方法,组成方法的步骤包括:提供在一晶片上的一整体基板(表体基板,bulksubstrate);垂直承载于该基板上的一第一选择粘结半导体层,该粘结半导体层包含弱粘结区域和强粘结区域;垂直承载于该第一选择粘结半导体层上的一第二选择粘结半导体层;其中一电极与一可激励(可致动)元件被建立在该弱粘结区域处或在该弱粘结区域上;其中该电极与该可激励元件配置成彼此相对;以及其中该电极与该可激励元件垂直地跨越该第一选择粘结半导体层及该第二选择粘结半导体层。

在另一方面中,本发明是垂直的微机电系统器件,其包括:在一晶片上的一整体基板;垂直承载于该基板上的一第一选择粘结半导体层,该粘结半导体层包含弱粘结区域和强粘结区域;垂直承载于该第一选择粘结半导体层上的一第二选择粘结半导体层;其中一电极与一可激励元件被建立在该弱粘结区域处或在该弱粘结区域上;其中该电极与该可激励元件配置成彼此相对;以及其中该电极与该可激励元件垂直地跨越该第一选择粘结半导体层及该第二选择粘结半导体层。

在另一方面中,本发明是一种形成于晶粒上的垂直微机电系统器件,其包括:在一晶片上的一整体基板;垂直承载于该基板上的一第一选择粘结半导体层,该粘结半导体层包含弱粘结区域和强粘结区域;垂直承载于该第一选择粘结半导体层上的一第二选择粘结半导体层;其中一元件与一可激励元件被建立在该弱粘结区域处或在该弱粘结区域上;其中一元件与一可激励元件被建立在该弱粘结区域处或在该弱粘结区域上;其中该元件与该可激励元件配置成彼此相对;以及其中该元件与该可激励元件垂直地跨越该第一选择粘结半导体层及该第二选择粘结半导体层。

在另一方面中,本发明关于一种用于制造多层微流体器件的方法,其包括以下步骤:提供一整体基板;在该基板上选择性地建立强粘结区域和弱粘结区域;提供垂直承载于该基板上的第一粘结层;在该第一粘结层上建立一端口,该端口对应于该弱粘结区域;机械性地创造一个通道耦接至该端口;从该整体基板移除该第一层;以及粘结该第一层至一第二层。

在另一方面中,本发明关于一种多层微流体器件,其包括:在一晶片上的一整体基板;垂直承载于该基板上的一第一选择粘结层,该粘结层包含弱粘结区域和强粘结区域;垂直承载于该第一选择粘结层上的一第二选择粘结层;其中解构端口和解构通道建立于所述弱粘结区域处或在所述弱粘结区域上;以及其中所述端口及所述通道垂直地跨越该第一选择粘结层与该第二选择粘结层。

在另一方面中,本发明关于一种在一晶粒上形成的多层微流体器件:在一晶片上的一整体基板;垂直承载于该基板上的一第一选择粘结层,该粘结层包含弱粘结区域和强粘结区域;垂直承载于该第一选择粘结层上的一第二选择粘结层;其中解构端口和解构通道建立于所述弱粘结区域处或在所述弱粘结区域上;其中所述端口及所述通道垂直地跨越该第一选择粘结层与该第二选择粘结层;以及其中该晶粒是由切割所述粘结半导体层而形成的。

在另一方面中,本发明是制造一个垂直微机电器件的方法,组成方法的步骤包括:提供在一晶片上的一整体基板;垂直承载于该基板上的一第一选择粘结半导体层,该粘结半导体层包含弱粘结区域和强粘结区域;垂直承载于该第一选择粘结半导体层上的一第二选择粘结半导体层;其中一电极与一可激励元件被建立在该弱粘结区域处或在该弱粘结区域上;其中该电极与该可激励元件配置成彼此相对;以及其中该电极与该可激励元件垂直地跨越该第一选择粘结半导体层及该第二选择粘结半导体层。

在另一方面中,本发明是垂直的微机电系统器件,其包括:在一晶片上的一整体基板;垂直承载于该基板上的一第一选择粘结半导体层,该粘结半导体层包含弱粘结区域和强粘结区域;垂直承载于该第一选择粘结半导体层上的一第二选择粘结半导体层;其中一电极与一可激励元件被建立在该弱粘结区域处或在该弱粘结区域上;其中该电极与该可激励元件配置成彼此相对;以及其中该电极与该可激励元件垂直地跨越该第一选择粘结半导体层及该第二选择粘结半导体层。

在另一方面中,本发明是一种形成于晶粒上的垂直微机电系统器件,其包括:在一晶片上的一整体基板;垂直承载于该基板上的一第一选择粘结半导体层,该粘结半导体层包含弱粘结区域和强粘结区域;垂直承载于该第一选择粘结半导体层上的一第二选择粘结半导体层;其中一元件与一可激励元件被建立在该弱粘结区域处或在该弱粘结区域上;其中一元件与一可激励元件被建立在该弱粘结区域处或在该弱粘结区域上;其中该元件与该可激励元件配置成彼此相对;以及其中该元件与该可激励元件垂直地跨越该第一选择粘结半导体层及该第二选择粘结半导体层。

在另一方面中,本发明是一种用于提高预定器件的生产率的方法,该器件由一个或多个多层晶粒组成,该方法包括以下步骤:诊断性地判断每一所述多层晶粒的功能层数量;以及依据所述功能层数量对各个所述多层晶粒进行分类。

在另一方面中,本发明是一种使一器件具有至少一预定数量的已知良品层(known good layer)的方法,该器件由一个或多个多层晶粒组成,该方法包括以下步骤:诊断性地判断每一个所述多层晶粒的功能层数量;依据所述功能层数量将各个多层晶粒分类到多个储存空间,每一储存空间具有相关的已知良品层最小数量;从其中一个储存空间中选择出具有该预定数量的已知良品层的多层晶粒中的一个,该储存空间具有至少等于已知良品层预定数量的相关的已知良品层最小数量。

在另一方面中,本发明是一种提供具有至少一预定数量的已知良品层的器件的方法,该器件由一个或多个多层晶粒组成,该方法包括以下步骤:诊断性地判断每一个所述多层晶粒的功能层数量;依据所述功能层数量将各个多层晶粒分类到多个储存空间,每一储存空间具有相关的已知良品层最小数量;选择多个所述多层晶粒,它们的已知良品层数量总和至少等于已知良品层预定数量;以及结合所述选择的多个多层晶粒来形成一组合晶粒,该组合晶粒具有至少等于已知良品层预定数量的已知良品层数量。

在另一方面中,本发明是一种提供具有至少一预定数量的已知良品层的器件的方法,该器件由一个或多个多层晶粒组成,该方法包括以下步骤:诊断性地判断各该多层晶粒的功能层数量;依据所述功能层的数量将各多层晶粒分类到多个储存空间,每一储存空间具有相关的已知良品层最小数量;从所述多层晶粒中选择一个多层晶粒,所述已知良品层数量较已知良品层预定数量多;以及切割该选择的多层晶粒来形成一第一多层晶粒部分以及一第二多层晶粒部分,该第一多层晶粒部分的已知良品层数量至少等于已知良品层预定数量;将该第二多层晶粒部分分类至一个所述储存空间,该储存空间具有与第二多层晶粒部分的已知良品层数量相对应的已知良品层最小数量。

在另一方面中,本发明是一种对多个晶片堆栈进行分类的方法,其中每个晶片堆栈包括多个垂直集成器件,所述方法包括以下步骤:对晶片上的一个或所有器件进行诊断;以及依据晶片堆栈中具有预定数量已知良品层的将被陆续切割的垂直集成器件的数量而对所述晶片堆栈进行分类。

在另一方面中,本发明是一种对多个晶片堆栈进行分类的方法,其中每个晶片堆栈包括多个垂直集成器件,所述方法包括以下步骤:对晶片上的一个或所有器件进行诊断;以及依据该晶片堆栈上所包含的所有所述器件的已知良品层最小数量而对所述晶片堆栈进行分类。

在另一方面中,本发明是一种制造垂直集成电路的方法,该方法包括以下步骤:提供一整体基板,该整体基板包括一埋设的氧化物层;在该基板上选择地建立强粘结区域和弱粘结区域;提供垂直地承载于该基板上的第一粘结半导体层;在该第一粘结半导体层上建立半导体器件部分,该半导体器件部分对应于该弱粘结区域;从该整体基板移除该第一半导体层;以及将该第一半导体层粘结到一第二半导体层。

在另一方面中,本发明是一种制造垂直集成电路的方法,该方法包括以下步骤:提供一整体基板;在该基板上选择性地建立强粘结区域和弱粘结区域;提供垂直承载于该基板上的第一粘结半导体层;在该第一粘结半导体层上建立半导体器件部分,所述半导体器件部分对应于所述弱粘结区域;在该第一半导体层与该整体基板间的界面处形成一埋设的氧化物层;从该整体基板移除该第一半导体层;以及将该第一半导体层粘结到一第二半导体层。

在另一方面中,本发明是一种制造垂直微机电器件的方法,该方法包括以下步骤:提供一整体基板,该整体基板包括一埋设的氧化物层;在该基板上选择性地建立强粘结区域和弱粘结区域;提供垂直承载于该基板上的第一粘结半导体层;在该第一粘结半导体层上建立一电极,该电极对应于所述弱粘结区域;建立一配置成与该电极相对的可激励元件;从该整体基板移除该第一半导体层;以及将该第一半导体层粘结到一第二半导体层。

在另一方面中,本发明是一种用于制造垂直微机电器件的方法,该方法包括以下步骤:提供一整体基板,该整体基板包括一埋设的氧化物层;在该基板上选择性地建立强粘结区域和弱粘结区域;提供垂直承载于该基板上的第一粘结半导体层;在该第一粘结半导体层上建立一电极,该电极对应于所述弱粘结区域;建立一配置成与该电极相对的可激励元件;在该第一半导体层与该整体基板间的界面处形成一埋设的氧化物层;从该整体基板移除该第一半导体层;以及将该第一半导体层粘结到一第二半导体层。

在另一方面中,本发明是一种制造垂直微机电器件的方法,该方法包括以下步骤:提供一整体基板,该整体基板包括一埋设的氧化物层;在该基板上选择性地建立强粘结区域和弱粘结区域;提供垂直承载于该基板上的第一粘结层;在该第一粘结层上建立一端口,该端口对应于该弱粘结区域;机械性地创造一个通道耦接至该端口;从该整体基板移除该第一层;以及粘结该第一层至一第二层。

在另一方面中,本发明是一种制造多层微流体器件的方法,该方法包括以下步骤:提供一整体基板;在该基板上选择性地建立强粘结区域和弱粘结区域;提供垂直承载于该基板上的第一粘结半导体层;在该第一粘结层与该整体基板间的界面处形成一埋设的氧化物层;在该第一粘结层上建立一端口,该端口对应于该弱粘结区域;机械性地创造一个通道耦接至该端口;从该整体基板移除该第一层;以及粘结该第一层至一第二层。

附图说明

连同所附附图阅读下列详细的描述,前面所述摘要和本发明的较佳实施例将更被了解。此处显示出较佳的附图与实施例。然而应了解的是,本发明并不仅限制于附图所绘的形式,而附图只是帮助了解本发明而已。在附图中,其中:

图1是依据本发明的原则选择性地粘结多层基板的一个示意剖视图;

图2是依据本发明的原则选择性地粘结多层基板的一个示意剖视图;

图3是依据本发明的原则选择性地粘结多层基板的一个示意剖视图;

图4是依据本发明的原则选择性地粘结多层基板的一个示意剖视图;

图5是依据本发明的原则选择性地粘结多层基板的一个示意剖视图;

图6是依据本发明的原则选择性地粘结多层基板的一个示意剖视图;

图7是依据本发明的原则选择性地粘结多层基板的一个示意剖视图;

图8是依据本发明的原则选择粘结性地多层基板的一个示意剖视图;

图9是依据本发明的原则选择粘结多层基板的一个示意剖视图;

图10是依据本发明的原则选择粘结多层基板的一个示意剖视图;

图11是依据本发明的原则选择粘结多层基板的一个示意剖视图;

图12是依据本发明的原则选择粘结多层基板的一个示意剖视图;

图13是依据本发明的原则选择粘结多层基板的一个示意剖视图;

图14是依据本发明的原则的晶片粘结区域的几何形状的一个水平剖视图;

图15是依据本发明的原则的晶片粘结区域的几何形状的一个水平剖视图;

图16是依据本发明的原则的晶片粘结区域的几何形状的一个水平剖视图;

图17是依据本发明的原则的晶片粘结区域的几何形状的一个水平剖视图;

图18是依据本发明的原则的晶片粘结区域的几何形状的一个水平剖视图;

图19是依据本发明的原则的晶片粘结区域的几何形状的一个水平剖视图;

图20是依据本发明的原则的晶片粘结区域的几何形状的一个水平剖视图;

图21是依据本发明的原则一种晶片解除粘结技术的一示意剖视图;

图22是依据本发明的原则一种晶片解除粘结技术的一示意剖视图;

图23是依据本发明的原则一种晶片解除粘结技术的一示意剖视图;

图24是依据本发明的原则一种晶片解除粘结技术的一示意剖视图;

图25是依据本发明的原则一种晶片解除粘结技术的一示意剖视图;

图26是依据本发明的原则一种晶片解除粘结技术的一示意剖视图;

图27是依据本发明的原则一种晶片解除粘结技术的一示意剖视图;

图28是依据本发明的原则一种晶片解除粘结技术的一示意剖视图;

图29是依据本发明的原则一种晶片解除粘结技术的一示意剖视图;

图30是依据本发明的原则一种晶片解除粘结技术的一示意剖视图;

图31是依据本发明的原则一种晶片解除粘结技术的一示意剖视图;

图32是依据本发明的原则一种晶片解除粘结技术的一示意剖视图;

图33是依据本发明的原则一种晶片解除粘结技术的一示意剖视图;

图34是依据本发明的原则的电路部分的一个示意剖视图;

图35是依据本发明的原则的一基板和取置部的示意剖视图;

图36是依据本发明的原则对齐及堆栈电路部分与导体的一个示意剖视图;

图37是依据本发明的原则对齐及堆栈电路部分与导体的一个示意剖视图;

图38是依据本发明的原则对齐及堆栈电路部分与导体的一个示意剖视图;

图39依据本发明的原则的电路部分的一个示意剖视图;

图40是依据本发明的原则对齐及堆栈电路部分与导体的一个示意剖视图;

图41是依据本发明的原则对齐及堆栈电路部分与导体的一个示意剖视图;

图42依据本发明的原则的电路部分的一个示意剖视图;

图43是依据本发明的原则对齐及堆栈电路部分与导体的一个示意剖视图;

图44是依据本发明的原则对齐及堆栈电路部分与导体的一个示意剖视图;

图45是依据本发明的原则对齐及堆栈电路部分与导体的一个示意剖视图;

图46依据本发明的原则的电路部分的一个示意剖视图;

图47依据本发明的原则的电路部分的一个示意剖视图;

图48依据本发明的原则的电路部分的一个示意剖视图;

图49依据本发明的原则的电路部分的一个示意剖视图;

图50是依据本发明的原则对齐及堆栈电路部分与导体的一个示意剖视图;

图51是依据本发明的原则对齐及堆栈电路部分与导体的一个示意剖视图;

图52是依据本发明的原则对齐及堆栈电路部分与导体的一个示意剖视图;

图53是依据本发明的原则对齐及堆栈电路部分与导体的一个示意剖视图;

图54是依据本发明的原则对齐及堆栈电路部分与导体的一个示意剖视图;

图55是依据本发明的原则对齐及堆栈电路部分与导体的一个示意剖视图;

图56是依据本发明的原则对齐及堆栈电路部分与导体的一个示意剖视图;

图57是依据本发明的原则对齐及堆栈电路部分与导体的一个示意剖视图;

图58是依据本发明的原则对齐及堆栈电路部分的一个示意剖视图;

图59是依据本发明的原则对齐及堆栈电路部分的一个示意剖视图;

图60依据本发明的原则的边缘互联与电路部分的一个示意剖视图;

图61是依据本发明的原则的边缘互联的一个示意剖视图;

图62是依据本发明的原则的边缘互联的一个示意剖视图;

图63是依据本发明的原则被对齐而且堆栈的电路部分的一个示意剖视图;

图64是依据本发明的原则被对齐而且堆栈的电路部分的一个示意剖视图;

图65是被依据本发明的原则在毗邻层体间具有的屏蔽层的一个示意剖视图;

图66是依据本发明的原则在层体间具有的通道的一个示意剖视图;

图67是依据本发明的原则在层体间的传热通道的一个示意剖视图;

图68是依据本发明的原则在器件下侧的一个示意剖视图;

图69显示依据本发明的原则的电路形成区域的示意剖视图;

图70是依据本发明的原则的选择粘结电路部分的示意侧视图;

图71是举例说明依据本发明的原则解除粘结技术的一个示意剖视图;

图72是举例说明依据本发明的原则对齐层体的一个示意图;

图73是举例说明依据本发明的原则对齐层体的一个示意图;

图74是举例说明依据本发明的原则对齐层体的一个示意图;

图75是举例说明依据本发明的原则对齐层体的一个示意图;

图76是举例说明依据本发明的原则对齐层体的一个示意图;

图77是举例说明依据本发明的原则对齐层体的一个示意图;

图78是举例说明依据本发明的原则对齐层体的一个示意图;

图79是举例说明依据本发明的原则对齐层体的一个示意图;

图80是依据本发明的原则一层体堆栈的一个立体图;

图81是依据本发明的原则金属化的一个示意立体图;

图82是现有技术金属化的一个示意立体图;

图83是依据本发明的原则的金属化的示意图;

图84是依据本发明的原则的金属化的示意图;

图85是依据本发明的原则的解除粘结技术的示意图;

图86是依据本发明的原则的对准技术的示意图;

图87是依据本发明的原则的对准技术的示意图;

图88是插头的示意图依据本发明的原则装满方法;

图89是依据本发明的原则的通路互联的示意图;

图90是依据本发明的原则的机械性对齐的示意图;

图91是依据本发明的原则的机械性对齐的示意图;

图92是依据本发明的原则分类层体的示意图;

图93是依据本发明的原则分类层体的示意图;

图94是依据本发明的原则分类层体的示意图;

图95是依据本发明的原则分类层体的示意图;

图96是依据本发明的原则的取置部的示意图;

图97是依据本发明的原则的取置部的示意图;

图98是依据本发明的原则的选择粘结器件的示意图;

图99为依据本发明的原则的微机电系统器件的处理步骤的示意图;以及

图100依据本发明的原则的微机电系统器件的处理步骤的示意图。

具体实施方式

本发明与形成三维空间的集成电路有关。在讨论这些三维空间的集成电路的特定形成的之前,首先讨论被呈现的基板,如申请人于2001年12月9日提交的未决美国专利申请No.09/950,909的“关于的薄膜和制造方法”中所说明,此基板关于一个选择粘结多层基板允许晶片的多重芯片的处理如公知,但更允许晶片的芯片层易于移除而较佳地没有机械的磨砺或另外地蚀刻移除技术。这个芯片层接着可堆栈在另一个芯片层上,如以下描述,或另外地,芯片层可被切割并且堆栈至个别的芯片中。

参照图1,其显示一选择粘结多层基板100。多层基板100包括具有暴露的表面1B的层1,且表面1A选择性地粘结到层2的表面2A。更进一步层2包括相对表面2B。大体上,为形成选择粘结多层基板100,层1、层2、或层1和2都被用来界定弱粘结区域5和强粘结区域6及之后的粘结,其中弱粘结区域5具有允许处理一个有用器件或结构的条件。

通常,层1和2是兼容的。即,层1和2构成兼容的热、机械的、及/或结晶特性。在特定实施例中,层1和2是相同的材料。当然,可使用不同的材料,但是较佳地为兼容性选择。

一个或多个层1被定义为基板区域,其中或其上有一个或多个像是微电子的结构被形成。这些区域可为任何所欲的图案,本申请中将更进一步描述。层1的选定区域接着可被处理以将粘结程度减到最弱形成弱粘结区域5。或者,层2的相对区域可被处理(连同层1一起处理,或取代层1的处理)以将粘结减到最小。进一步的替代选择包括,处理选定以形成结构外的区域中的层1及/或层2,如此同样地在强粘结区域6提高强度。

在层1及/或层2的处理之后,层体可被对齐并且粘结。借着任何的适当方法粘结。另外,层的对准可为机械的、光学的、或相关的组合。应该了解由于在现阶段层1上没有被形成的结构而不可能相当地对准。然而,如果两个层1和2经处理,对准将是减少选定基板区域变异所必备。

多层基板100可提供一个使用者处理在层1或层1之上任何所需结构。因此,形成可令使用者以传统制造技术、或已知的其它技术处理作用在各种不同的相关技术发展的任何结构或器件的多层基板100。一个基板受制于特定制造技术严苛的条件中,像是高温、压力、粗劣的化学药品、或其上任一组合。因此,多层基板100为了要抵抗这些条件,较佳地被形成。

有用结构或器件可形成在区域3或在区域3之上,部分地或大体上地重叠弱粘结区域5。因此,部分地或大体上地重叠强粘结区域6的区域4通常在其中或其上方没有该结构。当一个使用者在多层基板100的层1上或层1里面形成有用器件后,层1之后可被解除粘结。解除粘结可通过任何诸如剥除的已知技术,而没有必要直接地使有用器件遭受有害的分层技术。因为有用器件通常不是形成在区域4中或区域4上,这些区域可遭受诸如离子植入的解除粘结处理,而不会伤害形成在区域3内或区域3上的结构。

为了形成弱粘结区域5,表面1A、2A、或两者都可在弱粘结区域5处被处理以形成实质上没有粘结、或弱粘结。或者,弱粘结区域5可不加以处理,而藉使强粘结区域6被处理而感生强粘结。区域4部分地或实质上重叠强粘结区域6。为形成强粘结区域4,表面1A、2A、或两者都可在强粘结区域6处被处理。或者,强粘结区域6可不加以处理,而藉使弱粘结区域5被处理而感生弱粘结。此外,两个区域5和6可以不同的处理技术处理,其中所述处理技术可为性质上地或数量地不同。

在处理一个或两个弱粘结区域5和强粘结区域6的组合后,层1和2粘结在一起而形成一个实体上积体的多层基板100。因此,在形成后,多层基板100可遭受到最终使用者的恶劣环境,例如,用以在其中或其上形成结构或器件,尤其是在层1的区域3之内或之上。

本发明说明书中所用措词“弱粘结”一般指易于克服的层体间、或部分层体间的粘结作用,例如,诸如剥除等的解除粘结技术,其它像是机械性分离、热、光、压力、或与至少包含前述解除粘结技术组合的技术。这些解除粘结技术对层1和层2造成最小的损害,特别是在邻近弱粘结区域5处。

对于弱粘结区域5和强粘结区域6的单独处理或两者一同的处理可以多种方式。关于处理的重要发明层面在于弱粘结区域5比强粘结区域6更易于解除粘结(依照之后更进一步的描述步骤解除粘结)。这在解除粘结期间将避免对区域3的伤害或将其减小到最少,区域3上可包括有用结构。此外,包含强粘结区域6尤其在结构处理其间提高多层基板100的机械完整性。因此,当移除在其中或其上具有有用结构的层1时,其后续处理将被省略或减到最少。

强烈粘结区域对弱粘结区域(SB/WB)的强度比率大体上大于1。依强粘结区域和弱粘结区域的特定组配方式、及强粘结区域对弱粘结区域的相对区域大小,SB/WB的数值可接近无限大。即,如果强粘结区域在尺寸方面和在处理的时维持机械和热稳定度的力量够大,弱粘结区域的粘结强度可趋近于零。然而,SB/WB比率可剧烈地改变,是由于强粘结的力量(在典型的硅和硅衍生物中,举例来说:二氧化硅、晶片)可从大约500(mj/m2)变化到超过5000(mj/m2),如公知技术(例如,美国纽约州John Wiley andSons出版社于1999出版,由Q.Y.Tong与U.Goesle所著《半导体晶片粘结技术》一书中第104-118页,在此作为参考)所揭示。然而,弱粘结强度可甚至因材料、理想的有用结构(如果已知)、选用的粘结和解除粘结技术、相对强粘结区域比弱粘结区域、晶片上的强粘结与弱粘结的配置或图案等等诸如此类而更剧烈地改变。例如,离子植入是用在解除层体粘结,在离子植入及/或离子植入区相对的微泡进化之后,有用的弱粘结区域力量可与强粘结区域的力量相比较。因此,SB/WB的力量比率通常大于1、或较佳地大于2、5、10、甚至更高,端视所选择的解除粘结技术和选择形成在弱粘结区域中的可选的有用结构或器件。

对于个别处理或两区域一同处理的弱粘结区域5和强粘结区域6所采取的特殊处理型式端视所选择的材料。此外,层1和层2的粘结技术选择上至少部分地依据处理法则。另外,之后的解除粘结可依据诸如处理技术、粘结方法、材料、有用结构型态或存在的结构型态、或一个至少包含前述因子之一的组合等因子。在特定的实施例中,选定的处理组合、粘结、和之后的解除粘结(即,可被一个最终使用者形成在区域3中有用结构、或者作为一较高阶器件的中介构件)不需要用分裂传播来从层2移除层1、或机械式变薄来移除层2、以及较佳地省去分裂传播与机械式变薄两种方式。因此,依据传统所揭示的分裂传播或机械式变薄有损层2,致使其本质上若未经后续处理则形同没有用,其底部基板很少甚至不被重复使用。

参照图2和3,其中位于同样区域对照相似的参考数字,一种处理技术包括利用表面1A、2A、或1A与2A上含有一固态组件和一可分解组件的浆料。固态组件可为矾土、氧化硅(SiO(x))、其它的硬金属或金属氧化物、或其它将层1和层2的粘结减到最小的其它材料。可分解组件可为乙烯聚合物(PVA)、或其它适合的可分解聚合物。一般,浆料8施用在弱粘结区域5的表面1A(图2)、2A(图3)、或1A与2A两者。接下来,层1及/或层2可被加热,较佳地在惰性环境中分解聚合物。因此,渗透结构(包含浆料的固态组件)保持在弱粘结区域5,且一旦粘结,层1和层2在弱粘结区域5不粘结。

参照图4和5,另一处理技术可依照弱粘结区域5和强粘结区域6间的表面粗糙度变化。表面粗糙度可在表面1A(图4)、表面2A(图5)、或表面1A和2A上调整。大体上,弱粘结区域5可有较高于强粘结区域6的表面粗糙7(图4和5)。例如,在半导体材料中,弱粘结区域5可有约大于0.5纳米(nm)的一个表面粗糙度,而强粘结区域4可有一较低的表面粗糙度,通常约少于0.5nm。在另一个例子中,弱粘结区域5可有约大于1nm的表面粗糙度,而强粘结区域4可有一较低的表面粗糙度,通常少于约1nm。又另一个例子中,弱粘结区域5可具有约大于5nm的一表面粗糙度,而强粘结区域4可有一较低的表面粗糙度,通常约少于5nm。表面粗糙度能以蚀刻调整(例如,以KOH或HF的解决方式)或沉积程序修改(例如,低压化学气相沉积(LPCVD)、或电浆增强式化学气相沉积(PECVD))。与表面粗糙度有关的粘结力量更完全描述于,例如,电气化学期刊第148(4)G225-G228(2001)期,Gui等的“控制表面粗糙度的选择性晶片粘结”技术,于本申请中作为参考。

相同地(其中相类似的所在区域参照图4和5中相类似的附图标记),一个多孔区域7可被形成在弱粘结区域5,且强粘结区域6可保持不受处理。因此,层1由于弱粘结区域5的渗透性而在弱粘结区域5处与层2最微弱地粘结。渗透性可在表面1A(图4)、表面2A(图5)、或表面1A和2A上调整。大体上,弱粘结区域5在多孔区域7有较高于强粘结区域6的渗透性(图4和5)。

另一处理技术可依据选择性蚀刻弱粘结区域5(在表面1A(图4)、2A(图5)、或1A和2A),接着在该蚀刻区域施以一光阻或其它含碳材料的沉积(例如,包括聚合物为基材的可分解材料)。一旦层1和层2粘结,较佳地在足以分解载体材料的温度,其中包括一渗透性含碳材料的弱粘结区域5,使得层1和层2间在弱粘结区域5的粘结相较于层1和2间在强粘结区域6的粘结是非常弱的。本领域技术人员可明了视情况选择不会外泄气体、脏污的分解材质、或其它弄污基板层1或2分解材质、或任何有用结构形成在区域3或在区域3上的分解材质。

进一步的处理技术可使用放射来获得强粘结区域6及/或弱粘结区域5。在此技术中,层1及/或层2以中子、离子、质子束、或述的组合来辐射而获得所需强粘结及/或弱粘结。例如,诸如He+、H+、或其它适当的离子或质子、电磁能量、或激光束可在强粘结区域6辐射(在表面1A(图10)、2A(图11)、或1A和2A)。应该了解的是,此放射方法与离子植入法的不同在于,其为了分层通常在剂量及/或植入能量是少很多的。(例如,用于分层的剂量依照第1/100到第1/1000的量级)

参照图8和9,更进一步的处理技术包括蚀刻弱粘结区域5的表面。在此一蚀刻步骤,柱状物9被定义于表面1A(图8)、2A(图9)、或1A和2A上的弱粘结区域5中。柱状物可以选择性的蚀刻、留下柱状物来定义。柱状物的形状可为三角柱形、金字塔形、矩形、半球形的、或其它适当形状。或者,柱状物可在被蚀刻的区域中被植入或沉积。由于只有很少的粘结区来让材料粘结,在弱粘结区域5的整体力量远小于在强粘结区域6的粘结。

尚有另一处理技术,其关于在层1(图12)、层2(图13)的弱粘结区域5中利用诸如蚀刻、机制、或两者(视使用的材料而定)形成包括一个空区域10(图12和13)。由此,当第一层1粘结到第二层2时,空区域10将使粘结减到相对于强粘结区域6最小的力量,来促进之后的解除粘结。

再次参照图2和3,又另一种处理技术关于在表面1A(图2)、2A(图3)、或1A和2A上的弱粘结区域5包括一个或多个金属区域8。例如,包括但不限定的铜、金、铂、或其它任何组合或合金可在积设在弱粘结区域5上。一旦层1和层2粘结,弱粘结区域5将会微弱地粘结。强粘结区域可保持不受处理(其中该粘结力量差提供有关弱粘结层5与强粘结区6所必要的强粘结对弱粘结比率)、或可以前述或之后将叙述的处理来增强粘着。

一种进一步的处理技术关于在表面1A(图10)、2A(图11)、或1A和2A上的强烈粘结区域6包括使用一个或多个增进粘着物11。适当的增进粘着物包括、但是不限为:TiO(x)、金属氧化物、或其它的增进粘着物。另一可选择的,增进粘着物可用于大至上所有的表面1A及/或2A,其中一种金属材料被置于增进粘着物与弱粘结区域5的表面的1A或2A(视增进粘着物所在现场而定)间。因此一旦粘结,金属材料将避免在一弱粘结区域5的强粘结,而在强粘结区域6的增进粘着物促进强的粘结。

尚有另一种处理技术包括提供排水性及/或亲水性的变化区域。例如,亲水性的区域对强粘结区域6是特别有用的,因为像是硅的材料可自然地在室温下粘住。公知利用排水性和亲水性在室温和升温的粘结技术,揭示于John Wiley and Sons出版社于1999出版,由Q.Y.Tong与U.Goesle所著《半导体晶片粘结技术》一书中第49-135页中,于本申请中作为参考。

又另一处理技术包括一个或多个被选择地幅射的剥落作用层。例如,一个或多个剥落作用层可被放置在表面1A及/或2A上。没有放射的情况下用剥落作用层形同粘着物。一旦弱粘结区域5中暴露在诸如紫外光幅射的幅射下,粘着特性被减到最低。有用结构可在弱粘结区域5或弱粘结区域5之上被形成,而一后续的紫外光放射步骤或其它的解除粘结技术,可用来在强粘结区域6分开层1和层2。

参照图6和7,额外的处理技术包括植入离子12(图6和7)来使弱区域3中的层1(图6)、层2(图7)、或两个层1和2中一经热处理即能够形成多个微泡13。因此,当层1和层2被粘结,弱粘结区域5将粘结得比强粘结区域6少,以促进在弱粘结区域5的层1和层2之后的解除粘结步骤。

另一种处理技术包括一个仅紧跟着一个蚀刻步骤的离子植入步骤。在此一实施例中,这技术经由离子植入大致上所有的表面1B来实行。其后,弱粘结区域5可选择性地蚀刻。此一方法参考辛普森等人于电气化学固态文件第4(3)G26-G27的“铟磷化物的植入感生选择性化学蚀刻”中关于选择损害蚀刻移除的缺点的描述,此处作为参考。

又另一处理技术可知,选择地放置在弱粘结区域5及/或强粘结区域6的具有幅射及/或反射特性的一个或多个层,可依据窄或宽的波长范围为基础。例如,选择地放置在强粘结区域6的一个或多个层可依视暴露在特定幅射波长下而有粘着的特性,如此层体吸收幅射而粘结强粘结区域6处的层1和2。

本领域技术人员可明了,被使用任何额外的处理技术、以及包含组合至少其中一种前述技术的技术。然而,任何所采用技术的关键特性在于形成一个或多个弱粘结区域和一个或多个强粘结区域的能力,使得SB/WB力量比率大于1。

弱粘结区域5和强粘结区域的几何形状6在层1和层2间的界面可依据包括但不限定的下列因子来改变:形成在区域3或区域3上的有用结构种类、所选的解除粘结/粘结型式、所选用的处理技术、及其它因素。参照图14-20,多层基板100可具有可为同心的(图14、16、和18)、有条纹状的(图15)、放射状的(图17)、格状的(图20)、或组合格状与环形的(图19)、或任何上述形式组合的弱粘结和强粘结区域。当然本领域技术人员可判断可如何选用任何几何形状。此外,强粘结区域对弱粘结区域的比率可改变。一般而言,比率提供充份的粘结作用(即,在强粘结区域6)而不需包含整个多层结构100,尤其是在结构处理的期间。较佳地,此比率还使结构处理的有用区域(即,弱粘结区域5)达最大。

实质上如前述的弱粘结区域5及/或强粘结区域6的一表面或两表面1A和2A被处理后,层1和2粘结在一起形成一个实质上整体的多层基板100。层1和2可借着多种技术及/或物理现象被粘结在一起,包括、但不限为:共融合金、熔合、电镀、真空、凡得瓦耳力、化学粘着、排水性、亲水性、氢粘结、库伦力,毛细作用力、极近距力、或至少包含前述粘结技术之一及/或物理现象的组合力等。当然本领域技术人员可明了粘结技术及/或物理现象端视所使用的一个或多个处理技术、在其上或在其中形成的有用结构型态、预期解除粘结方法、或其它的因素而择以用之。

另一可选用方式,一个埋设的氧化物层可形成在器件层的底表面。氧化物层可早于器件层的选择性粘结之前形成到整体基板。此外,氧化物层可以氧气植入至一需要埋设氧化物层的深度。

在多层基板上形成一氧化物层有各种不同的技术。第一种在硅基板中形成埋设的二氧化硅层的技术是通过植入高浓度的氧后于高于1300℃的温度下磨。经过离子植入,可形成所欲的埋设的二氧化硅层的厚度。

形成一个埋设氧化物层的另一可选用技术包含在多层基板的一个表面上形成一个薄的二氧化硅薄膜,然后经由二氧化硅薄膜粘结基板至一第二硅基板。然后利用已知机械研磨和抛光来形成一具有所需厚度的硅层于被埋设氧化硅层上。多层基板上的氧化硅层是以连续地氧化表面、接着蚀刻该依序形成的氧化表面来获得所需要的厚度的形成。

另一种形成一埋设的氧化物层的技术,其借着氧化在一第一多层基板上的一个薄的氧化硅层,接着植入H+离子在第一多层基板中以形成在薄氧化硅层下面的一个空腔平面。其后,透过薄氧化硅层,第一本体被粘结到一第二多层基板,然后整个总成受制于热作用下来把空腔平面转变成一个裂开平面。如此可回复一可使用的SOI基板。

多层基板100由此可供给一个最终使用者(具有或没有一个埋设的氧化物层)。或者,导体的特定图案可与多层基板一同积设。最终使用者之后可在大体上或部分地重叠表面1A和2A界面处的弱粘结区域5的区域3或其上形成一可用结构(不显示)。可用的结构可包括一个或多个主动或被动元件、器件、装备、工具、通道、其它有用结构、或至少包含前述有用结构的任何一种的组合。例如,可包括一个集成电路或一个太阳能电池。当然,本领域技术人员可领会可形成各种不同依据微技术和纳米技术的器件。

例如,有源器件可形成在多层SOI晶片或基板上。这些有源器件形成于SOI基板的埋设氧化物薄膜上的单晶硅有源层中。硅有源层的厚度端视其中形成有源器件的目的而定。如果SOI元件是在高速和低耗电量之下操作的互补型金属氧化半导体(CMOS)元件,有源层厚度大约为50nm至100nm。如果SOI元件是高崩溃电压元件,有源层厚度可为几微米。一个保护性二极管是有源器件的一种例子。一保护性二极管供给一半导体设备的半导体元件,使其前导一过电流从一个连接引脚到一基板及到半导体器件的外部,藉此保护半导体设备的内部电路。

本领域技术人员可相当明白其它有源器件可以选择性搀杂和屏蔽单晶硅基板或SOI基板来制造。有源器件可包括、但不限制为:双极接面晶体管、金属氧化物半导体晶体管、场效晶体管、二极管、绝缘闸双极晶体管、及诸如此类。

另外可在多层基板上制造的有源器件是微机电系统器件。通常,微机电系统器件已包含电极、以及相对于基板上的已制造电极配布的可激励元件。可激励元件从电极转移控制来对机器结构提供电气控制。借着利用深蚀刻处理的整体微机械加工基板为制造微机电系统器件的一种技术,其采用减去型制造技术是因为其涉及自一个单一基板层蚀掉材料来形成MEMS结构。基板层可为10微米级而相对地厚,且此方法的精密程度使得基板中不同结构的微机械加工,诸如悬桁、桥接、渠、空腔、喷嘴、和薄膜。

另外一种可在多层基板上制造微机电系统器件的技术是借着表面的显微机械加工技术。它被视为一种附加方法是因为间隔的结构层与牺牲的空间层是以“往上建”来实现微机电系统结构的机械和电特性造。多晶硅(polysilicon)是最普遍使用的结构材料,而且氧化硅玻璃是最普遍使用的耗材。在传统的微机械加工程序中,这些层形成为硅基板上以一层硅氮化物隔离的多晶硅/氧化物对。这些层使用光学平版印刷术形成复杂的结构,像是电动机、齿轮、镜子和波束。当层被建立,切过氧化物层并以多晶硅填满来定位上结构层或底结构层。

在层1的一个或多个选择区域3或之上形成一个或多个结构后,层1可以多种方法解除粘结。可知,由于结构被形成在部分地或大体上地覆盖弱粘结区域5的区域4中或区域4上,层1的解除粘结可取而代之将与诸如结构缺点或形变有关的传统中对结构的伤害减少或消除。

解除粘结可通过多种公知的技术来完成。一般而言,解除粘结技术至少部分地端视处理技术、粘结技术、材料、型态、或可用结构的存在与否,或其它的因子。

参照图21-32,解除粘结技术可依据离子或质子的植入在一个参考深度形成微泡,一般与层1的厚度相等。离子或质子可衍生自氧、氢、氦、或其它的粒子14。被植入后可被强电磁幅射、热、光(例如,红外光或紫外线)、压力、或至少包含前面所述的一种组合,使得粒子或离子形成微泡15而最终扩大而使层1和2分层。植入、以及选择性的加热、光、及/或压力处理后也可跟随一机械隔离步骤(图23、26、29、32),例如,以一与层1和2垂直的方向、一与层1和2呈一角度的方向、一削除方向(如图23、26、29、32中断线所指示)、或上述方向的一个组合。例如,在Cheung等的名为“使薄膜自整体基板分离的电浆浸渍离子植入方法”的美国专利No.6,027,988案中进一步的细述分离薄层的离子植入法,于本申请中作为参考。

特别参照图21-23和图24-26,在层1和层2之间的界面处可选择性地植入,特别地在强粘结区域6形成微泡17。以此方式,粒子16在区域3(在其中或其上具有一个或多个可用的结构)的植入被减到最少,如此可能对区域3中有用结构减少可修理的可能性或发生不能修补的损害。选择性的植入可以选择的离子束扫瞄强粘结区域4(图24-26)或屏蔽区域3(图21-23)。选择的离子束扫瞄参照结构100的机械处理及/或用于指示将被植入的离子或粒子的器件。本领域技术人员可知,各种不同的器件和技术可用来实行选择性扫瞄,包括但是不限于着重在离子束和电磁波束。此外,各种屏蔽材料与技术也广为人知。

参照图27-29,植入可实质上穿过整个表面1B或2B。端视目标与植入材料而植入在适当层次以及所希望的深度。因此,层2远比层1厚许多的地方,植入穿过表面2B是不实际的;然而,如果层2以适当的厚度植入(例如,以可实行的植入能量),穿过表面2B的植入是令人想要的。这将减少可修理的可能性被除去、或减少可能对在区域3中有用结构发生的不能修补的损害。

在一实施例中,并参照图30-32及图18,强粘结区域6在层1和层2间界面的外缘形成。因此,例如,要从层2解除粘结层1,可植入离子18通过区域4来在层1和层2间的界面处形成微泡。较佳地,使用选择性扫瞄,其中该结构100可被旋转(箭号20所指方向),扫瞄装置21可被旋转(箭号22)、或其中的一种组合。在此一实施例中,一更进步的优势在于给予最终使用者在选择其上可用的结构方面提供了很大的灵活度。强粘结区域6的大小(即,宽度)适于维持多层基板100的机械和热的完整性。较佳地,强粘结区域6的尺寸被减到最小,使得弱粘结区域5用来作结构处理的区域最大化。例如,强粘结区域6在一八时晶片上可约为一微米。

此外,自层2解除粘结的层1的可被其它诸如蚀刻这样的传统方法像(平行表面)方法开始形成一穿过强粘结区域6的蚀刻。在如此一实施例中,处理技术是特定可兼容的,例如,其中强粘结区域6与一具有远高于整体材料(即,层1和层2)的蚀刻选择性的氧化物层一起受处理时。弱粘结区域5较佳地不需要在弱粘结区域5处蚀刻以从层2解除粘结层1,由于选择性处理或不处理,避免了将层1粘结到层2的步骤。

或者,断裂传播可用来从层2开始解除粘结层1。再一次,解除粘结较佳地仅需在强粘结区域6处,是因在弱粘结区域5的粘结有限。且如公知所知,解除粘结可以蚀刻(垂直表面)开始而较佳地限制在区域4的现场(即,部分地或大体上地重叠强粘结区域6)。

在另一实施例中,并参照图85,其显示一解除粘结的方法。包括提供一个多层基板100;在WB区域5中处理一个或多个有用结构(不显示);在SB区域6蚀刻掉,较佳地以一逐渐变小的角度(例如,45度);使器件层较佳地只有在被蚀刻的SB区域6受到低能量离子植入;以及在WB区域削去或简单地移除器件层部分。注意,当在WB层的二器件层如所示地被移动时,可了解这可用来促进器件层部分的释除。WB区域逐渐变小的边缘物理性地促进移动。有益地,可利用远低于渗透原本器件层厚度所需植入能量的离子植入能量。

层1和层2可为一样的或不同的材料,且材料可包括、但不限于:塑料(例如,聚合碳)、金属、半导体、绝缘体、单晶体、非晶形的、非晶体、生物的(例如,DNA薄膜)、或至少包含前述材料之一的组合。例如,特定类型的材料包括硅(例如,单晶、多晶、非晶、硅聚合物和衍生物如Si3N4、SiC、SiO2)、砷化镓、InP、CdSe、CdTe、SiGe、GaAsP、GaN、SiC、GaAlAs、InAs、AlGaSb、InGaAs、ZnS、AlN、锡、其它IIIA-VA的材料、IIB材料、VIA材料、蓝宝石、石英(水晶或玻璃)、钻石、硅石及/或硅酸盐基材料,或包含至少前面材料之一的任何组合。当然,其它的材料类型的处理可受益于此处描述的方法来提供理想的多层基板100组成。尤其在此处描述的方法是特别适用于以半导体材料(例如,硅)作为层及以半导体材料(例如,硅)作为层2,其它的组合包括但不限制在:半导体(层1)或玻璃(层2);在蓝宝石(层2)上的半导体(层1),硅碳化物(层2)上的半导体(层1);在蓝宝石(层2)上的GaN(层1);在玻璃(层2)上的GaN(层1);在硅碳化物(层2)上的GaN(层1);在塑料(层2)上的塑料(层1),其中层1和层2可为相同或不同的塑料;以及在玻璃上(层2)的塑料(层1)。

层1和层2可衍生自各种不同的来源,包括被沉积以形成薄膜及/或基板结构的晶片或液体材料。其中起始材料可为一晶片的形式,任何的传统程序可用来衍生层1及/或2。例如,层2可有一晶片,而层1可包含一样的或不同的部分晶片。构成层1的晶片部分可起源于机械式薄化(例如,机械磨砺、切割、抛光、化学机械式抛光、抛光-停止、或包括至少前述方法之一的组合)、断裂传播、后续机械式隔离的离子植入(例如,断裂传播、垂直结构100的平面、平行结构100的平面、在一削除方向,或其中一组合)、后续热、光、及/或压力感生的层体分离的离子植入法、化学蚀刻、或诸如此类。此外,层1和层2可被沉积或植入,例如,以化学蒸镀、种晶法等。

此方法、和产生的多层基板、或从多层基板衍生的薄膜的一种重要优势在于形成在区域3或在区域3上的,部分地或大体上地重叠弱粘结区域5。当层1被从层2移除时候,实体上将除去对有用结构的伤害或使的减到最少。解除粘结步骤通常需要浸入(例如,通过离子植入)、施力、或其它解除粘结层1和2必需的技术。由于在特定的实施例中,区域3或在区域3之上的结构不需要区域浸入、施力、或可能造成不一定可修理的结构损害的其它程序步骤,层1及自其衍生的结构可被移除而不需之后的维修处理。通常部分地或大体上地重叠于强粘结区域6的区域4上不具有结构,因此这些区域4可受于对结构无伤的浸入或力量。

层1可被移除作为自我支持薄膜或一个支持性的薄膜。例如,取置部一般用来附着层1使得层1可从层2移除、以及保持被取置部拖承。一般取置部可用来在之后放置薄膜或在所欲基板上的一部分(具有一个或多个可用结构)、另外加工的薄膜,或余留该取置部。

本方法的一种优势在于构成层2的材料是可被重复使用且可回收的。例如,可使用一个单一晶片以任何已知方法衍生层1。衍生的层1可在其上选择地粘结依照描述所余留的部分(层2)。当薄膜被解除粘结时,重复步骤,使用层2的余留部分获得一薄膜作为下一层1。直到不再能实行或无法再使用层2的余留部分衍生层1的薄膜前此方法可不断重复。

在如此详述一选择性粘结多层基板的形成方式后,此后将描述利用选择性粘结多层基板形成三维空间集成电路。

参照图80,其中显示从第1…第N晶片堆栈及从中切割的一晶粒的等角示意图。为使清楚而说明坐标和定义。一晶粒和晶片堆栈通常具有顶表面与底表面、以及向x和y坐标方向延伸的夹层,如一般所指的平面方向。注意平面方向包括在表面或在夹层上延伸的任何方向。一些层体在z方向上堆栈,在此处一般称为垂直地或在三维中。

在一晶粒切割步骤后,一晶粒除了夹层和顶端和底部的表面之外,通常尚有在z方向中延伸的四个边缘表面。

现在参照图33,具有一选择性粘结基板100,其具有如同前述的强粘结区域3和弱粘结区域4。虽然显示实施例中的强粘结图案约如图18所示,但可了解可利用任何图案的强粘结区域3和弱粘结区域4,其中一电路或其它有用器件依前述在弱粘结区域形成。

特别地,本发明可提供较IBM的美国专利No.6,355,501更具优势,在于本发明具有许多附加功能、以及效能增强同时减少连续处理步骤数量。

作为范例的,以一虚线圆圈显示一区域,且此区域的另外选择例将以各种不同的分解示意图来解释适于在三维空间堆栈的电路区域的形成。

参照图34,显示电路部分的一个例子,其具有适用为三维空间积设的芯片边缘互联结构。更细部的边缘互联结构可参照在Faris所有的美国专利No.5,786,629和6,355,976,两者于本申请中作为参考。

一个电路部分C在形成在选择粘结层基板的器件层的一个绝缘区域1。可为电的或光学的一导体W可从电路部分开始而延伸到电路封装边缘地被形成,以虚线表示。导体W通常可在x-y平面中的任何方向上延伸。整体区域在电路部分和导体处理期间作为机械的和热的支持。

应该了解到当只显示一个单一导体时(在此之前和之后所有的实施例),多个导体可被提供与一般在x-y平面的任何方向上延伸的各电路部分相联。这些导体可用自身的地址来编码每个电路部分;接受来自外部地址线的地址信息;携带数据并供电每个电路部分;接收来自电路部分(内存)的资料;或其它所需功能性。当使用复合导体时,这些导体可为独立的或多余的。

在一个实施例中,特别当其中形成一些独立导体时,半导体制程中所公知的,重叠区域被绝缘。

电路部分可为一样的或不同的,且可以各种不同的晶体管和二极管形成。这些器件包括(在一样的垂直集成电路里面)一样的或不同的微处理机(电的或光学的)(双极电路、CMOS电路、或任何其它的处理电路),内存电路部分,诸如单器件记忆单元、DRAM、SRAM、动画制作软件、讯号接收及/或传输电路功能、或诸如此类。因此,可以本方法形成各种不同的产品。积体式产品可针对多种联机和无线设备而包括处理器和内存、或处理器、内存讯号接收及/或传输电路功能。通过垂直地(在z方向上)积设,非常密集的芯片改良处理速度或内存储存量达N的系数(N表示积设的总层数,可为一位数、两位数、甚至三位数的量)。

参照图35,一个取置部是用来协助移除器件层。如上述,强粘结区域通常受制于促进解除粘结的步骤下,例如,离子植入。器件层因而可如前所述轻易地被移除(例如,有关图23、26、29、和32)而毋需传统的磨砺或其它蚀刻的步骤。由于电路部分与导体在弱粘结区域中形成,它们通常不会在这一个移除步骤期间受损害。在一较佳实施例中,所使用的取置部如2002年10月2日申请的PCT专利申请PT/US/02/31348名为“处理易碎对象的器件和方法及相关制造方法”中所述,于本申请中作为参考。

具有多个电路部分及边缘延伸导体的器件层如图36所示对齐与堆栈,于此处的进一步的描述。层体被对齐而且堆栈以致于多个电路部分形成一个垂直积体堆栈。视垂直集成器件所需而每个层的电路部分可为相同或不同的。

在一较佳实施例中,N个层体被堆栈,而后来所有的N层在一个单一步骤中粘结。例如,可通过使用紫外线或热处理在层体间的粘着物来完成。注意,因为互联位在每个芯片的边缘,在某些实施例中使电路部分本身接触到粘着物可能不会有害。虽然不是必需,但可减少处理步骤及最终成本。

现在参照图37,电路部分的每个堆栈依据公知技术切割。在切割步骤不会提供边缘平滑而为平面的情况下,布线边缘可被抛光以使每个电路部分接触到导体。

图38显示多个具有导体W的电路部分的边缘互联(电的或光学的)。可以公知的方法借着屏蔽和蚀刻导体材料沉积的薄膜以电气连接各电路部分来完成。其它的互联方法在前述美国专利No.5,786,629和6,355,976中被更详细地描述。

值得注意的重点在于边缘互联能作用在垂直积设芯片处理期间以及最终产品(垂直积设芯片)中。处理期间边缘互联可作为诊断之用。于是可在多个电路部分的互联期间避掉发生故障的电路部分。或者,发生故障的电路部分可被修理。又另一替代选择实施例,一个N层堆栈的电路部分可被缩减(即,水平地沿着电路部分平面)来除除发生故障的电路部分,而提供二层以上N层以下的堆栈N。某些应用中使用二或更多的堆栈而各堆栈有少于N层的电路部分层,取代舍弃具有一个或多个发生故障的电路部分的N层堆栈,可剧烈地增加已知良品晶粒(KGD)的整体生产量。

此后参照图38,在一个另一可选择的实施例中,一个垂直积设的边缘互联堆栈能提供一种本发明的第二垂直IC的垂直积设。如在图38所示,积体边缘堆栈互联有效地绕其垂直轴旋转而形成一个布线堆栈。借着将旋转的积体边缘堆栈粘结到第二垂直IC,可实现布线适应性。例如,旋转的积体边缘互联堆栈能在一水平的规模中提供超过一层的布线适应性的。例如,这对一个需要多重寻址线和控制电路以寻址与控制的大量数据储存芯片所需的控制电路是有用的。

在一个进一步的实施例中,边缘互联可作为大量储存寻址(MSA)如前述美国专利No.6,355,976所描述。

参照图39,显示电路部分的另一个例子,其具有适应于三维空间积体的通路互联结构。一电路部分C在选择粘结分层基板的器件层的一绝缘区域I里面被形成。可为电气的或光学的导体W可操作自电路部分开始而延伸到多层基板器件层的底部。每个电路封装以虚线表示。整体区域在电路部分和导体的处理期间作为机械的和热的支持。导体W(如前述可与各电路相关联)可延伸到器件层的底部侧缘,或者可自器件层底部侧缘的方向中延伸、藉此抛光步骤被执行以使垂直互联接触到导体。

接着一个取置部可利用来移除器件层,通常如图35所示。

器件分层堆栈有多个电路部分,而后如图40所示透过导体被对齐及堆栈,接下来有进一步的描述。层体被对齐及堆栈以致于多个电路部分形成一个垂直积体堆栈。视垂直集成器件所需而每个层的电路部分可为相同或不同的。

在一较佳实施例中,N个层被堆栈,而后续所有N层在一个单一步骤中粘结。例如,这可实现以通过使用紫外线或热处理在层体间的粘着物。而为了要避免垂直层体间的接触问题,取置部中应该避免粘着物。

恰如图41中显示的,每个电路部分堆栈依据已知技术切割。

参照图42,其显示电路部分的另一个例子,其具有顺应三维空间积设的混成边缘互联与通路互联。一个电路部分C在选择粘结分层基板器件层的绝缘区域I里面被形成。可为电气的或光学的导体Wt可操作自电路部分开始而延伸到多层基板器件层的底部。可了解的是,Wt也可用为一个机械的耦合器,例如,一个微机电系统器件。另一个导体We可从在电路部分开始延伸到电路封装的边缘,以虚线所示。整体区域在电路部分和导体的处理期间作为机械的和热的支持。导体Wt(如前述可与各电路相关联)可延伸到器件层的底部侧缘,或者可自器件层底部侧缘的方向中延伸、藉此抛光步骤被执行以使垂直互联接触到导体。可了解的,导体Wt和We能被制造于沿着晶片的预定位置以使边缘延伸导体能沿着晶片边缘任何地方制造。

接着一个取置部可被利用来移除器件层,通常如图35所示。具有多个电路部分与边缘延伸导体的器件层之后如图43所示对齐及堆栈,而此处进一步的描述。层体被对齐及堆栈以使多个电路部分形成一个垂直积体堆栈。视垂直集成器件所需而每个层的电路部分可为相同或不同的。

在一较佳实施例中,N个层被堆栈而其后所有的N层在一个单一步骤中粘结。这可通过使用例如,紫外线或热处理粘着物来实现。

现在参照图44,每个电路部分堆栈依据公知技术切割。在切割步骤中造成的不平滑非平面的边缘情况下,可抛光布线边缘以使每个电路部分接触到导体We。

图45显示整体互联的一个层面,多个电路部分以导体W′(电的或光学的)边缘互联。可以公知的方法借着屏蔽和蚀刻导体材料沉积的薄膜以电气连接各电路部分来完成。其它的互联方法在前述美国专利No.5,786,629和6,355,976中被更详细地描述。

注意,当边缘通路互联两者皆被使用时,可利用同一型或两类型来互联电路部分。相异互联可为多余的或独立的。或者,边缘互联可用作为诊断的目的,如同前述。在一个更进步的替代实施例中,两类型的互联可用来提供多余,藉此减少垂直积体芯片肇于芯片部分间互联所发生故障的可能。

为形成通路导体(如图39和42所示),每芯片部分的每个通路导体可首先被形成(例如,通过蚀刻一个洞而用传导性材料填补该洞),于是电路部分形成在导体顶上。

另外,参照图46,电路部分C可首先形成在第一在器件层之上或在器件层,且通路导体W从电路部分的顶端延伸到器件层的顶端。电路部分上面的区域可被处理以提供导体W和绝缘材料I(与该绝缘体相同的材料以达最佳匹配性)。

现在参照图47,其中同类附图标记表示之前图46中相同的结构,图中显示另外可选择的增强垂直的电路部分互联的特性。通常在各电路部分的顶端具有导体Wb。导体Wb作为优化来自堆栈层体上的通路导体Wt。导体可包含固态材料以使得自一堆栈的接触体有效提供层体间的接触。或者,导体Wb可包含焊料块,以使毗邻的导体可通过加热结合。或者又另一种可用方式,导体Wb可包含毗邻电路部分间的电连结。又,导体Wb可为包含光学波导的纯光学连接。导体的结合可以在堆栈每个层时、或较佳地在所有N层已堆栈后来实现,而使许多回流操作引发的导体连接伤害减到最少,如上述IBM的美国专利No.6,355,501所描述。

在另一个形成通路导体的方法(如图39和42中所示)、以及现在述及的图48-50,分离的器件层可形成电路部分层。参照图48所显示,一个具有电路部分的器件层,每个器件层具有与其它具有通路接触体的器件层接触的导体Wb。导体Wb可具有焊料块或永久固态导体。注意第二个导体Wb部分可如参照图47的前述内容提供来自堆栈上层体的通路导体Wt的传导。图49显示一个具有通路连接Wt的器件层。层体可如图50所示以堆栈、粘结、及结合电接触器件来提供一个包含电路部分层和导体层的子堆栈。

现在参照图51,其中显示另一可选择的电路部分层。一个埋设的氧化物层(BOx)形成在一般在整体基板与器件层间的界面处的器件层中。公知技术中此埋设的氧化物层可以各种不同的方法形成,像是O+离子植入法。此外,埋设的氧化物层可在器件层被选择性地粘结到整体基板之后或之前被形成。

在埋设的氧化物层于器件层被选择性地粘结到整体基板之前形成的实施例中,一个SiOx层可在选择性粘结到整体基板前被形成在器件表面。器件层于是选择性地粘结到整体基板。注意其可令人满意地在粘结之前先处理氧化物层而增强粘结。

在埋设的氧化物层于器件层被选择性地粘结到整体基板之后形成的实施例中,器件层可被例如,氧气植入以在理想深度处形成氧化物层,即,以整体基板和器件层间的界面。屏蔽器件层欲强粘结的区域来区域性地避免强粘结区域氧化是令人满意的。

在埋设的氧化物层形成后,电路部分C毗邻于器件层上弱粘结区域中的埋设氧化物形成。导体W2以电气或光学形成(例如,沉积)与电路部分的接触,且导体W1是以电的或光学的与导体W2接触。注意导体W1和W2可在一个步骤中或在多个步骤中形成。同时,当导体W1和W2显示成T形时,这些导体(或一个相同作的单一导体用)可为L形、矩形、或任何其它的适当形状。

在器件层从整体基板(如上述)移除之后,埋设的氧化物层被暴露出。如图52所示,一个埋设的氧化物层区域可被蚀刻离开,而通路导体W3在其中形成。导体W3用作为一堆栈上器件层及其毗邻导体W1的互联。

虽说所述方法在某些层面上相似于IBM的美国专利No.6,335,501中对于芯片规模的揭示,不过本发明的方法有多种优势。在上述的前案中,整体基板移除仅通过磨砺与蚀刻,然而本发明的方法上有削除或其它的更容易的移动方法,其基于弱粘结区域形成的电路部分、以及强粘结区域的存在以支撑至整体支持基板的层体,如上所述。此外,本发明的方法可在一晶片规模上获得。满意的生产率可通过层体测试、及后续利用很多N层及少于N层的堆栈所导致,依照上面的描述。

现在参照图53,另一可选择的电路部分层与其相联导体的实施例如所示。一个埋设的氧化物层(BOx)形成在整体基板和器件层间的界面的器件层中。一个导体在电路部分形成区域的BOx上形成。电路区域被形成,而导体W2和W3(或一整个导体)在电路部分的顶上被形成。注意导体W1(或导体部分)以逐渐变小的边缘和一个凸出腹部分--这用作为在其它的材料之中促进对准及提高导体的机械完整性。

现在参照图54,当器件层从整体基板(依上述,可利用削除)被移除后,埋设的氧化物层接着被暴露而形成W3区域。较佳地,这些区域与逐渐变小的导体或导体部分W1的形状和大小相符合。

如图55所示在W3区域中,一个焊料栓塞被提供作为最后地形成导体W3。这导体W3作为与一相邻堆栈上器件层的导体W1互联层,如图56所示。

当层体堆栈的时候,在一个实施例中,堆栈的层体可被回流作为将被堆栈的层体。在一较佳实施例中,在N层层体形成之后,整个的堆栈受制于回流处理。还有另一个实施例,堆栈可在部分区段中回流。

可知分离层的导体W1和W3的形状和角度更进一步协助机械性地对齐被堆栈的层体。

现在参照图64,显示更进一步形成一个三维空间电路或内存器件的器件层的一个的实施例。一个埋设的氧化物层(BOx)通常形成在整体基板和器件层界面的器件层中。这一个埋设的氧化物层可被各种不同公知方法形成。此外,埋设的氧化物层可在器件层选择性地粘结整体基板之前或之后形成。注意,具有BOx的器件层可如上述移除以衍生一个“未经处理”的SOI晶片层,该层可供给一个消费者或储存给之后的处理。

在器件层选择地粘结整体基板之前形成埋设的氧化物层的实施例中,一SiO2层可在器件层选择地粘结整体基板之前形成于整体基板表面。器件层接着选择性地粘结到整体基板。注意其可令人满意地在粘结之前先处理氧化物层而增强粘结、或屏蔽器件层欲强粘结的区域来区域性地避免强粘结区域氧化。

在器件层选择地粘结整体基板后形成埋设的氧化物层的实施例中,器件层可以例如,氧气植入于所需的深度来形成氧化物层,即,整体基板和器件层间的界面处。

在埋设的氧化物层形成之后,电路部分C毗邻于器件层上弱粘结区域中的埋设氧化物形成。一个或多个导体W以电气或光学形成(例如,沉积)与电路部分的接触,且可延伸到芯片的任何空间边缘,如同上述。

在此描述在器件层从整体基板(如上所述)移除之后,埋设的氧化物层被暴露。BOx层可作为一个通透的绝缘体层,且可用以遮蔽一层体作为在层体堆栈时的对其他层的屏蔽。又,BOx层提供一个准备好的绝缘体于隔离电路部分使用、或提供在导体间的噪声屏蔽。此外,BOx层中可蚀刻出一个洞,如同前面参照图52和54所描述,及上述提及的IBM美国专利No.6,355,501。

参照图57,另一个电路部分的例子显示为具有适应于三维空间积体的芯片边缘互联结构。更进一步的芯片边缘互联结构细述可见于前述Faris所有的美国专利第5,786,629和6,355,976中寻得。在此一实施例中,一个电路部分C在选择粘结分层堆栈基板的器件层的一个绝缘区域I里面形成。此处,导体在每一电路部分的多重边缘上被形成,以WL、WR、和WR/WL表示。然而,注意,导体还能够或选择性地把垂直线向四面八方延伸到层体(例如,到电路部分的四个主要边缘)。

器件层体具有多个电路部分,而多重边缘延伸导体于是依图58所示对齐与堆栈。层体被对齐及堆栈以致于多个电路部分形成一个垂直积体堆栈。视垂直集成器件所需电路部分而每个层体可相同的或不相同的。又,虽然边缘互联显示在每个层上,一般预计某些层可有一、二、三、或四个边缘互联。一般更进一步预计某些层可具有唯一的穿越互联。又更进一步预计某些层可有一、二、三、或四个边缘互联和一个或更多通路互联。

在一较佳实施例中,N个层被堆栈,且所有连续的N层是在一个单一步骤中粘结。这可利用,例如,紫外线或热来处理层体间的粘着物所致。注意,由于一般互联在每个芯片的边缘,在特定的实施例中暴露电路部分本身接触到粘着物虽然非必需也不会有害,而可减少处理步骤及最后地花费。

现在参照图59,电路部分的每个堆栈依据公知技术切割。在切割无法提供平滑的平面的边缘情况下,布线边缘可被抛光使电路部分触及每个导体。

参照图60中显示多个电路部分边缘与导体W′R和W′L(电的或光学的)互联,虽然一般预计可能有一些或所有的层有垂直纸面的边缘互联(指向和/或来自纸面)。可藉以公知屏蔽和蚀刻导体材料的沉积薄膜的方法电气连接各电路部分导体。其它的互联方式如前述美国专利No.5,786,629和6,355,976更详细地描述。

重要的是,边缘互联能在垂直积体芯片处理期间及最终产品(垂直积设的芯片)中作用。在处理的时候,边缘互联可作为诊断之效。尚可有各种不同的选择。例如,一个或多个边缘互联可用为诊断及其它电量、资料、内存存取、或其它的个别电路部分的功能性。边缘的一个或多个互联可余留的,以改良器件产量。边缘互联可独立地存取电路部分不同区域以增加的功能性。大量储存寻址功能也为可行的,根据客户需要而在高密度储存设备中提供互联。

图61为没有显示出互联W’的垂直积设芯片的等角视图。图62是显示有互联W的一个可能的垂直积设芯片。注意可具有各种不同互联W’的组合,端视所需要的功能性。利用一个、两个、三个、或四个边缘、以及选择性通路导体(例如,堆栈底层或顶层),更使互联区段力量倍增(相较于一个通路互联)及高流量互联,使用达三维垂直积体部分的六个面(或更多,若为更多面体的话)。此外多重导体可从各边缘延伸,例如,与特定层的电路部分的不同部分相联的边缘、或余留的边缘。

参照图63显示电路部分的另一个例子,其具有顺应三维空间积设的芯片边缘互联结构。在这一个实施例中,一个电路部分C在选择粘结分层基板器件层的绝缘区域I里面被形成。一个或多个导体在电路部分上的器件层表面穿越地形成。一般,提供延伸穿越芯片部分的部分(如图63所示的左右方)作为余留,以增加垂直积体芯片的一侧损坏或无法互联的故障状况下的生产率。注意,如前述,多重导体可穿过晶片以存取电路部分的不同区域。

现在参照图81和82,比较本发明(图81)与一上述IBM的专利No.6,355,501所揭示的方法(图82)。图82(IBM)显示在一个BOx层上的一个SOI器件。金属化仅被提供Z方向上,即,在SOI器件的顶端和底部垂直穿越连接。特别地,以本发明所示意及叙述提供边缘互联,提供了增高器件效率、减少全部处理步骤、并允许诸如诊断性及增强与简化互联的功能。

在特定的实施例中,可令人满意的通过增加尺寸(接触区域)、传导系数(减少电阻系数)、或两者,而增强此处所述晶片规模或芯片规模堆栈器件的互联。

现在参照图83,显示提高边缘互联传导系数的一个实施例。大体上,离子植入在金属化层区域中提供过度的搀杂(n++或p++)。公知技术中已知此n++或p++搀杂。因此,以这方法提供的互联提高整体的传导系数,例如,以连接边缘暴露导体。这一个步骤可发生在金属化之后或之前,而一般是在包括具氧化物层的电路部分的器件层被移除之前(或在个别器件被移除之前)。

在形成互联的另一个方法中,特别是穿越互联,可使用热电漂移处理。可用于热电漂移处理的铝或其它适用传导性金属沉积在一个硅层的顶端上。一旦在升温下施加电场(例如,上述200℃),铝漂移过基板而提供一个传导路径。这方法可用来形成至少10微米厚的通路互联(迁移方向)。热电迁移处理在多层基板的一个器件层上执行,留下在器件层被形成的电路部分的通路互联。或者,层体可在器件层被选择地粘结到整体层前受到于热电迁移处理。

参照图88,其显示提高接触区域和传导系数的一焊料栓塞充填方法。例如,一般以一个45度角先行蚀刻在基板中形成一逐渐变小的蚀刻。一个导体被形成穿过基板的顶端,并横过进入该逐渐变小蚀刻区域之内。注意需要小的角度(较佳地小于60,更佳地少于45度)将导体的机械性故障减到最少。接着该逐渐变小的蚀刻区域被填满适当的传导性材料。

该较佳地逐渐变小蚀刻部分位于也存在晶粒的边缘。焊料栓塞沿着切割线被切割,暴露出传导性焊料栓塞材料与导体。一些层可被堆栈及边缘连接,藉使接触电阻显著地因传导性栓塞焊料部分的存在而减到最少。

为进入形成的金属化层而可蚀刻(例如,较佳地以约45度逐渐变小的蚀刻)通孔。通孔是以可熔化的或可烧结的传导性的材料栓塞。参照图89,其描述以本方法形成的一通路互联。注意,当边缘连接时,在x-y平面中延伸的金属化层可延伸作为边缘连接。一逐渐变小的通孔在较低的层中被蚀刻。金属化层在其中形成,而通孔被填以可熔化或可烧结材料的栓塞焊料。一后续层在第一层的顶部形成。一逐渐变小的通孔在顶部层中蚀刻。金属化层形成在顶层,而通孔被填满可熔化或可烧结材料的栓塞焊料。

在一个实施例中,当层体堆栈时,传导性的栓塞焊料被烧结或熔化。这可作用于对齐粘结,即非暂时的粘结,而当接合是一个接触的时候其将不移除,且不会总被视为唯一永久粘结的足够粘结力。

在一实施例中,较佳地,可熔化的或可烧结的传导性材料直到最后的粘结步骤才被熔化或烧结,较佳地,熔合或其它的适用粘结也熔化或烧结传导性栓塞焊料。消费者可在熔合和传导性熔化/烧结之后、或在熔合和传导性熔化/烧结之前,被提供分层堆栈的器件。

相较于上述IBM美国专利No.6,355,501仅一通路互联,通过提供一个或多个边缘互联,可具有仅一通路互联所无法达到的各种不同附加功能如所述。例如,参照图65,屏蔽层可被提供在毗邻的层体之间。这避免电路部分层之间的交叉噪声。

经由通路连接,噪声从一个层幅射到下一个。这是垂直堆栈电路的一个公知问题。因为本发明的较佳实施例仰赖边缘连接而具有一个屏蔽层。屏蔽层形成物质如铜,钨,鉏或其它的传导性材料。在特定的实施例中,此种屏蔽层更用来除热。屏蔽层与毗邻的金属化层的适应绝缘性属公知。有益地,一个层产生的任何杂音是传送不到毗邻层的。这对垂直混合集成电路是特别令人想要的,包括混合垂直集成电路与下列有用器件其中之一的组合,如电源、模拟、射频、数字、光学、光、微机电系统、微流体、和包含至少包含前面诸类型的有用器件之一的组合。屏蔽层更可更进一步被用于光学的连接电路形成包覆层。

这一个屏蔽层也可视为一个接地平面以建立超高速和超宽频传输电线路,如公知所广为人知的。注意,IBM的美国专利No.6,355,501不包括如此的屏蔽层,在其中揭示方法只有穿越连接。

参照图66,通道可被提供在层体之间以散热。除热通道可为除热而载有流体(液体或气)。例如,通道可流过惰性空气或其它的单独冷却液体来冷却层体。另可选择的微流体泵或其它的器件可被包括在其中来提供气体或其它的可选用的流体来冷却层体。

通常,对于这讨论的目的,将了解本发明的多层结构中可附加地在多层基板上制造微流体器件。其所知该互联及通孔提供与微流体器件的沟槽、井、和通道类似的电功能。除了一些需要电的或光学的控制等一些动电微流体器件外,大多数的微流体器件是微标度结构的机械器件组成,通过普遍用于集成电路制造的制造技术。因此,一本领域技术人员可了解,在此处称作互联、导体、电极、及通孔可对应到微流体器件环境下的端口、槽、井、和微通道。

对于微机电系统器件和微流体器件而言,必需将所欲器件解构成一系列薄的水平薄片。通常,所需要的厚度约在2微米至10微米间的任何地方。每一个薄片建立在一个使用许多微机电系统或微流体已知晶片处理技术之一的硅晶片上。一旦微机电系统或微流体薄片在晶片的顶表面上建立,薄片在晶片另一个顶表面上被剥落而且堆栈在其它薄片上来制造微机电系统或微流体结构。经过这连续的剥落与堆栈,能建立一个达约一公分高具有复杂的内部结构和几何形体的微机电系统或微流体器件。

参照图67,这些通道可包括传热部分(即,沉积金属)以更进一步协助散热。或者,这些通道可被形成像格子松饼一样的结构,例如,如上述美国专利No.6,355,976所描述。

现在参照图68,与各电路部分有关的通道或其它热传导部分在被取置部维护时可被形成在器件层下面。

这些通道可在电路部分和导体形成后依照描述形成。屏蔽层可选择地被直接形成在这些通道上以形成图66和67中显示的结构。

或者,遮蔽及/或传热部分在器件层被选择性粘结到整体基板之前可被形成在器件层的下面。

此外,遮蔽及/或传热部分可被形成如一个或多个分离层体,被对齐、堆栈、和粘结而形成在图64-66中显示的结构。

在另一个实施例中,通道可在器件层被选择性地粘结到整体基板之前被形成。例如,如上述,形成弱粘结区域的处理技术包括蚀刻弱粘结区域5的表面。在这一个蚀刻步骤,柱状物9被定义在表面1A(图8)、2A(图9)、或1A和2A上的弱粘结区域5中。柱状物可以选择性地蚀刻、余留柱状物来界定。柱状物的形状可为三角形的、金字塔形、矩形、半球形的、或其它适当形状。或者,柱状物可在被蚀刻的区域中被植入或积设。另一前述处理技术,其关于在层1(图12)、层2(图13)的弱粘结区域5中利用诸如蚀刻、机制、或两者(视使用的材料而定)形成包括一个空区域10(图12和13)。由此,当第一层1粘结到第二层2时,空区域10将使粘结减到相对于强粘结区域6最小的力量,来促进之后的解除粘结。针对选择粘接的削除或形成空白区,阶由于只有很少的粘结区来让材料粘结,在弱粘结区域5的整体力量远小于在强粘结区域6的粘结。可选择地,这些通道可包括如上述中被沉积的热传导材料。

注意图65-67的这些功能。依据上述IBM的美国专利No.6,355,501中揭示不能够利用通路连接器有效地形成。如上述中,导体可通过沉积适当的传导材料形成在可实施电或光学导通的电路部分中。除此之外,导体可在形成选择粘结器件层的程序中被固定形成。

依照上述,形成强粘结区域的处理技术之一设计利用在表面1A(图2)或1A和2A的弱粘结区域5上的一个或多个金属区域8。例如,以包括但限为铜、金、铂、或任何组合金属或其合金沉积在弱粘结区域5上。一旦层1和2的粘结,弱粘结区域5将微弱地粘结。强粘结区域可保持未经处理的(其中强度不同分别提供必要的强粘结对弱粘结比率给弱粘结层5和强粘结区欲6),或可依前所述和之后说明来促进强力附着。

随着预先形成在器件层弱粘结侧的传导层可为电路部分的处理做好准备。在特定的实施例中,电路部分可被形成一个足以联系该预先形成传导层的深度。在其它特定的实施例中,那该预先形成传导层可作为之后层体的至少部分导体。可明了的是,该预先形成传导层可被留下当作是、或可被蚀刻形成一需要的图案。

或者,不在器件层下面形成作为弱粘结之用的金属层,尚可采用多种处理技术来形成传导层需要的图案的金属层。金属层可在一个或多个其它处理技术(例如,粗加工)之后被形成。又,金属层可在一个或多个其它的处理技术之前被形成。

在一进一步的实施例中,堆栈的一个单独的层可被供于互联。这层可允许路由和桥接来避免混杂同时使绝缘边缘焊线的需求最小。例如,图62上水平(x方向)的连接可在层体中形成,如果该层体是依照此处描述的混杂层。

较佳地在此处描述的各种不同的方法是在一个晶片规模上实施。然而,对于在一个芯片规模上的垂直整合芯片制造中所重视的许多功能也非常有用。

现在参照图69,图说一个具有多个选择粘结电路形成区域(显示为白色)的选择粘结多层基板。注意,为清楚只有显示一些代表性的电路区域,而在一个单一晶片可提供100个或1000个电路部分。选择粘结多层基板的剩余阴影部分通常被强劲的粘结力粘结,如同在上面描述。图70显示这一系列选择粘结电路部分的侧视图。这些强粘结区域通常粘住强粘结区域的壕沟以在处理及/或剥除的时候维持电路部分或器件的结构完整性。为了要移除选择粘结电路部分(例如,在电路处理之后),各电路部分可如同图71中所示意的及上述的解除粘结技术来移除。注意,器件层中可具有一个BOx层,如前述,在WB或WB和SB双区域提供SOI芯片。

一些堆栈层体的对准可借着已知对准技术完成的。例如,上述IBM的美国专利No.6,355,501所描述,可使用光学的对准,藉使毗邻层体(例如,与透明的区域相联)上的附图标记使用已知的光学装制的彼此对齐。该参考前案中也揭示了一种自我对齐栓塞焊料的方法,藉此使用机械性互联(例如,如图53-56显示)。

在另一个实施例中并且参照图90,提供另一机械对准方法连同器件层晶片堆栈一起使用。一个层体上具有机械性突出或柱体,而在另一个层体上具有通孔。当它们机械性吻合时可达成对准。

在另一个实施例中,对准可以上述美国专利No.6,355,976中揭示的方法实现。如其中所显示,在一个对准站使用固定的参考,层体利用比较参考对准、可矫治粘着紫外光被施用,层体被堆栈在先前以固定的参考为基础而维持精确对准的堆栈层体上(或一个基板)。而当与先前的层上之附图标记相较时,感生累增的错误堆积。当每个层被堆栈的时候紫外光被施用。

一种用于对齐多个层体的方法和系统通常利用将被对齐的层体的一个投影,投影可与除了层体或堆栈层体之外的对准参考对齐,藉此除去在上述层体间对准时感生的错误放大。

此方法包括在一个机械基板上放置一第一层。在一较佳实施例中,第一层和机械基板间包括一个低粘度粘着物材料。聚合材料是较佳地可聚合的(例如,暴露在紫外光幅射时),且可选择地,此聚合材料是可分解的,依据在此处描述的步骤,另一可选择的粘着物可用来永久地粘住多个层体,在它们已经被形成之后。

系统进一步包括一个极化反射器,通常以相对于第一层的45度角对齐。一光源106被导向极化反射器,而极化光指向在第一层上的对准标记。另外,一个四分之一波相位延迟器设置在极化反射器和第一层之间。此四分之一波相位延迟器使得从反射器反射的极化光接下来可从对准标记反射回来并透过极化反射器104传送,如同极化状态被四分之一波相延迟器反相。

层进一步包括一个或多个对准标记。这些对准标记可为蚀刻区域、对层体施用材料、塑形区域、或其它的已知对准标记方法。当极化或不极化光被传输至极化反射器的时候,光从这些对准标记反射,及,在特定的实施例中,经过四分之一波相延迟器返回并接着经过极化反射器投影出对准标记的位置影像。

对准标记的位置影像被与对准参考相较。此对准参考包括对照在第一层上的对准标记的对准标记。如果第一个层被判断为适当地对齐,例如,由在检测器或比较器中发现的一个零值,则不需要进一步的行动。然而,在层体未被对齐的情况下,通过对准参考的光能被检测器或比较器发现,而须要机械性对齐层体。一个适当的X-Y-Θ子系统以x方向、y方向、及/或角度方向来重新定位第一层、直到在对准参考中来自极化反射器反射的反映光的对准标记如检测器或比较器所指示地被对齐。当检波器发现层一个无效力的数值(即,和在对准参考上的对准标记的对准来自第一个层的光)的时候被对齐。

或者,对准标记可为不反射的极化光、以及选择未从剩下未标记的部分层体的特定波长极化光。因此,当光在除了在对准参考上的对准标记的位置之外所有的部分反射的时候,将获得一个无效力的数值。

在一较佳实施例中,零位检测器或比较器是耦接至X-Y-Θ子系统的,以致于可实现自动化的对准程序。即,如果零位检波器发现光,X-Y-Θ子系统将被调整直到一个无效力的数值(零值)被发现。

在另一可选择实施例中,取代当对准为正确时发现现零值,可利用光透过诸如符合对准标记的对准参考中的孔或透明的部分来传输(有关于光所使用的)。其中只有当对准是适当的时候光通过。

所述程序可重复于一第二层、一第三层、直到一第n层等。另一可选择的投影系统可包括扫瞄程序,表面被一个被反映的激光束扫瞄,反射是可经过适当软件或另一个比较器与对准参考相比来进行。这可包括已知的傅立叶光和使用其它的扫瞄和检波系统。

此系统的一种重要的优势在于消除起于程序层错误的错误被除去,因为对准参考在对准和堆栈操作各处保持固定或已知道。N个层将被个别地与对准参考对齐,如此所需具有一个N层堆栈的最终产品将适当地对准。通过本方法,可实现极准确,因为每个个体层被个别与已知的或固定的参考对齐,相对地分别被之前的层对齐。因此,即使在最差的状况下也可达到极端的准确度,其基于对准会因个别层体的单一错误停止而非相对的由N层错误相乘才停止。

当被堆栈的N层对齐时,可借着上述粘着物粘结,并依所述,那些粘着物也被分解也可以另外的粘着物替换。

参照图72,描述一个范例性系统和方法。该方法包含在一个机械基板102上包括一个对准标记170的第一层150。对准标记170可包含一个点、线、曲线、形状、或在层体或层体上的其它标记,藉蚀刻或沉积的类似方式形成在层里面。依照更进一步描述,对准标记170通常反射特定偏极化的光。

系统进一步包括一个极化反射104,通常以相对于第一层150的45度角对齐。一光源106被导向极化反射器104,而极化光108指向在第一层150上的对准标记170。另外,一个四分的一波相位延迟器110设置在极化反射器104和第一层150之间。此四分之一波相位延迟器110使得从反射器104反射的极化光108接下来可从对准标记170反射回来112并透过极化反射器104传送,如同极化状态被四分之一波相延迟器110反相。

当从极化反射器104传送的极化光108具有一个第一极化状态,具有相同的第一极化状态的极化光经过四分之一波相延迟器110从这些对准标记反射,此处光被转变到一个第二极化状态,促成从对准标记反射的光经过极化反射器104被传输以投影对准标记位置的影像112。

对准标记的位置影像112被与对准参考114相较。此对准参考114包括对照在第一层上的对准标记的对准标记。如果第一个层被判断为适当地对齐,例如,由在检测器或比较器116中发现的一个零值,则不需要进一步的行动。然而,在层体未被对齐的情况下,通过对准参考114的光能被检测器或比较器116发现,而须要机械性对齐层150。

参照图73,一对对准标记270可被提供来增加准确度。

参照图74,一对光源可被导至极化反射器以减少能量,每个光源被导至一个区域,该区域中对准标记被评估来预期对准误差。

连同图76参照图75,具有可控制耦接至检测器或比较器的X-Y-Θ子系统490和590。X-Y-Θ子系统以x方向、y方向、及/或角度方向来重新定位第一层、直到在对准参考中来自极化反射器反射的反映光的对准标记如检测器或比较器所指示地被对齐。在一较佳实施例中,零位检测器或比较器可操作地耦接至X-Y-Θ子系统,以实现被自动对准程序。即,如果零位检波器发现光,X-Y-Θ子系统将被调整直到一个无效力的数值被发现。

当一个低粘性、可聚合的粘着物被用来粘接层150到基板(或一个后来的层在一个先前的层顶上),该粘着物通过X-Y-Θ子系统允许层体被重新定位。当达到对准时,此粘着材料可被聚合以“确置”该对齐层于定位。

如图75所示,X-Y-Θ子系统490包括一个耦接至晶片或适当取置部层(例如,在晶片的边缘)的运作控制系统。例如,运作控制系统可包含一个或多个个附着到边缘的真空处理器、或一个最接近晶片层边缘的指定环形区域。此外,通孔可在晶片中形成以使运作控制系统经一臂部进入。

如图76所示,在响应于检测器或比对器的未对准检侧而被重新定位的层体的相对侧上具有一对X-Y-Θ子系统590。

于另一实施例中,现在参见图77,多组光学系统(各大致类似于图72所示)被设置来配合多个对齐标记,以提高精确度。

现请参见图78,其中所示器件适于一种或多种对齐程序机能。此器件内包括有多组子系统;于一实施例中,诸子系统各提供单一机能,例如写入对齐标记或检测对齐标记。例如,一器件可包括有用以写入对齐标记的多组子系统,而另一器件可包括有用以检测对齐标记的多组子系统。为确保对齐精确度,此等个别器件应制作成使写入位置与检测参考位置大致相同,或至少在必要的器件公差范围内。

在使用一对齐装置的一种对齐方法中,对齐标记可于处理电路部分期间定置于一器件层上。此处,对齐标记可包括于电路部分处理所用一个或多个屏蔽上,使诸对齐标记对应于对齐标记检测装置中用于检测对齐标记的多组子系统。

于使用一对齐标记检测装置与一写入装置的另一方法中,诸器件本身对齐安置;此外,诸器件可结合在一起,以便确保对齐精确度。只要其它器件和欲对齐层体间的器件对其它器件呈通透状,那么顺序(也即欲对齐层体的关系)就不重要;例如,若最外侧器件为对齐标记检测装置,则在例如采用光学附图标记检测法或其它扫描法时,写入装置应呈光学通透状;若最外侧器件为写入装置,则在例如通过使欲写上标记的层体暴露于某波长光线来进行对齐标记写入时,对齐装置应对写入装置呈通透状;或者,标记写入可采一已知角度,而可略过检测装置。

在另一实施例中,写入和对齐动作可用同一器件执行。例如,如上所述的一光学数组可用来将层体暴露于一标记光信号,以及事后检测所形成标记。

对齐标记写入及/或写入与检测装置、或是其复制型态,也可用来在用于在各器件层上形成电路部分的一个或多个屏蔽内标示及/或蚀刻对齐标记。传统上,IC、MEMS或其它可用器件是由多个不同层体所形成,是以每一层的屏蔽应与前一屏蔽对齐。在此,第N层的屏蔽则非对齐于第(N-1)层,而是对齐于一共享写入器/检测器。于另一实施例中,写入器/对齐器也可整合到具有屏蔽写入机能的一装置内。

在更一实施例中,一器件层可在电路部分处理之前设置对齐标记。如同本文所述的相同或一实质同等的对齐标记写入装置、或是其它写入装置,被用来标示将用于形成电路、MEMS或其它有用器件区域的屏蔽及/或曝光装置。

先精确对齐器件层,再对齐屏蔽及/或曝光装置,可用和对齐写入器匹配的一参考对齐标记检测器轻易达成,而能为器件层上有用器件的妥适界定图案提供匹配的对齐标记。或者,如本文所述,可用一体式对齐标记写入器/检测器来确保对齐精确性。

应知,该器件本身可用本文所述的多层基板形成各层(图上未示)、及对齐、堆栈、和粘结多个层体而制成。诸子系统可包括(并不限于)偏极化系统、透镜系统、光玻锥、STM尖端系统、电子束穿孔、摄影机、附光源光圈、光检测器、电子光圈、离子光圈、x光光圈、和前述至少一种所组成的组合。

于又一实施例中,所写入的对齐标记可进一步包括例如围绕中心点的对映线或标记;这在采用例如扫描技术时特别合宜,因为扫描仪/比较器不只可检测是否已对齐,更可通过检测已知的对映标记来提供对映指令。藉此,为“聚焦”于一对齐标记上所需的系统与时间需求,便大幅降低。例如,比较器可判定X-Y-θ子系统的移动动作应依读取对映标记的结果,把层体定置于-.1微米X和+.05微米Y处。

上述新颖对齐技术可令N个层体对齐时有空前的nm精确度。此一对齐法结合本文所述其它多个多层处理技术与各个例示性应用,可大大促进众多3D微米和纳米器件的诞生。

现请参见图86,其中揭示了另一种对齐法。此处,一锥状孔(例如具有约45度的锥化推拔角)于欲堆栈的多个器件层上设于一对齐位置处(例如取代对齐标记)。此等对齐孔可于形成有用结构之前或之后制成。当诸层体堆栈时,一光束试图射过此等孔;若层体未对齐,光线即无法通过;然后移动层体,直到光线自第N层反射为止。

或者,锥状孔可填上例如诸如SiOx的光学透明材料。此外,虽因可能发生累积性误差而非较佳,但一层体也可与相邻层体对齐。

现请参见图87,其中提供晶片级堆栈对齐法。屏蔽可如上述设有对齐机能,然而,仍可能无法达到完美的格栅对齐效果。例如,电路部分与相关联接点的相对位置可能会如虚线参考线所示地偏移;而由于一晶片上可能有多达数百个有用器件受处理,故一些有用结构部分的此种随机歪斜现象可能对于晶片级堆栈会造成问题。

为解决此一潜在问题,可于晶片阶层设置总体互联体或金属化设施。一般而言,如图87所示,总体金属化设施包含尺寸超出的金属化体。此种总体金属化设施可于每一阶层利用同一屏蔽制成;其具有够大尺寸,而能补偿任何局部晶粒位置偏移。此外,总体金属化设施也可如上所述用于提供边缘互联机能;应知,所示切割线是位于总体金属化设施末端。

现请参见图91,示出又一种光学对齐技术。一第一晶片与一第二晶片各设有一对匹配的对齐窗,此等对齐窗呈例如互相垂直的一对矩形的形式。当第二晶片如图所示移动超越第一晶片时,只可见到一个正方形。依据此图案,可作x方向移动,直到见到第二尝试图案为止。接着,作y方向移动,直到光线匹配于对齐孔为止。

或者,处理器可包括有一共振层,而兼作处理器和对齐装置。此处理器可包含任何已知处理器,包括前述2002年10月2日申请的PCT专利申请PCT/US/02/31348“用于处理易碎物品的器件与方法及其制造方法”中所述。

此种混成型处理器/LC对齐器连同使用此处理器的对齐方法均显示于图96中。一LC电路有部分形成于该处理器内;注意其为开路。该层体包括有匹配该开路区域的一导体,作为对齐标记。而包括有该匹配对齐导体的此层体依处理器技术领域公知的方式受处理。器件层层体从处理器内的开路LC电路馈以RF信号;当器件接近对齐时,RF激励作用即增强,且通常于对齐位置(也即LC电路完全闭合)达到最大。

此方法相反于IBM公司专利No.6355501所述的电容法,该法是于诸相邻层体上形成相同共振电路,一个AC信号施加于金属图案共振电路并依共振电路所感应感测电流大小对齐,而以最大感测电流值表示完美对齐点。此方法在欲对齐层体上有侵入性处理,可能造成损坏;而在使用混成型处理器/LC对齐器的本案

实施例中,则由处理器器件承受侵入性传输。

参见图97,针对次微米或纳米级对齐,可设置各种导体图案(以及因而有各类混成型处理器/LC对齐器系统[均未示于图中])。

本文所述的粘结可为暂时性或永久性。暂时性粘结例如可如上文针对对齐措施所述地形成(也即,在层体适当对齐后,于层体局部区域形成暂时性粘结)。应知,此种粘结可能保持到最终处理程序之后,或是可如本文所述地分解。此外,通常发生于对齐动作之后的此种粘结步骤,可能足以充作“永久性”粘结。

大体上,诸个别层体如本文所述在对齐后的永久性粘结可藉多种技术及/或物理现象达成,包括但不限于:镕合、融合、阳极化、凡得瓦、化学粘合、疏水现象、亲水现象、氢键结、库仑力、毛细力、极短程力、或包含前述粘结技术及/或物理现象中的至少一种的组合。

于一实施例中,使用辐射(热、UV、X光等等)可固化粘合剂,以求简便制造。UV粘结可在每一层体堆栈时进行,或是一起以单一步骤实施。

于某些实施例中,当以单一步骤实施UV粘结时,晶片的边缘部分,或是若在芯片级制造的话则在芯片边缘部分,应具UV通透性,以便提供水平UV通入作用。为从晶片顶部透过辐射使粘合剂固化,可在数个层体设置辐射通透区,以便让粘合剂暴露于适当辐射下。

在其它实施例中,诸层体则逐层固化。又在它种实施例中,粘合剂则可从边缘施敷。

较佳地,晶粒一些部分包括有粘着部分,且因而可包括有辐射通透区。

在另一实施例中,为免粘胶暴露于欲形成互联体的金属化区域,或是为免粘胶暴露于电路或其它有用器件部分,粘胶可在欲粘着表面上依图案敷设。于一实施例中,遮蔽要避开的区域、以及绕过所述区域敷设粘合剂,即可提供图案化粘合剂。或者,控制式积设法可用来选择性积设粘合剂。应知,粘合剂的公差可比其它程序步骤的公差为大。

为使粘合剂固化,边缘辐射通透部分可大致如前述美国专利No.6355976所述地设置。或者,如上所述,可在有图案化粘合区的光学对阶段设置一些辐射通透窗。

图案化粘合剂最好可分解,使得粘著作用可为暂时性。因此,于整个堆栈形成后,暂时粘结作用可依意愿予以解构,而堆栈体则藉诸如融合等等其它手段予以永久粘结。

在堆栈体切割(切片)后,边缘受金属化处理。金属化体可包括至少一层/图案;也可设置多个金属化层,它们最好如公知技术所作地绝缘。

于一实施例中,可如前述美国专利No.6355976所述地包括有MSA架构。明显地,可提供编码措施,而容许选择堆栈体上具有最少连接与最短传播延迟的个别电路。

其它状况曾遭遇一种问题,特别是在晶片级堆栈与集积状况下,会有与有用器件生产率方面的问题。而在本申请中,这可通过在切割与分类后依据例如机能层数量执行合适诊断动作,而予以克服。本方法可让生产率接近100%。

本方法包括:提供具有未知器件健康状态(通常在可供贩售栏呈“空白”形态,但已有互联布线,且大体上已可供进行例如微处理、模块处理、钻头切片处理、平行处理、或储存应用)的多个垂直集成器件;对诸垂直集成器件执行诊断;以及依已知良品层数量将诸垂直集成器件分类。

另一实施例中,该方法包含在形成垂直集成器件晶粒前在一晶片上分类多个垂直集成器件。因此可在一个或所有晶片上的器件进行诊断。晶片堆栈于是根据各种条件分类。例如,在一实施例中,晶片堆栈可依据有多少垂直集成器件具有预定数量的已知良品层被分类。另一实施例中,晶片堆栈可依据所有装在晶片堆栈上的器件的已知良品层最小数量而被分类。

诸器件或晶片可藉本文所述之一种或多种程序提供,或是由其它已知的垂直集成器件形成方法提供。基于几个理由,本文所述方法在某些实施例中属较佳者。本案方法的边缘互联体可供进行外部诊断程序。

由于在晶片级堆栈和切割多个垂直集成器件,故可充分利用到规模经济的优点。本案方法也有助于连接的冗余安排。

于诊断期间,可用公知诊断方法来判断器件有多少层良好。根据已知良品层数量,垂直集成器件被分类划归到符合一已知良品层数量范围的储存空间;或者,或是再结合进一步条件,依据器件速度来分类所述垂直集成器件。于是,不同储存空间即代表适于不同使用者的产品。

例如,参见图92,假设目标是要在制造500个晶粒的一晶片的晶片级上达成1000个堆栈层,则所提供储存空间可分为1000个已知良品层、500个已知良品层、250个已知良品层、100个已知良品层、50个已知良品层、和1个已知良品层。

又假设只有10%的晶粒符合1000个堆栈层的标准,这些就分类到“1000”储存空间;明显地,这些具有所期望层数者是最昂贵的晶粒堆栈体。再假设有10%的晶粒有多于900但少于1000个已知良品层,这些就分类到“500”储存空间。于剩余的80%中,假设有40%介于500到900个已知良品层之间,这些也分类到“500”储存空间。当然应知,每一储存空间的已知良品层数量水准可依例如顾客需求而变。假设有20%有介于250到499个之间的已知良品层,这些也分类到“250”储存空间。再假设有10%有介于100到249个之间的已知良品层,有5%有介于50到99个之间的已知良好晶粒层,且余下的5%有介于1到49个之间的已知良好晶粒层,则这些即分别分类到“100”储存空间、“50”储存空间、和“1”储存空间。

每个储存空间即依此定价,且所出现的需求将会针对含有某一数量已知良品层的各种晶粒。因此,商业生产率即可大幅提高。

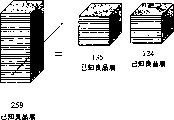

再以上述情况为例,假设一顾客指定要至少100个已知良品层,则在“100”储存空间中的任何晶粒堆栈体均属合适者。或者,参见图93,带有259层的一器件可水平切割成一个135层堆栈体和另一个124层堆栈体。此种切割通常沿x-y平面为之,以使堆栈体的z轴大小缩减。于一较佳实施例中,此种切割动作可在几个已知坏晶粒层之一处为之,以便减少废料。

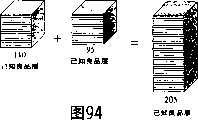

于另一实例中,参见图94,假设顾客指定含有200个可操作层的器件,则可将含110个已知良好晶粒的一堆栈体与含95个已知良好晶粒的一堆栈体沿z方向垂直堆栈起来,而构成具205个已知良品层的一器件。当然,此处不难想到也可堆栈两个以上的晶粒堆栈体。于是,在制造上,即可取用某一储存空间的晶粒来修补欠缺完满堆栈体的晶粒。

参见图95,也可从边缘来堆栈诸晶粒堆栈体;这在本申请中是大致如上述地以多个边缘连接器来提供。

于再一实施例中,在诊断后且在堆栈前,一层体或其一部分可用来储存健康状态或测试结果信息。此外,于堆栈晶粒中也可提供以程序规划和寻址机能;应知,当这些晶粒受堆栈时,可用两个层体来储存健康状态或测试结果信息,但也可想到的是,这些层体可接受重新规划以更新的健康和状态信息。本方法在诸层体为相同层体时尤为有用。

有多种产品与器件可用本案所揭示的程序来制成。如前所述,“胚体”不管是单层或是垂直集积层(完全附有互联结构和随意而定的寻址与编码机能),通常由相同层体构成。另种系列的产品和器件则可由不同层体构成;这些产品和器件可为标准型(例如附有积体处理机及/或内存的MEMS或微流体器件),或是也可以依需求特别订制,例如,GPS、RF、电池、太阳能电池、和其它有用器件均可集积于此等垂直堆栈体中。

垂直积体微电子器件可含有形成于其内的多种有用结构或器件。例如,极高速处理机能即可通过依本案方法堆栈多个处理电路而达成;若采用MSA架构,甚至可引生更高的速度。

于另一实施例中,可依本案方法制成大容量资料储存器(例如可储存64GB者)。此等器件可随意而定地将垂直积体内存与有线及/或无线外部连接结构结合,用于对PC、TV、PDA、或其它需要内存的器件来回进行通讯和资料传送动作。

在再一实施例中,依本案方法制成的垂直集成器件可包括一个或多个处理机及/或内存器件再搭配上光学处理、通讯或交换机能。

在又一实施例中,依本案方法制成的垂直集成器件可包括一个或多个处理机及/或内存器件再搭配上RF传输及/或接收机能。

在更一实施例中,依本案方法制成的垂直集成器件可包括一个或多个处理机及/或内存器件再搭配上全球定位系统接收器及/或发射器。

在进一实施例中,依本案方法制成的垂直集成器件可包括一个或多个处理机及/或内存器件,并再搭配上光学处理、通讯或交换机能、RF传输及/或接收机能、及/或全球定位系统接收器及/或发射器。

例如,一种范例性产品可包括一个微自动点唱机,在媒体上提供一个使用者每星期100多个小时的依客户需求修改的程序规划,以在此处揭示的方法形成。

其它的内存储存器系统包括光学的、扫瞄取样微镜/纳米级储存;以及全息储存。

微流体器件可达许多目的。费用缩减和品质与功能性的增加可与依现在的方法和系统获得。微流体可被提供为各种不同的使使,包括但是不限制在生物科技、化学的分析、产生器件、微米级和纳米级材料的沉积、热转移(例如,如同在此处描述)。

如美国专利No.6,355,976和前所描述,可在器件层之间形成冷却层。特别地,这些冷却层并未依据于IBM美国专利No.6,355,501的揭示。

微流体器件也可通过堆栈通道形成,例如,如上述2002年10月2日申请的名称为“脆性物体的取置装置和方法以及其制造方法”的PCT/US/02/31348中有关取置部的说明部分所描述。

除了通道的堆栈之外,其它的微流体器件也可轻易地被整合,通过依据已知的技术形成器件、或较佳地在器件的弱粘结区域上以易于移动、或通过总成通常有关于微机电系统的部分,如下面描述。这些器件可包括,但是没被限制在,微流量感应器(例如,气流量感应器、表面修剪感应器、液体流量感应器、热的稀释流量感应器、热的传播时间感应器和压差流量感应器)、和外部的致动器(例如,螺管活柱、压电的致动器、空气的致动器、塑造内存合金致动器)的微阀门、和整合的致动器(例如,静电致动器、二金属的致动器、热气式致动器、电磁的致动器)的微阀门、检查装阀门,机械的微帮浦(例如,压电的微帮浦、空气的微帮浦、热气式微帮浦、静电微帮浦)、非机械的泵(例如,超音波受到驱策的微帮浦电渗透微帮浦、电子水力式微帮浦)。

在此描述使用程序,一个包括微流体和处理器、内存、光学处理、通信或交换功能的整合装置;射频传输及/或收受功能;微机电系统;及/或一个全球定位系统接收机及/或发射机。

2002年8月15日提交的名称为“微机电系统和制造微机电系统的方法”的申请PCT/US/02/26090揭示了一个方法形成一个包括微机电系统和其它的功能性的垂直积体堆栈,于本申请中作为参考。大体上,方法中用为在器件层弱粘结区域形成每个微机电系统器件(如此处所述)。较佳地,在一个晶片规模上,器件层以对微机电系统器件造成最小伤害的方式移除,而且晶片通常与其它的微机电系统或具有其它有用器件的层体一起堆栈、对齐、和粘结。

现在参照图98,其显示一截面、一悬桁边缘、一电接触边缘、以及形成在或在一个多层基板的选择粘结器件区域之上或之中的多个层体上视图。一般,图中呈现堆栈器件截面部分堆栈形成的微机电系统器件。底部层1通常视为一个基板。层2包括延伸接触的边缘。层3包括一部分边缘延伸接触和一个通路,一般避免微机电系统器件机械元件的移动限制。层4包括一个通路。层5是被放置在堆栈里用与接处层3相接触的部分机械元件(例如,一个悬桁)部分。层6是层5的机械元件的另一个部分。层7是允许层8和层6中的机械器件间接触的一个通路。层8包括通路和其它机械元件。层9显示一个通路。层10显示延伸到垂直IC边缘的机械元件。

图99和100显示处理图98的微机电系统器件的特定步骤的部分放大视图。注意每个层通常非常简单的一个截面,被用于所欲旋臂结构的微机械。这为任何的微机电系统器件都是真实的,使得它们可依实体和机械的特性易于拆解。

可选择地,为了在堆栈的时候支持层体,一可分解材料可在区域中提供空白区且该区需要机械性支持。

在进一步的实施例,逻辑电路、内存、射频电路、光学电路、电源器件、微流体、或任何至少包含前面有用器件之一的组合可整合在堆栈中(一般在如图98中描述的截面)。

微机电系统可包括,但是没被限制在,悬臂结构(例如,谐振器或谐振检波器)、微涡轮、微齿轮、微转盘、光学开关、可转变镜子(硬的和薄膜基的)、V-槽接合(例如,用于卷缩结构、弯曲结构、或为机器人的手及/或腿);能测量一个或多个物理性或非物理性的变量包括加速度、压力、力、转矩、流量、磁场、温度、气体成份、湿度、酸味、流体离子的浓度、和生物的气体/液体/分子的浓度的微传感器,微致动器、微活塞、或任何其它的微机电系统器件。

依照所述,如本发明中揭示微机电系统器件可能依截面拆解及在多层体上分别制造。然而,可了解的整个微机电系统器件可在器件层上被制造,并转移及堆栈到另一个器件上、或单独使用为一单机器件。

使用此处描述程序:一包括微机电系统的整合器件,及包括微机电处理器、内存、光学处理、通信或交换功能性、射频传输及/或收受功能性、微流体、及/或一个全球定位系统接收机及/或发射机的整合器件。

依据本发明描述的方法的其它可被形成的器件包括,但是没被限制在,微喷射机(例如,用于微卫星、机器昆虫、生物探针器件、指示型智能“药丸”(例如,其中具有适当感应器的一个微喷射机能够设置特定的组织,例如,伴随着内建于微流体器件、和一个药剂载体,可将药剂施于被影响的组织))。进一步依据本发明描述的方法可形成的器件包括位截割处理器、平行处理器、模块处理器、具有微流体、集成电路、内存、微机电系统或上述任何组合的微引擎。

已经显示并且描述本发明的较佳实施例,不过各种不悖离本发明精神与范畴的不同的修改和替换形式即可视为本发明。因此,应了解本发明已描述的方式及描述并不限制本发明的可行形式。

Claims (104)

1.一种用于制造垂直微机电器件的方法,该方法包括以下步骤:

提供一整体基板;

在该基板上选择性地建立强粘结区域和弱粘结区域;

提供垂直承载于该基板上的第一粘结半导体层;

在该第一粘结半导体层上建立一电极,该电极对应于所述弱粘结区域;

建立一配置成与该电极相对的可激励元件;

从该整体基板移除该第一半导体层;以及

将该第一半导体层粘结到一第二半导体层。

2.如权利要求1所述的方法,进一步包括使该第一半导体层对齐具有设置位置相同的电极的该第二半导体。

3.如权利要求2所述的方法,其中该对齐步骤是机械式对齐。

4.如权利要求2所述的方法,其中该对齐步骤是光学式对齐。

5.如权利要求1所述的方法,进一步包括以下步骤:在该第二半导体层上建立一电极。

6.如权利要求5所述的方法,其中该第二半导体层在该弱粘结区域上具有半导体器件部分。

7.如权利要求1所述的方法,其中该强粘结区域与该弱粘结区域的面积比率大于1。

8.如权利要求1所述的方法,其中该强粘结区域与该弱粘结区域的粘结强度比率大于1。

9.如权利要求1所述的方法,进一步包括以下步骤:将该第一半导体层与该第二半导体层互联。

10.如权利要求9所述的方法,其中该互联的步骤实施于所述半导体层的边缘。

11.如权利要求10所述的方法,其中该互联的步骤是电气地耦接。

12.如权利要求10所述的方法,其中该互联的步骤是光学地耦接。

13.如权利要求9所述的方法,其中该互联的步骤是垂直穿越所述半导体层实施的。

14.如权利要求5所述的方法,进一步包括以下步骤:

从该整体基板移除该第二半导体层;以及

粘结该第二半导体层至该第一半导体层。

15.如权利要求1所述的方法,进一步包括以下步骤:

提供一垂直地承载于该整体基板上的第N半导体层,该第N半导体层具有强粘结区域和弱粘结区域;

在该第N半导体层上建立电极,该电极对应于该弱粘结区域;

从该整体基板移除该第N半导体层;以及

将该第N半导体层粘结到第N-1半导体层。

16.如权利要求15所述的方法,其中由N个半导体层中的任何两层形成微机电系统器件。

17.如权利要求1所述的方法,进一步包括以下步骤:

切割粘结半导体层来形成一个或多个晶粒。

18.如权利要求17所述的方法,进一步包括以下步骤:

于该切割步骤之后互联粘结半导体层。

19.如权利要求18所述的方法,进一步包括以下步骤:

在所述一个或多个晶粒的边界上形成边缘连接器。

20.如权利要求19所述的方法,其中所述边缘连接器用作为判断个别晶粒层的健康状况的诊断导体。

21.一种垂直微机电系统器件,其包括:

在一晶片上的一整体基板;

垂直承载于该基板上的一第一选择粘结半导体层,该粘结半导体层包含弱粘结区域和强粘结区域;

垂直承载于该第一选择粘结半导体层上的一第二选择粘结半导体层;

其中一电极与一可激励元件被建立在该弱粘结区域处或在该弱粘结区域上;

该电极与该可激励元件配置成彼此相对;以及

该电极与该可激励元件垂直地跨越该第一选择粘结半导体层及该第二选择粘结半导体层。

22.一种形成于晶粒上的垂直微机电系统器件,其包括:

在一晶片上的一整体基板;

垂直承载于该基板上的一第一选择粘结半导体层,该粘结半导体层包含弱粘结区域和强粘结区域;

垂直承载于该第一选择粘结半导体层上的一第二选择粘结半导体层;

其中一元件与一可激励元件被建立在该弱粘结区域处或在该弱粘结区域上;

该元件与该可激励元件垂直地跨越该第一选择粘结半导体层及该第二选择粘结半导体层;以及

该晶粒是由切割所述粘结半导体层而形成的。

23.如权利要求22所述的器件,其中该晶粒绕其本身垂直轴旋转而形成一布线堆栈。

24.如权利要求1所述的方法,其中该整体基板包括一埋设的氧化物层。

25.如权利要求24所述的方法,其中该埋设的氧化物层是通过离子注入而形成的。

26.一种用于制造多层微流体器件的方法,其包括以下步骤:

提供一整体基板;

在该基板上选择性地建立强粘结区域和弱粘结区域;

提供垂直承载于该基板上的第一粘结层;

在该第一粘结层上建立一端口,该端口对应于该弱粘结区域;

建立一机械性地耦接至该端口的通道;

从该整体基板移除该第一层;以及

粘结该第一层至一第二层。

27.如权利要求26所述的方法,进一步包括以下步骤:使该第一半导体层对齐具有设置位置相同的端口的该第二半导体。

28.如权利要求27所述的方法,其中该对齐步骤是机械式对齐。

29.如权利要求27所述的方法,其中该对齐步骤是光学式对齐。

30.如权利要求26所述的方法,进一步包括以下步骤:在该第二层上建立一端口。

31.如权利要求30所述的方法,其中该第二层在该弱粘结区域上具有微流体器件部分。

32.如权利要求26所述的方法,其中该强粘结区域与该弱粘结区域的面积比率大于1。

33.如权利要求26所述的方法,其中该强粘结区域与该弱粘结区域的粘结强度比率大于1。

34.如权利要求26所述的方法,进一步包括以下步骤:使该第一层与该第二层互联。

35.如权利要求34所述的方法,其中该互联的步骤实施于该第一和第二层的边缘。

36.如权利要求35所述的方法,其中该互联的步骤是垂直穿越该第一和第二层实施的。

37.如权利要求34所述的方法,进一步包括以下步骤:

从该整体基板移除该第二层;以及

将该第二层粘结到该第一层。

38.如权利要求26所述的方法,进一步包括以下步骤:

提供垂直地承载于该整体上的第N层,该第N层具有强粘结区域和弱粘结区域;

在该第N层上建立一端口,该端口对应于该弱粘结区域;

从该整体基板移除该第N层;以及

粘结该第N层至一第N-1层。

39.如权利要求38所述的方法,其中由N层中的任两层形成微流体器件。

40.如权利要求26所述的方法,进一步包括以下步骤:

切割该粘结区层来形成一个或多个晶粒。

41.如权利要求40所述的方法,进一步包括以下步骤:

在该切割步骤后互联所述粘结层。

42.如权利要求41所述的方法,进一步包括以下步骤:

在所述一个或多个晶粒的边界上形成边缘连接器。

43.如权利要求42所述的方法,其中该边缘连接器用作为判断个别晶粒层的健康状况的诊断导体

44.如权利要求26所述的方法,其中该整体基板包括一埋设的氧化层。

45.如权利要求44所述的方法,其中该埋设的氧化层是通过离子注入而形成的。

46.一种多层微流体器件,其包括:

在一晶片上的一整体基板;

垂直承载于该基板上的一第一选择粘结层,该粘结层包含弱粘结区域和强粘结区域;

垂直承载于该第一选择粘结层上的一第二选择粘结层;

其中解构端口和解构通道建立于所述弱粘结区域处或在所述弱粘结区域上;以及

所述端口及所述通道垂直地跨越该第一选择粘结层与该第二选择粘结层。

47.一种形成在晶粒上的多层微流体器件,其包括:

在一晶片上的一整体基板;

垂直承载于该基板上的一第一选择粘结层,该粘结层包含弱粘结区域和强粘结区域;

垂直承载于该第一选择粘结层上的一第二选择粘结层;

其中解构端口和解构通道建立于所述弱粘结区域处或在所述弱粘结区域上;

所述端口及所述通道垂直地跨越该第一选择粘结层与该第二选择粘结层;以及

该晶粒是由切割所述粘结半导体层而形成的。

48.如权利要求47所述的器件,其中该晶粒绕其垂直轴旋转而形成一堆栈。

49.一种制造垂直集成电路的方法,该方法包括以下步骤:

提供一整体基板;

在该基板上选择地建立强粘结区域和弱粘结区域;

提供一垂直地承载于该基板上的第一粘结半导体层;

在该第一粘结半导体层上建立半导体器件部分,该半导体器件部分对应于该弱粘结区域;

从该整体基板移除该第一半导体层;以及

将该第一半导体层粘结到一第二半导体层。

50.如权利要求49所述的方法,进一步包括以下步骤:将该第一半导体层与具有设置位置相同的半导体器件部分的该第二半导体层对齐。

51.如权利要求50所述的方法,其中该对齐步骤是机械性对齐。

52.如权利要求50所述的方法,其中该对齐步骤是光学对齐。

53.如权利要求49所述的方法,进一步包括以下步骤:在该第二半导体层上建立半导体器件部分。

54.如权利要求53所述的方法,其中该第二半导体层在该弱粘结区域上具有半导体器件部分。

55.如权利要求49所述的方法,其中该强粘结区域与该弱粘结区域的面积比率大于1。

56.如权利要求49所述的方法,其中该强粘结区域与该弱粘结区域的粘结强度比率大于1。

57.如权利要求49所述的方法,进一步包括以下步骤:将该第一半导体层与该第二半导体层互联。

58.如权利要求57所述的方法,其中该互联的步骤实施于所述半导体层的边缘。

59.如权利要求58所述的方法,其中该互联的步骤是电气地耦接。

60.如权利要求58所述的方法,其中该互联的步骤是光学地耦接。

61.如权利要求57所述的方法,其中该互联的步骤是垂直穿越所述半导体层实施的。

62.如权利要求53所述的方法,进一步包括以下步骤:

从该整体基板移除该第二半导体层;以及

将该第二半导体层粘结到该第一半导体层。

63.如权利要求49所述的方法,进一步包括以下步骤:

提供一垂直地承载于该整体基板上的第N半导体层,该第N半导体层具有强粘结区域和弱粘结区域;

在该第N半导体层上建立半导体器件部分,该半导体器件部分对应于该弱粘结区域;

从该整体基板移除该第N半导体层;以及

将该第N半导体层粘结到第N-1半导体层。

64.如权利要求63所述的方法,其中由N个半导体层中的任何两层形成有源半导体元件。

65.如权利要求49所述的方法,进一步包括以下步骤:

切割粘结半导体层来形成一个或多个晶粒。

66.如权利要求65所述的方法,进一步包括以下步骤:

于该切割步骤之后互联粘结半导体层。

67.如权利要求66所述的方法,进一步包括以下步骤:

在所述一个或多个晶粒的边界上形成边缘连接器。

68.如权利要求67所述的方法,其中所述边缘连接器用作为判断个别晶粒层的健康状况的诊断导体。

69.如权利要求49所述的方法,其中该整体基板包括一埋设的氧化物层。

70.如权利要求69所述的方法,其中该埋设的氧化物层是通过离子注入而形成的。

71.一种垂直集成电路,其包括:

在一晶片上的一整体基板;

垂直承载于该基板上的一第一选择粘结半导体层,该粘结半导体层包含弱粘结区域和强粘结区域;

垂直承载于该第一选择粘结半导体层上的一第二选择粘结半导体层;

其中一半导体器件部分被建立在该弱粘结区域处或在该弱粘结区域上;以及

该半导体器件部分垂直地跨越该第一选择粘结半导体层及该第二选择粘结半导体层。

72.一种形成在晶粒上的垂直集成电路,其包括:

在一晶片上的一整体基板;

垂直承载于该基板上的一第一选择粘结半导体层,该粘结半导体层包含弱粘结区域和强粘结区域;

垂直承载于该第一选择粘结半导体层上的一第二选择粘结半导体层;

其中一半导体器件部分被建立在该弱粘结区域处或在该弱粘结区域上;

该半导体器件部分垂直地跨越该第一选择粘结半导体层及该第二选择粘结半导体层;以及

该晶粒是由切割所述粘结半导体层而形成的。

73.一种用于提高预定器件的生产率的方法,该器件由一个或多个多层晶粒组成,该方法包括以下步骤:

诊断性地判断每一所述多层晶粒的功能层数量;以及

依据所述功能层数量对各个所述多层晶粒进行分类。

74.如权利要求73所述的方法,进一步包括结合二个或更多所述多层晶粒以使每一所述多层晶粒的功能层彼此互联。

75.如权利要求73所述的方法,其中该判断步骤是经由测试所述多层晶粒的一个或多个边缘互联来执行的。

76.如权利要求74所述的方法,其中该结合步骤包括二层或更多层晶粒的垂直堆栈。

77.如权利要求74所述的方法,其中该结合步骤包括二层或更多层晶粒的边缘堆栈。

78.如权利要求73所述的方法,进一步包括储存有关各该多层晶粒在一或多层上或在一或多层的一部分上的健康数据。

79.如权利要求78所述的方法,其中该健康数据包括在每一该多层晶粒上的已知良品层或已知坏层的指示。

80.如权利要求73所述的方法,其中所述多层晶粒中的至少一层晶粒包括:

垂直承载于一基板上的一第一选择粘结半导体层,该粘结半导体层包含弱粘结区域和强粘结区域;

垂直承载于该第一选择粘结半导体层上的一第二选择粘结半导体层;

其中一半导体器件部分被建立在该弱粘结区域处或在该弱粘结区域上;

该半导体器件部分垂直地跨越该第一选择粘结半导体层及该第二选择粘结半导体层;以及

该晶粒是由切割所述粘结半导体层而形成的。

81.一种提供具有至少一预定数量的已知良品层的器件的方法,该器件由一个或多个多层晶粒组成,该方法包括以下步骤:

诊断性地判断每一个所述多层晶粒的功能层数量;

依据所述功能层数量将各个多层晶粒分类到多个储存空间,每一储存空间具有相关的已知良品层最小数量;

从其中一个储存空间中选择出具有该预定数量的已知良品层的多层晶粒中的一个,该储存空间具有至少等于已知良品层预定数量的相关的已知良品层最小数量。

82.如权利要求81所述的方法,其中至少一个所述多层晶粒包括:

垂直承载于一基板上的一第一选择粘结半导体层,该粘结半导体层包含弱粘结区域和强粘结区域;

垂直承载于该第一选择粘结半导体层上的一第二选择粘结半导体层;

其中一半导体器件部分被建立在该弱粘结区域处或在该弱粘结区域上;

该半导体器件部分垂直地跨越该第一选择粘结半导体层及该第二选择粘结半导体层;以及

该晶粒是由切割所述粘结半导体层而形成的。

83.一种提供具有至少一预定数量的已知良品层的器件的方法,该器件由一个或多个多层晶粒组成,该方法包括以下步骤:

诊断性地判断每一个所述多层晶粒的功能层数量;

依据所述功能层数量将各个多层晶粒分类到多个储存空间,每一储存空间具有相关的已知良品层最小数量;

选择多个所述多层晶粒,它们的已知良品层数量总和至少等于已知良品层预定数量;以及

结合所述选择的多个多层晶粒来形成一组合晶粒,该组合晶粒具有至少等于已知良品层预定数量的已知良品层数量。

84.如权利要求83所述的方法,其中所述选择的多个多层晶粒被水平地组合,且经由在每一所述选择的多个多层晶粒的一个或多个边缘互联而被互联。

85.如权利要求83所述的方法,其中所述选择的多个多层晶粒被垂直地组合。

86.如权利要求83所述的方法,其中至少一个所述多层晶粒包括:

垂直地承载于一基板上的一第一选择粘结半导体层,该粘结半导体层包含弱粘结区域和强粘结区域;

垂直承载于该第一选择粘结半导体层上的一第二选择粘结半导体层;

其中一半导体器件部分被建立在该弱粘结区域处或在该弱粘结区域上;

该半导体器件部分垂直地跨越该第一选择粘结半导体层及该第二选择粘结半导体层;以及

该晶粒是由切割所述粘结半导体层而形成的。

87.一种提供具有至少一预定数量的已知良品层的器件的方法,该器件由一个或多个多层晶粒组成,该方法包括以下步骤:

诊断性地判断各该多层晶粒的功能层数量;

依据所述功能层的数量将各多层晶粒分类到多个储存空间,每一储存空间具有相关的已知良品层最小数量;

从所述多层晶粒中选择一个多层晶粒,该多层晶粒的已知良品层数量大于已知良品层预定数量;以及

切割该选择的多层晶粒来形成一第一多层晶粒部分以及一第二多层晶粒部分,该第一多层晶粒部分的已知良品层数量至少等于已知良品层预定数量;

将该第二多层晶粒部分分类至一个所述储存空间,该储存空间具有与第二多层晶粒部分的已知良品层数量相对应的已知良品层最小数量。

88.如权利要求87所述的方法,其中该切割步骤在该选择的多层晶粒的一个已知坏层进行。

89.如权利要求87所述的方法,其中至少一个所述多层晶粒包括:

垂直地承载于一基板上的一第一选择粘结半导体层,该粘结半导体层包含弱粘结区域和强粘结区域;

垂直承载于该第一选择粘结半导体层上的一第二选择粘结半导体层;

其中一半导体器件部分被建立在该弱粘结区域处或在该弱粘结区域上;

该半导体器件部分垂直地跨越该第一选择粘结半导体层及该第二选择粘结半导体层;以及

该晶粒是由切割所述粘结半导体层而形成的。

90.一种对多个晶片堆栈进行分类的方法,其中每个晶片堆栈包括多个垂直集成器件,所述方法包括以下步骤:

对晶片上的一个或所有器件进行诊断;以及

依据晶片堆栈中具有预定数量已知良品层的将被陆续切割的垂直集成器件的数量而对所述晶片堆栈进行分类。

91.一种对多个晶片堆栈进行分类的方法,其中每个晶片堆栈包括多个垂直集成器件,所述方法包括以下步骤:

对晶片上的一个或所有器件进行诊断;以及

依据该晶片堆栈上所包含的所有所述器件的已知良品层最小数量而对所述晶片堆栈进行分类。

92.一种制造垂直集成电路的方法,该方法包括以下步骤:

提供一整体基板,该整体基板包括一埋设的氧化物层;

在该基板上选择地建立强粘结区域和弱粘结区域;

提供垂直地承载于该基板上的第一粘结半导体层;

在该第一粘结半导体层上建立半导体器件部分,该半导体器件部分对应于该弱粘结区域;

从该整体基板移除该第一半导体层;以及

将该第一半导体层粘结到一第二半导体层。

93.如权利要求92所述的方法,其中该埋设的氧化物层是通过离子注入而形成的。

94.如权利要求93所述的方法,其中该埋设的氧化物层是通过氧气注入而形成的。

95.一种制造垂直集成电路的方法,该方法包括以下步骤:

提供一整体基板;

在该基板上选择性地建立强粘结区域和弱粘结区域;

提供垂直承载于该基板上的第一粘结半导体层;

在该第一粘结半导体层上建立半导体器件部分,所述半导体器件部分对应于所述弱粘结区域;

在该第一半导体层与该整体基板间的界面处形成一埋设的氧化物层;

从该整体基板移除该第一半导体层;以及

将该第一半导体层粘结到一第二半导体层。

96.如权利要求95所述的方法,其中该埋设的氧化物层是通过离子注入而形成的。

97.一种制造垂直微机电器件的方法,该方法包括以下步骤:

提供一整体基板,该整体基板包括一埋设的氧化物层;

在该基板上选择性地建立强粘结区域和弱粘结区域;

提供垂直承载于该基板上的第一粘结半导体层;

在该第一粘结半导体层上建立一电极,该电极对应于所述弱粘结区域;

建立一配置成与该电极相对的可激励元件;

从该整体基板移除该第一半导体层;以及

将该第一半导体层粘结到一第二半导体层。

98.如权利要求97所述的方法,其中该埋设的氧化物层是通过离子注入而形成的。

99.一种用于制造垂直微机电器件的方法,该方法包括以下步骤:

提供一整体基板,该整体基板包括一埋设的氧化物层;

在该基板上选择性地建立强粘结区域和弱粘结区域;

提供垂直承载于该基板上的第一粘结半导体层;

在该第一粘结半导体层上建立一电极,该电极对应于所述弱粘结区域;

建立一配置成与该电极相对的可激励元件;

在该第一半导体层与该整体基板间的界面处形成一埋设的氧化物层;

从该整体基板移除该第一半导体层;以及

将该第一半导体层粘结到一第二半导体层。

100.如权利要求99所述的方法,其中该埋设的氧化物层是通过离子注入而形成的。

101.一种制造垂直微机电器件的方法,该方法包括以下步骤:

提供一整体基板,该整体基板包括一埋设的氧化物层;

在该基板上选择性地建立强粘结区域和弱粘结区域;

提供垂直承载于该基板上的第一粘结层;

在该第一粘结层上建立一端口,该端口对应于该弱粘结区域;

建立一机械性地耦接至该端口的通道;

从该整体基板移除该第一层;以及

粘结该第一层至一第二层。

102.如权利要求101所述的方法,其中该氧化物层是通过离子注入而形成的。

103.一种制造多层微流体器件的方法,该方法包括以下步骤:

提供一整体基板;

在该基板上选择性地建立强粘结区域和弱粘结区域;

提供垂直承载于该基板上的第一粘结半导体层;

在该第一粘结层与该整体基板间的界面处形成一埋设的氧化物层;

在该第一粘结层上建立一端口,该端口对应于该弱粘结区域;

建立一机械性地耦接至该端口的通道;

从该整体基板移除该第一层;以及

粘结该第一层至一第二层。

104.如权利要求103所述的方法,其中该氧化物层是通过离子注入而形成的。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US42812502P | 2002-11-20 | 2002-11-20 | |

| US60/428,125 | 2002-11-20 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN1742358A true CN1742358A (zh) | 2006-03-01 |

Family

ID=33551213

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNA2003801090448A Pending CN1742358A (zh) | 2002-11-20 | 2003-11-20 | 在基板上制造多层器件的方法和系统 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US7056751B2 (zh) |

| EP (1) | EP1573788A3 (zh) |

| JP (1) | JP2006520089A (zh) |

| KR (1) | KR20050083935A (zh) |

| CN (1) | CN1742358A (zh) |

| AU (1) | AU2003304218A1 (zh) |

| TW (3) | TW200428538A (zh) |

| WO (1) | WO2004112089A2 (zh) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102247786A (zh) * | 2010-03-24 | 2011-11-23 | 韩国电子通信研究院 | 微流体控制器件及其制造方法 |

| CN102844176A (zh) * | 2009-09-30 | 2012-12-26 | 微型实验室诊断股份有限公司 | 微流体装置中选择性的粘结性降低 |

| CN108475646A (zh) * | 2015-12-26 | 2018-08-31 | 英帆萨斯公司 | 提供具有已知良好晶粒的三维晶圆组件的系统和方法 |

| CN114035030A (zh) * | 2021-11-05 | 2022-02-11 | 爱迪特(秦皇岛)科技股份有限公司 | 一种测试组件 |

Families Citing this family (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2839505B1 (fr) * | 2002-05-07 | 2005-07-15 | Univ Claude Bernard Lyon | Procede pour modifier les proprietes d'une couche mince et substrat faisant application du procede |

| US7659631B2 (en) * | 2006-10-12 | 2010-02-09 | Hewlett-Packard Development Company, L.P. | Interconnection between different circuit types |

| US20090026524A1 (en) * | 2007-07-27 | 2009-01-29 | Franz Kreupl | Stacked Circuits |

| US8829329B2 (en) * | 2010-08-18 | 2014-09-09 | International Business Machines Corporation | Solar cell and battery 3D integration |

| DE102010041763A1 (de) | 2010-09-30 | 2012-04-05 | Siemens Aktiengesellschaft | Mikromechanisches Substrat |

| US10543662B2 (en) | 2012-02-08 | 2020-01-28 | Corning Incorporated | Device modified substrate article and methods for making |

| WO2015157202A1 (en) | 2014-04-09 | 2015-10-15 | Corning Incorporated | Device modified substrate article and methods for making |

| US9340443B2 (en) | 2012-12-13 | 2016-05-17 | Corning Incorporated | Bulk annealing of glass sheets |

| US10086584B2 (en) | 2012-12-13 | 2018-10-02 | Corning Incorporated | Glass articles and methods for controlled bonding of glass sheets with carriers |

| TWI617437B (zh) | 2012-12-13 | 2018-03-11 | 康寧公司 | 促進控制薄片與載體間接合之處理 |

| US10014177B2 (en) | 2012-12-13 | 2018-07-03 | Corning Incorporated | Methods for processing electronic devices |

| US10510576B2 (en) | 2013-10-14 | 2019-12-17 | Corning Incorporated | Carrier-bonding methods and articles for semiconductor and interposer processing |

| JP6770432B2 (ja) | 2014-01-27 | 2020-10-14 | コーニング インコーポレイテッド | 薄いシートの担体との制御された結合のための物品および方法 |

| WO2016187186A1 (en) | 2015-05-19 | 2016-11-24 | Corning Incorporated | Articles and methods for bonding sheets with carriers |

| CN107810168A (zh) | 2015-06-26 | 2018-03-16 | 康宁股份有限公司 | 包含板材和载体的方法和制品 |

| TW201825623A (zh) | 2016-08-30 | 2018-07-16 | 美商康寧公司 | 用於片材接合的矽氧烷電漿聚合物 |

| TWI821867B (zh) | 2016-08-31 | 2023-11-11 | 美商康寧公司 | 具以可控制式黏結的薄片之製品及製作其之方法 |

| CN111615567B (zh) | 2017-12-15 | 2023-04-14 | 康宁股份有限公司 | 用于处理基板的方法和用于制备包括粘合片材的制品的方法 |

| US11315789B2 (en) * | 2019-04-24 | 2022-04-26 | Tokyo Electron Limited | Method and structure for low density silicon oxide for fusion bonding and debonding |

| KR20210136068A (ko) * | 2020-02-20 | 2021-11-16 | 양쯔 메모리 테크놀로지스 씨오., 엘티디. | Xtacking 아키텍처를 가진 dram 메모리 디바이스 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS63155731A (ja) * | 1986-12-19 | 1988-06-28 | Agency Of Ind Science & Technol | 半導体装置 |

| US5094697A (en) * | 1989-06-16 | 1992-03-10 | Canon Kabushiki Kaisha | Photovoltaic device and method for producing the same |

| JP3214631B2 (ja) * | 1992-01-31 | 2001-10-02 | キヤノン株式会社 | 半導体基体及びその作製方法 |

| JP4126747B2 (ja) * | 1998-02-27 | 2008-07-30 | セイコーエプソン株式会社 | 3次元デバイスの製造方法 |

| US6133582A (en) * | 1998-05-14 | 2000-10-17 | Lightspeed Semiconductor Corporation | Methods and apparatuses for binning partially completed integrated circuits based upon test results |

| JP5121103B2 (ja) * | 2000-09-14 | 2013-01-16 | 株式会社半導体エネルギー研究所 | 半導体装置、半導体装置の作製方法及び電気器具 |

| US6965895B2 (en) * | 2001-07-16 | 2005-11-15 | Applied Materials, Inc. | Method and apparatus for analyzing manufacturing data |

-

2003

- 2003-11-20 US US10/719,666 patent/US7056751B2/en not_active Expired - Fee Related

- 2003-11-20 AU AU2003304218A patent/AU2003304218A1/en not_active Abandoned

- 2003-11-20 TW TW092132601A patent/TW200428538A/zh unknown

- 2003-11-20 EP EP03816310A patent/EP1573788A3/en active Pending

- 2003-11-20 CN CNA2003801090448A patent/CN1742358A/zh active Pending

- 2003-11-20 TW TW092132599A patent/TW200423261A/zh unknown

- 2003-11-20 KR KR1020057009160A patent/KR20050083935A/ko not_active Application Discontinuation

- 2003-11-20 JP JP2005500831A patent/JP2006520089A/ja not_active Withdrawn

- 2003-11-20 WO PCT/US2003/037304 patent/WO2004112089A2/en not_active Application Discontinuation

- 2003-11-20 TW TW092132597A patent/TW200421497A/zh unknown

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102844176A (zh) * | 2009-09-30 | 2012-12-26 | 微型实验室诊断股份有限公司 | 微流体装置中选择性的粘结性降低 |

| CN102247786A (zh) * | 2010-03-24 | 2011-11-23 | 韩国电子通信研究院 | 微流体控制器件及其制造方法 |

| CN108475646A (zh) * | 2015-12-26 | 2018-08-31 | 英帆萨斯公司 | 提供具有已知良好晶粒的三维晶圆组件的系统和方法 |

| US11114408B2 (en) | 2015-12-26 | 2021-09-07 | Invensas Corporation | System and method for providing 3D wafer assembly with known-good-dies |

| CN114035030A (zh) * | 2021-11-05 | 2022-02-11 | 爱迪特(秦皇岛)科技股份有限公司 | 一种测试组件 |

| CN114035030B (zh) * | 2021-11-05 | 2023-10-24 | 爱迪特(秦皇岛)科技股份有限公司 | 一种测试组件 |

Also Published As

| Publication number | Publication date |

|---|---|

| AU2003304218A1 (en) | 2005-01-04 |

| AU2003304218A8 (en) | 2005-01-04 |

| EP1573788A3 (en) | 2005-11-02 |

| US20040241888A1 (en) | 2004-12-02 |

| WO2004112089A2 (en) | 2004-12-23 |

| KR20050083935A (ko) | 2005-08-26 |

| TW200423261A (en) | 2004-11-01 |

| TW200428538A (en) | 2004-12-16 |

| WO2004112089A3 (en) | 2005-09-15 |

| JP2006520089A (ja) | 2006-08-31 |

| EP1573788A2 (en) | 2005-09-14 |

| US7056751B2 (en) | 2006-06-06 |

| TW200421497A (en) | 2004-10-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1742358A (zh) | 在基板上制造多层器件的方法和系统 | |

| CN1132245C (zh) | 3维器件的制造方法 | |

| TW559945B (en) | Thin films and production methods thereof | |

| CN1288710C (zh) | 半导体器件及其制造方法 | |

| TW471012B (en) | Three dimensional device integration method and integrated device | |

| CN1143394C (zh) | 剥离方法、溥膜器件的转移方法和薄膜器件 | |

| CN1294618C (zh) | 半导体器件及剥离方法以及半导体器件的制造方法 | |

| TWI335066B (en) | Three dimensional integrated circuit and method of making the same | |

| US6875671B2 (en) | Method of fabricating vertical integrated circuits | |

| CN1523668A (zh) | 半导体器件 | |

| US7033910B2 (en) | Method of fabricating multi layer MEMS and microfluidic devices | |

| CN101336471B (zh) | 对绝缘体上半导体结构进行抛光的方法 | |

| CN1975345A (zh) | 微结构体的测试方法以及微机械 | |

| US20030020062A1 (en) | MEMS and method of manufacturing MEMS | |

| CN108735863A (zh) | 发射型led显示装置制造方法 | |

| CN1251327C (zh) | 半导体集成电路、信号传输装置、光电装置和电子仪器 | |

| CN1790751A (zh) | 具有执行器的半导体装置 | |

| CN1875481A (zh) | 半导体装置及其制造方法 | |

| CN1551312A (zh) | 半导体芯片的制造方法、半导体装置的制造方法、半导体芯片及半导体装置 | |

| CN1409374A (zh) | 剥离方法以及制造半导体器件的方法 | |

| CN1873998A (zh) | 半导体器件及其制造方法 | |

| CN1969168A (zh) | 振动型陀螺传感器 | |

| TWI311335B (en) | Exclusion zone for stress-sensitive circuit design | |

| CN104332441B (zh) | 生产半导体器件的方法 | |

| CN1734749A (zh) | 转移方法和有源矩阵基板的制造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C02 | Deemed withdrawal of patent application after publication (patent law 2001) | ||

| WD01 | Invention patent application deemed withdrawn after publication |