JP4726187B2 - 半導体集積回路 - Google Patents

半導体集積回路 Download PDFInfo

- Publication number

- JP4726187B2 JP4726187B2 JP2004344524A JP2004344524A JP4726187B2 JP 4726187 B2 JP4726187 B2 JP 4726187B2 JP 2004344524 A JP2004344524 A JP 2004344524A JP 2004344524 A JP2004344524 A JP 2004344524A JP 4726187 B2 JP4726187 B2 JP 4726187B2

- Authority

- JP

- Japan

- Prior art keywords

- access

- queue

- command

- memory

- selection

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Description

前記内蔵メモリに対して設けられ、対応する内蔵メモリへのアクセスコマンドを保持する複数のコマンドキューと、

前記複数の機能処理モジュールから内蔵メモリに対するメモリアクセスの要求があると、当該メモリアクセスに対応するメモリアクセスコマンドを各機能処理モジュールにより要求された内蔵メモリに対する複数のコマンドキューの同一の段に入力するコマンド入力手段と、

前記複数のコマンドキューの先頭に保持されているメモリアクセスコマンドに基づいて複数の内蔵メモリに並列にアクセスする制御手段とを有することを特徴とする。

102 RAM1

103 RAM2

104 RAM3

105 メモリ制御回路

106 コマンド発行機構

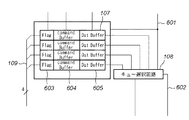

107 アクセスキュー

108 キュー選択回路

109 キュー状態信号

110 アクセスデコード回路

111 コマンドディスパッチャー(Command Dispatcher)

112 キュー制御機構

113 アクセスデコード機構0

114 アクセスデコード機構1

115 アクセスデコード機構2

116 コマンド制御機構

117 機能処理回路MST0

118 機能処理回路MST1

119 機能処理回路MST2

120 機能処理回路MST3

121 機能処理回路MST4

122 機能処理回路MST5

301 アクセスインターフェース(256ビット)

302 アクセス選択信号(2ビット)

303 アクセスバッファ

401 アクセスインターフェース(512ビット)

402 アクセス選択信号(1ビット)

403 アクセスバッファ

501 アクセスインターフェース(1024ビット)

502 アクセスバッファ

601 キュー出力信号

602 キュー指定信号

603 キューフラグ

701 256ビットキュー指定信号

702 512ビットキュー指定信号

703 1024ビットキュー指定信号

801 コマンド選択機構

802 512ビット選択禁止信号

803 512ビット選択禁止信号

804 1024ビット選択禁止信号

805 選択信号生成回路

806 キュー指定信号

901 6入力OR回路

902 2入力OR回路

903 アクセス有効信号

Claims (1)

- 内蔵メモリへアクセスする際のアクセスバス幅が異なる複数の機能処理モジュールからアクセスされ、前記複数の機能処理モジュールのアクセスバス幅のうちの最も小さいビット幅に相当するビット構成の内蔵メモリを、該アクセスバス幅のうちの最も大きいビット幅に相当するビット数を満たす個数分有する半導体集積回路であって、

前記内蔵メモリに対して設けられ、対応する内蔵メモリへのアクセスコマンドを保持する複数のコマンドキューと、

前記複数の機能処理モジュールから内蔵メモリに対するメモリアクセスの要求があると、当該メモリアクセスに対応するメモリアクセスコマンドを各機能処理モジュールにより要求された内蔵メモリに対する複数のコマンドキューの同一の段に入力するコマンド入力手段と、

前記複数のコマンドキューの先頭に保持されているメモリアクセスコマンドに基づいて複数の内蔵メモリに並列にアクセスする制御手段とを有することを特徴とする半導体集積回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004344524A JP4726187B2 (ja) | 2004-11-29 | 2004-11-29 | 半導体集積回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004344524A JP4726187B2 (ja) | 2004-11-29 | 2004-11-29 | 半導体集積回路 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2006155220A JP2006155220A (ja) | 2006-06-15 |

| JP2006155220A5 JP2006155220A5 (ja) | 2008-01-17 |

| JP4726187B2 true JP4726187B2 (ja) | 2011-07-20 |

Family

ID=36633446

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004344524A Expired - Fee Related JP4726187B2 (ja) | 2004-11-29 | 2004-11-29 | 半導体集積回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4726187B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7966469B2 (en) | 2006-08-14 | 2011-06-21 | Qimonda Ag | Memory system and method for operating a memory system |

| JP5375441B2 (ja) * | 2009-08-27 | 2013-12-25 | 株式会社リコー | 半導体集積回路、記憶制御方法、記憶制御プログラム及び記録媒体 |

| JP2012014397A (ja) * | 2010-06-30 | 2012-01-19 | Fujitsu Ltd | 入出力制御装置、及び情報処理装置 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS57211659A (en) * | 1981-06-23 | 1982-12-25 | Fujitsu Ltd | Memory access controller |

| JPH0520183A (ja) * | 1991-07-17 | 1993-01-29 | Fujitsu Ltd | メモリアクセス制御方式 |

-

2004

- 2004-11-29 JP JP2004344524A patent/JP4726187B2/ja not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS57211659A (en) * | 1981-06-23 | 1982-12-25 | Fujitsu Ltd | Memory access controller |

| JPH0520183A (ja) * | 1991-07-17 | 1993-01-29 | Fujitsu Ltd | メモリアクセス制御方式 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2006155220A (ja) | 2006-06-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6496906B1 (en) | Queue based memory controller | |

| US7222224B2 (en) | System and method for improving performance in computer memory systems supporting multiple memory access latencies | |

| US7277988B2 (en) | System, method and storage medium for providing data caching and data compression in a memory subsystem | |

| US6950910B2 (en) | Mobile wireless communication device architectures and methods therefor | |

| JP4317166B2 (ja) | データを転送するインタフェースを有する光記憶システム | |

| EP1769369A1 (en) | Memory controller with command look-ahead | |

| KR100679370B1 (ko) | 메모리 소자에서의 워드 순서지정 방법 | |

| US7899940B2 (en) | Servicing commands | |

| US6425044B1 (en) | Apparatus for providing fast memory decode using a bank conflict table | |

| US6046952A (en) | Method and apparatus for optimizing memory performance with opportunistic refreshing | |

| US6360305B1 (en) | Method and apparatus for optimizing memory performance with opportunistic pre-charging | |

| US7536516B2 (en) | Shared memory device | |

| JP4726187B2 (ja) | 半導体集積回路 | |

| JP3583844B2 (ja) | キャッシュメモリ方式 | |

| US6425043B1 (en) | Method for providing fast memory decode using a bank conflict table | |

| JP2007108882A (ja) | メモリコントローラ及びメモリ制御方法と情報処理装置 | |

| US20020069311A1 (en) | Bus control device | |

| US20090100220A1 (en) | Memory system, control method thereof and computer system | |

| KR970010367B1 (ko) | 멀티프로세서 시스템에서 주기억장치의 보드내 인터리빙 장치 및 방법 | |

| JP4772975B2 (ja) | 半導体記憶装置 | |

| JP4496923B2 (ja) | 共有メモリシステム | |

| WO2007116485A1 (ja) | メモリ装置、そのインタフェース回路、メモリ・システム、メモリ・カード、回路基板及び電子機器 | |

| JP2006195810A (ja) | メモリコントローラおよび高速データ転送方法 | |

| JPS6269347A (ja) | ダイレクトメモリアクセスコントロ−ラ | |

| JP2000066946A (ja) | メモリコントローラ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071127 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20071127 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20071127 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20101222 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110107 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110303 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110408 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110411 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140422 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |