JP4654047B2 - D級増幅器 - Google Patents

D級増幅器 Download PDFInfo

- Publication number

- JP4654047B2 JP4654047B2 JP2005025874A JP2005025874A JP4654047B2 JP 4654047 B2 JP4654047 B2 JP 4654047B2 JP 2005025874 A JP2005025874 A JP 2005025874A JP 2005025874 A JP2005025874 A JP 2005025874A JP 4654047 B2 JP4654047 B2 JP 4654047B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- circuit

- amplifier

- side drive

- low

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F1/00—Details of amplifiers with only discharge tubes, only semiconductor devices or only unspecified devices as amplifying elements

- H03F1/30—Modifications of amplifiers to reduce influence of variations of temperature or supply voltage or other physical parameters

- H03F1/305—Modifications of amplifiers to reduce influence of variations of temperature or supply voltage or other physical parameters in case of switching on or off of a power supply

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Amplifiers (AREA)

- Noise Elimination (AREA)

- Electronic Switches (AREA)

Description

Claims (1)

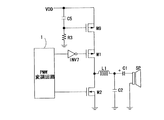

- 入力PWM信号に応じて、高電位側電源端子に直接接続されたハイサイドドライブ用トランジスタおよび低電位側電源端子に直接接続されたローサイドドライブ用トランジスタが交互にスイッチング動作をし、該スイッチングによる信号で、前記ハイサイドドライブ用トランジスタおよび前記ローサイドドライブ用トランジスタの共通接続端子に接続されたAC結合用コンデンサを介してスピーカ又はヘッドフォンを駆動するD級増幅器であって、

前記ハイサイドドライブ用トランジスタのゲートを駆動する第1の駆動回路と、前記ローサイドドライブ用トランジスタのゲートを駆動する第2の駆動回路と、起動時又は復帰時に前記第1の駆動回路の動作を時定数を持って立ち上げる第1の制御手段と、起動時又は復帰時に前記第2の駆動回路の動作を時定数を持って立ち上げる第2の制御手段とを有し、

前記第1の制御手段は、前記第1の駆動回路と電源又は接地間に接続した第1の制御トランジスタと、起動時又は復帰時に該第1の制御トランジスタを時定数をもって導通させる第1の時定数回路とからなり、前記第2の制御手段は、前記第2の駆動回路と電源又は接地間に接続した第2の制御トランジスタと、起動時又は復帰時に該第2の制御トランジスタを時定数をもって導通させる第2の時定数回路とからなる、

ことを特徴とするD級増幅器。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005025874A JP4654047B2 (ja) | 2005-02-02 | 2005-02-02 | D級増幅器 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005025874A JP4654047B2 (ja) | 2005-02-02 | 2005-02-02 | D級増幅器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006217106A JP2006217106A (ja) | 2006-08-17 |

| JP4654047B2 true JP4654047B2 (ja) | 2011-03-16 |

Family

ID=36979968

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005025874A Expired - Fee Related JP4654047B2 (ja) | 2005-02-02 | 2005-02-02 | D級増幅器 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4654047B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4859709B2 (ja) | 2007-03-01 | 2012-01-25 | 富士通セミコンダクター株式会社 | 電圧制御回路 |

| JP2010213114A (ja) | 2009-03-11 | 2010-09-24 | Yamaha Corp | D級増幅回路 |

| JP5454560B2 (ja) * | 2011-12-06 | 2014-03-26 | オンキヨー株式会社 | スイッチングアンプ |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6214728Y2 (ja) * | 1979-12-06 | 1987-04-15 | ||

| JP3398113B2 (ja) * | 2000-02-14 | 2003-04-21 | ローム株式会社 | ミュート回路およびデジタルオーディオ増幅回路 |

| US6781458B2 (en) * | 2002-08-23 | 2004-08-24 | Tripath Technology, Inc. | Providing DC isolation in switching amplifiers |

-

2005

- 2005-02-02 JP JP2005025874A patent/JP4654047B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2006217106A (ja) | 2006-08-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8284953B2 (en) | Circuit and method of reducing pop-up noise in a digital amplifier | |

| US8044719B2 (en) | Class D amplifier circuit | |

| CN104135237B (zh) | 栅极驱动电路 | |

| US20110096944A1 (en) | High perceived audio quality class d amplifier | |

| JP3637904B2 (ja) | 電源回路 | |

| JP4265894B2 (ja) | Dc/dcコンバータの制御回路及びdc/dcコンバータ | |

| JP2010148234A (ja) | 残留電荷放電回路および電源用半導体装置 | |

| JP5095312B2 (ja) | D級増幅回路 | |

| JP2008017596A (ja) | 半導体集積回路 | |

| JP2007166444A (ja) | 過電流検出回路及びスイッチング回路 | |

| JP2007174671A (ja) | 起動時クリック雑音除去を備えるd級増幅器 | |

| JP2005538626A (ja) | 二重電源を使用するディジタルオーディオ増幅器におけるポップノイズ除去回路及びポップノイズ除去方法 | |

| JP2005536966A (ja) | スイッチング増幅器におけるdc分離の提供 | |

| CN100514842C (zh) | 信号输出电路、使用其的音频信号输出装置、电子设备 | |

| JP4654047B2 (ja) | D級増幅器 | |

| JP6647932B2 (ja) | オーディオアンプ回路、それを用いたオーディオ出力装置、およびそれを用いた電子機器 | |

| WO2005122373A1 (ja) | レベルシフト回路及びこれを備えたスイッチングレギュレータ | |

| JP2004153577A (ja) | インバータ回路 | |

| CN115942197B (zh) | 一种直流检测电路、音频放大器和电子设备 | |

| US20080088370A1 (en) | Method, apparatus and system for reducing noise from an amplifier | |

| JP4533707B2 (ja) | アンプ装置、アンプ用電源回路およびオーディオ信号再生装置 | |

| JP2005295754A (ja) | スイッチングレギュレータ | |

| US9431984B2 (en) | Acoustic apparatus | |

| CN115298945B (zh) | Y桥式驱动器中的电源间短路的检测和保护 | |

| JP2009141697A (ja) | D級アンプ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20071206 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100216 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100407 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20100720 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101012 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20101026 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101214 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101220 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4654047 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131224 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |