JP4621368B2 - データ・リンクとのインターフェースを制御するコントローラと方法 - Google Patents

データ・リンクとのインターフェースを制御するコントローラと方法 Download PDFInfo

- Publication number

- JP4621368B2 JP4621368B2 JP2001048005A JP2001048005A JP4621368B2 JP 4621368 B2 JP4621368 B2 JP 4621368B2 JP 2001048005 A JP2001048005 A JP 2001048005A JP 2001048005 A JP2001048005 A JP 2001048005A JP 4621368 B2 JP4621368 B2 JP 4621368B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- controller

- slot

- buffer

- control

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q11/00—Selecting arrangements for multiplex systems

- H04Q11/04—Selecting arrangements for multiplex systems for time-division multiplexing

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q2213/00—Indexing scheme relating to selecting arrangements in general and for multiplex systems

- H04Q2213/13103—Memory

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q2213/00—Indexing scheme relating to selecting arrangements in general and for multiplex systems

- H04Q2213/13107—Control equipment for a part of the connection, distributed control, co-processing

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q2213/00—Indexing scheme relating to selecting arrangements in general and for multiplex systems

- H04Q2213/13291—Frequency division multiplexing, FDM

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q2213/00—Indexing scheme relating to selecting arrangements in general and for multiplex systems

- H04Q2213/13292—Time division multiplexing, TDM

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q2213/00—Indexing scheme relating to selecting arrangements in general and for multiplex systems

- H04Q2213/13332—Broadband, CATV, dynamic bandwidth allocation

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q2213/00—Indexing scheme relating to selecting arrangements in general and for multiplex systems

- H04Q2213/13392—Channels assigned according to rules

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Time-Division Multiplex Systems (AREA)

- Information Transfer Systems (AREA)

- Communication Control (AREA)

Description

【発明の属する技術分野】

本発明はデータ・リンクとのインターフェースを制御するコントローラと方法に関する。

【0002】

【従来の技術】

製品間の通信を行うには、データ・リンクを介した製品間の通信の書式を指定する標準化されたインターフェースを開発する必要がある。標準化されたインターフェースは、データ・リンクを通る、特定のデータ要素に関係する多数のデータ・ストリームを処理するように設計する。データ・リンクを時間または周波数で分割して多数のデータ・スロットを定義し、各データ要素を特定のデータ・スロットに割り付けることが多い。この方法により、複数の異なるデータ要素に関係するデータをデータ・リンクを介して同時に送信することができる。

【0003】

例えばコーデック(コーダ・デコーダ)の分野で、インテルはコーデック・チップとインターフェースするインターフェース・プロトコルを開発した。このインターフェース・プロトコルは、コーデック・チップと、このチップと通信する任意の製品との間の、通信データ・リンク用の書式を定義する。より詳しく述べると、このインターフェース・プロトコルは、多数の入力および出力データ・ストリームを処理するための一連のTDM(時間分割多重化)書式を用いるディジタル・データ・リンクを規定する。このプロトコルでは、リンク構造は各オーディオ・フレームを多数のデータ・スロットに分割し、特定のデータ要素(例えば、左チャンネル・オーディオ、右チャンネル・オーディオ、ヘッドセット、モデムなど)を特定のデータ・スロットに割り当てる。

【0004】

一般に全てのアプリケーションにおいて、上記のデータ・リンクを介してコーデックとインターフェースするコントローラを開発する。どんなアプリケーションでもコントローラは用いるデータ・スロットの部分集合にだけ有用なので、コントローラは一般に特定のアプリケーションに関係して開発される。この方法によるとコントローラの複雑さは減少するが、アプリケーション毎に異なるコントローラを開発しなければならない。

【0005】

【発明が解決しようとする課題】

しかし一般に、これは包括的なコントローラを製作するより好ましい方法であると考えられている。なぜなら、かかる包括的なコントローラにはデータ・リンク仕様が支援するデータ・スロット毎に別個のデータ・バッファ回路が必要になるので、かかる包括的なコントローラのサイズとコストが大きくなるからである。

本発明の目的は、かかるサイズとコストの問題を緩和する包括的なコントローラを提供することである。

【0006】

【課題を解決するための手段】

第1の態様では、本発明は、多数のデータ要素に関係するデータ項目をデータ・リンクの対応するデータ・スロットで転送するデータ・リンクにおいて、データ・リンクとのインターフェースを制御するコントローラを提供する。このコントローラは次の要素を備える。すなわち、少なくとも1つのチャンネルであって、各チャンネルはデータ項目を記憶するデータ・バッファと前記データ・バッファに関連し且つ制御データを記憶する制御レジスタを備え、前記制御データをセットすることによりどのデータ要素のためのデータ項目をそのデータ・バッファ内に記憶するかを規定することができる、少なくとも1つのチャンネルと、前記制御データに従って少なくとも1つのチャンネルとデータ・リンクのデータ・スロットとの間のデータ項目の転送を制御するインターフェース機構と、を備える。

【0007】

本発明はデータ・リンクとインターフェースするコントローラを提供するもので、データ・リンクは多数のデータ要素(例えば、左スピーカ、右スピーカ、モデムなど)に関係するデータ項目をデータ・リンクの対応するデータ・スロットで転送することができる型のものである。理解されるようにデータ・スロットは、例えば時分割多重化(TDM)、符号分割多重化(CDM)、周波数分割多重化(FDM)などの、任意の適当な方法で定義することができる。

【0008】

本発明ではコントローラは少なくとも1つのチャンネルを備え、各チャンネルはデータ・バッファと、このデータ・バッファに関連する制御レジスタを備える。各データ・バッファはデータ・リンクに出力するデータ項目またはデータ・リンクから受信するデータ項目を記憶し、関連する制御レジスタは、セットすることによりどのデータ要素のためのデータ項目をそのデータ・バッファ内に記憶するかを規定することができる制御データを有する。したがって、例えば1つのデータ・バッファは左および右オーディオ・チャンネルに関係するデータ項目を記憶し、別のデータ・バッファはモデム・データに関係するデータ項目を記憶するようにすることができる。または別の例では、1つのデータ・バッファ内でオーディオデータとモデム・データを混合することができる。

【0009】

本発明のコントローラは、制御データに従って少なくとも1つのチャンネルとデータ・リンクのデータ・スロットとの間のデータ項目の転送を制御するインターフェース機構を更に含む。理解されるように、制御データは種々の形式をとることができる。例えば、特定のデータ要素とデータ・リンクの特定のデータ・スロットは対応しているので、データ要素を参照するかまたは対応するデータ・スロットを参照して制御データを指定することができる。どちらの場合も、制御データによりインターフェース機構は、特定のデータ・バッファから取り出したデータ項目をどのデータ・スロットに挿入するかを決定し、および/またはデータ・リンクの特定のデータ・スロットで受信したデータ項目をどのデータ・バッファ内に置くかを決定することができる。

【0010】

制御データの設定に関して述べると、理解されるように、制御レジスタはコントローラを最初にプログラムするときに一度だけ制御データを設定するようにしてもよいし、または必要であれば、制御レジスタは、制御データを任意のときに再プログラミングすることによりコントローラの動作中に特定のデータ・バッファの使用を変更できるようにしてもよい。

本発明により、データ・リンクが支援するデータ・スロット毎に別個のデータ・バッファ回路を設ける必要のない包括的コントローラを開発することができるので、包括的コントローラの開発を妨げるコストとサイズの問題を緩和することができる。

【0011】

本発明の1つの実施の形態では、少なくとも1つのチャンネルの少なくとも1つのデータ・バッファは制御データが指定する1つ以上のデータ要素に関係するデータ項目をデータ・リンクで送信する前に記憶し、インターフェース機構は制御データに応じてデータ・バッファから取り出したデータ項目を対応する1つ以上のデータ・スロットでデータ・リンクにより送信する。

また、少なくとも1つのチャンネルの少なくとも1つのデータ・バッファはデータ・リンクから受信し且つ制御データが指定する1つ以上のデータ要素に関係するデータ項目を記憶し、インターフェース機構は制御データに応じて対応する1つ以上のデータ・スロットから受信したデータ項目をデータ・バッファ内に記憶する。

【0012】

コントローラはデータ項目をデータ・リンクで送信するだけか、またはデータ・リンクからデータ項目を受信するだけでよいが、好ましい実施の形態ではコントローラはデータ項目の送信と受信の両方を行うようにする。かかる好ましい実施の形態では、好ましくは各チャンネルは1対の前記データ・バッファとこれに関連する制御レジスタを備え、前記データ・バッファの一方はデータ・リンクで送信するデータ項目を記憶し、前記データ・バッファの他方はデータ・リンクから受信したデータ項目を記憶する。したがって、好ましい実施の形態では各チャンネルはデータ項目の送信と受信を行うことができる。注意すべきは、或るチャンネル内のデータ・バッファの対はそれぞれの関連する制御レジスタを有するので、好ましい実施の形態では送信データ・バッファは受信データ・バッファと同じ型のデータ要素を処理する必要はなく、送信データ・バッファと受信データ・バッファの制御レジスタは完全に独立にプログラムすることができることである。

【0013】

好ましい実施の形態では、コントローラが提供するチャンネルの数は、そのデータ項目をデータ・リンクで転送するデータ要素の数より少ない。その制御データをセットすることによりどのデータ要素のためのデータ項目をそのデータ・バッファ内に記憶するかを規定することができる制御レジスタをデータ・バッファ毎に設ければこれを達成することができる。理解されるように、この方式によるとどんな事例でもコントローラを極めて柔軟に用いることができると同時に、コントローラの全体のサイズを許容できるサイズに収めることができる。

好ましい実施の形態では、各データ・バッファは同じサンプリング速度を有する1つ以上のデータ要素に関係するデータ項目を記憶する。この条件を付けることにより、コントローラ内の制御機構を大幅に簡単化することができることが分かった。

【0014】

前に述べたように、本発明を用いて種々の異なるデータ・リンクとのインターフェースを制御することにより、多数のデータ要素に関係するデータ項目をデータ・リンクの対応するデータ・スロットで転送することができる。好ましい実施の形態では、コントローラはデータ・リンクを介してコーデックに接続することができる。特に好ましい実施の形態では、コーデックはオーディオ・コーデックであり、データ・リンクはインテルのAC97仕様に準拠したACリンクである。AC97仕様に関する情報については、ウエブ・ページ「http://www.intel.com/pc-supp/platform/ac97」を参照していただきたい。データ・バッファは種々の形式をとることができる。しかし好ましい実施の形態では、各データ・バッファは先入れ先出し(FIFO)バッファで構成する。

【0015】

理解されるように、コントローラは一般にデータ・リンクに接続するだけでなく、リンクからのデータ項目を送信する先の、またデータ・リンクで送信されるデータ項目を送信した元の、他のデータ処理回路に接続する。好ましい実施の形態では、コントローラは、コントローラとメモリとを結合してメモリと少なくとも1つのチャンネルとの間でデータ項目を転送することのできるメモリ・インターフェースを更に備える。1つの実施の形態では、メモリ・インターフェースは、メモリへのアクセスを制御するプロセッサを介してコントローラをメモリに結合する。しかし当業者が理解するように、例えば直接メモリアクセス(DMA)方式などの他の方式を用いてコントローラのメモリ・インターフェースをメモリに結合してもよい。

【0016】

好ましい実施の形態では、各制御レジスタは、セットすることによりコンパクト・モードであることを示す第1のフィールドを有する。コンパクト・モードでは、関連するデータ・バッファとメモリとの間で転送されるデータ語は複数の前記データ項目を含む。コントローラとメモリとの間で転送されるデータ語のサイズが十分大きくて複数のデータ項目を含むことが可能な場合は、この方式によりコントローラとメモリとの間の通信効率を向上させることができる。例えば、コントローラとメモリとの間に32ビットのデータ語を転送することが可能であって且つデータ項目の実際のサイズが16ビット以下である場合は、第1のフィールド内にコンパクト・モードを指定することにより、メモリとコントローラとの間で転送される各データ語内に2つのデータ項目を含めることができる。

【0017】

好ましい実施の形態では、データ・スロットで転送するときのデータ項目は固定サイズで表され、各制御レジスタは、セットすることにより関連するデータ・バッファ内に記憶されているデータ項目の実際のサイズを示すことができる第2のフィールドを有する。第1のフィールドがセットされた場合は、メモリ・インターフェースは第2のフィールドを参照して、関連するデータ・バッファとメモリとの間で転送される各データ語内にデータ項目をいくつ含めるか決定する。したがって好ましい実施の形態では、制御レジスタ内の1つのフィールドを用いてデータ項目の実際のサイズを指定し、第1のフィールド内にセットされた情報と共にこの情報を用いて、各データ語内に含むべきデータ項目の数を決定することができる。

【0018】

しかし理解されるように、コントローラがかかるコンパクト・モードを支援するかどうかに関わらず、データ項目の実際のサイズに関する情報は有用な情報である。詳しく述べると、セットしたとき関連するデータ・バッファ内に記憶されている各データ項目の実際のサイズを示すフィールドを制御レジスタ内に含むことにより、メモリ・インターフェースはデータ項目を実際のサイズか固定サイズかに変換することができる。したがって好ましい実施の形態では、データ・バッファに追加するデータ項目をメモリ・インターフェースが受信すると、メモリ・インターフェースはデータ項目を所要のビット数だけシフトして固定サイズでデータ項目を表現した後、この固定サイズのデータ項目をデータ・バッファ内に置くことができる。逆に、データ・バッファからの固定サイズのデータ項目をメモリ・インターフェースを介してメモリに転送するときは、メモリ・インターフェースは実際のサイズの情報を用いてデータ項目を再びシフトして、その実際のサイズのデータ項目を作ることができる。

【0019】

好ましい実施の形態では、制御レジスタ内の制御データは関連するデータ・バッファ内に記憶されているデータ項目を有するデータ要素の数を指定し、メモリ・インターフェースは制御データに従ってデータ・バッファとメモリとの間のデータの転送速度を制御する。したがって、2つのデータ要素のためのデータ項目がデータ・バッファ内に記憶されていることを制御データが示す場合は、好ましい実施の形態ではこれらのデータ項目をデータ・バッファ内に記憶し、データ・バッファから対で読み出す。したがって、メモリ・インターフェースは可能な限り送信データ・バッファ内に常に2つのデータ項目を置いて、かかるデータ項目をデータ・リンクで送信する要求に応じるだけの十分なデータを用意しなければならない。また、メモリ・インターフェースは好ましくは、受信データ・バッファ内に2つのデータ項目を受信する空間を常に用意しなければならない。

【0020】

第2の態様では、本発明は、多数のデータ要素に関係するデータ項目をデータ・リンクの対応するデータ・スロットで転送するデータ・リンクにおいて、データ・リンクとのインターフェースを制御する方法を提供する。この方法は、(a)データ項目を記憶するデータ・バッファとこのデータ・バッファに関連する制御レジスタとをそれぞれ備える少なくとも1つのチャンネルを設け、(b)どのデータ要素のためのデータ項目を関連するデータ・バッファ内に記憶するかを規定する制御データを制御レジスタ内に記憶し、(c)前記制御データに従って少なくとも1つのチャンネルとデータ・リンクのデータ・スロットとの間のデータ項目の転送を制御する。

【0021】

【発明の実施の形態】

前に述べたように、多数のデータ要素に関係するデータ項目をデータ・リンクの対応するデータ・スロットで転送するデータ・リンクにおいて、本発明を用いて種々のデータ・リンクとのインターフェースを制御するコントローラを開発することができる。しかし本発明の好ましい実施の形態を示すために、コントローラはデータ・リンクを介してオーディオ・コーデックに接続し、特にデータ・リンクはインテルのAC97仕様に準拠すると仮定する。この仕様では、データ・リンクをACリンクと呼ぶことがある。

【0022】

図1は、ACリンク60を介してオーディオ・コーデックと通信するチップ10の要素の間の関係を示す略ブロック図である。チップ10は、バス50によりメモリ40から取り出したデータにデータ処理を行うマイクロプロセッサ20を含む。当業者が理解するように、図1はチップ10を非常に簡単化した図であって、マイクロプロセッサ20とメモリ40との間には一般に他の要素が接続されている。例えば、マイクロプロセッサ20はマイクロプロセッサが用いる命令および/またはデータを記憶するキャッシュにアクセスすることができる。このとき、マイクロプロセッサ20は書込みバッファなどによりメモ40から切り離される。メモリ40はチップ10の外部にあってよい。

【0023】

しかし、本発明の好ましい実施の形態を記述するのにマイクロプロセッサ20がメモリ40と通信する方法を正確に記述する必要はないので、簡単のためにこの図ではバス50を介してメモリ40をマイクロプロセッサに直接接続した。

本発明の好ましい実施の形態では、コントローラ30もバス50に接続して、チップ10と、ACリンク60を介してチップ10に接続するオーディオ・コーデックとの間の、データ項目の転送を制御する。詳しく述べると、チップ10がデータ項目をオーディオ・コーデックに送るとき、マイクロプロセッサ20はメモリ40からこれらのデータ項目を取り出してバス50によりコントローラ30に送り、ACリンク60の該当するデータ・スロットで出力する。同様に、コントローラ30がACリンク60によりオーディオ・コーデックからデータ項目を受信すると、これらのデータ項目をコントローラ30内でバッファされ、マイクロプロセッサ20はこれを取り出してメモリ40内に記憶する。

【0024】

理解されるように、或る実施の形態では直接メモリ・アクセス(DMA)方式を用いて、マイクロプロセッサ20を用いずにコントローラ30とメモリ40の間で直接通信を行うことができる。DMA方式はよく知られているので、これ以上説明しない。

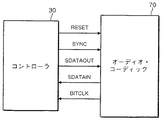

図2は、コントローラ30とオーディオ・コーデック70との間のACリンクの詳細を示す。ACリンクは5ピンのインターフェースから成り、双方向で、固定速度で、直列PCM(パルス・コード変調)ストリームであり、時分割多重化(TDM)方式を用いて多数の入力および出力オーディオ・ストリームと制御レジスタ・アクセスとを処理する。コントローラ30とコーデック70とを接続する5ピンは次の通り。

【0025】

BITCLK−−これは12.288MHzに固定されたクロック信号である。

RESET−−これは外部コーデックの非同期コールド・リセットを開始するのに用いられる信号で、アクティブ・ローである。コールド・リセットを行うと、コーデック・レジスタ内の全ての情報は消失する。

SDATAIN−−この入力は状態情報とディジタル・オーディオ入力ストリームを受信する。これはBITCLKの立下がりエッジでサンプリングされ、立上がりエッジでコーデックから出力される。

SDATAOUT−−この出力は制御情報とディジタル・オーディオ出力ストリームを送信する。BITCLKの立上がりエッジで出力される。

【0026】

SYNC−−この信号は48kHzに固定されており、直列クロック(BITCLK)を分割することにより得られる。SYNC信号はBITCLKの立上がりエッジでセットされる。またオーディオ・コーデックが電力断状態のとき、SYNC信号を非同期に出力してオーディオ・コーデックを再起動することができる(コーデック・レジスタ内の情報は一切消失せずに)。

ACリンク構造は各データ・フレームを、SDATAOUTピンとSDATAINピンを介して送信される12の出力データ・ストリームと、12の入力データ・ストリームに分割する。これらのデータ・ストリーム(以後、データ・スロットと呼ぶ)はそれぞれ20ビットのサンプル分解能を有する。

【0027】

図3は、双方向フレームの書式の詳細を示す図である。図から分かるように、フレームはタグとデータ相で構成する。各相は多数のデータ・スロットを有する。スロット0はタグ相であり、スロット1から12まではデータ相である。データ相内の12のデータ・スロットはそれぞれ特定のデータ要素に割り当てられ、各データ・スロットはそのデータ・スロットに関連するデータ要素の関係のデータ項目だけを運ぶ。

【0028】

まずSDATAOUTピンに出力する出力データ・ストリームを見ると、コントローラからのデータ出力フレームは外部コーデック向けの制御データとPCMデータを含む。図3から分かるように、SDATAOUTに送られる情報は多数の異なるスロットから成り、各スロットは多数のビットから成り、新しい各ビット位置はBITCLKの立上がりエッジでACリンクに与えられる。SDATAOUTに送られるスロット0から12までについて、以下にそれぞれ簡単に説明する。

【0029】

SDATAOUTスロット0:タグ相(16ビット)

スロット0の第1ビットを「有効フレーム」ビットと呼ぶ。この第1ビットが1の場合は現在のデータ・フレームは有効なデータの少なくとも1つのスロットを含むことを示し、外部コーデックはこのスロット0内の後続のビットをサンプリングしてどのフレームが実際に有効データを有するかを判定する。次の12ビットの位置は対応する12タイム・スロットのどれが有効データを含むかを示す。有効スロットは各ビット位置の1で示す。ビット2−0は常に0でなければならない。コントローラはスロット0を生成する。これは、コントローラの関連するデータ・バッファ内のデータの有効性と、送信制御レジスタ内の値と、SDATAINスロット1からの禁止要求ビットの値により決定される。或るスロットが有効でない場合は、コントローラは関連するSDATAOUTスロットに0を入れる。

【0030】

SDATAOUTスロット1:レジスタ・アドレス(20ビット)

スロット1は現在のフレームのレジスタ・アクセスのレジスタ・アドレスを示すのに用いられる。スロット1のMSB(ビット19)は現在の制御動作が読取り(0)か書込み(1)かを示す。ビット18−12は読取りまたは書込み動作のレジスタ・アドレスを指定するのに用いられる。最後の12ビットは予約であり、0でなければならない。

SDATAOUTスロット2:レジスタ書込みデータ(20ビット)

スロット2は現在のフレーム(スロット1で規定される)のレジスタ書込みアクセスのレジスタ・データを含む。ビット19−4はレジスタに書き込む16ビットの値を含む。ハードウエアはビット3−0を0にする。アクセスがレジスタ読取りの場合は、スロット全体に0を入れる(この要求はコントローラが決定する。コントローラはスロット1のビット19を用いて動作が読取りか書込みかを決定する)。

【0031】

SDATAOUTスロット3:PCMプレイバック左チャンネル(20ビット)スロット3はコーデックの左チャンネルDACのためのPCMプレイバック・データを送信するのに用いられる。

SDATAOUTスロット4:PCMプレイバック右チャンネル(20ビット)スロット4はコーデックの右チャンネルDACのためのPCMプレイバック・データを送信するのに用いられる。

SDATAOUTスロット5:モデム1チャンネル(20ビット)

スロット5はモデム・ライン1DAC入力データを送信するのに用いられる。

SDATAOUTスロット6:PCMプレイバック中央チャンネル(20ビット)

スロット6はコーデックの中央チャンネルのためのPCMプレイバック・データを送信するのに用いられる。

【0032】

SDATAOUTスロット7:PCMプレイバック左サラウンドチャンネル(20ビット)

スロット7はコーデックの左サラウンドチャンネルのためのPCMプレイバック・データを送信するのに用いられる。

SDATAOUTスロット8:PCMプレイバック右サラウンドチャンネル(20ビット)

スロット8はコーデックの右サラウンドチャンネルのためのPCMプレイバック・データを送信するのに用いられる。

SDATAOUTスロット9:PCMプレイバック低周波効果サラウンドチャンネル(20ビット)

スロット9はコーデックのLFE(低周波効果)チャンネルのためのPCMプレイバック・データを送信するのに用いられる。

【0033】

SDATAOUTスロット10:モデム2チャンネル(20ビット)

スロット10は96kHzのサンプリング速度が要求されたとき(例えば、DVDプレヤー)にモデム・ライン2DAC入力データまたはPCM左チャンネル・データを送信するのに用いられる。

SDATAOUTスロット11:ヘッドセット・チャンネル(20ビット)

スロット11は96kHzのサンプリング速度が要求されるとき(例えば、DVDプレヤー)にヘッドセット入力データまたはPCM右チャンネル・データを送信するのに用いられる。

SDATAOUTスロット12:IO制御チャンネル(20ビット)

スロット12は96kHzサンプリング速度が要求されるとき(例えば、DVDプレヤー)にIO制御入力データまたはPCM中央チャンネル・データを送信するのに用いられる。

【0034】

次に入力データ・ストリームでは、コントローラのSDATAINピンに入力するオーディオ入力フレーム入力は、外部コーデック制御レジスタおよびステレオADC(アナログ・ディジタル変換器)からの状態とPCMデータを含む。タグ・スロット(スロット0)は16ビットを含み、外部コーデックが作動可能かどうかと、いくつかの装置部分からのデータが有効かどうかをコントローラに知らせる。

【0035】

図3から明らかなように、SDATAINに送信される入力データ・ストリームも多数の異なるデータ・スロットから成り、各データ・スロットは多数のビットから成り、新しい各ビット位置はBITCLKの立上がりエッジでACリンクに与えられる。SDATAINに送信されるスロット0から12までの詳細は次の通りである。

SDATAINスロット0:コーデック状態ビット(16ビット)

SDATAINスロット0の第1ビット(ビット15)はコーデックが作動可能かどうかを示す。コントローラはスロット0内の後続のデータビットを調べて他の装置部分が作動可能かどうか判断する。例えば、ビット14が1であるとスロット1のデータが有効であったことを示し、ビット13が1であるとスロット2のデータが有効であったことを示す、などである。このスロットから得られるデータはコントローラ内に記憶されるので、ここからのビットによりフレーム内のスロットを確認することができる。

【0036】

SDATAINスロット1:状態アドレス

スロット1は、コーデックが前のフレームから読取り要求を受けたときに外部コーデック・レジスタ・アドレスをコントローラに返すのに用いられる。外部コーデックは読取りアクセスのためのレジスタ・インデックスだけを返す。(書込みアクセスの場合はスロット1で有効データを返さない)。

読取りでは、ビット19は常に0である。ビット18−12はコーデック・レジスタの7ビットのレジスタ・インデックスを含む。ビット11−2はサンプリング速度変換(SRC)機能性に用いられる。スロット3−12ではこれを禁止要求ビットと呼ぶ。外部コーデックがこれらのビットを1にセットしたときは、対応するスロットは後続のフレームでSDATAOUTにデータを送ってはならない。外部コーデックがこれらのビットを0にセットしたときは(コントローラの送信制御レジスタ内でセットされたアクティブ出力データ・スロットのために)、対応するスロットは次のフレームでSDATAOUTにデータを送らなければならない。コントローラが特定のデータ・スロットのデータ項目を記憶する準備をしていない場合は、禁止要求ビットはそのデータ・スロットに影響を与えない。かかる場合は、次のフレームのそのデータ・スロットで0が送信される。

【0037】

コントローラ内の関連するデータ・バッファ(要求されたデータ・スロットのデータ項目を記憶する準備をした)内に送信するデータがない場合はアンダーフローが発生して、データ・バッファが空でなくなるまで、または送信が禁止されるまで、無効データ(全て0)がそのデータ・バッファから送信される。マイクロプロセッサ20は送信割込み要求に応じて十分な速度で送信データを書き込み、アンダーフローエラー状態を防ぐように調整されている。

SDATAINスロット0に関する前の説明に関して述べると、注意すべきはスロット1の有効性に関するスロット0内の関連ビットはレジスタ・アドレスの有効性(すなわち、ビット18−12内のデータの有効性)だけに関係するので、コントローラはスロット0内のスロット1の有効性ビットの値に関係なく禁止要求ビットを調べることである。

【0038】

SDATAINスロット2:状態データ

スロット2は前の読取り要求からコントローラが要求した制御レジスタ・データを返す。スロット0内のコーデック状態ビットによりスロット2が無効という「タグを付けられている」場合は、コーデックはスロット全体に0を入れる。ビット19−4はコントローラに返す16ビットのコーデック・レジスタ値を含む。ビット3−0は0で返す。

SDATAINスロット3:左チャンネルPCM捕獲データ

スロット3は左チャンネルADCデータを含む。ディジタル化された信号はレジスタ1Ahを介して選択され、そのレジスタのデフォルト値は0000hであり、MIC入力を選択する。これは20ビットのスロットで、1PCMデータはMSBから先に返され、最後に残ったビットは0である。

【0039】

SDATAINスロット4:PCMレコード右チャンネル

スロット4は右チャンネルADCデータを含む。ディジタル化された信号はレジスタ1Ahを介して選択され、そのレジスタのデフォルト値は0000hであり、MIC入力を選択する。これは20ビットのスロットで、18ビットのPCMデータはMSBから先に返され、最後に残った2ビットは0である。

SDATAINスロット5:モデム1ADC

スロット5はモデム・ライン1ADC出力データを含む。

SDATAINスロット6:マイクロホン・レコード・データ

スロット6はマイクロホン・レコード・データを含む。

【0040】

SDATAINスロット7−9:予約(1スロット・タッチスクリーン?)

現在これらのスロットは予約であるが、スロットからデータが要求された場合は受信FIFOは送られたデータを受け付けることができる。

SDATAINスロット10:モデム2ADC

スロット10はモデム・ライン2ADC出力データを含む。

SDATAINスロット11:ヘッドセットADC

スロット11はヘッドセットADC出力データを含む。

SDATAINスロット12:

スロット12はIO状態データを含む。

【0041】

SDATAINへの入力データはコントローラがBITCLKの立下がりエッジでサンプリングする。

外部コーデックを起動する前に、コントローラはコーデックが「コーデック作動可能」であることを示すオーディオ・フレーム入力内の第1ビット(SDATAINスロット0、ビット15)をポーリングしなければならない。

スロット0で受信した第1ビットはグローバル・ビットで、これはコーデックが「コーデック作動可能」状態であるかどうかを示すフラグである。「コーデック作動可能」が0の場合はコーデックの通常の作動が可能でないことを示す。「コーデック作動可能」が1の場合は、制御レジスタと状態レジスタは完全に作動状態にある。次にユーザは更に別の制御/状態レジスタを調べて、作動可能な装置部分があるかどうか判定しなければならない。

【0042】

図3から分かるように、SYNC信号毎に各データ・スロットを一度サンプリングすることができる。前に述べたように、好ましい実施の形態ではSYNC信号は48kHzに固定されている。しかしSDATAINスロット1の以前の説明から明らかなように、コーデックはスロット3から12で禁止要求ビットを出すことができるので、これらの10スロットは可変サンプリング速度を持つことができる。本発明の好ましい実施の形態のコントローラは新規な構造を持ち、スロット毎に別個のデータ・バッファを設けなくても可変サンプリング速度スロットと固定サンプリング速度スロットを支援することができる。好ましい実施の形態のコントローラの構造を図4に示す。

【0043】

図4に示すように、コントローラは4つのチャンネル110、120、130、140を備える。好ましい実施の形態では、各チャンネルは、ACリンクに出力するデータ項目のための送信データ・バッファと、ACリンクから受信するデータ項目のための受信データ・バッファと、送信データ・バッファと受信データ・バッファのための別々の制御レジスタを内蔵する。好ましい実施の形態では、データ・バッファはFIFOで実現される。全てのACリンク・スロットを支援するのに必要なチャンネルの最小数は4であることが分かっており、これによりモデム、オーディオ、ヘッドセット、マイクロホンのチャンネル間を独立にすることができる。

【0044】

コントローラが各フレームの全てのスロットを支援できるようにするために、好ましい実施の形態のコントローラは、データ要素の複数のグループのサンプリング速度が同じであるという仮定に基づいている。したがって、全てのオーディオ・データは同じサンプリング速度であり、全てのモデム・データは同じサンプリング速度であると仮定する。例えば、外部コーデックがPCMLEFT、PCMRIGHT、MODEM1、PCMCENTRE、PCMLSURROUND、PCMRSURROUND、PCMLFE、MODEM2、HSETのチャンネルを支援する場合は、送信データ・バッファでは全てのオーディオ・データはチャンネル1を通り、モデム・データはチャンネル2を通り、HSETデータはチャンネル3を通るようにチャンネル内の制御レジスタをプログラムしてよい。またコントローラはMICデータを異なる速度で受信し、これをチャンネル4を通して受信することができる。または、受信データ・バッファの各チャンネルに別個の制御レジスタが設けられるので、MICデータは適当と考えられる任意の他のチャンネルを通して受信することができる。

【0045】

各FIFOに関連する制御レジスタを設けることにより、コントローラは特定のデータ要素に関するデータ項目を極めて柔軟に処理することができる。詳しく述べると、制御レジスタ内の制御データをセットすることによりどのデータ要素のためのデータ項目を対応するデータ・バッファ内に記憶するかを規定することができるので、任意のデータ・バッファを用いてフレーム内の任意のデータ・スロットと授受する任意のデータ項目を記憶することができる。しかし好ましい実施の形態では、この自由度を制限して任意の特定のデータ・バッファ内に記憶されるデータ項目が同じサンプリング速度を持つデータ要素だけに関係するようにして、FIFOバッファを用いてコントローラ内の制御機構を簡単化する。

【0046】

図5は、図4に示すチャンネル110内の要素の詳細を示す。好ましい実施の形態では、4つのチャンネルはそれぞれ同じ構造を有する。チャンネル110の受信部は受信制御レジスタ230を介して制御される。このレジスタは、どのデータ要素のためのデータ項目を関連するFIFOバッファ210内に記憶するか、したがってオーディオ・フレーム内のどのデータ・スロットからデータ項目をFIFOバッファ210内に記憶するか、を識別する制御データを含む。前に述べたように、受信制御レジスタ230内の制御データは、FIFO210内に記憶されている全てのデータ項目が同じサンプリング速度になるようにセットしなければならない。

【0047】

どのデータ要素のためのデータ項目をFIFOバッファ210内に記憶するかを規定するだけでなく、制御レジスタ230はデータ項目の実際に必要なビット数も識別する。前に述べたように、データ項目はデータ・スロットで転送するときは固定サイズ(好ましい実施の形態では20ビット)で表すが、データ項目の実際のサイズは20ビット以下でよい。好ましい実施の形態では、受信制御レジスタ230は、マイクロプロセッサとコントローラとの間のデータ項目の転送方法に影響を与えるコンパクト・モードを可能にするフィールドも含む。このコンパクト・モードについては後で詳細に説明する。

【0048】

図6は、本発明の好ましい実施の形態に係る、受信制御レジスタ230内の種々の制御データ・ビットの関連を示す表である。必要であれば制御レジスタは、例えばFIFOが使用可能かどうかを示したり、タイムアウト・カウント値を与え(例えばFIFOが空でないのに或る時間他のデータを受信しなかったときに、関連するFIFOはタイムアウト割込みを発生する機能を有する)たりする追加のビットを記憶してもよい。

【0049】

次にチャンネル110の送信部に移ると、これは送信制御レジスタ220を介して制御される。このレジスタは、オーディオ・フレームのどのデータ・スロットで関連するFIFO200内のデータ項目を送信するか、すなわちどのデータ要素のためのデータ項目をFIFO200内に記憶するか、を指定するのに用いられる。チャンネルの受信部と同様に、好ましい実施の形態に係る制御データは、FIFO200内の全てのデータ項目が同じサンプリング速度を持つデータ・スロットに用いれられるようにセットしなければならない。また好ましい実施の形態では、データ項目は最小のスロット番号から先に出して、適当な順序でフレーム生成器/デコーダ100に送るようにしなければならない。また制御レジスタ内のデータは、マイクロプロセッサ20からコントローラ30に送るデータのデータ項目の長さを20ビットにするために追加すべきビット数を識別する。受信制御レジスタと同様に、好ましい実施の形態ではコンパクト・モード動作を可能にするためのフィールドも設ける。図7は、送信制御レジスタ220内の種々の制御データ・ビットの意味を示す表である。

【0050】

また好ましい実施の形態では、制御レジスタ220はデータ項目を送信する前にFIFO200内に置かなければならないデータ語の数を識別するのにも用いられる。FIFO200内に十分なデータ項目が存在しないときにコーデック70がチャンネルを通すデータ・スロットのデータ項目を要求した場合は、好ましい実施の形態ではアンダーフロー割込みが発生する。理解されるように、FIFO内のデータ項目の数は、そのデータ項目をFIFO内に記憶することのできるデータ要素の数(送信制御レジスタ220内のTXビットで示す)以上でなければならない。

【0051】

またチャンネルの送信部は、外部コーデックから入力データ・ストリームのスロット1で送信されるデータ要求禁止ビットを介して、可変サンプリング速度を支援する。これらのビットはフレーム生成器/デコーダ100で復号され、図4に示す該当するチャンネル110、120、130、140に送られ、次の出力オーディオ・フレームでこれらのチャンネルからデータ項目を出力すべきかどうかを示す。

【0052】

また好ましい実施の形態では、送信FIFO200内の有効語のビットを用いて、FIFO内の対応するデータ項目が有効であって次の利用可能なフレームで送ることができるかどうか判定する。送信のスロット0は、送信制御レジスタ220内の値と、データ要求禁止ビットと、有効な送信データを有するFIFOに基づいて、コントローラが決定する。或るスロットが或るフレーム内に送信データを持たない場合は、コントローラは対応するデータ・スロットに0を入れる。前に述べたように、次のフレームでデータを出力ことをデータ要求禁止ビットが指示しているのに対応するFIFO内にデータ項目がない場合は、コントローラはアンダーフロー割込みを発生させる。コーデックは所定のサンプリング速度の全てのデータ要求禁止ビットを同時にセットする(例えば、オーディオ・データの全てのデータ要求禁止ビットを同時にセットする)と仮定する。前に述べたように、好ましい実施の形態では同じサンプリング速度を持つデータ項目は好ましくは同じ送信FIFO200内に記憶されており、要求されたときは好ましくはFIFO内に送信データ項目が存在しなければならない。

【0053】

外部コーデックがデータ要求禁止ビットをサポートしていない場合はこれらのビットは常に0にセットされて、標準サンプリング速度の48kHzであることを示す。しかし前に述べたように、外部コーデックがデータ要求禁止ビットをサポートしているかどうかに関わらず、データ要求禁止ビットはコントローラがデータ項目を送信する準備をしていないデータ・スロットには影響を与えない。かかるデータ・スロットについては、コントローラは次のフレームで0を出力する。

【0054】

好ましい実施の形態ではスロット1と2は常に48kHzで送信されるので、外部コーデックはこれらのスロットにデータ要求禁止ビットを与えない。本発明の好ましい実施の形態では、図4に示すように別々のレジスタ150、160、170を設けてスロット12、1、2のデータ項目をそれぞれ記憶する。したがってスロット1、2、12で送信されるデータは、チャンネル110、120、130、140がこれらのデータ・スロットに関連するデータ項目を記憶するよう決められている場合はこの4つのチャンネルの1つから、またはレジスタ150、160、170から直接、得ることができる。好ましい実施の形態では、制御データをセットすることにより特定のスロットのデータ項目の発信源を1つに制限しなければならない、そのため、レジスタ150、160、170をスロット12、1、2のデータ項目に用いる場合は、チャンネル110から140内の制御レジスタの関係する制御ビットはセットせず、これらのチャンネルがこれらのスロットのデータ項目を処理しないようにしなければならない。しかしこれらのデータ・スロットのデータがレジスタ150、160、170とチャンネル110から140の1つに存在する場合は、コントローラにデフォルト値をセットする(例えばデータ項目をまず関連するチャンネルで送る)ことができる。

【0055】

好ましい実施の形態では、スロット1、2、12のデータ項目を受信するとき、関連する制御ビットが関連する制御レジスタ内ですでにセットされている場合は、データ項目は該当するチャンネル内に記憶し、レジスタ150、160には記憶しない。しかし関連する制御ビットがチャンネル内にセットされていない場合は、データ項目は必ずレジスタ150、160に入る。

好ましい実施の形態では、外部コーデックが作動準備中のときは、各チャンネルはスロット1と2のデータを送信することにだけ用いられる。外部コーデックの準備が完了したとき、スロット1と2のデータ項目はレジスタ160、170を介して送るのが好ましい。これにより利用可能なチャンネルを空けることができる。

【0056】

次に図5に戻って、アンパッカ240、リサイザ245、リサイザ255、パッカ250の目的について詳細に説明する。まず送信アンパッカ240であるが、前に述べたように送信制御レジスタ220はコンパクト・モード(CM)ビットを有し、これをセットすることによりマイクロプロセッサ20からのデータは32ビット語か16ビット語かを決定する。また送信制御レジスタは、送信すべきデータ項目の実際のサイズを示すTSIZEビットを含む。データ項目の長さが12ビットまたは16ビットを示すようTSIZEビットがセットされ且つCMビットがセットされた(好ましい実施の形態では論理1の値に)場合は、マイクロプロセッサからコントローラに送られる32ビット語は2つのデータ項目を含む。このときアンパッカ240は32ビット語を2つの16ビット成分に分割するのに用いられる。注意すべきであるが、このコンパクト・モードはTSIZEビットが12ビットまたは16ビットにセットされた場合だけ動作し、18ビットまたは20ビットにセットされた場合は動作しない。また、CMビットがセットされていない(すなわち、好ましい実施の形態では論理0値にセットされている)場合は、マイクロプロセッサからコントローラに送られる32ビット語は、TSIZEが12ビットまたは16ビットにセットされている場合でも内容は1つのデータ項目だけを含む。好ましい実施の形態では、CMビットがセットされている場合は、FIFOバッファは偶数のデータ項目(例えば、スロット3と4のデータ項目であって、スロット3、4、5のデータ項目ではない)を受け入れるようにしなければならない。

【0057】

アンパッカ240が必要なアンパッキングを行うと、送信リサイザ245により各データ項目のサイズを20ビット表現に変更する。前に述べたように、送信制御レジスタ内のTSIZEビットはマイクロプロセッサから受信したデータ項目の実際のサイズを示す。したがって要求に応じてデータをアンパックすると、リサイザ245はデータ項目を所要量だけ左にシフトして20ビット語を作り、FIFO200内に記憶する。好ましい実施の形態では最下位の各ビットに0を入れる。TSIZEが20にセットされている場合は、左シフトも0注入も必要ない。また注意すべきであるが、好ましい実施の形態ではデータ項目はFIFOで最小のスロット番号から先に記憶して、後でこれらのデータ項目をフレーム生成器/デコーダ100に適当な順序で与えることができるようにする。例えば、データスロット3と4に関するデータ項目を記憶するようFIFO200を準備した場合は、先にスロット3のデータ項目をFIFOに入れ、次にスロット4のデータ項目をFIFOに入れる。TSIZEが12ビットまたは16ビットにセットされ且つコンパクト・モードがセットされた場合は、マイクロプロセッサから受信したデータ語内のビット15:0はスロット3のデータ項目を含み、ビット31:16はスロット4のデータ項目を含まなければならない。

【0058】

出力オーディオ・フレームをフレーム生成器/デコーダで構築するときは、データ項目をFIFOバッファ200から20ビット語ずつ取り出す。フレーム生成器/デコーダ100は並列直列シフト変換器を内蔵する。この変換器はデータ項目のビットを最上位ビットから先に出力する。

チャンネル110の受信部に戻り、データ項目を直列並列シフト変換器からFIFOに読み取るときデータは最上位ビットから先に与えられる。FIFOが満杯であるのに受信チャンネルが更にデータを受信した場合は受信オーバーラン割込みが用いられる。

【0059】

前に述べたように、オーディオ・フレームのデータ・スロットで転送するときデータ項目は20ビットの固定長であり、これらの20ビットのデータ項目は受信FIFO210内に記憶される。受信制御レジスタ230内のRSIZEビットは受信バッファ210内に記憶されたデータ項目の実際のサイズを示す。20ビットのデータをFIFOから読み出してマイクロプロセッサに送信するときに、リサイザ255はこのRSIZEビット情報を用いて最下位ビット(LSB)を調整する。RSIZEビットが12ビット、16ビット、18ビットのデータ項目を示すようセットされている場合は、リサイザ255はFIFOからの20ビットのデータを必要量だけ右にシフトして、データ項目の正しいデータサイズを形成する。例えば、データ項目の長さが12ビットであることをRSIZEが示す場合は、FIFOからの20ビット語を8ビット位置だけ右にシフトする。次にリサイザはデータ語の最上位の各ビットに0を入れる。またコンパクト・モード・ビットはリサイザ255が作成したデータ語のサイズを決定する。

【0060】

また注意すべきであるが、受信チャンネル内のデータ項目は最小のスロット番号から先に出さなければならない。したがって、例えば受信FIFO210がデータ・スロット3と4からのデータ項目を記憶するよう準備されている場合は、FIFOからの最初のデータ項目はスロット3に関係し、次のデータ項目はスロット4に関係する。RSIZEの値が12ビットまたは16ビットにセットされていて且つコンパクト・モード・ビットがセットされた場合は、好ましい実施の形態ではスロット3に関するデータ項目はマイクロプロセッサに送信されるデータ語のビット15:0に含まれ、スロット4のデータ項目はこのデータ語のビット31:16に含まれる。

【0061】

この過程は受信パッカ250が行い、CMビット情報とRSIZEビット情報に基づいて、2つのデータ項目を1つのデータ語にまとめてマイクロプロセッサに送ることができるかどうか判断する。詳しく述べると、コントローラが出力する32ビット語を2つのデータ項目で構成することができる場合は、パッカ250はリサイザ255からの2つのデータ語を結合して1つの32ビット語にする。前にチャンネルの送信部の説明で述べたように、コンパクト・モードはRSIZEビットを12ビットまたは16ビットにセットしたときだけ動作する。また、コンパクト・モードがセットされていない場合は、RSIZEが12ビットまたは16ビットにセットされていても、コントローラから出力される32ビット語の内容は1データ語だけである。またコンパクト・モードがセットされている場合は、ユーザはFIFOチャンネルが偶数のデータ項目を受信するよう準備されている(例えばスロット3と4のデータ項目であってスロット3、4、5のデータ項目ではない)ことを確認しなければならない。

【0062】

当業者が理解するように、リサイザ245および255、パッカ250、および/またはアンパッカ240の1つまたは複数の機能をチャンネルの外部に設けて1個の論理ユニットにより全てのチャンネルのこれらの機能を処理し、チャンネルの制御レジスタを介して制御することもできる。

【0063】

本発明の好ましい実施の形態に係るフレーム生成器/デコーダ100の動作について、図8と図9の流れ図を参照して以下に詳細に説明する。まず図8は、フレーム生成器/デコーダ100が出力フレームXを生成する流れを示す。ステップ300で始まり、流れはステップ320に進んで、前の入力フレームX−1のスロット1からのデータ要求禁止ビットを調べる。前に述べたように、データ要求禁止ビットが外部コーデックにより支援されていない場合はこれらのビットは0にセットされており、これは全てのデータスロットに標準のサンプリング速度を用いなければならないことを示す(したがって好ましい実施の形態では全てのデータ・スロットのデータ項目は理論的には次のフレーム(フレームX)で出力しなければならない)。しかしデータ要求禁止ビットが外部コーデックにより支援されている場合は、1つまたは複数のビットが1にセットされており、対応するデータ・スロットのデータ項目をフレームXで出力してはならないことを示す。

【0064】

データ要求禁止ビットが支援されているかどうかに関わらず、コントローラはコントローラが記憶するよう準備されているデータ要素に対応するデータ・スロット内のデータ項目だけを出力することができる。したがって一例として、コントローラのどの送信FIFOもモデム・ライン1のデータを処理するよう準備されていない場合は、関連するデータ要求禁止ビットの値に関わらず、コントローラは対応するデータ・スロット(データ・スロット5)で有効データを出力することができない。したがって、ステップ320でデータ要求禁止ビットを調べるだけでなく、流れはステップ330に進んで、送信制御レジスタ内の制御データを参照する。この制御データとデータ要求禁止ビットの値に基づいて、フレーム生成器100はどのデータ・スロットのためのデータ項目が出力フレームXで要求されているか判定する。したがって好ましい実施の形態では、関連するデータ要求禁止ビットが0にセットされ、制御データが送信FIFOの1つがそのデータ・スロットのデータ項目を処理するセットされている場合、一つのデータ・スロットが必要である。

【0065】

次に流れはステップ340に進み、全ての要求されたスロットのデータ項目が利用可能かどうか判定する。前に述べたように、好ましい実施の形態では、コントローラはデータ・バッファ内に十分なデータ項目が常に存在するように管理するので、全ての要求されたスロットのデータ項目が利用可能であるはずであり、このとき流れはステップ360に進む。しかしいくつかのデータ項目が利用可能でない場合は流れはステップ350に分岐し、割込みが発生する。理解されるように、割込みは多くの異なる方法で処理することができる。例えば、割込みを用いて、要求されたデータ項目をメモリから関連するデータ・バッファに取り出した後、流れを再開してよい。受信FIFOと送信FIFOに常に十分なデータ項目が存在するようにコントローラがこれらのFIFOを管理する方法については、後で図10と図11を参照して詳細に説明する。

【0066】

流れがステップ340からステップ360に進んだ場合は、フレーム生成器100はスロット0のデータを生成してこれを転送する。前に述べたように、スロット0のデータは、コントローラの関連するデータ・バッファ内のデータ項目の有効性と、送信制御レジスタ内の値と、可変速度が可能な場合のフレームX−1の入力スロット1からの禁止要求ビットの値、に基づいて生成される。スロット0のデータを転送する前に、ACリンクに出力するために並列直列変換器を用いてスロット0のビットを直列データ・ストリームに変換する。

【0067】

ACリンクで送信のためのデータ転送が一度行われると、ステップ370で変数「n」を1にセットし、次にステップ375に進んでスロットnのデータ項目が要求されているかどうか判定する。この判定は、前にステップ330で決定した情報を参照してコントローラが行う。このスロットのデータ項目が要求されていない場合は、コントローラはステップ378で全て0のデータ項目を生成する。次に流れはステップ400に進み、並列直列変換を行い、データを転送して、ACリンクで送信するデータ・フレームの該当するスロットで送信する。

【0068】

ステップ375で、スロットnにデータ項目が要求されていると判定した場合は、流れはステップ380に進んでどのチャンネルがスロット(n)のデータ項目を有するか判定する。この判定を行うため、フレーム生成器100は送信FIFOに関連する送信制御レジスタ内のデータを調べる。これらの制御レジスタは、対応する送信FIFOがどのデータ要素(したがってどのデータ・スロット)のデータ項目を記憶しているかを識別する制御データを含む。この判定を行った後、ステップ390でフレーム生成器100は関連するチャンネルの送信FIFOからデータ項目を読み出し、次に流れはステップ400に進んで並列直列変換を行い、データを転送して、ACリンクで送信するデータ・フレームの該当するスロットで送信する。

【0069】

次に、各フレーム内のデータ・スロット(スロット0を除く)の数nMAXに対して、ステップ410でnがnMAXに等しいかどうか判定する。nがnMAXに等しい場合は流れはステップ430に進んで終了する。等しくない場合は流れはステップ420に進み、nを1だけ増分してステップ375に戻り、次のデータ・スロットのデータ項目を生成する。

【0070】

図9は、ACリンクから受信したデータの入力フレームを復号するときの、好ましい実施の形態で行われる流れを示す流れ図である。流れはステップ500で始まり、ステップ510に進んでスロット0を受信してキャッシュ内に記憶する。この流れでは、スロット0のデータは直列並列変換器を通って、キャッシュ内に記憶するデータ項目を生成する。このデータは入力データ・フレームの残りのスロット内のデータの有効性を示すのでキャッシュ内に記憶し、フレーム・デコーダ100は入力フレームを復号するときにこれを参照する必要がある。

次にステップ520で変数「n」を1にセットした後、流れはステップ530に進んでスロットnからのデータ項目を20ビットのレジスタに読み込む。この場合も、流れはACリンクから受信した直列データの直列並列変換を行い、レジスタ内に記憶する20ビットのデータ項目を生成する。

【0071】

次に流れはステップ540に進み、このデータ項目が有効かどうか判定する。この流れは、データ項目が有効かどうかを調べるために、ステップ510でフレーム・デコーダ100がキャッシュ内に記憶したスロット0のデータを調べることを含む。データ項目が無効な場合は、流れはステップ545に進んでnが1かどうか判定する。1の場合は流れはステップ570に進む。ステップ570については後で説明する。しかしnが1でない場合は流れはステップ580に進み、nがnMAXに等しいかどうか、すなわちフレーム内の最後のデータ・スロットを受信したかどうか判定する。等しい場合は流れはステップ590に分岐して終了する。等しくない場合は流れはステップ585に進み、nを1だけ増分してステップ530に戻り、入力フレーム内の次のスロットからデータ項目を読み取る。

【0072】

ステップ540で現在のデータ・スロットのデータ項目が有効であると判定した場合は、ステップ550でどのチャンネルがスロットnのデータ項目を記憶するかを判定する。フレーム・デコーダ100は各チャンネル内の受信FIFOに関連する受信制御レジスタを参照してこの判定を行う。これらの受信制御レジスタは、対応する受信FIFOがどのデータ要素(したがってどのデータ・スロット)のデータ項目を記憶しているかを識別する制御データを含む。

【0073】

該当するチャンネルを識別すると、ステップ560でデータ項目を20ビットのレジスタから関連するチャンネルの受信FIFOに送る。更にステップ570で、nが1の場合はデータ項目をキャッシュにも記憶する。これは後でフレーム生成器/デコーダ100が後続の出力フレームの送信確認を行うのに用いる。この流れについては図8を参照してすでに説明した。

次に流れはステップ580に戻り、nがnMAXに等しいかどうか判定する。等しい場合は流れは終了する。等しくない場合はnを1だけ増分して、流れはステップ530に戻る。

【0074】

フレーム生成器/デコーダ100が出力フレームを生成しまた入力フレームを復号する方法を上に説明したが、次に、コントローラ内で特定のチャンネルの受信および送信FIFOの内容を管理する流れについて、図10と図11を参照して詳細に説明する。図10は、コントローラが受信FIFOの内容を管理する方法を示す流れ図である。好ましい実施の形態では、この流れは受信FIFO毎に独立に行われる。まずステップ600で、関連する受信制御レジスタから、受信FIFOに記憶するデータ項目を有するデータ要素の数(変数Zとする)を決定する。したがって、対応するFIFOがスロット3と4のデータ項目を記憶することを制御レジスタ内の制御データが示す場合はZは2である。

【0075】

次にステップ610で、Zの値に従ってFIFOの変数「MAXNUMBER」を決定する。理解されるように、MAXNUMBERの適当な値を決定するのに種々のアルゴリズムを用いてよい。例えば、FIFOが6項目を記憶することが可能であり且つZが2の場合は、該当するMAXNUMBERは2か4でよい。MAXNUMBERを6にセットとした場合は、何らかの方法で受信FIFOからメモリにデータ項目を移す前にFIFOは満杯になることを意味する。これでは後続の入力フレームで受信した新しいデータ項目を受信FIFOに記憶することができないので、明らかに良くない。

【0076】

MAXNUMBERが決まると流れはステップ620に進み、FIFO内のデータ項目の数がMAXNUMBER以上かどうか判定する。データ項目の数がMAXNUMBER以上でない場合は流れはステップ620に戻り、以上である場合はステップ630に進む。ステップ630で、マイクロプロセッサが所定数(以後「PZ」で表し、Pは整数)のデータ項目をFIFOから読み出すようコントローラはマイクロプロセッサに要求する。これにより、データ項目をFIFOからメモリに読み出したとき、FIFOが管理するデータ項目を有するデータ要素の数は必ず整数になる。例えば、受信FIFOが3個のデータ要素(例えばデータ・スロット3、4、5)のデータ項目を記憶している場合は、マイクロプロセッサは受信FIFOから3の倍数のデータ項目だけを読み出す。

ステップ630を実行すると、流れはステップ620に戻る。好ましい実施の形態では、ステップ620をクロック・サイクル毎に繰り返す。

【0077】

次に送信FIFOの管理に移り、図11にこの流れの詳細を示す。好ましい実施の形態では、この流れは送信FIFO毎に独立に行われる。ステップ700で、コントローラは特定の送信FIFOの送信制御レジスタから、FIFOに記憶してよいデータ項目を有するデータ要素の数Zを決定する。これは図10に示したステップ600と同様である。

【0078】

次に流れはステップ710に進み、Zの値に従って送信FIFOの変数「MINNUMBER」を決定する。当業者に理解されるように、この場合もMINNUMBERの適当な値を決定するのに種々のアルゴリズムを用いてよい。好ましい実施の形態では、MINNUMBERはどんな場合でもZ以上の値を選択する。なぜなら、データ・フレームのデータ・スロットで送信するためにデータ項目を送信FIFOから読み出すとき特定のフレームのZ個のデータ項目を読み出すので、送信FIFOには少なくともZ個のデータ項目が存在しなければならないからである。

【0079】

変数MINNUMBERが決まると、流れはステップ720に進んで送信FIFO内のデータ項目の数がMINNUMBER以下かどうか判定する。データ項目の数がMINNUMBER以下でない場合は流れはステップ720に戻り、以下の場合はステップ730に進む。

【0080】

ステップ730で、送信FIFOに記憶する所定数「PZ」(Pは整数)のデータ項目を送るようコントローラはマイクロプロセッサに要求する。これにより、マイクロプロセッサはFIFOに記憶するデータ項目の該当する数を送る。例えば、FIFOがデータ・スロット3、4、5のデータ項目を記憶している場合は、これによりマイクロプロセッサは3の倍数の多数のデータ項目を送る。例えば、3個のデータ項目をスロットに1つ、スロット4に1つ、スロット5に1つ送る。

ステップ730を実行すると流れはステップ720に戻り、再び送信FIFO内のデータ項目の数がMINNUMBER以下かどうか判定する。好ましい実施の形態では、ステップ720をクロック・サイクル毎に繰り返す。

【0081】

当業者に理解されるように、図10と図11に示した流れを変更しても、やはり送信および受信FIFOを効率的に管理することができる。例えば簡単化された方法として、データ要素の数Zは各制御レジスタ内にセットされた制御データに従って変化するので、MAXNUMBERとMINNUMBERをZに従わせず、固定数であるFIFO内の項目の総数に従ってセットしてよい。一例を挙げると、FIFOが8つの項目を持つ(したがって8つのデータ項目を記憶することができる)場合は、MAXNUMBERとMINNUMBERを4(すなわち、FIFOのサイズの半分)にセットするとよい。これにより、図10のステップ600および610と、図11のステップ700および710はなくなる。しかしステップ630と730を参照すると、どの転送シーケンスでもやはりデータ項目の所定数PZをFIFOとメモリとの間で転送することが好ましい。

【0082】

本発明の特定の実施の形態について説明したが、本発明はこれに限定されるものではなく、発明の範囲内で種々の変更や追加が可能なことは明らかである。例えば、本発明の範囲から逸れることなく特許請求の範囲の各請求項の特徴を種々に結合することができる。

【図面の簡単な説明】

本発明について、以下の図面に示す好ましい実施の形態を参照して説明した。

【図1】本発明の好ましい実施の形態に係る、コントローラを用いるチップのブロック図。

【図2】本発明の好ましい実施の形態に係る、コントローラとオーディオ・コーデックとの間のインターフェースを示す図。

【図3】出力および入力のデータ・ストリームのオーディオ・フレームの内容を示す図。

【図4】本発明の好ましい実施の形態に係る、コントローラの要素の詳細を示すブロック図。

【図5】本発明の好ましい実施の形態に係る、コントローラ内に設けられたチャンネルの詳細を示すブロック図。

【図6】本発明の好ましい実施の形態に係る、受信データ・バッファに関連する制御レジスタ内の制御データを示す表。

【図7】本発明の好ましい実施の形態に係る、送信データ・バッファに関連する制御レジスタ内の制御データを示す表。

【図8】本発明の好ましい実施の形態に係る、出力フレームを生成する流れを示す流れ図。

【図9】本発明の好ましい実施の形態に係る、入力フレームを復号する流れを示す流れ図。

【図10】本発明の好ましい実施の形態に係る、受信データ・バッファを管理する流れを示す流れ図。

【図11】本発明の好ましい実施の形態に係る、送信データ・バッファを管理する流れを示す流れ図。

【符号の説明】

30 コントローラ

60 データ・リンク

110−140 チャンネル

200,210 データ・バッファ

220,230 制御レジスタ

Claims (16)

- 多数のデータ要素に関係するデータ項目をデータ・リンクの対応するデータ・スロットで転送するデータ・リンクにおいて、前記データ・リンクとのインターフェースを制御するコントローラであって、

少なくとも1つのチャンネルであって、各チャンネルはデータ項目を記憶するデータ・バッファと、前記データ・バッファに関連し且つ制御データを記憶する制御レジスタとを備え、前記制御データはどのデータ要素のためのデータ項目をそのデータ・バッファ内に記憶するかを規定するようセット可能であり、前記コントローラにより提供されるチャンネルの数は前記データ・リンクで転送することのできるデータ項目を有するデータ要素の数より少ない、少なくとも1つのチャンネルと、

前記制御データに従って前記少なくとも1つのチャンネルと前記データ・リンクのデータ・スロットとの間のデータ項目の転送を制御するインターフェース機構と、

を備える、コントローラ。 - 前記少なくとも1つのチャンネルの少なくとも1つのデータ・バッファは前記制御データが指定する1つ以上のデータ要素に関係するデータ項目を前記データ・リンクにより送信する前に記憶し、前記インターフェース機構は前記制御データに応じて前記データ・バッファから取り出したデータ項目を対応する1つ以上のデータ・スロットで前記データ・リンクにより送信する、請求項1に記載のコントローラ。

- 前記少なくとも1つのチャンネルの少なくとも1つのデータ・バッファは前記データ・リンクから受信し且つ前記制御データが指定する1つ以上のデータ要素に関係するデータ項目を記憶し、前記インターフェース機構は前記制御データに応じて対応する1つ以上のデータ・スロットから受信したデータ項目を前記データ・バッファ内に記憶する、請求項1に記載のコントローラ。

- 各チャンネルは1対の前記データ・バッファとその関連する制御レジスタを備え、前記データ・バッファの一方は前記データ・リンクにより送信するデータ項目を記憶し、前記データ・バッファの他方は前記データ・リンクから受信したデータ項目を記憶する、請求項1に記載のコントローラ。

- 各データ・バッファは同じサンプリング速度を有する1つ以上のデータ要素に関係するデータ項目を記憶する、請求項1に記載のコントローラ。

- 前記コントローラは前記データ・リンクを介してコーデックに接続可能である、請求項1に記載のコントローラ。

- 各データ・バッファは先入れ先出し(FIFO)バッファを備える、請求項1に記載のコントローラ。

- 前記コントローラをメモリに結合して前記メモリと前記少なくとも1つのチャンネルとの間にデータ項目を転送することができるメモリ・インターフェースを更に備える、請求項1に記載のコントローラ。

- 前記メモリ・インターフェースは前記メモリへのアクセスを制御するプロセッサを介して前記コントローラを前記メモリに結合する、請求項8に記載のコントローラ。

- 各制御レジスタは前記関連するデータ・バッファと前記メモリの間で転送されるデータ語が複数の前記データ項を含むコンパクト・モードであることを示すためにセット可能な第1フィールドを有する、請求項8に記載のコントローラ。

- 前記データ・スロットで転送するときのデータ項目は固定サイズで表され、各制御レジスタは、前記関連するデータ・バッファ内に記憶されているデータ項目の実際のサイズを示すためにセット可能な第2のフィールドを有し、前記第1のフィールドがセットされた場合は前記メモリ・インターフェースは前記第2のフィールドを参照して、前記関連するデータ・バッファと前記メモリとの間で転送される各データ語内にデータ項目をいくつ含めるかを決定する、請求項10に記載のコントローラ。

- 前記データ・スロットで転送するときのデータ項目は固定サイズで表され、各制御レジスタは、前記関連するデータ・バッファ内に記憶されている各データ項目の実際のサイズを示すためにセット可能なフィールドを有し、これにより前記メモリ・インターフェースは前記データ項目を実際のサイズと固定サイズとの間で変換することができる、請求項8に記載のコントローラ。

- 前記制御レジスタ内の制御データは前記関連するデータ・バッファ内に記憶されているデータ項目を有するデータ要素の数を指定し、前記メモリ・インターフェースは前記制御データに従って前記データ・バッファと前記メモリの間のデータの転送速度を制御する、請求項8に記載のコントローラ。

- 多数のデータ要素に関係するデータ項目をデータ・リンクの対応するデータ・スロットで転送するデータ・リンクにおいて、前記データ・リンクとのインターフェースを制御する方法であって、

(a) データ項目を記憶するデータ・バッファと前記データ・バッファに関連する制御レジスタをそれぞれ備える少なくとも1つのチャンネルを設け、

(b) どのデータ要素のためのデータ項目を前記関連するデータ・バッファ内に記憶するかを規定する制御データを前記制御レジスタ内に記憶し、前記ステップ(a)で提供されるチャンネルの数は前記データ・リンクで転送することのできるデータ項目を有するデータ要素の数より少なく、

(c) 前記制御データに従って前記少なくとも1つのチャンネルと前記データ・リンクのデータ・スロットとの間のデータ項目の転送を制御する、

ステップを含む方法。 - 前記少なくとも1つのチャンネルの少なくとも1つのデータ・バッファは前記制御データが指定する1つ以上のデータ要素に関係するデータ項目を前記データ・リンクにより送信する前に記憶し、前記ステップ(c)は前記制御データに応じて前記データ・バッファから取り出したデータ項目を前記対応する1つ以上のデータ・スロットで前記データ・リンクにより送信する、請求項14に記載の方法。

- 前記少なくとも1つのチャンネルの少なくとも1つのデータ・バッファは前記データ・リンクから受信し且つ前記制御データが指定する1つ以上のデータ要素に関係するデータ項目を記憶し、前記ステップ(c)は前記制御データに応じて対応する1つ以上のデータ・スロットから受信したデータ項目を前記データ・バッファ内に記憶する、請求項14に記載の方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| GB0004416A GB2359703B (en) | 2000-02-24 | 2000-02-24 | A controller and method for controlling interfacing to a data link |

| GB0004416.4 | 2000-02-24 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001298494A JP2001298494A (ja) | 2001-10-26 |

| JP2001298494A5 JP2001298494A5 (ja) | 2007-12-06 |

| JP4621368B2 true JP4621368B2 (ja) | 2011-01-26 |

Family

ID=9886347

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001048005A Expired - Fee Related JP4621368B2 (ja) | 2000-02-24 | 2001-02-23 | データ・リンクとのインターフェースを制御するコントローラと方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US7016370B2 (ja) |

| JP (1) | JP4621368B2 (ja) |

| GB (1) | GB2359703B (ja) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2002054601A1 (en) | 2000-12-29 | 2002-07-11 | Morphics Technology, Inc. | Channel codec processor configurable for multiple wireless communications standards |

| US7277420B2 (en) * | 2002-02-12 | 2007-10-02 | Broadcom Corporation | Temporal alignment of codec data with wireless local area network RF slots |

| DE10219357B4 (de) * | 2002-04-30 | 2004-03-11 | Advanced Micro Devices, Inc., Sunnyvale | Verbesserter Datentransfer in Audiocodeccontrollern |

| US7124208B2 (en) * | 2003-04-17 | 2006-10-17 | Intel Corporation | Method and apparatus for enumerating devices on a link |

| US20060083259A1 (en) * | 2004-10-18 | 2006-04-20 | Metcalf Thomas D | Packet-based systems and methods for distributing data |

| JP2008517561A (ja) * | 2004-10-18 | 2008-05-22 | アビオム、インク. | データ配信用のパケットベースのシステムおよび方法 |

| US7526526B2 (en) * | 2005-10-06 | 2009-04-28 | Aviom, Inc. | System and method for transferring data |

| US20070104332A1 (en) * | 2005-10-18 | 2007-05-10 | Clemens Robert P | System and method for automatic plug detection |

| WO2010072030A1 (zh) * | 2008-12-25 | 2010-07-01 | 中兴通讯股份有限公司 | 移动终端多媒体广播驱动接口及实现方法 |

| CN105404607B (zh) * | 2015-11-20 | 2018-02-13 | 英业达科技有限公司 | 通用串行输入输出的数据传输方法 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5398234A (en) * | 1992-10-21 | 1995-03-14 | Digital Equipment Corporation | DS-0 loop-back detection on a DS-1 line |

| GB2323000A (en) * | 1994-04-15 | 1998-09-09 | Vlsi Technology Inc | Programmable serial interface |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US2323000A (en) * | 1939-10-10 | 1943-06-29 | Auwarter Max | Guide for molten silicates |

| US5574944A (en) * | 1993-12-15 | 1996-11-12 | Convex Computer Corporation | System for accessing distributed memory by breaking each accepted access request into series of instructions by using sets of parameters defined as logical channel context |

| US5960211A (en) * | 1995-12-15 | 1999-09-28 | Hughes Aircraft | Data formatting method and apparatus for a data processing array |

| US6044225A (en) * | 1996-03-13 | 2000-03-28 | Diamond Multimedia Systems, Inc. | Multiple parallel digital data stream channel controller |

| US5822553A (en) * | 1996-03-13 | 1998-10-13 | Diamond Multimedia Systems, Inc. | Multiple parallel digital data stream channel controller architecture |

| US5889480A (en) * | 1996-10-18 | 1999-03-30 | Samsung Electronics Co., Ltd. | Full duplex serial codec interface with DMA |

| US5974480A (en) * | 1996-10-18 | 1999-10-26 | Samsung Electronics Co., Ltd. | DMA controller which receives size data for each DMA channel |

| US6259957B1 (en) * | 1997-04-04 | 2001-07-10 | Cirrus Logic, Inc. | Circuits and methods for implementing audio Codecs and systems using the same |

| JPH117422A (ja) * | 1997-06-13 | 1999-01-12 | Nippon Telegr & Teleph Corp <Ntt> | メモリ搭載型の高速通信インタフェースボードとデータの送受信方法 |

| US5928342A (en) * | 1997-07-02 | 1999-07-27 | Creative Technology Ltd. | Audio effects processor integrated on a single chip with a multiport memory onto which multiple asynchronous digital sound samples can be concurrently loaded |

| US6226758B1 (en) * | 1997-09-30 | 2001-05-01 | Cirrus Logic, Inc. | Sample rate conversion of non-audio AES data channels |

| US6230219B1 (en) * | 1997-11-10 | 2001-05-08 | International Business Machines Corporation | High performance multichannel DMA controller for a PCI host bridge with a built-in cache |

| US6404780B1 (en) * | 1998-12-23 | 2002-06-11 | Agere Systems Guardian Corp. | Synchronizing data transfer protocol across high voltage interface |

| US6629001B1 (en) * | 1999-09-15 | 2003-09-30 | Intel Corporation | Configurable controller for audio channels |

| US6434633B1 (en) * | 1999-11-02 | 2002-08-13 | Conexant Systems, Inc. | Method and apparatus for facilitating AC-link communications between a controller and a slow peripheral of a codec |

| US6529975B1 (en) * | 1999-11-02 | 2003-03-04 | Conexant Systems, Inc. | Method and apparatus for addressing and controlling exspansion devices through an AC-link and a codec |

-

2000

- 2000-02-24 GB GB0004416A patent/GB2359703B/en not_active Expired - Fee Related

-

2001

- 2001-01-16 US US09/759,372 patent/US7016370B2/en not_active Expired - Lifetime

- 2001-02-23 JP JP2001048005A patent/JP4621368B2/ja not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5398234A (en) * | 1992-10-21 | 1995-03-14 | Digital Equipment Corporation | DS-0 loop-back detection on a DS-1 line |

| GB2323000A (en) * | 1994-04-15 | 1998-09-09 | Vlsi Technology Inc | Programmable serial interface |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001298494A (ja) | 2001-10-26 |

| US7016370B2 (en) | 2006-03-21 |

| GB2359703B (en) | 2004-04-07 |

| GB0004416D0 (en) | 2000-04-12 |

| GB2359703A (en) | 2001-08-29 |

| US20010022787A1 (en) | 2001-09-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6874039B2 (en) | Method and apparatus for distributed direct memory access for systems on chip | |

| USRE36647E (en) | System for transmitting and receiving digital information through parallel printer port of computer by using embedding strobe bit in eight bit data of printer port | |

| US5532556A (en) | Multiplexed digital audio and control/status serial protocol | |

| KR100638067B1 (ko) | 고성능 통신 제어기 | |

| US5471632A (en) | System for transferring data between a processor and a system bus including a device which packs, unpacks, or buffers data blocks being transferred | |

| US7433972B2 (en) | Method and apparatus for operating a CD independently from a host processor | |

| US5392406A (en) | DMA data path aligner and network adaptor utilizing same | |

| RU2390053C2 (ru) | Диспетчер сообщений и способ управления доступом к данным в памяти сообщений коммуникационного компонента | |

| JP4621368B2 (ja) | データ・リンクとのインターフェースを制御するコントローラと方法 | |

| JPH01241935A (ja) | 同期フォーマッタ | |

| JPS62233870A (ja) | 順次通信制御装置 | |

| US6671765B1 (en) | Architecture enabling code overlay using a dedicated endpoint | |

| US5602848A (en) | Multi-mode TDM interface circuit | |

| US6029221A (en) | System and method for interfacing a digital signal processor (DSP) to an audio bus containing frames with synchronization data | |

| CN107507617A (zh) | 一种实现dsd音频硬解的系统及方法 | |

| US7313146B2 (en) | Transparent data format within host device supporting differing transaction types | |

| US6094696A (en) | Virtual serial data transfer mechanism | |

| US7920596B2 (en) | Method for high speed framing and a device having framing capabilities | |

| KR100246768B1 (ko) | 포맷가변형 데이터 전송 장치 및 방법 | |

| JPH10164544A (ja) | データ集中管理型音・動画再生システム | |

| JPH0721102A (ja) | メッセージ送受信装置 | |

| JP2002185420A (ja) | 圧縮メディア・データを通信する方法とプロセッサ回路 | |

| JPH08265393A (ja) | シリアル通信方法およびシリアル通信コントローラ | |

| JPH10222442A (ja) | 非同期式データ送受信装置 | |

| JPH10164516A (ja) | データ集中管理型音・動画再生システム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071022 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20071022 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100114 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100122 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20100422 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20100427 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20100521 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20100526 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100622 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101005 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101101 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131105 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |