JP4619288B2 - データ処理システムにおける処理動作マスキング - Google Patents

データ処理システムにおける処理動作マスキング Download PDFInfo

- Publication number

- JP4619288B2 JP4619288B2 JP2005502327A JP2005502327A JP4619288B2 JP 4619288 B2 JP4619288 B2 JP 4619288B2 JP 2005502327 A JP2005502327 A JP 2005502327A JP 2005502327 A JP2005502327 A JP 2005502327A JP 4619288 B2 JP4619288 B2 JP 4619288B2

- Authority

- JP

- Japan

- Prior art keywords

- data processing

- register

- processor core

- instruction

- data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 230000000873 masking effect Effects 0.000 title description 2

- 239000010813 municipal solid waste Substances 0.000 claims description 43

- 230000008859 change Effects 0.000 claims description 22

- 238000000034 method Methods 0.000 claims description 22

- 238000003672 processing method Methods 0.000 claims description 5

- 230000008569 process Effects 0.000 description 15

- 230000007704 transition Effects 0.000 description 10

- 230000006870 function Effects 0.000 description 7

- 230000007246 mechanism Effects 0.000 description 7

- 230000004044 response Effects 0.000 description 6

- 230000006399 behavior Effects 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 238000009825 accumulation Methods 0.000 description 2

- 238000004458 analytical method Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000001010 compromised effect Effects 0.000 description 1

- 230000002028 premature Effects 0.000 description 1

- 230000001629 suppression Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30003—Arrangements for executing specific machine instructions

- G06F9/3005—Arrangements for executing specific machine instructions to perform operations for flow control

- G06F9/30058—Conditional branch instructions

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F21/00—Security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F21/70—Protecting specific internal or peripheral components, in which the protection of a component leads to protection of the entire computer

- G06F21/71—Protecting specific internal or peripheral components, in which the protection of a component leads to protection of the entire computer to assure secure computing or processing of information

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F21/00—Security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F21/70—Protecting specific internal or peripheral components, in which the protection of a component leads to protection of the entire computer

- G06F21/71—Protecting specific internal or peripheral components, in which the protection of a component leads to protection of the entire computer to assure secure computing or processing of information

- G06F21/75—Protecting specific internal or peripheral components, in which the protection of a component leads to protection of the entire computer to assure secure computing or processing of information by inhibiting the analysis of circuitry or operation

- G06F21/755—Protecting specific internal or peripheral components, in which the protection of a component leads to protection of the entire computer to assure secure computing or processing of information by inhibiting the analysis of circuitry or operation with measures against power attack

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30181—Instruction operation extension or modification

- G06F9/30189—Instruction operation extension or modification according to execution mode, e.g. mode flag

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline, look ahead

- G06F9/3836—Instruction issuing, e.g. dynamic instruction scheduling or out of order instruction execution

- G06F9/3842—Speculative instruction execution

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline, look ahead

- G06F9/3861—Recovery, e.g. branch miss-prediction, exception handling

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline, look ahead

- G06F9/3867—Concurrent instruction execution, e.g. pipeline, look ahead using instruction pipelines

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline, look ahead

- G06F9/3867—Concurrent instruction execution, e.g. pipeline, look ahead using instruction pipelines

- G06F9/3875—Pipelining a single stage, e.g. superpipelining

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09C—CIPHERING OR DECIPHERING APPARATUS FOR CRYPTOGRAPHIC OR OTHER PURPOSES INVOLVING THE NEED FOR SECRECY

- G09C1/00—Apparatus or methods whereby a given sequence of signs, e.g. an intelligible text, is transformed into an unintelligible sequence of signs by transposing the signs or groups of signs or by replacing them by others according to a predetermined system

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2207/00—Indexing scheme relating to methods or arrangements for processing data by operating upon the order or content of the data handled

- G06F2207/72—Indexing scheme relating to groups G06F7/72 - G06F7/729

- G06F2207/7219—Countermeasures against side channel or fault attacks

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2221/00—Indexing scheme relating to security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F2221/21—Indexing scheme relating to G06F21/00 and subgroups addressing additional information or applications relating to security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F2221/2123—Dummy operation

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Software Systems (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Mathematical Physics (AREA)

- Computer Security & Cryptography (AREA)

- Executing Machine-Instructions (AREA)

- Storage Device Security (AREA)

- Retry When Errors Occur (AREA)

- Complex Calculations (AREA)

- Signal Processing For Digital Recording And Reproducing (AREA)

- Advance Control (AREA)

Description

EP-A-1,1,158,384が開示しているプロセッサパイプラインでは、ランダムに選ばれたコードシーケンスがレジスタに書き込み中のこれらのシーケンスに対する結果と共に命令パイプラインに挿入される。これらはプロセッサの状態を変えない。

結果データ値を発生するデータ処理命令を実行するプロセッサコア(4)と、

結果データが書き込まれるプロセッサコアの状態を定義するデータ値を保持するデータ処理レジスタ(12)とを含み、

プロセッサコアにより実行される少なくとも1個のデータ処理命令が条件付きコード(26)を符号化する条件付き書き込みデータ処理命令であり、条件付きコードは、プロセッサコアの状態の変化をもたらすために、条件付き書き込みデータ処理命令がデータを書き込むのを許可するか否かという条件を特定し、

さらに、条件付き書き込みデータ処理命令の中の条件コードが、プロセッサコアの状態の変化をもたらすための書き込みを許さないとき、条件付き書き込みデータ処理命令の実行時にデータ処理レジスタの替わりに結果データ値を書き込むことができるトラッシュレジスタ(51)を含む、データ処理装置である。

データ処理命令のプロセッサコア(4)による実行時に結果データ値を発生するステップを含み、該ステップは実行される少なくとも1個のデータ処理命令が条件付きコード(26)を符号化する条件付き書き込みデータ処理命令であり、条件付きコードは、プロセッサコアの状態の変化をもたらすために、条件付き書き込みデータ処理命令がデータを書き込むのを許可するか否かという条件を特定し、

さらに、条件付き書き込みデータ処理命令の中の条件コードが、プロセッサコアの状態の変化をもたらすための書き込みを許さないとき、プロセッサコアの状態を定義するデータ値を保持するデータ処理レジスタに結果データ値が書き込まれず、替わりにトラッシュレジスタ(51)に結果データ値が書き込まれる、データ処理方法である。

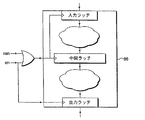

図1はプロセッサコア4、コプロセッサ6およびメモリ8を含むデータ処理システム2を示す。

動作時に、プロセッサコア4はメモリ8から命令とデータとを取込む。命令は命令パイプライン10に送られ、そこで命令は例えば、取込み、デコード、実行、記憶およびライトバックのようなパイプラインステージを、連続的な処理サイクルで次々と実行する。パイプライン式のプロセッサ自体は、処理性能を改善するために、部分的にオーバーラップしながらいくつかのプログラムの命令を効率的に実行する方法としてよく知られている。

Claims (8)

- データ処理装置において、

データ処理命令を実行して結果データ値を発生するプロセッサコア(4)と、

前記結果データ値が書き込まれるデータ処理レジスタ(12)であって、前記プロセッサコアの状態はデータ処理レジスタに保持されるデータ値によって定められる、データ処理レジスタと、

を含み、

前記プロセッサコアにより実行される少なくとも1つのデータ処理命令は条件付き書き込みデータ処理命令であり、条件付き書き込みデータ処理命令は、前記プロセッサコアの状態の変化をもたらすデータの書き込みを許可するか否かを指定する条件を符号化した条件コード(26)を含み、

さらに、前記データ処理装置はトラッシュレジスタ(51)を含み、

前記条件付き書き込みデータ処理命令の実行時に、前記条件付き書き込みデータ処理命令の中の前記条件コードが前記プロセッサコアの状態の変化をもたらす書き込みを許可しないことを指定している場合に、結果データ値はデータ処理レジスタではなくトラッシュレジスタに書き込まれ前記プロッセッサコアの状態を変化させない、データ処理装置。 - 請求項1記載の装置において、結果データが書き込まれる複数のデータレジスタを有するレジスタバンク(12)を含む、データ処理装置。

- 請求項2記載の装置において、前記トラッシュレジスタ(51)は前記レジスタバンクの一部であって、前記トラッシュレジスタがプログラム命令によって特定されないように、前記トラッシュレジスタはレジスタ番号にマップされていない、データ処理装置。

- データ処理装置において、

データ処理命令を実行して結果データ値を発生するプロセッサコア(4)と、

前記結果データ値が書き込まれるデータ処理レジスタ(12)であって、前記プロセッサコアの状態はデータ処理レジスタに保持されるデータ値によって定められる、データ処理レジスタと、

を含み、

前記プロセッサコアにより実行される少なくとも1つのデータ処理命令は条件付き書き込みデータ処理命令であり、条件付き書き込みデータ処理命令は、前記プロセッサコアの状態の変化をもたらすデータの書き込みを許可するか否かを指定する条件を符号化した条件コード(26)を含み、

さらに、前記データ処理装置はトラッシュレジスタ(51)を含み、

前記条件付き書き込みデータ処理命令の実行時に、前記条件付き書き込みデータ処理命令の中の前記条件コードが前記プロセッサコアの状態の変化をもたらす書き込みを許可しないことを指定している場合に、結果データ値はデータ処理レジスタではなくトラッシュレジスタに書き込まれ前記プロッセッサコアの状態を変化させない、

前記トラッシュレジスタ(51)は、トラッシュレジスタ制御信号によって、書き込みができないようにプログラムされ、前記トラッシュレジスタ制御信号はシステム・コンフィギュレーション・レジスタに記憶される、

データ処理装置。 - プロセッサコア(4)によって、データ処理命令の実行時に結果データ値を発生するステップを備え、

前記プロセッサコアにより実行される少なくとも1つのデータ処理命令は条件付き書き込みデータ処理命令であり、条件付き書き込みデータ処理命令は、データ処理レジスタに保持されるデータ値によって定められる前記プロセッサコアの状態の変化をもたらすデータの書き込みを許可するか否かを指定する条件を符号化した条件コード(26)を含み、

前記プロセッサコア(4)による前記条件付き書き込みデータ処理命令の実行時に、前記条件付き書き込みデータ処理命令の中の前記条件コードが前記プロセッサコアの状態の変化をもたらす書き込みを許可しないことを指定している場合に、結果データ値は前記データ処理レジスタではなくトラッシュレジスタに書き込まれ前記プロッセッサコアの状態を変化させない、

データ処理方法。 - 請求項5記載の方法において、前記データ処理レジスタは結果データが書き込まれる複数のデータレジスタを有するレジスタバンクの一部である、データ処理方法。

- 請求項6記載の方法において、前記トラッシュレジスタは前記レジスタバンクの一部であって、前記トラッシュレジスタがプログラム命令によって特定されないように、前記トラッシュレジスタはレジスタ番号にマップされていない、データ処理方法。

- プロセッサコア(4)によって、データ処理命令の実行時に結果データ値を発生するステップを備え、

前記プロセッサコアにより実行される少なくとも1つのデータ処理命令は条件付き書き込みデータ処理命令であり、条件付き書き込みデータ処理命令は、データ処理レジスタに保持されるデータ値によって定められる前記プロセッサコアの状態の変化をもたらすデータの書き込みを許可するか否かを指定する条件を符号化した条件コード(26)を含み、

前記プロセッサコア(4)による前記条件付き書き込みデータ処理命令の実行時に、前記条件付き書き込みデータ処理命令の中の前記条件コードが前記プロセッサコアの状態の変化をもたらす書き込みを許可しないことを指定している場合に、結果データ値は前記データ処理レジスタではなくトラッシュレジスタに書き込まれ前記プロッセッサコアの状態を変化させず、

前記プロセッサコア(4)が、前記トラッシュレジスタ(51)をトラッシュレジスタ制御信号によって書き込みができないようにプログラムすることができ、前記トラッシュレジスタ制御信号はシステム・コンフィギュレーション・レジスタに記憶される、

データ処理方法。

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| GBGB0229068.2A GB0229068D0 (en) | 2002-12-12 | 2002-12-12 | Instruction timing control within a data processing system |

| GBGB0302646.5A GB0302646D0 (en) | 2002-12-12 | 2003-02-05 | Processing activity masking in a data processing system |

| GBGB0302650.7A GB0302650D0 (en) | 2002-12-12 | 2003-02-05 | Processing activity masking in a data processing system |

| GB0307823A GB2396229B (en) | 2002-12-12 | 2003-04-04 | Processing activity masking in a data processing system |

| PCT/GB2003/004261 WO2004053662A2 (en) | 2002-12-12 | 2003-10-06 | Processing activity masking in a data processing system |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010185224A Division JP2010282651A (ja) | 2002-12-12 | 2010-08-20 | データ処理システムにおける処理動作マスキング |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2006522375A JP2006522375A (ja) | 2006-09-28 |

| JP2006522375A5 JP2006522375A5 (ja) | 2006-11-09 |

| JP4619288B2 true JP4619288B2 (ja) | 2011-01-26 |

Family

ID=32512449

Family Applications (4)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005502327A Expired - Lifetime JP4619288B2 (ja) | 2002-12-12 | 2003-10-06 | データ処理システムにおける処理動作マスキング |

| JP2005502328A Expired - Lifetime JP3848965B2 (ja) | 2002-12-12 | 2003-10-06 | データ処理装置内の命令タイミング制御 |

| JP2005502326A Expired - Fee Related JP4511461B2 (ja) | 2002-12-12 | 2003-10-06 | データ処理システムでの処理動作マスキング |

| JP2005502329A Pending JP2006510998A (ja) | 2002-12-12 | 2003-10-06 | データ処理システム内の処理アクティビティのマスキング |

Family Applications After (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005502328A Expired - Lifetime JP3848965B2 (ja) | 2002-12-12 | 2003-10-06 | データ処理装置内の命令タイミング制御 |

| JP2005502326A Expired - Fee Related JP4511461B2 (ja) | 2002-12-12 | 2003-10-06 | データ処理システムでの処理動作マスキング |

| JP2005502329A Pending JP2006510998A (ja) | 2002-12-12 | 2003-10-06 | データ処理システム内の処理アクティビティのマスキング |

Country Status (4)

| Country | Link |

|---|---|

| US (4) | US7134003B2 (ja) |

| JP (4) | JP4619288B2 (ja) |

| GB (3) | GB2406684B (ja) |

| WO (4) | WO2004053685A1 (ja) |

Families Citing this family (52)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4619288B2 (ja) * | 2002-12-12 | 2011-01-26 | エイアールエム リミテッド | データ処理システムにおける処理動作マスキング |

| US7949883B2 (en) * | 2004-06-08 | 2011-05-24 | Hrl Laboratories, Llc | Cryptographic CPU architecture with random instruction masking to thwart differential power analysis |

| US9246728B2 (en) | 2004-07-29 | 2016-01-26 | Qualcomm Incorporated | System and method for frequency diversity |

| KR100925911B1 (ko) * | 2004-07-29 | 2009-11-09 | 콸콤 인코포레이티드 | 다이버시티 인터리빙을 위한 시스템 및 방법 |

| US20070081484A1 (en) * | 2004-07-29 | 2007-04-12 | Wang Michael M | Methods and apparatus for transmitting a frame structure in a wireless communication system |

| US8391410B2 (en) * | 2004-07-29 | 2013-03-05 | Qualcomm Incorporated | Methods and apparatus for configuring a pilot symbol in a wireless communication system |

| US20080317142A1 (en) * | 2005-07-29 | 2008-12-25 | Qualcomm Incorporated | System and method for frequency diversity |

| FR2875657B1 (fr) * | 2004-09-22 | 2006-12-15 | Trusted Logic Sa | Procede de securisation de traitements cryptographiques par le biais de leurres. |

| JP4702004B2 (ja) * | 2004-12-21 | 2011-06-15 | 株式会社デンソー | マイクロコンピュータ |

| US7725694B2 (en) * | 2004-12-21 | 2010-05-25 | Denso Corporation | Processor, microcomputer and method for controlling program of microcomputer |

| JP4889235B2 (ja) * | 2005-04-27 | 2012-03-07 | 株式会社デンソー | プログラム制御プロセッサ |

| US8312297B2 (en) * | 2005-04-21 | 2012-11-13 | Panasonic Corporation | Program illegiblizing device and method |

| US7769983B2 (en) * | 2005-05-18 | 2010-08-03 | Qualcomm Incorporated | Caching instructions for a multiple-state processor |

| US9391751B2 (en) * | 2005-07-29 | 2016-07-12 | Qualcomm Incorporated | System and method for frequency diversity |

| US9042212B2 (en) | 2005-07-29 | 2015-05-26 | Qualcomm Incorporated | Method and apparatus for communicating network identifiers in a communication system |

| EP1920376A2 (en) * | 2005-08-24 | 2008-05-14 | Nxp B.V. | Processor hardware and software |

| US8074059B2 (en) | 2005-09-02 | 2011-12-06 | Binl ATE, LLC | System and method for performing deterministic processing |

| JP4783104B2 (ja) * | 2005-09-29 | 2011-09-28 | 株式会社東芝 | 暗号化/復号装置 |

| EP1783648A1 (fr) * | 2005-10-10 | 2007-05-09 | Nagracard S.A. | Microprocesseur sécurisé avec vérification des instructions |

| JP4882625B2 (ja) * | 2005-12-26 | 2012-02-22 | 株式会社デンソー | マイクロコンピュータ |

| US20070288740A1 (en) * | 2006-06-09 | 2007-12-13 | Dale Jason N | System and method for secure boot across a plurality of processors |

| US7774616B2 (en) * | 2006-06-09 | 2010-08-10 | International Business Machines Corporation | Masking a boot sequence by providing a dummy processor |

| US20070288739A1 (en) * | 2006-06-09 | 2007-12-13 | Dale Jason N | System and method for masking a boot sequence by running different code on each processor |

| US7594104B2 (en) * | 2006-06-09 | 2009-09-22 | International Business Machines Corporation | System and method for masking a hardware boot sequence |

| US20070288738A1 (en) * | 2006-06-09 | 2007-12-13 | Dale Jason N | System and method for selecting a random processor to boot on a multiprocessor system |

| US20070288761A1 (en) * | 2006-06-09 | 2007-12-13 | Dale Jason N | System and method for booting a multiprocessor device based on selection of encryption keys to be provided to processors |

| JP4680876B2 (ja) * | 2006-12-11 | 2011-05-11 | ルネサスエレクトロニクス株式会社 | 情報処理装置及び命令フェッチ制御方法 |

| US7711927B2 (en) * | 2007-03-14 | 2010-05-04 | Qualcomm Incorporated | System, method and software to preload instructions from an instruction set other than one currently executing |

| JP5146156B2 (ja) * | 2008-06-30 | 2013-02-20 | 富士通株式会社 | 演算処理装置 |

| WO2010116474A1 (ja) | 2009-03-30 | 2010-10-14 | 富士通株式会社 | 光伝送システム及び光伝送方法 |

| EP2367102B1 (en) * | 2010-02-11 | 2013-04-10 | Nxp B.V. | Computer processor and method with increased security properties |

| GB2480296A (en) * | 2010-05-12 | 2011-11-16 | Nds Ltd | Processor with differential power analysis attack protection |

| US8624624B1 (en) | 2011-08-26 | 2014-01-07 | Lockheed Martin Corporation | Power isolation during sensitive operations |

| US8525545B1 (en) | 2011-08-26 | 2013-09-03 | Lockheed Martin Corporation | Power isolation during sensitive operations |

| US8694862B2 (en) | 2012-04-20 | 2014-04-08 | Arm Limited | Data processing apparatus using implicit data storage data storage and method of implicit data storage |

| JP5926655B2 (ja) * | 2012-08-30 | 2016-05-25 | ルネサスエレクトロニクス株式会社 | 中央処理装置および演算装置 |

| US20150161401A1 (en) * | 2013-12-10 | 2015-06-11 | Samsung Electronics Co., Ltd. | Processor having a variable pipeline, and system-on-chip |

| US9569616B2 (en) | 2013-12-12 | 2017-02-14 | Cryptography Research, Inc. | Gate-level masking |

| US9558032B2 (en) | 2014-03-14 | 2017-01-31 | International Business Machines Corporation | Conditional instruction end operation |

| US9454370B2 (en) | 2014-03-14 | 2016-09-27 | International Business Machines Corporation | Conditional transaction end instruction |

| US10120681B2 (en) | 2014-03-14 | 2018-11-06 | International Business Machines Corporation | Compare and delay instructions |

| US9305167B2 (en) * | 2014-05-21 | 2016-04-05 | Bitdefender IPR Management Ltd. | Hardware-enabled prevention of code reuse attacks |

| US10049211B1 (en) * | 2014-07-16 | 2018-08-14 | Bitdefender IPR Management Ltd. | Hardware-accelerated prevention of code reuse attacks |

| KR102335203B1 (ko) * | 2015-08-10 | 2021-12-07 | 삼성전자주식회사 | 부채널 공격에 대응하는 전자 장치 |

| US10210350B2 (en) * | 2015-08-10 | 2019-02-19 | Samsung Electronics Co., Ltd. | Electronic device against side channel attacks |

| US10459477B2 (en) | 2017-04-19 | 2019-10-29 | Seagate Technology Llc | Computing system with power variation attack countermeasures |

| US10200192B2 (en) | 2017-04-19 | 2019-02-05 | Seagate Technology Llc | Secure execution environment clock frequency hopping |

| US10270586B2 (en) | 2017-04-25 | 2019-04-23 | Seagate Technology Llc | Random time generated interrupts in a cryptographic hardware pipeline circuit |

| US10511433B2 (en) | 2017-05-03 | 2019-12-17 | Seagate Technology Llc | Timing attack protection in a cryptographic processing system |

| US10771236B2 (en) | 2017-05-03 | 2020-09-08 | Seagate Technology Llc | Defending against a side-channel information attack in a data storage device |

| FR3071121B1 (fr) * | 2017-09-14 | 2020-09-18 | Commissariat Energie Atomique | Procede d'execution d'un code binaire d'une fonction securisee par un microprocesseur |

| US11308239B2 (en) | 2018-03-30 | 2022-04-19 | Seagate Technology Llc | Jitter attack protection circuit |

Family Cites Families (35)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4064558A (en) * | 1976-10-22 | 1977-12-20 | General Electric Company | Method and apparatus for randomizing memory site usage |

| US4168396A (en) * | 1977-10-31 | 1979-09-18 | Best Robert M | Microprocessor for executing enciphered programs |

| US4593353A (en) * | 1981-10-26 | 1986-06-03 | Telecommunications Associates, Inc. | Software protection method and apparatus |

| JPS59739A (ja) * | 1982-06-28 | 1984-01-05 | Fujitsu Ltd | マイクロプログラム処理装置における時間保障方式 |

| JPS595354A (ja) | 1982-06-30 | 1984-01-12 | Fujitsu Ltd | デ−タ処理装置 |

| JP2562838B2 (ja) * | 1989-02-10 | 1996-12-11 | 富士通株式会社 | プロセッサ及びストアバッファ制御方法 |

| US5574912A (en) * | 1990-05-04 | 1996-11-12 | Digital Equipment Corporation | Lattice scheduler method for reducing the impact of covert-channel countermeasures |

| GB2282245B (en) * | 1993-09-23 | 1998-04-15 | Advanced Risc Mach Ltd | Execution of data processing instructions |

| US5404402A (en) * | 1993-12-21 | 1995-04-04 | Gi Corporation | Clock frequency modulation for secure microprocessors |

| IL110181A (en) * | 1994-06-30 | 1998-02-08 | Softchip Israel Ltd | Install microprocessor and peripherals |

| US5675645A (en) * | 1995-04-18 | 1997-10-07 | Ricoh Company, Ltd. | Method and apparatus for securing executable programs against copying |

| FR2745924B1 (fr) * | 1996-03-07 | 1998-12-11 | Bull Cp8 | Circuit integre perfectionne et procede d'utilisation d'un tel circuit integre |

| JP3683031B2 (ja) * | 1996-04-17 | 2005-08-17 | 株式会社リコー | プログラム保護装置 |

| US5802360A (en) * | 1996-05-01 | 1998-09-01 | Lucent Technologies Inc. | Digital microprocessor device having dnamically selectable instruction execution intervals |

| US6192475B1 (en) * | 1997-03-31 | 2001-02-20 | David R. Wallace | System and method for cloaking software |

| FR2765361B1 (fr) * | 1997-06-26 | 2001-09-21 | Bull Cp8 | Microprocesseur ou microcalculateur imprevisible |

| EP1019794B1 (en) * | 1997-10-02 | 2008-08-20 | Koninklijke Philips Electronics N.V. | Data processing device for processing virtual machine instructions |

| US6216223B1 (en) | 1998-01-12 | 2001-04-10 | Billions Of Operations Per Second, Inc. | Methods and apparatus to dynamically reconfigure the instruction pipeline of an indirect very long instruction word scalable processor |

| US6510518B1 (en) * | 1998-06-03 | 2003-01-21 | Cryptography Research, Inc. | Balanced cryptographic computational method and apparatus for leak minimizational in smartcards and other cryptosystems |

| DE69938045T2 (de) * | 1998-06-03 | 2009-01-15 | Cryptography Research Inc., San Francisco | Verwendung von unvorhersagbarer Information zur Leckminimierung von Chipkarten und anderen Kryptosystemen |

| CA2243761C (en) * | 1998-07-21 | 2009-10-06 | Certicom Corp. | Timing attack resistant cryptographic system |

| US6332215B1 (en) | 1998-12-08 | 2001-12-18 | Nazomi Communications, Inc. | Java virtual machine hardware for RISC and CISC processors |

| FR2787900B1 (fr) * | 1998-12-28 | 2001-02-09 | Bull Cp8 | Circuit integre intelligent |

| US6804782B1 (en) * | 1999-06-11 | 2004-10-12 | General Instrument Corporation | Countermeasure to power attack and timing attack on cryptographic operations |

| US6609201B1 (en) * | 1999-08-18 | 2003-08-19 | Sun Microsystems, Inc. | Secure program execution using instruction buffer interdependencies |

| FR2802733B1 (fr) * | 1999-12-21 | 2002-02-08 | St Microelectronics Sa | Bascule de type d maitre-esclave securisee |

| JP4168305B2 (ja) * | 2000-01-12 | 2008-10-22 | 株式会社ルネサステクノロジ | Icカードとマイクロコンピュータ |

| JP2001266103A (ja) * | 2000-01-12 | 2001-09-28 | Hitachi Ltd | Icカードとマイクロコンピュータ |

| CA2298990A1 (en) * | 2000-02-18 | 2001-08-18 | Cloakware Corporation | Method and system for resistance to power analysis |

| AU2001245511A1 (en) | 2000-03-10 | 2001-09-24 | Arc International Plc | Method and apparatus for enhancing the performance of a pipelined data processor |

| DE50010164D1 (de) * | 2000-05-22 | 2005-06-02 | Infineon Technologies Ag | Sicherheits-Datenverarbeitungseinheit sowie dazugehöriges Verfahren |

| US6625737B1 (en) * | 2000-09-20 | 2003-09-23 | Mips Technologies Inc. | System for prediction and control of power consumption in digital system |

| GB2367653B (en) * | 2000-10-05 | 2004-10-20 | Advanced Risc Mach Ltd | Restarting translated instructions |

| DE10101956A1 (de) * | 2001-01-17 | 2002-07-25 | Infineon Technologies Ag | Verfahren zur Erhöhung der Sicherheit einer CPU |

| JP4619288B2 (ja) * | 2002-12-12 | 2011-01-26 | エイアールエム リミテッド | データ処理システムにおける処理動作マスキング |

-

2003

- 2003-10-06 JP JP2005502327A patent/JP4619288B2/ja not_active Expired - Lifetime

- 2003-10-06 WO PCT/GB2003/004304 patent/WO2004053685A1/en active Application Filing

- 2003-10-06 GB GB0501017A patent/GB2406684B/en not_active Expired - Lifetime

- 2003-10-06 US US10/512,093 patent/US7134003B2/en not_active Expired - Lifetime

- 2003-10-06 WO PCT/GB2003/004261 patent/WO2004053662A2/en active Application Filing

- 2003-10-06 US US10/527,812 patent/US20060117167A1/en not_active Abandoned

- 2003-10-06 JP JP2005502328A patent/JP3848965B2/ja not_active Expired - Lifetime

- 2003-10-06 US US10/527,575 patent/US7313677B2/en not_active Expired - Lifetime

- 2003-10-06 JP JP2005502326A patent/JP4511461B2/ja not_active Expired - Fee Related

- 2003-10-06 JP JP2005502329A patent/JP2006510998A/ja active Pending

- 2003-10-06 WO PCT/GB2003/004256 patent/WO2004053683A2/en active Application Filing

- 2003-10-06 US US10/527,960 patent/US7426629B2/en active Active

- 2003-10-06 GB GB0423310A patent/GB2403572B/en not_active Expired - Lifetime

- 2003-10-06 GB GB0502061A patent/GB2406943B/en not_active Expired - Fee Related

- 2003-10-06 WO PCT/GB2003/004313 patent/WO2004053684A2/en active Application Filing

Also Published As

| Publication number | Publication date |

|---|---|

| JP4511461B2 (ja) | 2010-07-28 |

| JP2006522375A (ja) | 2006-09-28 |

| US20050289331A1 (en) | 2005-12-29 |

| GB0501017D0 (en) | 2005-02-23 |

| JP2006510127A (ja) | 2006-03-23 |

| US7426629B2 (en) | 2008-09-16 |

| US20060117167A1 (en) | 2006-06-01 |

| JP2006510998A (ja) | 2006-03-30 |

| GB0423310D0 (en) | 2004-11-24 |

| WO2004053683A2 (en) | 2004-06-24 |

| US7313677B2 (en) | 2007-12-25 |

| US20060036833A1 (en) | 2006-02-16 |

| WO2004053684A3 (en) | 2004-08-12 |

| GB2406943B (en) | 2005-10-05 |

| GB0502061D0 (en) | 2005-03-09 |

| WO2004053662A3 (en) | 2004-08-12 |

| WO2004053684A2 (en) | 2004-06-24 |

| GB2403572A (en) | 2005-01-05 |

| GB2403572B (en) | 2005-11-09 |

| GB2406943A (en) | 2005-04-13 |

| WO2004053683A3 (en) | 2004-08-05 |

| US20060155962A1 (en) | 2006-07-13 |

| GB2406684B (en) | 2005-08-24 |

| WO2004053685A1 (en) | 2004-06-24 |

| JP2006510126A (ja) | 2006-03-23 |

| WO2004053662A2 (en) | 2004-06-24 |

| JP3848965B2 (ja) | 2006-11-22 |

| GB2406684A (en) | 2005-04-06 |

| US7134003B2 (en) | 2006-11-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4619288B2 (ja) | データ処理システムにおける処理動作マスキング | |

| US7178011B2 (en) | Predication instruction within a data processing system | |

| May et al. | Non-deterministic processors | |

| KR20200051694A (ko) | 호출 경로 의존 인증 | |

| US20130097408A1 (en) | Conditional compare instruction | |

| US10782972B2 (en) | Vector predication instruction | |

| JP5759537B2 (ja) | 命令としてデータ値を評価するシステムおよび方法 | |

| WO2019175530A1 (en) | Branch target variant of branch-with-link instruction | |

| KR20200090103A (ko) | 분기 예측기 | |

| EP3329361B1 (en) | Vector operand bitsize control | |

| JP2010282651A (ja) | データ処理システムにおける処理動作マスキング | |

| JP7377208B2 (ja) | データ処理 | |

| EP3433724B1 (en) | Processing vector instructions | |

| GB2515020A (en) | Operand generation in at least one processing pipeline | |

| GB2396229A (en) | Processor to register writing masking by writing to normal register or to a trash register | |

| EP4080386A1 (en) | Method to protect program in integrated circuit |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A529 | Written submission of copy of amendment under article 34 pct |

Free format text: JAPANESE INTERMEDIATE CODE: A529 Effective date: 20050222 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20051116 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060724 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090424 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090723 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091020 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100120 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20100420 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100820 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20100916 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101008 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101026 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131105 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4619288 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |