JP4608921B2 - 表示装置の製造方法および表示装置 - Google Patents

表示装置の製造方法および表示装置 Download PDFInfo

- Publication number

- JP4608921B2 JP4608921B2 JP2004082477A JP2004082477A JP4608921B2 JP 4608921 B2 JP4608921 B2 JP 4608921B2 JP 2004082477 A JP2004082477 A JP 2004082477A JP 2004082477 A JP2004082477 A JP 2004082477A JP 4608921 B2 JP4608921 B2 JP 4608921B2

- Authority

- JP

- Japan

- Prior art keywords

- insulating film

- conductive film

- film

- substrate

- organic layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 40

- 239000000758 substrate Substances 0.000 claims description 77

- 239000012044 organic layer Substances 0.000 claims description 57

- 239000010410 layer Substances 0.000 claims description 49

- 238000000034 method Methods 0.000 claims description 42

- 239000000463 material Substances 0.000 claims description 13

- 238000002955 isolation Methods 0.000 claims description 11

- 238000009413 insulation Methods 0.000 claims description 4

- 239000010408 film Substances 0.000 description 274

- 230000002093 peripheral effect Effects 0.000 description 24

- 239000004020 conductor Substances 0.000 description 18

- 229920002577 polybenzoxazole Polymers 0.000 description 18

- 238000002347 injection Methods 0.000 description 12

- 239000007924 injection Substances 0.000 description 12

- 238000000151 deposition Methods 0.000 description 9

- 239000011347 resin Substances 0.000 description 9

- 229920005989 resin Polymers 0.000 description 9

- 229910001316 Ag alloy Inorganic materials 0.000 description 7

- 238000005530 etching Methods 0.000 description 7

- 238000001704 evaporation Methods 0.000 description 7

- 230000001681 protective effect Effects 0.000 description 7

- UBSJOWMHLJZVDJ-UHFFFAOYSA-N aluminum neodymium Chemical compound [Al].[Nd] UBSJOWMHLJZVDJ-UHFFFAOYSA-N 0.000 description 6

- 230000006866 deterioration Effects 0.000 description 6

- 230000008020 evaporation Effects 0.000 description 6

- 239000011810 insulating material Substances 0.000 description 6

- 238000004528 spin coating Methods 0.000 description 6

- 238000004544 sputter deposition Methods 0.000 description 6

- 230000000052 comparative effect Effects 0.000 description 5

- 230000007547 defect Effects 0.000 description 5

- 239000011521 glass Substances 0.000 description 5

- PQXKHYXIUOZZFA-UHFFFAOYSA-M lithium fluoride Chemical compound [Li+].[F-] PQXKHYXIUOZZFA-UHFFFAOYSA-M 0.000 description 5

- 238000001459 lithography Methods 0.000 description 5

- 239000004642 Polyimide Substances 0.000 description 4

- 238000005229 chemical vapour deposition Methods 0.000 description 4

- 230000008021 deposition Effects 0.000 description 4

- 239000011261 inert gas Substances 0.000 description 4

- 229920001721 polyimide Polymers 0.000 description 4

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 4

- 229910045601 alloy Inorganic materials 0.000 description 3

- 239000000956 alloy Substances 0.000 description 3

- 238000004140 cleaning Methods 0.000 description 3

- 238000010438 heat treatment Methods 0.000 description 3

- 230000004048 modification Effects 0.000 description 3

- 238000012986 modification Methods 0.000 description 3

- 238000001179 sorption measurement Methods 0.000 description 3

- 229920001187 thermosetting polymer Polymers 0.000 description 3

- 238000001771 vacuum deposition Methods 0.000 description 3

- 238000007740 vapor deposition Methods 0.000 description 3

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 238000009826 distribution Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 239000000284 extract Substances 0.000 description 2

- 230000005525 hole transport Effects 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 2

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 238000007872 degassing Methods 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 230000036962 time dependent Effects 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/131—Interconnections, e.g. wiring lines or terminals

-

- D—TEXTILES; PAPER

- D06—TREATMENT OF TEXTILES OR THE LIKE; LAUNDERING; FLEXIBLE MATERIALS NOT OTHERWISE PROVIDED FOR

- D06J—PLEATING, KILTING OR GOFFERING TEXTILE FABRICS OR WEARING APPAREL

- D06J1/00—Pleating, kilting or goffering textile fabrics or wearing apparel

- D06J1/12—Forms of pleats or the like

-

- D—TEXTILES; PAPER

- D06—TREATMENT OF TEXTILES OR THE LIKE; LAUNDERING; FLEXIBLE MATERIALS NOT OTHERWISE PROVIDED FOR

- D06C—FINISHING, DRESSING, TENTERING OR STRETCHING TEXTILE FABRICS

- D06C23/00—Making patterns or designs on fabrics

- D06C23/04—Making patterns or designs on fabrics by shrinking, embossing, moiréing, or crêping

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K50/00—Organic light-emitting devices

- H10K50/80—Constructional details

- H10K50/84—Passivation; Containers; Encapsulations

- H10K50/841—Self-supporting sealing arrangements

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K50/00—Organic light-emitting devices

- H10K50/80—Constructional details

- H10K50/84—Passivation; Containers; Encapsulations

- H10K50/844—Encapsulations

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/122—Pixel-defining structures or layers, e.g. banks

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/124—Insulating layers formed between TFT elements and OLED elements

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/80—Constructional details

- H10K59/87—Passivation; Containers; Encapsulations

- H10K59/873—Encapsulations

Landscapes

- Engineering & Computer Science (AREA)

- Textile Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Electroluminescent Light Sources (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

Description

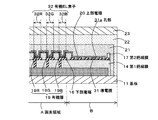

ここでは、上面発光型の有機ELディスプレイを例にとり、各部材の詳細な構成を製造工程順に説明する。なお、背景技術で説明したものと同様の構成には同一の番号を付して説明する。

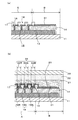

第1実施形態では、上面発光型の有機ELディスプレイを例にとり説明したが、本実施形態では、有機層で生じた光を下部電極側から取り出す下面発光型の有機ELディスプレイについて図5(a)および図5(b)を用いて説明する。なお、第1実施形態と同様の構成には、同一の番号を付して説明することとする。

上述したように、下部電極16よりも高い導電性を有する材料で導電膜31を形成する場合には、第2絶縁膜17上に導電膜31を形成してもよい。この場合の表示装置の製造方法について、第2実施形態と同様に、下面発光型の表示装置を例にとり、図6を用いて説明する。ここで、TFTアレイ13が形成された基板11上に、第1絶縁膜14を塗布形成し、第1絶縁膜14にTFTと接続するためのコンタクトホール15を形成した後、基板11にベーク処理を行うまでの工程は、図5(a)を用いて説明した第2実施形態と同様の方法で行うこととする。また、ここまでの構成が、請求項11および請求項14の基板に相当する。

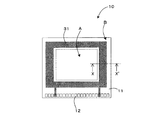

上記第1実施形態と同様の方法により、図3に示す上面発光型の表示装置を製造した。また、これに対する比較例1として、第1絶縁膜14の周辺領域Bに、孔部31aが設けられていない状態の導電膜31を、画素領域Aを囲う形状で約3mmの幅で形成した表示装置を製造した。

上記第2実施形態と同様の方法により、図5(b)に示す下面発光型の表示装置を製造した。また、これに対する比較例2として、第1絶縁膜14の周辺領域Bに、孔部31aが設けられていない状態の導電膜31を、画素領域Aを囲う形状で約3mmの幅で形成した表示装置を製造した。

Claims (14)

- 基板上に下部電極と上部電極とで有機層を挟持してなる複数の画素が配列形成された画素領域を有する表示装置の製造方法であって、

前記基板上に絶縁膜を形成する第1工程と、

前記画素領域内の前記絶縁膜上に、前記各画素に対応する複数の前記下部電極を形成するとともに、前記画素領域の外側の前記絶縁膜上に補助配線としての導電膜を形成し、当該導電膜に前記絶縁膜に達する孔部を形成する第2工程と、

前記下部電極および前記導電膜が設けられた前記基板にベーク処理を行う第3工程と、 前記下部電極上に前記有機層を設け、前記有機層および前記導電膜を覆う状態で上部

電極を形成する第4工程とを有する

表示装置の製造方法。 - 前記下部電極と前記導電膜が同一材料で形成されている

請求項1記載の表示装置の製造方法。 - 前記第2工程では、

前記導電膜の全域に渡って略均等に配置されるように、複数の前記孔部を形成する

請求項1記載の表示装置の製造方法。 - 前記第2工程と前記第3工程との間に、

前記下部電極および前記導電膜を覆う状態で、前記絶縁膜上に素子分離絶縁膜を形成し、

当該素子分離絶縁膜に前記各下部電極の表面を露出する画素開口を形成するとともに、前記導電膜上の素子分離絶縁膜を除去して前記導電膜の表面を露出する工程を行い、

前記第4工程では、

前記有機層、前記素子分離絶縁膜および前記導電膜を覆う状態で、上部電極を形成することで、当該上部電極と前記導電膜とを接続する

請求項1記載の表示装置の製造方法。 - 前記導電膜の表面を露出する工程では、

当該導電膜の端部を前記素子分離絶縁膜で覆う状態で、前記導電膜上の素子分離絶縁膜を除去する

請求項4記載の表示装置の製造方法。 - 基板上に、下部電極と上部電極とで有機層を挟持してなる複数の画素が配列形成された画素領域を有する表示装置であって、

前記基板上に設けられた絶縁膜と、

前記画素領域内の前記絶縁膜上に設けられた前記各画素に対応する複数の前記下部電極と、

前記画素領域の外側の前記絶縁膜上に設けられた導電膜と、

前記下部電極上に設けられた前記有機層と、

前記有機層および前記導電膜を覆う状態で設けられた上部電極とを備え、

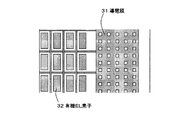

前記導電膜は前記上部電極と接続され補助配線として機能すると共に、当該膜内に前記絶縁膜に達する孔部を有する

表示装置。 - 前記下部電極と前記導電膜が同一材料である

請求項6記載の表示装置。 - 前記孔部が複数設けられており、前記導電膜の全域に渡って略均等に配置されている

請求項6記載の表示装置。 - 前記絶縁膜上に設けられ、前記導電膜を露出した状態で、前記各下部電極を露出する前記画素開口が設けられた素子分離絶縁膜と、

前記有機層、前記素子分離絶縁膜および前記導電膜を覆う状態で設けられた上部電極とを備え、

当該上部電極と前記導電膜とが接続された

請求項6記載の表示装置。 - 前記導電膜の端部が前記素子分離絶縁膜で覆われている

請求項9記載の表示装置。 - 基板上に、下部電極と上部電極とで有機層を挟持してなる複数の画素が配列形成された画素領域を有する表示装置の製造方法であって、

前記基板上に、前記各画素に対応する複数の前記下部電極を形成する第1工程と、

前記下部電極を覆う状態で、前記基板上に絶縁膜を形成し、当該絶縁膜に前記各下部電極の表面を露出する画素開口を形成する第2工程と、

前記画素領域の外側の前記絶縁膜上に補助配線としての導電膜を形成するとともに、当該導電膜に前記絶縁膜に達する孔部を形成する第3工程と、

前記導電膜が設けられた前記基板にベーク処理を行う第4工程と、

前記下部電極上に前記有機層を設け、前記有機層、前記絶縁膜および前記導電膜を覆う状態で上部電極を形成する第5工程とを有する

表示装置の製造方法。 - 前記第3工程では、

前記導電膜の全域に渡って略均等に配置されるように、複数の前記孔部を形成する

請求項11記載の表示装置の製造方法。 - 基板上に、下部電極と上部電極とで有機層を挟持してなる複数の画素が配列形成された画素領域を有する表示装置であって、

前記画素領域内の前記基板上に設けられた各画素に対応する複数の前記下部電極と、

前記基板上に設けられるとともに、前記各下部電極を露出する画素開口が設けられた絶縁膜と、

前記画素領域の外側の前記絶縁膜上に設けられた導電膜と、

前記下部電極上に設けられた前記有機層と、

前記有機層、前記絶縁膜および前記導電膜を覆う状態で設けられた上部電極とを備え、前記導電膜は前記上部電極と接続され補助配線として機能すると共に、当該膜内に前記絶縁膜に達する複数の孔部を有する

表示装置。 - 前記孔部が複数設けられており、前記導電膜の全域に渡って略均等に配置されている

請求項13記載の表示装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004082477A JP4608921B2 (ja) | 2004-03-22 | 2004-03-22 | 表示装置の製造方法および表示装置 |

| US11/084,957 US8120246B2 (en) | 2004-03-22 | 2005-03-21 | Display device with improved moisture prevention and production method for the same |

| TW094108663A TWI275317B (en) | 2004-03-22 | 2005-03-21 | Display device and production method for the same |

| CNB200510069800XA CN100546421C (zh) | 2004-03-22 | 2005-03-22 | 显示装置及其制造方法 |

| KR1020050023527A KR101161443B1 (ko) | 2004-03-22 | 2005-03-22 | 표시 장치 및 그의 제조 방법 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004082477A JP4608921B2 (ja) | 2004-03-22 | 2004-03-22 | 表示装置の製造方法および表示装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005266667A JP2005266667A (ja) | 2005-09-29 |

| JP2005266667A5 JP2005266667A5 (ja) | 2007-02-01 |

| JP4608921B2 true JP4608921B2 (ja) | 2011-01-12 |

Family

ID=34985553

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004082477A Expired - Lifetime JP4608921B2 (ja) | 2004-03-22 | 2004-03-22 | 表示装置の製造方法および表示装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8120246B2 (ja) |

| JP (1) | JP4608921B2 (ja) |

| KR (1) | KR101161443B1 (ja) |

| CN (1) | CN100546421C (ja) |

| TW (1) | TWI275317B (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10727433B2 (en) | 2018-04-30 | 2020-07-28 | Samsung Display Co., Ltd. | Display device |

Families Citing this family (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4679187B2 (ja) * | 2004-03-26 | 2011-04-27 | 株式会社半導体エネルギー研究所 | 発光装置の作製方法 |

| US7423373B2 (en) | 2004-03-26 | 2008-09-09 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device and manufacturing method thereof |

| KR100573149B1 (ko) * | 2004-05-29 | 2006-04-24 | 삼성에스디아이 주식회사 | 전계 발광 디스플레이 장치 및 이의 제조 방법 |

| JP4655942B2 (ja) * | 2006-01-16 | 2011-03-23 | セイコーエプソン株式会社 | 発光装置、発光装置の製造方法および電子機器 |

| JP4809087B2 (ja) | 2006-03-14 | 2011-11-02 | セイコーエプソン株式会社 | エレクトロルミネッセンス装置、電子機器、およびエレクトロルミネッセンス装置の製造方法 |

| JP2009187898A (ja) * | 2008-02-08 | 2009-08-20 | Seiko Epson Corp | 有機el装置及びその製造方法 |

| JP5256863B2 (ja) * | 2008-06-06 | 2013-08-07 | ソニー株式会社 | 有機発光素子およびその製造方法ならびに表示装置 |

| KR101572084B1 (ko) * | 2008-07-16 | 2015-11-26 | 삼성디스플레이 주식회사 | 유기 발광 표시 장치 및 그 제조 방법 |

| KR101015851B1 (ko) * | 2009-02-09 | 2011-02-23 | 삼성모바일디스플레이주식회사 | 유기 발광 표시 장치 |

| US8163358B2 (en) * | 2009-02-18 | 2012-04-24 | Synergeyes, Inc. | Surface modification of contact lenses |

| WO2011045911A1 (ja) * | 2009-10-15 | 2011-04-21 | パナソニック株式会社 | 表示パネル装置及びその製造方法 |

| JP5593676B2 (ja) | 2009-10-22 | 2014-09-24 | ソニー株式会社 | 表示装置および表示装置の製造方法 |

| KR101146991B1 (ko) * | 2010-05-07 | 2012-05-23 | 삼성모바일디스플레이주식회사 | 유기 발광 디스플레이 장치 및 그 제조방법 |

| KR20120078954A (ko) | 2011-01-03 | 2012-07-11 | 삼성모바일디스플레이주식회사 | 유기전계발광표시장치 및 그 제조방법 |

| KR101521676B1 (ko) * | 2011-09-20 | 2015-05-19 | 엘지디스플레이 주식회사 | 유기발광 다이오드 표시장치 및 그의 제조방법 |

| JP2014029814A (ja) * | 2012-07-31 | 2014-02-13 | Sony Corp | 表示装置および電子機器 |

| KR102100880B1 (ko) * | 2013-06-26 | 2020-04-14 | 엘지디스플레이 주식회사 | 유기발광 다이오드 표시장치 |

| KR102372091B1 (ko) * | 2015-01-16 | 2022-03-11 | 삼성디스플레이 주식회사 | 유기 발광 표시 장치 및 그 제조 방법 |

| KR102591636B1 (ko) * | 2016-03-24 | 2023-10-20 | 삼성디스플레이 주식회사 | 유기발광 디스플레이 장치 |

| KR20220068308A (ko) | 2020-11-18 | 2022-05-26 | 삼성디스플레이 주식회사 | 표시 장치 |

| KR20220083047A (ko) | 2020-12-11 | 2022-06-20 | 엘지디스플레이 주식회사 | 터치센서를 포함하는 표시장치 및 그의 제조방법 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS61179698U (ja) * | 1985-04-30 | 1986-11-10 | ||

| JP2002318556A (ja) * | 2001-04-20 | 2002-10-31 | Toshiba Corp | アクティブマトリクス型平面表示装置およびその製造方法 |

| JP2004055530A (ja) * | 2002-05-28 | 2004-02-19 | Seiko Epson Corp | 発光装置および電子機器 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS61179698A (ja) | 1985-02-05 | 1986-08-12 | Fujitsu Ltd | 制御関与判定方式 |

| JPH0417393A (ja) * | 1990-05-10 | 1992-01-22 | Sumitomo Metal Mining Co Ltd | ポリイミド絶縁多層基板及びその製造方法 |

| US5643407A (en) * | 1994-09-30 | 1997-07-01 | Taiwan Semiconductor Manufacturing Company, Ltd. | Solving the poison via problem by adding N2 plasma treatment after via etching |

| US6123212A (en) * | 1999-08-27 | 2000-09-26 | Alcoa Closure Systems International | Plastic closure with rotation-inhibiting projections |

| JP4472120B2 (ja) * | 2000-06-08 | 2010-06-02 | 東北パイオニア株式会社 | 有機エレクトロルミネッセンス素子及びその製造方法 |

| US7301279B2 (en) * | 2001-03-19 | 2007-11-27 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting apparatus and method of manufacturing the same |

| US7309269B2 (en) * | 2002-04-15 | 2007-12-18 | Semiconductor Energy Laboratory Co., Ltd. | Method of fabricating light-emitting device and apparatus for manufacturing light-emitting device |

| JP3778176B2 (ja) * | 2002-05-28 | 2006-05-24 | セイコーエプソン株式会社 | 発光装置および電子機器 |

| AU2003271178A1 (en) * | 2002-10-17 | 2004-05-25 | Asahi Glass Company, Limited | Multilayer body, base with wiring, organic el display device, connection terminal of organic el display device, and methods for manufacturing these |

| US7247986B2 (en) * | 2003-06-10 | 2007-07-24 | Samsung Sdi. Co., Ltd. | Organic electro luminescent display and method for fabricating the same |

-

2004

- 2004-03-22 JP JP2004082477A patent/JP4608921B2/ja not_active Expired - Lifetime

-

2005

- 2005-03-21 US US11/084,957 patent/US8120246B2/en active Active

- 2005-03-21 TW TW094108663A patent/TWI275317B/zh active

- 2005-03-22 CN CNB200510069800XA patent/CN100546421C/zh active Active

- 2005-03-22 KR KR1020050023527A patent/KR101161443B1/ko active IP Right Grant

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS61179698U (ja) * | 1985-04-30 | 1986-11-10 | ||

| JP2002318556A (ja) * | 2001-04-20 | 2002-10-31 | Toshiba Corp | アクティブマトリクス型平面表示装置およびその製造方法 |

| JP2004055530A (ja) * | 2002-05-28 | 2004-02-19 | Seiko Epson Corp | 発光装置および電子機器 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10727433B2 (en) | 2018-04-30 | 2020-07-28 | Samsung Display Co., Ltd. | Display device |

Also Published As

| Publication number | Publication date |

|---|---|

| CN100546421C (zh) | 2009-09-30 |

| TW200607380A (en) | 2006-02-16 |

| TWI275317B (en) | 2007-03-01 |

| US20050206309A1 (en) | 2005-09-22 |

| KR101161443B1 (ko) | 2012-07-02 |

| KR20060044531A (ko) | 2006-05-16 |

| JP2005266667A (ja) | 2005-09-29 |

| CN1735296A (zh) | 2006-02-15 |

| US8120246B2 (en) | 2012-02-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4608921B2 (ja) | 表示装置の製造方法および表示装置 | |

| TWI549329B (zh) | 有機發光裝置及其製造方法 | |

| JP4089544B2 (ja) | 表示装置及び表示装置の製造方法 | |

| US7863814B2 (en) | Organic electroluminescent device comprising a stack partition structure | |

| CN110571361B (zh) | 有机发光显示面板及制作方法、显示装置 | |

| JP2005322564A (ja) | 表示装置の製造方法および表示装置 | |

| KR102453921B1 (ko) | 유기 발광 표시 장치 및 그 제조 방법 | |

| JP4637831B2 (ja) | 有機エレクトロルミネッセンス素子及びその製造方法並びに表示装置 | |

| JP2007123240A (ja) | 表示装置の製造方法および表示装置 | |

| JP2006339028A (ja) | 表示装置の製造方法および表示装置 | |

| KR102671037B1 (ko) | 유기 발광 표시 장치 및 유기 발광 표시 장치의 제조 방법 | |

| JP6868904B2 (ja) | 有機el表示パネルの製造方法 | |

| US20160218165A1 (en) | Organic light-emitting diode display and method of manufacturing the same | |

| JP4884320B2 (ja) | 画像表示装置 | |

| JP2007188895A (ja) | 表示装置及び表示装置の製造方法 | |

| JP2005209421A (ja) | 表示装置の製造方法および表示装置 | |

| JP2009092908A (ja) | 表示装置及びその製造方法 | |

| WO2020220443A1 (zh) | 有机发光显示面板及其制备方法 | |

| JP2009283242A (ja) | 有機el表示装置 | |

| JP2011222146A (ja) | 有機el表示装置の製造方法 | |

| JP4618497B2 (ja) | 表示装置および表示装置の製造方法 | |

| CN111785852A (zh) | 一种显示基板、其制作方法、显示面板及显示装置 | |

| JP2012174356A (ja) | 表示装置およびその製造方法 | |

| CN112599703A (zh) | 显示基板及其制备方法、显示面板 | |

| US20060108917A1 (en) | Organic electroluminescent device and fabricating method thereof |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061208 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061208 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20091021 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20091026 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20091105 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100405 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100608 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100802 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100914 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100927 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131022 Year of fee payment: 3 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 4608921 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131022 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S303 | Written request for registration of pledge or change of pledge |

Free format text: JAPANESE INTERMEDIATE CODE: R316303 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| S803 | Written request for registration of cancellation of provisional registration |

Free format text: JAPANESE INTERMEDIATE CODE: R316803 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |