JP4588163B2 - 表示装置 - Google Patents

表示装置 Download PDFInfo

- Publication number

- JP4588163B2 JP4588163B2 JP2000132761A JP2000132761A JP4588163B2 JP 4588163 B2 JP4588163 B2 JP 4588163B2 JP 2000132761 A JP2000132761 A JP 2000132761A JP 2000132761 A JP2000132761 A JP 2000132761A JP 4588163 B2 JP4588163 B2 JP 4588163B2

- Authority

- JP

- Japan

- Prior art keywords

- video data

- digital video

- bit digital

- gradation

- pixel

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Description

【発明の属する技術分野】

【0002】

本発明は、アクティブマトリクス型の表示装置に関する。特に、電圧階調と時間階調との両方によって階調表示を行う表示装置に関する。

【0003】

【従来の技術】

【0004】

最近安価なガラス基板上に半導体薄膜を形成した半導体装置、例えば薄膜トランジスタ(TFT)を作製する技術が急速に発達してきている。その理由は、アクティブマトリクス型液晶表示装置の需要が高まってきたことによる。

【0005】

アクティブマトリクス型液晶表示装置は、マトリクス状に配置された数十〜数百万個もの画素にそれぞれ画素TFTが配置され、各画素TFTに接続された画素電極に出入りする電荷を画素TFTのスイッチング機能により制御するものである。

【0006】

近年、アクティブマトリクス型液晶表示装置は、従来からよく用いられているノートブック型のパーソナルコンピュータのディスプレイとしてのみならず、デスクトップ型のパーソナルコンピュータのディスプレイとして普及してきている。

【0007】

パーソナルコンピュータにおいては、複数の情報(文字情報や画像情報を含む)を一度に表示することが求められており、パーソナルコンピュータの表示能力としての画像の高解像度化、多階調表示化(望ましくはフルカラー表示化)が図られている。

【0008】

このようなパーソナルコンピュータの表示能力の向上にともない、その表示装置としてのアクティブマトリクス型液晶表示装置の改良が進められている。

【0009】

【発明が解決しようとする課題】

【0010】

パーソナルコンピュータ等からの映像データはデジタルデータであり、アナログドライバのアクティブマトリクス型液晶表示装置にそのようなデジタルデータを直接入力することはできない。よって、パーソナルコンピュータ等からのデジタルデータをD/A変換回路によってアナログデータに変換した後、アクティブマトリクス型液晶表示装置に入力するようにしている。

【0011】

一般的に、より多階調の表示を実現するためには、D/A変換回路が処理することのできるデジタルデータのビット数を上げることが必要である。しかし、D/A変換回路は、デジタルデータのビット数が増加するとその素子のレイアウト面積が指数関数的に増加し、また、D/A変換回路の回路構成が複雑になる。よって、D/A変換回路の素子の大きさや価格が問題となっている。

【0012】

しかし、上述した様に、多階調(好ましくはフルカラー)を表示することができるアクティブマトリクス型液晶表示装置が要求されており、低ビット数のデジタルデータを処理するD/A変換回路を用いて多階調表示を実現する液晶表示装置が望まれている。

【0013】

【課題を解決するための手段】

【0014】

本発明は上述の問題に鑑みてなされたものであり、高解像度化および多階調化を実現することのできる表示装置を提供するものである。

【0015】

本発明によると、

複数の画素TFTがマトリクス状に配置された画素部と、

前記複数のTFTを駆動するソースドライバおよびゲートドライバと、

外部から入力されるmビットデジタルビデオデータを2m-n個のnビットデジタルビデオデータに変換する処理回路と(m、nは共に2以上の正数、m>n)、

前記nビットデジタルデータをアナログビデオデータに変換し、前記ソースドライバへ出力するD/A変換回路と、

を有する表示装置であって、

前記処理回路は、前記D/A変換回路へ前記2m-n個のnビットデジタルデータをランダムに出力し、

前記nビットデジタルビデオデータによって形成されるサブフレームを2m-n個表示することによって1フレームの映像を形成することを特徴とする表示装置が提供される。

【0016】

また、本発明によると、

複数の画素TFTがマトリクス状に配置された画素部と、

前記複数のTFTを駆動するソースドライバおよびゲートドライバと、

外部から入力されるmビットデジタルビデオデータを2m-n個のnビットデジタルビデオデータに変換する処理回路と(m、nは共に2以上の正数、m>n)、

前記nビットデジタルデータをアナログビデオデータに変換し、前記ソースドライバへ出力するD/A変換回路と、

を有する表示装置であって、

前記処理回路は、前記D/A変換回路へ前記2m-n個のnビットデジタルデータをランダムに出力し、

前記nビットデジタルビデオデータによって形成されるサブフレームを2m-n個表示することによって1フレームの映像を形成し、

(2m−(2m-n−1))通りの表示階調を得ることを特徴とする表示装置が提供される。

【0017】

また、本発明によると、

複数の画素TFTがマトリクス状に配置された画素部と、

前記複数のTFTを駆動するソースドライバおよびゲートドライバと、

外部から入力されるmビットデジタルビデオデータを2m-n個のnビットデジタルビデオデータに変換する処理回路と(m、nは共に2以上の正数、m>n)、

前記nビットデジタルデータをアナログビデオデータに変換し、前記ソースドライバへ出力するD/A変換回路と、

を有する表示装置であって、

前記2m-n個のnビットデジタルデータは、複数の出力パターンからランダムに選択されたパターンによって前記D/A変換回路へ出力され、

前記nビットデジタルビデオデータによって形成されるサブフレームを2m-n個表示することによって1フレームの映像を形成することを特徴とする表示装置が提供される。

【0018】

また、本発明によると、

複数の画素TFTがマトリクス状に配置された画素部と、

前記複数のTFTを駆動するソースドライバおよびゲートドライバと、

外部から入力されるmビットデジタルビデオデータを2m-n個のnビットデジタルビデオデータに変換する処理回路と(m、nは共に2以上の正数、m>n)、

前記nビットデジタルデータをアナログビデオデータに変換し、前記ソースドライバへ出力するD/A変換回路と、

を有する表示装置であって、

前記2m-n個のnビットデジタルデータは、複数の出力パターンからランダムに選択されたパターンによって前記D/A変換回路へ出力され、

前記nビットデジタルビデオデータによって形成されるサブフレームを2m-n個表示することによって1フレームの映像を形成し、

(2m−(2m-n−1))通りの表示階調を得ることを特徴とする表示装置が提供される。

【0019】

また、本発明によると、

複数の画素TFTがマトリクス状に配置された画素部と、

前記複数のTFTを駆動するソースドライバおよびゲートドライバと、

外部から入力されるアナログビデオデータをmビットデジタルビデオデータに変換するA/D変換回路と、

前記mビットデジタルビデオデータを2m-n個のnビットデジタルビデオデータに変換する処理回路と(m、nは共に2以上の正数、m>n)、

前記nビットデジタルデータをアナログビデオデータに変換し、前記ソースドライバへ出力するD/A変換回路と、

を有する表示装置であって、

前記処理回路は、前記D/A変換回路へ前記2m-n個のnビットデジタルデータをランダムに出力し、

前記nビットデジタルビデオデータによって形成されるサブフレームを2m-n個表示することによって1フレームの映像を形成することを特徴とする表示装置が提供される。

【0020】

また、本発明によると、

複数の画素TFTがマトリクス状に配置された画素部と、

前記複数のTFTを駆動するソースドライバおよびゲートドライバと、

外部から入力されるアナログビデオデータをmビットデジタルビデオデータに変換するA/D変換回路と、

前記mビットデジタルビデオデータを2m-n個のnビットデジタルビデオデータに変換する処理回路と(m、nは共に2以上の正数、m>n)、

前記nビットデジタルデータをアナログビデオデータに変換し、前記ソースドライバへ出力するD/A変換回路と、

を有する表示装置であって、

前記処理回路は、前記D/A変換回路へ前記2m-n個のnビットデジタルデータをランダムに出力し、

前記nビットデジタルビデオデータによって形成されるサブフレームを2m-n個表示することによって1フレームの映像を形成し、

(2m−(2m-n−1))通りの表示階調を得ることを特徴とする表示装置が提供される。

【0021】

また、本発明によると、

複数の画素TFTがマトリクス状に配置された画素部と、

前記複数のTFTを駆動するソースドライバおよびゲートドライバと、

外部から入力されるアナログビデオデータをmビットデジタルビデオデータに変換するA/D変換回路と、

前記mビットデジタルビデオデータを2m-n個のnビットデジタルビデオデータに変換する処理回路と(m、nは共に2以上の正数、m>n)、

前記nビットデジタルデータをアナログビデオデータに変換し、前記ソースドライバへ出力するD/A変換回路と、

を有する表示装置であって、

前記2m-n個のnビットデジタルデータは、複数の出力パターンからランダムに選択されたパターンによって前記D/A変換回路へ出力され、

前記nビットデジタルビデオデータによって形成されるサブフレームを2m-n個表示することによって1フレームの映像を形成することを特徴とする表示装置が提供される。

【0022】

また、本発明によると、

複数の画素TFTがマトリクス状に配置された画素部と、

前記複数のTFTを駆動するソースドライバおよびゲートドライバと、

外部から入力されるアナログビデオデータをmビットデジタルビデオデータに変換するA/D変換回路と、

前記mビットデジタルビデオデータを2m-n個のnビットデジタルビデオデータに変換する処理回路と(m、nは共に2以上の正数、m>n)、

前記nビットデジタルデータをアナログビデオデータに変換し、前記ソースドライバへ出力するD/A変換回路と、

を有する表示装置であって、

前記2m-n個のnビットデジタルデータは、複数の出力パターンからランダムに選択されたパターンによって前記D/A変換回路へ出力され、

前記nビットデジタルビデオデータによって形成されるサブフレームを2m-n個表示することによって1フレームの映像を形成し、

(2m−(2m-n−1))通りの表示階調を得ることを特徴とする表示装置が提供される。

【0023】

以下の実施の形態をもって本発明を詳しく説明する。

【0024】

【発明の実施の形態】

【0025】

図1を参照する。図1には、本発明の表示装置の概略構成図が示されている。

101はアナログドライバを有するアクティブマトリクス型表示装置である。アクティブマトリクス型表示装置101は、アクティブマトリクス基板101−1および対向基板101−2(図示せず)を有している。アクティブマトリクス基板101−1は、ソースドライバ101−1−1、ゲートドライバ101−1−2および101−1−3、および複数の画素TFTがマトリクス状に配置された画素部101−1−4を有している。ソースドライバ101−1−1およびゲートドライバ101−1−2ならびに101−1−3は、画素部の複数の画素TFTを駆動する。また、対向基板101−2は、対向電極101−2−1(図示せず)を有している。

【0026】

102はデジタルビデオデータ時間階調処理回路である。デジタルビデオデータ時間階調処理回路102は、外部から入力されるmビットデジタルビデオデータ基づいて電圧階調の為の2m-n個のシリアルなnビットデジタルビデオデータを作成する。外部から入力されるmビットデジタルビデオデータが、デジタルビデオデータ時間階調処理回路102によって電圧階調の為の2m-n個のシリアルなnビットデジタルビデオデータに変換するわけである。

【0027】

mビットデジタルビデオデータを2m-n個のシリアルなnビットデジタルビデオデータに変換する場合、2m-n個のnビットデジタルビデオデータの出力順序はランダムに行われる。

【0028】

なお、前記mビットのデジタルビデオデータのうち(m−n)ビットの階調情報は、時間階調による階調表示に用いられる。本願明細書における、時間階調によって階調表示を行う方法については後で詳述する。

【0029】

デジタルビデオデータ時間階調処理回路102によって作成された2m-n個のシリアルなnビットデジタルビデオデータはD/A変換回路103に入力され、アナログビデオデータに変換される。

【0030】

D/A変換回路によって作成されたアナログビデオデータは、アナログドライバを有するアクティブマトリクス型表示装置101に入力される。

【0031】

アクティブマトリクス型表示装置101に入力されたアナログビデオデータは、ソースドライバ101−1−1に入力され、ソースドライバ内のサンプリング回路によって各ソース信号線に供給され、対応する画素TFTに供給される。

【0032】

なお、本願明細書においては、本発明の表示装置は、アナログドライバを有するアクティブマトリクス型表示装置、デジタルビデオデータ時間階調処理回路およびD/A変換回路を有するものとする。また、後述するが、アナログドライバを有するアクティブマトリクス型液晶表示装置とデジタルビデオデータ時間階調処理回路とD/A変換回路とが同一基板上に一体形成されたものも本発明の表示装置とする。

【0033】

以下に本発明の表示装置を実施例をもって詳しく説明する。ただし、本発明の液晶表示装置は、以下の実施例に限定されるわけではない。

【0034】

【実施例】

【0035】

(実施例1)

【0036】

本実施例においては、説明の簡略のため、外部から4ビットデジタルビデオデータが供給される本発明の表示装置として液晶表示装置を例にとっている。

【0037】

図2を参照する。図2には、本発明の液晶表示装置の概略構成図が示されている。201はアナログドライバを有するアクティブマトリクス型液晶表示装置である。アクティブマトリクス型液晶表示装置201は、アクティブマトリクス基板201−1および対向基板201−2(図示せず)を有している。アクティブマトリクス基板201−1は、ソースドライバ201−1−1、ゲートドライバ201−1−2ならびに201−1−3、および複数の画素TFTがマトリクス状に配置された画素部201−1−4を有している。ソースドライバ201−1−1およびゲートドライバ201−1−2ならびに201−1−3は、画素部の複数の画素TFTを駆動する。また、対向基板201−2は、対向電極201−2−1(図示せず)を有している。

【0038】

202はデジタルビデオデータ時間階調処理回路である。デジタルビデオデータ時間階調処理回路202は、外部から入力される4ビットデジタルビデオデータに基づいて電圧階調の為の4個(=24-2個)のシリアルな2ビットデジタルビデオデータを作成する。上述したように、4個の2ビットデジタルビデオデータの出力順序はランダムにされる。前記4ビットのデジタルビデオデータのうち2ビットの階調情報は、時間階調による階調表示に用いられる。

【0039】

デジタルビデオデータ時間階調処理回路202によって作成された4個の2ビットデジタルビデオデータはD/A変換回路203にランダムにかつシリアルに入力され、アナログビデオデータに変換される。

【0040】

D/A変換回路によって作成されたアナログビデオデータは、アナログドライバを有するアクティブマトリクス型液晶表示装置201に入力される。

【0041】

アクティブマトリクス型液晶表示装置201に入力されたアナログビデオデータは、ソースドライバ201−1−1に入力され、ソースドライバ内のサンプリング回路によって各ソース信号線に供給され、対応する画素TFTに供給される。

【0042】

ここで、本実施例の液晶表示装置のアクティブマトリクス型液晶表示装置201の回路構成、特に画素部201−1−4の構成について、図3を用いて説明する。

【0043】

本実施例においては、画素部201−1−4は、(x×y)個の画素を有している。それぞれの画素には、説明の便宜上、P1,1、P2,1、・・・、Py,x等の符号が付けられている。また、それぞれの画素は、画素TFT301、保持容量303を有している。アクティブマトリクス基板と対向基板との間には液晶が挟まれており、液晶302は各画素に対応する液晶を模式的に示したものである。なお、COMはコモン電圧端子であり、対向電極および保持容量の一端に接続されている。

【0044】

一般に、表示装置においては、1画面の表示を1フレームと呼ぶが、本実施例においては、4個のサブフレームを連続的に時分割表示することによって1フレームを形成する。そこで、本実施例においては、1フレームの表示を行うのに要する時間を1フレーム期間(Tf)と呼び、1フレーム期間(Tf)を4分割した期間をサブフレーム期間(Tsf)と呼び、さらに、1画素にアナログ階調電圧を書き込むのに要する時間を1サブフレームドット期間(Tsfd)と呼ぶことにする。

【0045】

次に、本実施例の液晶表示装置の階調表示について説明する。本実施例の液晶表示装置には4ビットデジタルビデオデータが供給され、前記4ビットデジタルビデオデータが24=16通りの階調情報を有していることは上述の通りである。ここで、図4を参照する。図4には、本実施例の液晶表示装置に用いられるD/A変換回路の階調電圧レベルと実際に表示され、観察者が認識する階調(階調表示レベル)とが示されている。電圧レベルVLはD/A変換回路に入力される最低の電圧レベルであり、また、電圧レベルVHはD/A変換回路に入力される最高の電圧レベルである。

【0046】

本実施例においては、2ビット、つまり4階調の電圧レベルを実現するために、電圧レベルVHと電圧レベルVLとの間をほぼ等電圧に4分割し、その等電圧をαとした(α=(VH−VL)/4である)。なお、ここではαを電圧レベルのステップと呼ぶ。よって、本実施例のD/A変換回路が出力する階調電圧レベルは、2ビットデジタルビデオデータのアドレスが(00)の時はVLとなり、2ビットデジタルビデオデータのアドレスが(01)の時はVL+αとなり、2ビットデジタルビデオデータのアドレスが(10)の時はVL+2αとなり、2ビットデジタルビデオデータのアドレスが(11)の時はVL+3αとなる。

【0047】

本実施例のD/A変換回路が出力できる階調電圧レベルは、上述の様にVL、VL+α、VL+2α、およびVL+3αの4通りであが、本発明においては、時間階調表示を組合わせることによって液晶表示装置の階調表示レベルの数を上げることができる。

【0048】

つまり、本実施例においては、4ビットデジタルビデオデータのうちの2ビット分の階調情報を時間階調表示の情報として用いることによって、電圧レベルのステップαをほぼ4等分した階調電圧レベルに相当する階調表示レベルを実現することができる。すなわち、本実施例の液晶表示装置は、VL、VL+α/4、VL+2α/4、VL+3α/4、VL+α、VL+5α/4、VL+6α/4、VL+7α/4、VL+2α、VL+9α/4、VL+10α/4、VL+11α/4、VL+3αの階調電圧レベルに相当する階調表示レベルを実現することができる。

【0049】

本発明の液晶表示装置は、1フレーム期間Tfを4つのサブフレーム期間(1st Tsf、2nd Tsf、3rd Tsf、および4th Tsf)に分割して表示を行っている。さらに、本実施例の液晶表示装置は、いわゆる点順次駆動を行うので、1フレーム期間において各画素には1サブフレームドット期間(Tsfd)の間、階調電圧が書き込まれ、サブフレーム期間中画素に階調情報が保持される。よって、各サブフレーム期間(1st Tsf、2nd Tsf、3rd Tsf、および4th Tsf)に対応する各サブフレームドット期間(1st Tsfd、2nd Tsfd、3rd Tsfd、および4th Tsfd)に、時間階調処理後の2ビットデジタルビデオデータのアドレスがD/A変換回路に入力され、D/A変換回路からアナログビデオデータ(階調電圧)が出力され、液晶表示装置のソースドライバに入力される。ソースドライバに入力される階調電圧はソースドライバのサンプリング回路によってサンプリングされ、対応する画素に供給される。

【0050】

4つのサブフレームドット期間(1st Tsfd、2nd Tsfd、3rd Tsfd、および4th Tsfd)に書き込まれる階調電圧によって4回のサブフレームの表示が高速に行われ、結果として1フレームの階調表示レベルは、各サブフレームドット期間の階調電圧レベルの総和を時間平均したものになる。

【0051】

ここで、図5〜図8を参照し、本発明の液晶表示装置における、上記の階調電圧レベルに相当する階調表示レベルの表示方法について説明する。

【0052】

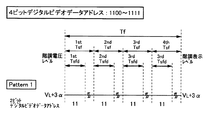

まず、図5を参照する。図5には、外部から入力される4ビットデジタルビデオデータのアドレスが(0000)の場合に、各サブフレームドット期間(1st Tsfd、2nd Tsfd、3rd Tsfd、または4th Tsfd)に各画素(画素TFT)に供給されるD/A変換回路によって作成された階調電圧レベルが実線で、階調表示レベルが点線で示されている。(ただし、階調表示レベルを示す点線は、図5においては、階調電圧レベルを示す実線と重なっている。)

【0053】

デジタルビデオデータ時間階調処理回路は、外部から入力される4ビットデジタルビデオデータを基に4個の2ビットのデジタルビデオデータを作成する。外部から入力される4ビットデジタルビデオデータのアドレスが(0000)の時、デジタルビデオデータ時間階調処理回路は2ビットのデジタルビデオデータ(アドレス(00))を作成しD/A変換回路へ出力する。D/A変換回路は、入力される2ビットのデジタルビデオデータを階調電圧に変換し、アクティブマトリクス型液晶表示装置のソースドライバに供給する。図5に示されるように、外部から入力される4ビットデジタルビデオデータのアドレスが(0000)の時、各サブフレームドット期間(1st Tsfd、2nd Tsfd、3rd Tsfd、および4th Tsfd)には、階調電圧レベルVL(アドレス(00))がそれぞれ対応する画素に出力される。図5に示されるように、外部から入力される4ビットデジタルビデオデータのアドレスが(0000)の時、各サブフレームドット期間(1st Tsfd、2nd Tsfd、3rd Tsfd、および4th Tsfd)に供給される階調電圧レベルのパターンは、1通り(Pattern 1)のみである。よって、階調表示レベルはVLとなる。

【0054】

次に、図6を参照する。図6には、外部から入力される4ビットデジタルビデオデータのアドレスが(0001)の場合に、各サブフレームドット期間(1st Tsfd、2nd Tsfd、3rd Tsfd、または4th Tsfd)に各画素(画素TFT)に供給されるD/A変換回路によって作成された階調電圧レベルが実線で、階調表示レベルが点線で示されている。

【0055】

デジタルビデオデータ時間階調処理回路は、外部から入力される4ビットデジタルビデオデータのアドレスが(0001)の時、2ビットのデジタルビデオデータ(アドレス(00)または(01))を作成しD/A変換回路へ出力する。D/A変換回路は、入力される2ビットのデジタルビデオデータを階調電圧に変換し、アクティブマトリクス型液晶表示装置のソースドライバに供給する。図6に示されるように、外部から入力される4ビットデジタルビデオデータのアドレスが(0001)の時、各サブフレームドット期間には、階調電圧レベルVL(アドレス(00))が3回およびVL+α(アドレス(01))が1回、順序をランダムにして対応する画素に供給される。図6から理解されるように、外部から入力される4ビットデジタルビデオデータのアドレスが(0001)の時、各サブフレームドット期間に各画素に供給される階調電圧レベルのパターンは、4通り(Pattern 1、Pattern 2、Pattern 3、およびPattern 4)であり、何れの場合においても階調表示レベルはVL+α/4となる。

【0056】

このように、本発明の液晶表示装置においては、外部から入力される4ビットデジタルビデオデータのアドレスが(0001)の時、各サブフレームドット期間に各画素に供給される階調電圧レベルを、これら4通りのパターン(Pattern 1、Pattern 2、Pattern 3、およびPattern 4)がランダムで供給されるようにする。こうすることによって、VL+α/4に対応する階調表示レベルを実現でき、かつ、各サブフレームドット期間に各画素に偏りなく階調電圧が書き込まれることになり、フレーム周波数を上げなくてもフリッカの発生を減少させることができる。

【0057】

次に、図7を参照する。図7には、外部から入力される4ビットデジタルビデオデータのアドレスが(0010)の場合に、各サブフレームドット期間(1st Tsfd、2nd Tsfd、3rd Tsfd、または4th Tsfd)に各画素(画素TFT)に供給されるD/A変換回路によって作成された階調電圧レベルが実線で、階調表示レベルが点線で示されている。

【0058】

デジタルビデオデータ時間階調処理回路は、外部から入力される4ビットデジタルビデオデータのアドレスが(0010)の時、2ビットのデジタルビデオデータ(アドレス(00)または(01))を作成しD/A変換回路へ出力する。D/A変換回路は、入力される2ビットのデジタルビデオデータを階調電圧に変換し、アクティブマトリクス型液晶表示装置のソースドライバに供給する。図7に示されるように、外部から入力される4ビットデジタルビデオデータのアドレスが(0010)の時、各サブフレームドット期間には、階調電圧レベルVL(アドレス(00))が2回およびVL+α(アドレス(01))が2回、順序をランダムにして対応する画素に供給される。図7から理解されるように、外部から入力される4ビットデジタルビデオデータのアドレスが(0010)の時、各サブフレームドット期間に各画素に供給される階調電圧レベルのパターンは、6通り(Pattern 1、Pattern 2、Pattern 3、Pattern 4、Pattern 5、およびPattern 6)であり何れの場合においても、階調表示レベルはVL+2α/4となる。

【0059】

このように、外部から入力される4ビットデジタルビデオデータのアドレスが(0010)の時も、各サブフレームドット期間に各画素に供給される階調電圧レベルを、これら6通りのパターン(Pattern 1、Pattern 2、Pattern 3、Pattern 4、Pattern 5、およびPattern 6)がランダムで出力されるようにする。こうすることによって、VL+2α/4に対応する階調表示レベルを実現でき、かつ、各サブフレームドット期間に各画素に偏りなく階調電圧が書き込まれることになり、フレーム周波数を上げなくてもフリッカの発生を減少させることができる。

【0060】

次に、図8を参照する。図8には、外部から入力される4ビットデジタルビデオデータのアドレスが(0011)の場合に、各サブフレームドット期間(1st Tsfd、2nd Tsfd、3rd Tsfd、または4th Tsfd)に各画素(画素TFT)に供給されるD/A変換回路によって作成された階調電圧レベルが実線で、階調表示レベルが点線で示されている。

【0061】

デジタルビデオデータ時間階調処理回路は、外部から入力される4ビットデジタルビデオデータのアドレスが(0011)の時、2ビットのデジタルビデオデータ(アドレス(00)または(01))を作成しD/A変換回路へ出力する。D/A変換回路は、入力される2ビットのデジタルビデオデータを階調電圧に変換し、アクティブマトリクス型液晶表示装置のソースドライバに供給する。図8に示すように、外部から入力される4ビットデジタルビデオデータのアドレスが(0011)の時、各サブフレームドット期間には、階調電圧レベルVL(アドレス(00))が1回およびVL+α(アドレス(01))が3回、順序をランダムにして対応する画素に供給される。図8から理解されるように、外部から入力される4ビットデジタルビデオデータのアドレスが(0011)の時、各サブフレームドット期間に各画素に供給される階調電圧レベルのパターンは、4通り(Pattern 1、Pattern 2、Pattern 3、およびPattern 4)であり何れの場合においても、階調表示レベルはVL+3α/4となる。

【0062】

このように、外部から入力される4ビットデジタルビデオデータのアドレスが(0011)の時も、各サブフレームドット期間に各画素に供給される階調電圧レベルを、これら4通りのパターン(Pattern 1、Pattern 2、Pattern 3、およびPattern 4)がランダムで出力されるようにする。こうすることによって、VL+3α/4に対応する階調表示レベルを実現でき、かつ、各サブフレームドット期間に各画素に偏りなく階調電圧が書き込まれることになり、フレーム周波数を上げなくてもフリッカの発生を減少させることができる。

【0063】

同様に、外部から入力される4ビットデジタルビデオデータのアドレスが、(0100)、(0101)、(0110)、および(0111)の場合について以下に説明する。

【0064】

図9を参照する。図9には、外部から入力される4ビットデジタルビデオデータのアドレスが(0100)の場合に、各サブフレームドット期間(1st Tsfd、2nd Tsfd、3rd Tsfd、または4th Tsfd)に各画素(画素TFT)に供給されるD/A変換回路によって作成された階調電圧レベルが実線で、階調表示レベルが点線で示されている。

【0065】

デジタルビデオデータ時間階調処理回路は、外部から入力される4ビットデジタルビデオデータを基に2ビットのデジタルビデオデータを作成する。外部から入力される4ビットデジタルビデオデータのアドレスが(0100)の時、デジタルビデオデータ時間階調処理回路は、2ビットのデジタルビデオデータ(アドレス(01))を作成しD/A変換回路へ出力する。D/A変換回路は、入力される2ビットのデジタルビデオデータを階調電圧に変換し、アクティブマトリクス型液晶表示装置のソースドライバに供給する。図9に示されるように、外部から入力される4ビットデジタルビデオデータのアドレスが(0100)の時、各サブフレームドット期間(1st Tsfd、2nd Tsfd、3rd Tsfd、および4th Tsfd)には、各階調電圧レベルVL+α(アドレス(01))がそれぞれ対応する画素に供給される。図9に示されるように、外部から入力される4ビットデジタルビデオデータのアドレスが(0100)の時、各サブフレームドット期間(1st Tsfd、2nd Tsfd、3rd Tsfd、および4th Tsfd)に供給される階調電圧レベルのパターンは、1通り(Pattern 1)のみである。よって、階調表示レベルはVL+αとなる。

【0066】

次に、図10を参照する。図10には、外部から入力される4ビットデジタルビデオデータのアドレスが(0101)の場合に、各サブフレームドット期間(1st Tsfd、2nd Tsfd、3rd Tsfd、または4th Tsfd)に各画素(画素TFT)に供給されるD/A変換回路によって作成された階調電圧レベルが実線で、階調表示レベルが点線で示されている。

【0067】

デジタルビデオデータ時間階調処理回路は、外部から入力される4ビットデジタルビデオデータのアドレスが(0101)の時、2ビットのデジタルビデオデータ(アドレス(01)または(10))を作成し、D/A変換回路へ出力する。D/A変換回路は、入力される2ビットのデジタルビデオデータを階調電圧に変換し、アクティブマトリクス型液晶表示装置のソースドライバに供給する。図10に示されるように、外部から入力される4ビットデジタルビデオデータのアドレスが(0101)の時、各サブフレームドット期間には、階調電圧レベルVL+α(アドレス(01))が3回およびVL+2α(アドレス(10))が1回、順序をランダムにして対応する画素に供給される。図10から理解されるように、外部から入力される4ビットデジタルビデオデータのアドレスが(0101)の時、各サブフレームドット期間に供給される階調電圧レベルのパターンは、4通り(Pattern 1、Pattern 2、Pattern 3、およびPattern 4)であり何れの場合においても、階調表示レベルはVL+5α/4となる。

【0068】

なお、外部から入力される4ビットデジタルビデオデータのアドレスが(0101)の時、各サブフレームドット期間に各画素に供給される階調電圧レベルを、これら4通りのパターン(Pattern 1、Pattern 2、Pattern 3、およびPattern 4)がランダムで出力されるようにする。こうすることによって、VL+5α/4に対応する階調表示レベルを実現でき、かつ、各サブフレームドット期間に各画素に偏りなく階調電圧が書き込まれることになり、フレーム周波数を上げなくてもフリッカの発生を減少させることができる。

【0069】

次に、図11を参照する。図11には、外部から入力される4ビットデジタルビデオデータのアドレスが(0110)の場合に、各サブフレームドット期間(1st Tsfd、2nd Tsfd、3rd Tsfd、または4th Tsfd)に各画素(画素TFT)に供給されるD/A変換回路によって作成された階調電圧レベルが実線で、階調表示レベルが点線で示されている。

【0070】

デジタルビデオデータ時間階調処理回路は、外部から入力される4ビットデジタルビデオデータのアドレスが(0110)の時、2ビットのデジタルビデオデータ(アドレス(01)または(10))を作成しD/A変換回路へ出力する。D/A変換回路は、入力される2ビットのデジタルビデオデータを階調電圧に変換し、アクティブマトリクス型液晶表示装置のソースドライバに供給する。図11に示されるように、外部から入力される4ビットデジタルビデオデータのアドレスが(0110)の時、各サブフレームドット期間には、階調電圧レベルVL+α(アドレス(01))が2回およびVL+2α(アドレス(10))が2回、順序をランダムにして対応する画素に供給される。図11から理解されるように、外部から入力される4ビットデジタルビデオデータのアドレスが(0110)の時、各サブフレームドット期間に各画素に供給される階調電圧レベルのパターンは、6通り(Pattern 1、Pattern 2、Pattern 3、Pattern 4、Pattern 5、およびPattern 6)であり何れの場合においても、階調表示レベルはVL+6α/4となる。

【0071】

なお、外部から入力される4ビットデジタルビデオデータのアドレスが(0110)の時も、各サブフレームドット期間に各画素に供給される階調電圧レベルを、これら6通りのパターン(Pattern 1、Pattern 2、Pattern 3、Pattern 4、Pattern 5、およびPattern 6)がランダムで出力されるようにする。こうすることによって、VL+6α/4に対応する階調表示レベルを実現でき、かつ、各サブフレームドット期間に各画素に偏りなく階調電圧が書き込まれることになり、フレーム周波数を上げなくてもフリッカの発生を減少させることができる。

【0072】

次に、図12を参照する。図12には、外部から入力される4ビットデジタルビデオデータのアドレスが(0111)の場合に、各サブフレームドット期間(1st Tsfd、2nd Tsfd、3rd Tsfd、または4th Tsfd)に各画素(画素TFT)に供給されるD/A変換回路によって作成された階調電圧レベルが実線で、階調表示レベルが点線で示されている。

【0073】

デジタルビデオデータ時間階調処理回路は、外部から入力される4ビットデジタルビデオデータのアドレスが(0111)の時、2ビットのデジタルビデオデータ(アドレス(01)または(10))を作成しD/A変換回路へ出力する。D/A変換回路は、入力される2ビットのデジタルビデオデータを階調電圧に変換し、アクティブマトリクス型液晶表示装置のソースドライバに供給する。図12に示されるように、外部から入力される4ビットデジタルビデオデータのアドレスが(0111)の時、各サブフレームドット期間には、階調電圧レベルVL+α(アドレス(01))が1回およびVL+2α(アドレス(10))が3回、順序をランダムにして対応する画素に供給される。図12から理解されるように、外部から入力される4ビットデジタルビデオデータのアドレスが(0111)の時、各サブフレームドット期間に各画素に供給される階調電圧レベルのパターンは、4通り(Pattern 1、Pattern 2、Pattern 3、およびPattern 4)であり何れの場合においても、階調表示レベルはVL+7α/4となる。

【0074】

このように、外部から入力される4ビットデジタルビデオデータのアドレスが(0111)の時も、各サブフレームドット期間に各画素に供給される階調電圧レベルを、これら4通りのパターン(Pattern 1、Pattern 2、Pattern 3、およびPattern 4)がランダムで出力されるようにする。こうすることによって、VL+7α/4に対応する階調表示レベルを実現でき、かつ、各サブフレームドット期間に各画素に偏りなく階調電圧が書き込まれることになり、フレーム周波数を上げなくてもフリッカの発生を減少させることができる。

【0075】

同様に、外部から入力される4ビットデジタルビデオデータのアドレスが、(1000)、(1001)、(1010)、および(1011)の場合について以下に説明する。

【0076】

図13を参照する。図13には、外部から入力される4ビットデジタルビデオデータのアドレスが(1000)の場合に、各サブフレームドット期間(1st Tsfd、2nd Tsfd、3rd Tsfd、または4th Tsfd)に各画素(画素TFT)に供給されるD/A変換回路によって作成された階調電圧レベルが実線で、階調表示レベルが点線で示されている。

【0077】

デジタルビデオデータ時間階調処理回路は、外部から入力される4ビットデジタルビデオデータを基に2ビットのデジタルビデオデータを作成する。外部から入力される4ビットデジタルビデオデータのアドレスが(1000)の時、デジタルビデオデータ時間階調処理回路は、2ビットのデジタルビデオデータ(アドレス(10))を作成しD/A変換回路へ出力する。D/A変換回路は、入力される2ビットのデジタルビデオデータを階調電圧に変換し、アクティブマトリクス型液晶表示装置のソースドライバに供給する。図13に示されるように、外部から入力される4ビットデジタルビデオデータのアドレスが(1000)の時、各サブフレームドット期間(1st Tsfd、2nd Tsfd、3rd Tsfd、および4th Tsfd)には、階調電圧レベルVL+2α(アドレス(10))がそれぞれ対応する画素に供給される。図13に示されるうように、外部から入力される4ビットデジタルビデオデータのアドレスが(1000)の時、各サブフレームドット期間(1st Tsfd、2nd Tsfd、3rd Tsfd、および4th Tsfd)に供給される階調電圧レベルのパターンは、1通り(Pattern 1)のみである。よって、階調表示レベルはVL+2αとなる。

【0078】

次に、図14を参照する。図14には、外部から入力される4ビットデジタルビデオデータのアドレスが(1001)の場合に、各サブフレームドット期間(1st Tsfd、2nd Tsfd、3rd Tsfd、または4th Tsfd)に各画素(画素TFT)に供給されるD/A変換回路によって作成された階調電圧レベルが実線で、階調表示レベルが点線で示されている。

【0079】

デジタルビデオデータ時間階調処理回路は、外部から入力される4ビットデジタルビデオデータのアドレスが(1001)の時、2ビットのデジタルビデオデータ(アドレス(10)または(11))を作成しD/A変換回路へ出力する。D/A変換回路は、入力される2ビットのデジタルビデオデータを階調電圧に変換し、アクティブマトリクス型液晶表示装置のソースドライバに供給する。図14に示されるように、外部から入力される4ビットデジタルビデオデータのアドレスが(1001)の時、各サブフレームドット期間には、階調電圧レベルVL+2α(アドレス(10))が3回およびVL+3α(アドレス(11))が1回、順序をランダムにして対応する画素に供給される。図14から理解されるように、外部から入力される4ビットデジタルビデオデータのアドレスが(1001)の時、各サブフレームドット期間に各画素に供給される階調電圧レベルのパターンは、4通り(Pattern 1、Pattern 2、Pattern 3、およびPattern 4)であり何れの場合においても、階調表示レベルはVL+9α/4となる。

【0080】

なお、外部から入力される4ビットデジタルビデオデータのアドレスが(1001)の時、各サブフレームドット期間に各画素に供給される階調電圧レベルを、これら4通りのパターン(Pattern 1、Pattern 2、Pattern 3、およびPattern 4)がランダムで出力されるようにしている。こうすることによって、VL+9α/4に対応する階調表示レベルを実現でき、かつ、各サブフレームドット期間に各画素に偏りなく階調電圧が書き込まれることになり、フレーム周波数を上げなくてもフリッカの発生を減少させることができる。

【0081】

次に、図15を参照する。図15には、外部から入力される4ビットデジタルビデオデータのアドレスが(1010)の場合に、各サブフレームドット期間(1st Tsfd、2nd Tsfd、3rd Tsfd、または4th Tsfd)に各画素(画素TFT)に供給されるD/A変換回路によって作成された階調電圧レベルが実線で、階調表示レベルが点線で示されている。

【0082】

デジタルビデオデータ時間階調処理回路は、外部から入力される4ビットデジタルビデオデータのアドレスが(1010)の時、2ビットのデジタルビデオデータ(アドレス(10)または(11))を作成しD/A変換回路へ出力する。D/A変換回路は、入力される2ビットのデジタルビデオデータを階調電圧に変換し、アクティブマトリクス型液晶表示装置のソースドライバに供給する。図15に示されるように、外部から入力される4ビットデジタルビデオデータのアドレスが(1010)の時、各サブフレームドット期間には、階調電圧レベルVL+2α(アドレス(10))が2回およびVL+3α(アドレス(11))が2回、順序をランダムにして対応する画素に供給される。図15から理解されるように、外部から入力される4ビットデジタルビデオデータのアドレスが(1010)の時、各サブフレームドット期間に各画素に供給される階調電圧レベルのパターンは、6通り(Pattern 1、Pattern 2、Pattern 3、Pattern 4、Pattern 5、およびPattern 6)であり何れの場合においても、階調表示レベルはVL+10α/4となる。

【0083】

外部から入力される4ビットデジタルビデオデータのアドレスが(1010)の時も、各サブフレームドット期間に各画素に供給される階調電圧レベルを、これら6通りのパターン(Pattern 1、Pattern 2、Pattern 3、Pattern 4、Pattern 5、およびPattern 6)がランダムで出力されるようにする。こうすることによって、VL+10α/4に対応する階調表示レベルを実現でき、かつ、各サブフレームドット期間に各画素に偏りなく階調電圧が書き込まれることになり、フレーム周波数を上げなくてもフリッカの発生を減少させることができる。

【0084】

次に、図16を参照する。図16には、外部から入力される4ビットデジタルビデオデータのアドレスが(1011)の場合に、各サブフレームドット期間(1st Tsfd、2nd Tsfd、3rd Tsfd、または4th Tsfd)に各画素(画素TFT)に供給されるD/A変換回路によって作成された階調電圧レベルが実線で、階調表示レベルが点線で示されている。

【0085】

デジタルビデオデータ時間階調処理回路は、外部から入力される4ビットデジタルビデオデータのアドレスが(1011)の時、2ビットのデジタルビデオデータ(アドレス(10)または(11))を作成しD/A変換回路へ出力する。D/A変換回路は、入力される2ビットのデジタルビデオデータを階調電圧に変換し、アクティブマトリクス型液晶表示装置のソースドライバに供給する。図16に示される、外部から入力される4ビットデジタルビデオデータのアドレスが(1011)の時、各サブフレームドット期間には、階調電圧レベルVL+2α(アドレス(10))が1回およびVL+3α(アドレス(11))が3回、順序をランダムにして対応する画素に供給される。図16から理解されるように、外部から入力される4ビットデジタルビデオデータのアドレスが(1011)の時、各サブフレームドット期間に各画素に供給される階調電圧レベルのパターンは、4通り(Pattern 1、Pattern 2、Pattern 3、およびPattern 4)であり何れの場合においても、階調表示レベルはVL+11α/4となる。

【0086】

外部から入力される4ビットデジタルビデオデータのアドレスが(1011)の時も、各サブフレームドット期間に各画素に供給される階調電圧レベルを、これら4通りのパターン(Pattern 1、Pattern 2、Pattern 3、およびPattern 4)がランダムで出力されるようにする。こうすることによって、VL+11α/4に対応する階調表示レベルを実現でき、かつ、各サブフレームドット期間に各画素に偏りなく階調電圧が書き込まれることになり、フレーム周波数を上げなくてもフリッカの発生を減少させることができる。

【0087】

次に図17を参照する。図17には、外部から入力される4ビットデジタルビデオデータのアドレスが(1100)〜(1111)の場合に、各サブフレームドット期間(1st Tsfd、2nd Tsfd、3rd Tsfd、または4th Tsfd)に各画素(画素TFT)に供給されるD/A変換回路によって作成された階調電圧レベルが実線で、階調表示レベルが点線で示されている。

【0088】

デジタルビデオデータ時間階調処理回路は、外部から入力される4ビットデジタルビデオデータを基に2ビットのデジタルビデオデータを作成する。外部から入力される4ビットデジタルビデオデータのアドレスが(1100)〜(1111)の時、デジタルビデオデータ時間階調処理回路は、2ビットのデジタルビデオデータ(アドレス(11))を作成しD/A変換回路へ出力する。D/A変換回路は、入力される2ビットのデジタルビデオデータを階調電圧に変換し、アクティブマトリクス型液晶表示装置のソースドライバに供給する。図17に示されるように、外部から入力される4ビットデジタルビデオデータのアドレスが(1100)〜(1111)の時、各サブフレームドット期間(1st Tsfd、2nd Tsfd、3rd Tsfd、および4th Tsfd)には、階調電圧レベルVL(アドレス(11))がそれぞれ対応する画素に供給される。図17に示されるうように、外部から入力される4ビットデジタルビデオデータのアドレスが(1100)〜(1111)の時、各サブフレームドット期間(1st Tsfd、2nd Tsfd、3rd Tsfd、および4th Tsfd)に供給される階調電圧レベルのパターンは、1通り(Pattern 1)のみである。よって、階調表示レベルはVL+3αとなる。

【0089】

ここで、図18および図19を参照する。図18および図19には、本実施例の液晶表示装置の駆動タイミングチャートが示されている。図18および図19には、画素P1,1、画素P1,2、画素P1,3、および画素Py,xが例にとって示されている。なお、図18および図19は時間的に連続したタイミングチャートであるが、図面の都合上、2図に分けて示されている。

【0090】

前述の様に、1フレーム期間(Tf)は、第1サブフレーム期間(1st Tsf)、第2サブフレーム期間(2nd Tsf)、第3サブフレーム期間(3rd Tsf)、および第4サブフレーム期間(4th Tsf)によって構成される。各サブフレーム期間の始まりには、水平帰線期間(Th)がある。

【0091】

第1サブフレーム期間(1st Tsf)においては、画素P1,1には、第1サブフレームドット期間(1st Tsfd)に画素P1,1に対応する2ビットのデジタルビデオデータがD/A変換回路によってアナログ階調電圧に変換され、画素P1,1に書き込まれる。

【0092】

次に、画素P1,2には、第1サブフレームドット期間(1st Tsfd)に画素P1,3に対応する2ビットのデジタルビデオデータがD/A変換回路によってアナログ階調電圧に変換され、画素P1,2に書き込まれる。

【0093】

このようにして、全ての画素画素P1,1〜画素Py,xに画像情報を有するアナログ階調電圧が順に書き込まれる。よって第1サブフレーム期間が終了する。

【0094】

そして、第1サブフレーム期間の経過後、第2サブフレーム期間が始まる。第2サブフレーム期間(2nd Tsf)においても、水平帰線期間Thの後、画素P1,1には、第2サブフレームドット期間(1st Tsfd)に画素P1,1に対応する2ビットのデジタルビデオデータがD/A変換回路によってアナログ階調電圧に変換され、画素P1,1に書き込まれる。次に、画素P1,2には、第1サブフレームドット期間(1st Tsfd)に画素P1,3に対応する2ビットのデジタルビデオデータがD/A変換回路によってアナログ階調電圧に変換され、画素P1,2に書き込まれる。

【0095】

このようにして、全ての画素画素P1,1〜画素Py,xに画像情報を有するアナログ階調電圧が順に書き込まれる。よって第2サブフレーム期間が終了する。

【0096】

第3サブフレーム期間(3rd Tsf)および第4サブフレーム期間(4th Tsf)においても同様の動作が行われる。

【0097】

このようにして、第1サブフレーム期間から第4サブフレーム期間が終了する。

【0098】

第1のフレーム期間終了後、第2のフレーム期間が始まる(図19)。本実施例では、フレーム期間ごとに液晶に印加される電界の向きが逆となるフレーム反転を行う。

【0099】

ここで、図20を参照する。図20は、ある画素(例えば、画素P1,1)の画素電極にサブフレーム期間ごとに書き込まれるアナログ階調電圧レベルと、フレーム期間における階調表示レベルとの関係を示した例である。

【0100】

始めに1フレーム期間目に着目する。1フレーム期間目には、外部から4ビットのデジタルデータのアドレスが(0110)のデジタルデータが供給されている。この1フレーム目には、上述の4ビットデジタルビデオデータのアドレスが(0110)の場合の、パターン2(Pattern 2)の出力がされている。第1のサブフレームドット期間(1st Tsfd)にはVL+2αの階調電圧が書き込まれ第1のサブフレーム期間(1st Tsf)中保持され、階調電圧VL+2αに対応した階調表示が行われる。第2サブフレームドット期間(2nd Tsfd)にはVL+αの階調電圧が書き込まれ、第2のサブフレーム期間(2nd Tsf)には階調電圧VL+αに対応した階調表示が行われる。第3のサブフレームドット期間(3rd Tsfd)にはVL+2αの階調電圧が書き込まれ、第3のサブフレーム期間(3rd Tsf)には階調電圧VL+2αに対応した階調表示が行われる。第4のサブフレームドット期間(1st Tsfd)にはVL+αの階調電圧が書き込まれ、第4のサブフレーム期間(4th Tsf)には階調電圧VL+αに対応した階調表示が行われる。よって、1フレーム目の階調表示レベルは、VL+6α/4の階調電圧レベルに対応した階調表示となる。

【0101】

次に2フレーム期間目に着目する。2フレーム期間目には、外部から4ビットのデジタルデータのアドレスが(0011)のデジタルデータが供給されている。この1フレーム目には、上述の4ビットデジタルビデオデータのアドレスが(0011)の場合の、パターン4(Pattern 4)の出力がされている。第1のサブフレームドット期間(1st Tsfd)にはVLの階調電圧が書き込まれ、第1のサブフレーム期間(1st Tsf)には階調電圧VLに対応した階調表示が行われる。第2サブフレームドット期間(2nd Tsfd)にはVL+αの階調電圧が書き込まれ、第2のサブフレーム期間(2nd Tsf)には階調電圧VL+αに対応した階調表示が行われる。第3のサブフレームドット期間(3rd Tsfd)にはVL+αの階調電圧が書き込まれ、第3のサブフレーム期間(3rd Tsf)には階調電圧VL+αに対応した階調表示が行われる。第4のサブフレームドット期間(1st Tsfd)にはVL+αの階調電圧が書き込まれ、第4のサブフレーム期間(4th Tsf)には階調電圧VL+αに対応した階調表示が行われる。よって、1フレーム目の階調表示レベルは、VL+3α/4の階調電圧レベルに対応した階調表示となる。

【0102】

なお、図20に示す表示例は、あくまでも一例であり、入力される4ビットデジタルデータに対応したどのパターンの出力がされるかは、ランダムに決定される。

【0103】

なお、本実施例においては、4階調の電圧レベルを実現するために、電圧レベルVHと電圧レベルVLとの間をほぼ等電圧レベルに分割し、その等電圧をステップをαとしたが、電圧レベルVHと電圧レベルVLとの間を等電圧レベルに分割せず任意に設定した場合でも、本発明を適用することもできる。

【0104】

また、本実施例においては、D/A変換回路に電圧レベルVHと電圧レベルVLとを入力し階調電圧レベルを実現できるようにしたが、3以上の電圧レベルの入力によって階調電圧レベルを実現するようにすることもできる。

【0105】

また、本実施例においては、外部から入力される4ビットデジタルビデオデータに基づいて2ビットの電圧階調の為のデジタルビデオデータを作成し、4ビットのデジタルビデオデータのうち2ビットの階調情報は、時間階調によって表現されるようにした。ここで、一般に、外部からmビットのデジタルビデオデータが時間階調処理回路によって、階調電圧の為のnビットデジタルビデオデータに変換され、(m−n)ビットの階調情報は、時間階調によって表現される場合を考える。なお、m、nは共に2以上の整数であり、m>nとする。

【0106】

この場合、フレーム期間(Tf)とサブフレーム期間(Tsf)との関係は、

Tf=2m-n・Tsf

となり、(2m−(2m-n−1))通りの階調表示を行うことができる。

【0107】

なお、本実施例においては、m=4かつn=2の場合を例にとって説明したが、これらの場合に限定されるわけではないことは、言うまでもない。m=12かつn=4であってもよい。また、m=8かつn=2であってもよい。また、m=8かつn=6であってもよい。また、m=10かつn=2であってもよいし、その他の場合であってもよい。

【0108】

なお、階調電圧レベルは、液晶に実際に印加される電圧であるとしてもよい。つまり、階調電圧レベルは、対向電極に印加されるVCOMを考慮にいれた電圧レベルであるとしてもよい。

【0109】

(実施例2)

【0110】

本実施例においては、上記実施例1における本発明の液晶表示装置の構成において、サブフレームごとにフレーム反転駆動を行った場合について説明する。

【0111】

図21を参照する。図21には、本実施例の液晶表示装置の駆動タイミングチャートが示されている。図21は、画素P1,1、画素P2,1、画素P3,1、および画素Py,xが例にとって示されている。

【0112】

本実施例においても、前述の様に、1フレーム期間(Tf)は、第1サブフレーム期間(1st Tsf)、第2サブフレーム期間(2nd Tsf)、第3サブフレーム期間(3rd Tsf)、および第4サブフレーム期間(4th Tsf)によって構成される。各サブフレーム期間の始まりには、水平帰線期間Thがある。

【0113】

図21に示される様に、本実施例においては、サブフレーム期間毎に液晶に印加される電界の向きが逆になるサブフレーム反転方式によって表示を行うので、よりちらつきの少ない表示が可能となる。

【0114】

(実施例3)

【0115】

本実施例においては、mビットデジタルビデオデータが入力される液晶表示装置について説明する。図22を参照する。図22には、本実施例の液晶表示装置の概略構成図が示されている。液晶表示装置2001は、アクティブマトリクス基板2001−1および対向基板2001−2(図示せず)を有している。アクティブマトリクス基板2001−1には、ソースドライバ2001−1−1、ゲートドライバ2001−1−2ならびに2001−1−3、複数の画素TFTがマトリクス状に配置された画素部2001−1−4、デジタルビデオデータ時間階調処理回路2001−1−5、およびD/A変換回路2001−1−6を有している。また、対向基板2001−2は、対向電極2001−2−1(図示せず)を有している。

【0116】

本実施例においては、図22に示すように、画素部、ドライバ、デジタルビデオデータ時間階調処理回路およびD/A変換回路がアクティブマトリクス基板上に一体形成され、液晶表示装置が構成されている。

【0117】

本実施例の液晶表示装置の動作については、既述の例を参照することができる。

【0118】

(実施例4)

【0119】

本実施例においては、アナログビデオデータが入力される液晶表示装置について説明する。図23を参照する。図23には、本実施例の液晶表示装置の概略構成図が示されている。液晶表示装置2101は、アクティブマトリクス基板2101−1および対向基板2101−2(図示せず)を有している。アクティブマトリクス基板2101−1には、ソースドライバ2101−1−1、ゲートドライバ2101−1−2ならびに2101−1−3、複数の画素TFTがマトリクス状に配置された画素部2101−1−4、A/D変換回路2101−1−5、デジタルビデオデータ時間階調処理回路2101−1−6、およびD/A変換回路2101−1−7を有している。また、対向基板2101−2は、対向電極2101−2−1(図示せず)を有している。

【0120】

本実施例においては、図23に示すように、画素部、ドライバ、デジタルビデオデータ時間階調処理回路、D/A変換回路およびA/D変換回路がアクティブマトリクス基板上に一体形成され、液晶表示装置が構成されている。

【0121】

外部から入力されるアナログビデオデータは、A/D変換回路2101−1−5によってmビットデジタルビデオデータに変換される。

【0122】

本実施例の液晶表示装置の動作については、既述の例を参照することができる。

【0123】

(実施例5)

【0124】

本実施例では、本発明の液晶表示装置の作製方法の一例について説明する。ここでは、画素部とその周辺に設けられるドライバのTFTを同時に作製する方法について説明する。

【0125】

ここでは画素部の画素TFTと、画素部の周辺に設けられる駆動回路(ソースドライバ、ゲートドライバ、D/A変換回路、A/D変換回路、デジタルビデオデータ時間階調処理回路等)のTFTを同一基板上に作製する方法について工程に従って詳細に説明する。但し、説明を簡単にするために、駆動回路ではシフトレジスタ回路、バッファ回路、D/A変換回路などの基本回路であるCMOS回路と、nチャネル型TFTとを図示することにする。

【0126】

図24(A)において、基板6001には低アルカリガラス基板や石英基板を用いることができる。本実施例では低アルカリガラス基板を用いた。この場合、ガラス歪み点よりも10〜20℃程度低い温度であらかじめ熱処理しておいても良い。この基板6001のTFTを形成する表面には、基板6001からの不純物拡散を防ぐために、酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜などの下地膜6002を形成する。例えば、プラズマCVD法でSiH4、NH3、N2Oから作製される酸化窒化シリコン膜を100nm、同様にSiH4、N2Oから作製される酸化窒化シリコン膜を200nmの厚さに積層形成する。

【0127】

次に、10〜150nm(好ましくは30〜80nm)の厚さで非晶質構造を有する半導体膜6003aを、プラズマCVD法やスパッタ法などの公知の方法で形成する。本実施例では、プラズマCVD法で非晶質シリコン膜を55nmの厚さに形成した。非晶質構造を有する半導体膜としては、非晶質半導体膜や微結晶半導体膜があり、非晶質シリコンゲルマニウム膜などの非晶質構造を有する化合物半導体膜を適用しても良い。また、下地膜6002と非晶質シリコン膜6003aとは同じ成膜法で形成することが可能であるので、両者を連続形成しても良い。下地膜を形成した後、一旦大気雰囲気に晒さないことでその表面の汚染を防ぐことが可能となり、作製するTFTの特性バラツキやしきい値電圧の変動を低減させることができる。(図24(A))

【0128】

そして、公知の結晶化技術を使用して非晶質シリコン膜6003aから結晶質シリコン膜6003bを形成する。例えば、レーザー結晶化法や熱結晶化法(固相成長法)を適用すれば良いが、ここでは、特開平7−130652号公報で開示された技術に従って、触媒元素を用いる結晶化法で結晶質シリコン膜6003bを形成した。結晶化の工程に先立って、非晶質シリコン膜の含有水素量にもよるが、400〜500℃で1時間程度の熱処理を行い、含有水素量を5atom%以下にしてから結晶化させることが望ましい。非晶質シリコン膜を結晶化させると原子の再配列が起こり緻密化するので、作製される結晶質シリコン膜の厚さは当初の非晶質シリコン膜の厚さ(本実施例では55nm)よりも1〜15%程度減少した。(図24(B))

【0129】

そして、結晶質シリコン膜6003bを島状に分割して、島状半導体層6004〜6007を形成する。その後、プラズマCVD法またはスパッタ法により50〜100nmの厚さの酸化シリコン膜によるマスク層6008を形成する。(図24(C))

【0130】

そしてレジストマスク6009を設け、nチャネル型TFTを形成する島状半導体層6005〜6007の全面にしきい値電圧を制御する目的で1×1016〜5×1017atoms/cm3程度の濃度でp型を付与する不純物元素としてボロン(B)を添加した。ボロン(B)の添加はイオンドープ法で実施しても良いし、非晶質シリコン膜を成膜するときに同時に添加しておくこともできる。ここでのボロン(B)添加は必ずしも必要でないが、ボロン(B)を添加した半導体層6010〜6012はnチャネル型TFTのしきい値電圧を所定の範囲内に収めるために形成することが好ましかった。(図24(D))

【0131】

駆動回路のnチャネル型TFTのLDD領域を形成するために、n型を付与する不純物元素を島状半導体層6010、6011に選択的に添加する。そのため、あらかじめレジストマスク6013〜6016を形成した。n型を付与する不純物元素としては、リン(P)や砒素(As)を用いれば良く、ここではリン(P)を添加すべく、フォスフィン(PH3)を用いたイオンドープ法を適用した。形成された不純物領域6017、6018のリン(P)濃度は2×1016〜5×101 9atoms/cm3の範囲とすれば良い。本明細書中では、ここで形成された不純物領域6017〜6019に含まれるn型を付与する不純物元素の濃度を(n-)と表す。また、不純物領域6019は、画素マトリクス回路の保持容量を形成するための半導体層であり、この領域にも同じ濃度でリン(P)を添加した。(図25(A))

【0132】

次に、マスク層6008をフッ酸などにより除去して、図24(D)と図25(A)で添加した不純物元素を活性化させる工程を行う。活性化は、窒素雰囲気中で500〜600℃で1〜4時間の熱処理や、レーザー活性化の方法により行うことができる。また、両者を併用して行っても良い。本実施例では、レーザー活性化の方法を用い、KrFエキシマレーザー光(波長248nm)を用い、線状ビームを形成して、発振周波数5〜50Hz、エネルギー密度100〜500mJ/cm2として線状ビームのオーバーラップ割合を80〜98%として走査して、島状半導体層が形成された基板全面を処理した。尚、レーザー光の照射条件には何ら限定される事項はなく、実施者が適宣決定すれば良い。

【0133】

そして、ゲート絶縁膜6020をプラズマCVD法またはスパッタ法を用いて10〜150nmの厚さでシリコンを含む絶縁膜で形成する。例えば、120nmの厚さで酸化窒化シリコン膜を形成する。ゲート絶縁膜には、他のシリコンを含む絶縁膜を単層または積層構造として用いても良い。(図25(B))

【0134】

次に、ゲート電極を形成するために第1の導電層を成膜する。この第1の導電層は単層で形成しても良いが、必要に応じて二層あるいは三層といった積層構造としても良い。本実施例では、導電性の窒化物金属膜から成る導電層(A)6021と金属膜から成る導電層(B)6022とを積層させた。導電層(B)6022はタンタル(Ta)、チタン(Ti)、モリブデン(Mo)、タングステン(W)から選ばれた元素、または前記元素を主成分とする合金か、前記元素を組み合わせた合金膜(代表的にはMo−W合金膜、Mo−Ta合金膜)で形成すれば良く、導電層(A)6021は窒化タンタル(TaN)、窒化タングステン(WN)、窒化チタン(TiN)膜、窒化モリブデン(MoN)で形成する。また、導電層(A)6021は代替材料として、タングステンシリサイド、チタンシリサイド、モリブデンシリサイドを適用しても良い。導電層(B)は低抵抗化を図るために含有する不純物濃度を低減させると良く、特に酸素濃度に関しては30ppm以下とすると良かった。例えば、タングステン(W)は酸素濃度を30ppm以下とすることで20μΩcm以下の比抵抗値を実現することができた。

【0135】

導電層(A)6021は10〜50nm(好ましくは20〜30nm)とし、導電層(B)6022は100〜400nm(好ましくは250〜350nm)とすれば良い。本実施例では、導電層(A)6021に30nmの厚さの窒化タンタル膜を、導電層(B)6022には350nmのTa膜を用い、いずれもスパッタ法で形成した。このスパッタ法による成膜では、スパッタ用のガスのArに適量のXeやKrを加えておくと、形成する膜の内部応力を緩和して膜の剥離を防止することができる。尚、図示しないが、導電層(A)6021の下に2〜20nm程度の厚さでリン(P)をドープしたシリコン膜を形成しておくことは有効である。これにより、その上に形成される導電膜の密着性向上と酸化防止を図ると同時に、導電層(A)または導電層(B)が微量に含有するアルカリ金属元素がゲート絶縁膜6020に拡散するのを防ぐことができる。(図25(C))

【0136】

次に、レジストマスク6023〜6027を形成し、導電層(A)6021と導電層(B)6022とを一括でエッチングしてゲート電極6028〜6031と容量配線6032を形成する。ゲート電極6028〜6031と容量配線6032は、導電層(A)から成る6028a〜6032aと、導電層(B)から成る6028b〜6032bとが一体として形成されている。この時、駆動回路に形成するゲート電極6029、6030は不純物領域6017、6018の一部と、ゲート絶縁膜6020を介して重なるように形成する。(図25(D))

【0137】

次いで、駆動回路のpチャネル型TFTのソース領域およびドレイン領域を形成するために、p型を付与する不純物元素を添加する工程を行う。ここでは、ゲート電極6028をマスクとして、自己整合的に不純物領域を形成する。このとき、nチャネル型TFTが形成される領域はレジストマスク6033で被覆しておく。そして、ジボラン(B2H6)を用いたイオンドープ法で不純物領域6034を形成した。この領域のボロン(B)濃度は3×1020〜3×1021atoms/cm3となるようにする。本明細書中では、ここで形成された不純物領域6034に含まれるp型を付与する不純物元素の濃度を(p+)と表す。(図26(A))

【0138】

次に、nチャネル型TFTにおいて、ソース領域またはドレイン領域として機能する不純物領域の形成を行った。レジストのマスク6035〜6037を形成し、n型を付与する不純物元素が添加して不純物領域6038〜6042を形成した。これは、フォスフィン(PH3)を用いたイオンドープ法で行い、この領域のリン(P)濃度を1×1020〜1×1021atoms/cm3とした。本明細書中では、ここで形成された不純物領域6038〜6042に含まれるn型を付与する不純物元素の濃度を(n+)と表す。(図26(B))

【0139】

不純物領域6038〜6042には、既に前工程で添加されたリン(P)またはボロン(B)が含まれているが、それに比して十分に高い濃度でリン(P)が添加されるので、前工程で添加されたリン(P)またはボロン(B)の影響は考えなくても良い。また、不純物領域6038に添加されたリン(P)濃度は図26(A)で添加されたボロン(B)濃度の1/2〜1/3なのでp型の導電性が確保され、TFTの特性に何ら影響を与えることはなかった。

【0140】

そして、画素マトリクス回路のnチャネル型TFTのLDD領域を形成するためのn型を付与する不純物添加の工程を行った。ここではゲート電極6031をマスクとして自己整合的にn型を付与する不純物元素をイオンドープ法で添加した。添加するリン(P)の濃度は1×1016〜5×101 8atoms/cm3であり、図25(A)および図26(A)と図26(B)で添加する不純物元素の濃度よりも低濃度で添加することで、実質的には不純物領域6043、6044のみが形成される。本明細書中では、この不純物領域6043、6044に含まれるn型を付与する不純物元素の濃度を(n--)と表す。(図26(C))

【0141】

その後、それぞれの濃度で添加されたn型またはp型を付与する不純物元素を活性化するために熱処理工程を行う。この工程はファーネスアニール法、レーザーアニール法、またはラピッドサーマルアニール法(RTA法)で行うことができる。ここではファーネスアニール法で活性化工程を行った。熱処理は酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒素雰囲気中で400〜800℃、代表的には500〜600℃で行うものであり、本実施例では550℃で4時間の熱処理を行った。また、基板6001に石英基板のような耐熱性を有するものを使用した場合には、800℃で1時間の熱処理としても良く、不純物元素の活性化と、該不純物元素が添加された不純物領域とチャネル形成領域との接合を良好に形成することができた。

【0142】

この熱処理において、ゲート電極6028〜6031と容量配線6032形成する金属膜6028b〜6032bは、表面から5〜80nmの厚さで導電層(C)6028c〜6032cが形成される。例えば、導電層(B)6028b〜6032bがタングステン(W)の場合には窒化タングステン(WN)が形成され、タンタル(Ta)の場合には窒化タンタル(TaN)を形成することができる。また、導電層(C)6028c〜6032cは、窒素またはアンモニアなどを用いた窒素を含むプラズマ雰囲気にゲート電極6028〜6031および容量配線6032を晒しても同様に形成することができる。さらに、3〜100%の水素を含む雰囲気中で、300〜450℃で1〜12時間の熱処理を行い、島状半導体層を水素化する工程を行った。この工程は熱的に励起された水素により半導体層のダングリングボンドを終端する工程である。水素化の他の手段として、プラズマ水素化(プラズマにより励起された水素を用いる)を行っても良い。

【0143】

島状半導体層が、非晶質シリコン膜から触媒元素を用いる結晶化の方法で作製された場合、島状半導体層中には微量の触媒元素が残留した。勿論、そのような状態でもTFTを完成させることが可能であるが、残留する触媒元素を少なくともチャネル形成領域から除去する方がより好ましかった。この触媒元素を除去する手段の一つにリン(P)によるゲッタリング作用を利用する手段があった。ゲッタリングに必要なリン(P)の濃度は図26(B)で形成した不純物領域(n+)と同程度であり、ここで実施される活性化工程の熱処理により、nチャネル型TFTおよびpチャネル型TFTのチャネル形成領域から触媒元素をゲッタリングをすることができた。(図26(D))

【0144】

活性化および水素化の工程が終了したら、ゲート配線とする第2の導電膜を形成する。この第2の導電膜は低抵抗材料であるアルミニウム(Al)や銅(Cu)を主成分とする導電層(D)と、にチタン(Ti)やタンタル(Ta)、タングステン(W)、モリブデン(Mo)から成る導電層(E)とで形成すると良い。本実施例では、チタン(Ti)を0.1〜2重量%含むアルミニウム(Al)膜を導電層(D)6045とし、チタン(Ti)膜を導電層(E)6046として形成した。導電層(D)6045は100〜400nm(好ましくは250〜350nm)とすれば良く、導電層(E)6046は50〜200(好ましくは100〜150nm)で形成すれば良い。(図27(A))

【0145】

そして、ゲート電極に接続するゲート配線を形成するために導電層(E)6046と導電層(D)6045とをエッチング処理して、ゲート配線6047、6048と容量配線6049を形成した。エッチング処理は最初にSiCl4とCl2とBCl3との混合ガスを用いたドライエッチング法で導電層(E)の表面から導電層(D)の途中まで除去し、その後リン酸系のエッチング溶液によるウエットエッチングで導電層(D)を除去することにより、下地との選択加工性を保ってゲート配線を形成することができた。

【0146】

第1の層間絶縁膜6050は500〜1500nmの厚さで酸化シリコン膜または酸化窒化シリコン膜で形成され、その後、それぞれの島状半導体層に形成されたソース領域またはドレイン領域に達するコンタクトホールを形成し、ソース配線6051〜6054と、ドレイン配線6055〜6058を形成する。図示していないが、本実施例ではこの電極を、Ti膜を100nm、Tiを含むアルミニウム膜300nm、Ti膜150nmをスパッタ法で連続して形成した3層構造の積層膜とした。

【0147】

次に、パッシベーション膜6059として、窒化シリコン膜、酸化シリコン膜、または窒化酸化シリコン膜を50〜500nm(代表的には100〜300nm)の厚さで形成する。この状態で水素化処理を行うとTFTの特性向上に対して好ましい結果が得られた。例えば、3〜100%の水素を含む雰囲気中で、300〜450℃で1〜12時間の熱処理を行うと良く、あるいはプラズマ水素化法を用いても同様の効果が得られた。なお、ここで後に画素電極とドレイン配線を接続するためのコンタクトホールを形成する位置において、パッシベーション膜6059に開口部を形成しておいても良い。(図27(C))

【0148】

その後、有機樹脂からなる第2の層間絶縁膜6060を1.0〜1.5μmの厚さに形成する。有機樹脂としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、BCB(ベンゾシクロブテン)等を使用することができる。ここでは、基板に塗布後、熱重合するタイプのポリイミドを用い、300℃で焼成して形成した。そして、第2の層間絶縁膜6060にドレイン配線6058に達するコンタクトホールを形成し、画素電極6061、6062を形成する。画素電極は、透過型液晶表示装置とする場合には透明導電膜を用いれば良く、反射型の液晶表示装置とする場合には金属膜を用いれば良い。本実施例では透過型の液晶表示装置とするために、酸化インジウム・スズ(ITO)膜を100nmの厚さにスパッタ法で形成した。(図28)

【0149】

こうして同一基板上に、駆動回路のTFTと画素部の画素TFTとを有した基板を完成させることができた。駆動回路にはpチャネル型TFT6101、第1のnチャネル型TFT6102、第2のnチャネル型TFT6103、画素部には画素TFT6104、保持容量6105が形成した。本明細書では便宜上このような基板をアクティブマトリクス基板と呼ぶ。

【0150】

駆動回路のpチャネル型TFT6101には、島状半導体層6004にチャネル形成領域6106、ソース領域6107a、6107b、ドレイン領域6108a,6108bを有している。第1のnチャネル型TFT6102には、島状半導体層6005にチャネル形成領域6109、ゲート電極6029と重なるLDD領域6110(以降、このようなLDD領域をLovと記す)、ソース領域6111、ドレイン領域6112を有している。このLov領域のチャネル長方向の長さは0.5〜3.0μm、好ましくは1.0〜1.5μmとした。第2のnチャネル型TFT6103には、島状半導体層6006にチャネル形成領域6113、LDD領域6114,6115、ソース領域6116、ドレイン領域6117を有している。このLDD領域はLov領域とゲート電極6030と重ならないLDD領域(以降、このようなLDD領域をLoffと記す)とが形成され、このLoff領域のチャネル長方向の長さは0.3〜2.0μm、好ましくは0.5〜1.5μmである。画素TFT6104には、島状半導体層6007にチャネル形成領域6118、6119、Loff領域6120〜6123、ソースまたはドレイン領域6124〜6126を有している。Loff領域のチャネル長方向の長さは0.5〜3.0μm、好ましくは1.5〜2.5μmである。さらに、容量配線6032、6049と、ゲート絶縁膜と同じ材料から成る絶縁膜と、画素TFT6104のドレイン領域6126に接続し、n型を付与する不純物元素が添加された半導体層6127とから保持容量6105が形成されている。図28では画素TFT6104をダブルゲート構造としたが、シングルゲート構造でも良いし、複数のゲート電極を設けたマルチゲート構造としても差し支えない。

【0151】

以上の様に本実施例では、画素TFTおよび駆動回路が要求する仕様に応じて各回路を構成するTFTの構造を最適化し、半導体装置の動作性能と信頼性を向上させることを可能とすることができる。さらにゲート電極を耐熱性を有する導電性材料で形成することによりLDD領域やソース領域およびドレイン領域の活性化を容易とし、ゲート配線低抵抗材料で形成することにより、配線抵抗を十分低減できる。従って、画素部(画面サイズ)が4インチクラス以上の表示装置にも適用することができる。

【0152】

(実施例6)

【0153】

上述の本発明の液晶表示装置は、図29に示すような3板式のプロジェクタに用いることができる。

【0154】

図29において、2401は白色光源、2402〜2405はダイクロイックミラー、2406ならびに2407は全反射ミラー、2408〜2410は本発明の液晶表示装置、および2411は投影レンズである。

【0155】

(実施例7)

【0156】

また、上述の本発明の液晶表示装置は、図30に示すような3板式のプロジェクタに用いることもできる。

【0157】

図30において、2501は白色光源、2502ならびに2503はダイクロイックミラー、2504〜2506は全反射ミラー、2507〜2509は本発明の液晶表示装置、および2510はダイクロイックプリズム、および2511は投影レンズである。

【0158】

(実施例8)

【0159】

また、上述の本発明の液晶表示装置は、図31に示すような単板式のプロジェクタに用いることもできる。

【0160】

図31において、2601はランプとリフレクターとから成る白色光源である。2602、2603、および2604は、ダイクロイックミラーであり、それぞれ青、赤、緑の波長領域の光を選択的に反射する。2605はマイクロレンズアレイであり、複数のマイクロレンズによって構成されている。2606は本発明の液晶表示装置である。2607は集光レンズ、2608は投射レンズ、2609はスクリーンである。

【0161】

(実施例9)

【0162】

上記実施例6〜8のプロジェクターは、その投影方法によってリアプロジェクターとフロントプロジェクターとがある。

【0163】

図32(A)はフロント型プロジェクタ−であり、本体10001、本発明の液晶表示装置10002、光源10003、光学系10004、スクリーン10005で構成されている。なお、図32(A)には、液晶表示装置を1つ組み込んだフロントプロジェクターが示されているが、液晶表示装置を3個(R、G、Bの光にそれぞれ対応させる)組み込んことによって、より高解像度・高精細のフロント型プロジェクタを実現することができる。

【0164】

図32(B)はリア型プロジェクターであり、10006は本体、10007は液晶表示装置であり、10008は光源であり、10009はリフレクター、10010はスクリーンである。なお、図32(B)には、アクティブマトリクス型半導体表示装置を3個(R、G、Bの光にそれぞれ対応させる)組み込んだリア型プロジェクタが示されている。

【0165】

(実施例10)

【0166】

本実施例では、本発明のアクティブマトリクス型表示装置をゴーグル型ディスプレイに用いた例を示す。

【0167】

図33を参照する。2801はゴーグル型ディスプレイ本体である。2802−Rならびに2802−Lは本発明のアクティブマトリクス型表示装置であり、2803−Rならびに2803−LはLEDバックライトであり、2804−Rならびに2804−Lは光学素子である。

【0168】

(実施例11)

本発明のアクティブマトリクス型表示装置を表示媒体として組み込んだ電子機器を例に挙げる。

【0169】

その様な電子機器としては、ビデオカメラ、デジタルカメラ、プロジェクター(リア型またはフロント型)、ヘッドマウントディスプレイ(ゴーグル型ディスプレイ)、カーナビゲーション、パーソナルコンピュータ、携帯情報端末(モバイルコンピュータ、携帯電話または電子書籍等)などが挙げられる。それらの一例を図34に示す。

【0170】

図34(A)はパーソナルコンピュータであり、本体11001、画像入力部11002、本発明のアクティブマトリクス型表示装置11003、キーボード11004で構成される。

【0171】

図34(B)はビデオカメラであり、本体12001、本発明のアクティブマトリクス型表示装置12002、音声入力部12003、操作スイッチ12004、バッテリー12005、受像部12006で構成される。

【0172】

図34(C)はモバイルコンピュータ(モービルコンピュータ)であり、本体13001、カメラ部13002、受像部13003、操作スイッチ13004、本発明のアクティブマトリクス型表示装置13005で構成される。

【0173】

図34(D)はデジタルカメラであり、本体14001、本発明のアクティブマトリクス型表示装置14002、接眼部14003、操作スイッチ14004、受像部(図示しない)で構成される。

【0174】

図34(E)は携帯書籍(電子書籍)であり、本体15001、本発明のアクティブマトリクス型表示装置15002、15003、記憶媒体15004、操作スイッチ15005、アンテナ15006で構成される。

【0175】

図34(F)は映像やプログラムを記録した記録媒体(以下、記録媒体と呼ぶ)を用いるプレーヤーであり、本体16001、アクティブマトリクス型表示装置16002、スピーカ部16003、記録媒体16004、操作スイッチ16005で構成される。なお、この装置は記録媒体としてDVD(Digtal Versatile Disc)、CD等を用い、音楽鑑賞や映画鑑賞やゲームやインターネットを行うことができる。

【0176】

以上の様に、本発明のアクティブマトリクス型表示装置の適用範囲は極めて広く、あらゆる分野の電子機器に適用することが可能である。

【0177】

(実施例12)

【0178】

上述の本発明の液晶表示装置にはTN液晶以外にも様々な液晶を用いることが可能である。例えば、1998, SID, "Characteristics and Driving Scheme of Polymer-Stabilized Monostable FLCD Exhibiting Fast Response Time and High Contrast Ratio with Gray-Scale Capability" by H. Furue et al.や、1997, SID DIGEST, 841, "A Full-Color Thresholdless Antiferroelectric LCD Exhibiting Wide Viewing Angle with Fast Response Time" by T. Yoshida et al.や、1996, J. Mater. Chem. 6(4), 671-673, "Thresholdless antiferroelectricity in liquid crystals and its application to displays" by S. Inui et al.や、米国特許第5594569 号に開示された液晶を用いることが可能である。

【0179】

ある温度域において反強誘電相を示す液晶を反強誘電性液晶という。反強誘電性液晶を有する混合液晶には、電場に対して透過率が連続的に変化する電気光学応答特性を示す、無しきい値反強誘電性混合液晶と呼ばれるものがある。この無しきい値反強誘電性混合液晶は、いわゆるV字型の電気光学応答特性を示すものがあり、その駆動電圧が約±2.5V程度(セル厚約1μm〜2μm)のものも見出されている。

【0180】

ここで、いわゆるV字型の電気光学応答を示す無しきい値反強誘電性混合液晶の印加電圧に対する光透過率の特性を示す例を図35に示す。図35に示すグラフの縦軸は透過率(任意単位)、横軸は印加電圧である。なお、液晶表示装置の入射側の偏光板の透過軸は、液晶表示装置のラビング方向にほぼ一致する無しきい値反強誘電性混合液晶のスメクティック層の法線方向とほぼ平行に設定されている。また、出射側の偏光板の透過軸は、入射側の偏光板の透過軸に対してほぼ直角(クロスニコル)に設定されている。

【0181】

図35に示されるように、このような無しきい値反強誘電性混合液晶を用いると、低電圧駆動かつ階調表示が可能となることがわかる。

【0182】

このような低電圧駆動の無しきい値反強誘電性混合液晶をアナログドライバを有する液晶表示装置に用いた場合には、画像信号のサンプリング回路の電源電圧を、例えば、5V〜8V程度に抑えることが可能となる。よって、ドライバの動作電源電圧を下げることができ、液晶表示装置の低消費電力化および高信頼性が実現できる。

【0183】

よって、このような低電圧駆動の無しきい値反強誘電性混合液晶を用いることは、比較的LDD領域(低濃度不純物領域)の幅が小さなTFT(例えば、0nm〜500nmまたは0nm〜200nm)を用いる場合においても有効である。

【0184】

また、一般に、無しきい値反強誘電性混合液晶は自発分極が大きく、液晶自体の誘電率が高い。このため、無しきい値反強誘電性混合液晶を液晶表示装置に用いる場合には、画素に比較的大きな保持容量が必要となってくる。よって、自発分極が小さな無しきい値反強誘電性混合液晶を用いるのが好ましい。

【0185】

なお、このような無しきい値反強誘電性混合液晶を用いることによって低電圧駆動が実現されるので、液晶表示装置の低消費電力が実現される。

【0186】

なお、図35に示すような電気光学特性を有する液晶であれば、いかなるものも本発明の液晶表示装置の表示媒体として用いることができる。

【0187】

(実施例13)

【0188】

本実施例では、本発明の表示装置に用いられる駆動方法をEL(エレクトロルミネッセンス)表示装置に用いた例について説明する。

【0189】

図36(A)は本実施例のEL表示装置の上面図である。図36(A)において、24010は基板、24011は画素部、24012はソース側駆動回路、24013はゲート側駆動回路であり、それぞれの駆動回路は配線24014〜24016を経てFPC24017に至り、外部機器へと接続される。

【0190】

図36(B)は本実施例のEL表示装置の断面構造である。このとき、少なくとも画素部、好ましくは駆動回路及び画素部を囲むようにしてカバー材26000、シール材27000、密封材(第2のシール材)27001が設けられている。

【0191】

また、基板24010、下地膜24021の上に駆動回路用TFT(但し、ここではnチャネル型TFTとpチャネル型TFTを組み合わせたCMOS回路を図示している。)24022及び画素部用TFT24023(但し、ここではEL素子への電流を制御するTFTだけ図示している。)が形成されている。

【0192】

駆動回路用TFT24022、画素部用TFT24023が完成したら、樹脂材料でなる層間絶縁膜(平坦化膜)24026の上に画素部用TFT24023のドレインと電気的に接続する透明導電膜でなる画素電極24027を形成する。透明導電膜としては、酸化インジウムと酸化スズとの化合物(ITOと呼ばれる)または酸化インジウムと酸化亜鉛との化合物を用いることができる。そして、画素電極24027を形成したら、絶縁膜24028を形成し、画素電極24027上に開口部を形成する。

【0193】

次に、EL層24029を形成する。EL層24029は公知のEL材料(正孔注入層、正孔輸送層、発光層、電子輸送層または電子注入層)を自由に組み合わせて積層構造または単層構造とすれば良い。どのような構造とするかは公知の技術を用いれば良い。また、EL材料には低分子系材料と高分子系(ポリマー系)材料がある。低分子系材料を用いる場合は蒸着法を用いるが、高分子系材料を用いる場合には、スピンコート法、印刷法またはインクジェット法等の簡易な方法を用いることが可能である。

【0194】

本実施例では、シャドーマスクを用いて蒸着法によりEL層を形成する。シャドーマスクを用いて画素毎に波長の異なる発光が可能な発光層(赤色発光層、緑色発光層及び青色発光層)を形成することで、カラー表示が可能となる。その他にも、色変換層(CCM)とカラーフィルターを組み合わせた方式、白色発光層とカラーフィルターを組み合わせた方式があるがいずれの方法を用いても良い。

勿論、単色発光のEL表示装置とすることもできる。

【0195】

EL層24029を形成したら、その上に陰極24030を形成する。陰極24030とEL層24029の界面に存在する水分や酸素は極力排除しておくことが望ましい。従って、真空中でEL層24029と陰極24030を連続成膜するか、EL層24029を不活性雰囲気で形成し、大気解放しないで陰極24030を形成するといった工夫が必要である。本実施例ではマルチチャンバー方式(クラスターツール方式)の成膜装置を用いることで上述のような成膜を可能とする。

【0196】

なお、本実施例では陰極24030として、LiF(フッ化リチウム)膜とAl(アルミニウム)膜の積層構造を用いる。具体的にはEL層24029上に蒸着法で1nm厚のLiF(フッ化リチウム)膜を形成し、その上に300nm厚のアルミニウム膜を形成する。勿論、公知の陰極材料であるMgAg電極を用いても良い。そして陰極24030は24031で示される領域において配線24016に接続される。配線24016は陰極24030に所定の電圧を与えるための電源供給線であり、導電性ペースト材料24032を介してFPC24017に接続される。

【0197】

24031に示された領域において陰極24030と配線24016とを電気的に接続するために、層間絶縁膜24026及び絶縁膜24028にコンタクトホールを形成する必要がある。これらは層間絶縁膜24026のエッチング時(画素電極用コンタクトホールの形成時)や絶縁膜24028のエッチング時(EL層形成前の開口部の形成時)に形成しておけば良い。また、絶縁膜24028をエッチングする際に、層間絶縁膜24026まで一括でエッチングしても良い。この場合、層間絶縁膜24026と絶縁膜24028が同じ樹脂材料であれば、コンタクトホールの形状を良好なものとすることができる。

【0198】

このようにして形成されたEL素子の表面を覆って、パッシベーション膜26003、充填材26004、カバー材26000が形成される。

【0199】

さらに、EL素子部を囲むようにして、カバー材26000と基板24010の内側にシール材27000が設けられ、さらにシール材27000の外側には密封材(第2のシール材)27001が形成される。

【0200】

このとき、この充填材26004は、カバー材26000を接着するための接着剤としても機能する。充填材26004としては、PVC(ポリビニルクロライド)、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いることができる。この充填材26004の内部に乾燥剤を設けておくと、吸湿効果を保持できるので好ましい。

【0201】

また、充填材26004の中にスペーサーを含有させてもよい。このとき、スペーサーをBaOなどからなる粒状物質とし、スペーサー自体に吸湿性をもたせてもよい。

【0202】

スペーサーを設けた場合、パッシベーション膜26003はスペーサー圧を緩和することができる。また、パッシベーション膜とは別に、スペーサー圧を緩和する樹脂膜などを設けてもよい。

【0203】

また、カバー材26000としては、ガラス板、アルミニウム板、ステンレス板、FRP(Fiberglass−Reinforced Plastics)板、PVF(ポリビニルフルオライド)フィルム、マイラーフィルム、ポリエステルフィルムまたはアクリルフィルムを用いることができる。なお、充填材26004としてPVBやEVAを用いる場合、数十μmのアルミニウムホイルをPVFフィルムやマイラーフィルムで挟んだ構造のシートを用いることが好ましい。

【0204】

但し、EL素子からの発光方向(光の放射方向)によっては、カバー材26000が透光性を有する必要がある。

【0205】

また、配線24016はシール材27000および密封材27001と基板24010との隙間を通ってFPC24017に電気的に接続される。なお、ここでは配線24016について説明したが、他の配線24014、24015も同様にしてシール材27000および密封材27001の下を通ってFPC24017に電気的に接続される。

【0206】

(実施例14)

本実施例では、実施例13とは異なる形態のEL表示装置を作製した例について、図37(A)、37(B)を用いて説明する。図36(A)、36(B)と同じ番号のものは同じ部分を指しているので説明は省略する。

【0207】

図37(A)は本実施例のEL表示装置の上面図であり、図37(A)をA-A'で切断した断面図を図37(B)に示す。

【0208】

実施例13に従って、EL素子の表面を覆ってパッシベーション膜26003までを形成する。

【0209】

さらに、EL素子を覆うようにして充填材6004を設ける。この充填材26004は、カバー材26000を接着するための接着剤としても機能する。充填材26004としては、PVC(ポリビニルクロライド)、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いることができる。この充填材26004の内部に乾燥剤を設けておくと、吸湿効果を保持できるので好ましい。

【0210】

また、充填材26004の中にスペーサーを含有させてもよい。このとき、スペーサーをBaOなどからなる粒状物質とし、スペーサー自体に吸湿性をもたせてもよい。

【0211】

スペーサーを設けた場合、パッシベーション膜26003はスペーサー圧を緩和することができる。また、パッシベーション膜とは別に、スペーサー圧を緩和する樹脂膜などを設けてもよい。

【0212】

また、カバー材26000としては、ガラス板、アルミニウム板、ステンレス板、FRP(Fiberglass−Reinforced Plastics)板、PVF(ポリビニルフルオライド)フィルム、マイラーフィルム、ポリエステルフィルムまたはアクリルフィルムを用いることができる。なお、充填材26004としてPVBやEVAを用いる場合、数十μmのアルミニウムホイルをPVFフィルムやマイラーフィルムで挟んだ構造のシートを用いることが好ましい。

【0213】

但し、EL素子からの発光方向(光の放射方向)によっては、カバー材6000が透光性を有する必要がある。

【0214】

次に、充填材26004を用いてカバー材26000を接着した後、充填材26004の側面(露呈面)を覆うようにフレーム材26001を取り付ける。フレーム材26001はシール材(接着剤として機能する)26002によって接着される。このとき、シール材26002としては、光硬化性樹脂を用いるのが好ましいが、EL層の耐熱性が許せば熱硬化性樹脂を用いても良い。なお、シール材26002はできるだけ水分や酸素を透過しない材料であることが望ましい。また、シール材26002の内部に乾燥剤を添加してあっても良い。

【0215】

また、配線24016はシール材26002と基板24010との隙間を通ってFPC24017に電気的に接続される。なお、ここでは配線24016について説明したが、他の配線24014、24015も同様にしてシール材26002の下を通ってFPC24017に電気的に接続される。

【0216】

(実施例15)

本実形態では、EL表示パネルにおける画素部のさらに詳細な断面構造を図38に、上面構造を図39(A)に、回路図を図39(B)に示す。図38、図39(A)及び図39(B)では共通の符号を用いるので互いに参照すれば良い。

【0217】

図38において、基板23001上に設けられたスイッチング用TFT23002は実施例4のTFT構造を用いてもよいし、公知のTFTの構造を用いてもよい。本実施例ではダブルゲート構造としているが、構造及び作製プロセスに大きな違いはないので説明は省略する。但し、ダブルゲート構造とすることで実質的に二つのTFTが直列された構造となり、オフ電流値を低減することができるという利点がある。なお、本実施例ではダブルゲート構造としているが、シングルゲート構造でも構わないし、トリプルゲート構造やそれ以上のゲート本数を持つマルチゲート構造でも構わない。

【0218】

また、電流制御用TFT23003はNTFTを用いて形成される。このとき、スイッチング用TFT23002のドレイン配線23035は配線23036によって電流制御用TFTのゲート電極23037に電気的に接続されている。また、23038で示される配線は、スイッチング用TFT23002のゲート電極23039a、23039bを電気的に接続するゲート配線である。

【0219】

電流制御用TFTはEL素子を流れる電流量を制御するための素子であるため、多くの電流が流れ、熱による劣化やホットキャリアによる劣化の危険性が高い素子でもある。そのため、電流制御用TFTのドレイン側に、ゲート絶縁膜を介してゲート電極に重なるようにLDD領域を設ける本発明の構造は極めて有効である。

【0220】

また、本実施例では電流制御用TFT23003をシングルゲート構造で図示しているが、複数のTFTを直列につなげたマルチゲート構造としても良い。さらに、複数のTFTを並列につなげて実質的にチャネル形成領域を複数に分割し、熱の放射を高い効率で行えるようにした構造としても良い。このような構造は熱による劣化対策として有効である。

【0221】

また、図39(A)に示すように、電流制御用TFT23003のゲート電極23037となる配線は23004で示される領域で、電流制御用TFT23003のドレイン配線23040と絶縁膜を介して重なる。このとき、23004で示される領域ではコンデンサが形成される。このコンデンサ23004は電流制御用TFT23003のゲートにかかる電圧を保持するためのコンデンサとして機能する。なお、ドレイン配線23040は電流供給線(電源線)23006に接続され、常に一定の電圧が加えられている。

【0222】

スイッチング用TFT23002及び電流制御用TFT23003の上には第1パッシベーション膜23041が設けられ、その上に樹脂絶縁膜でなる平坦化膜23042が形成される。平坦化膜23042を用いてTFTによる段差を平坦化することは非常に重要である。後に形成されるEL層は非常に薄いため、段差が存在することによって発光不良を起こす場合がある。従って、EL層をできるだけ平坦面に形成しうるように画素電極を形成する前に平坦化しておくことが望ましい。

【0223】

また、23043は反射性の高い導電膜でなる画素電極(EL素子の陰極)であり、電流制御用TFT23003のドレインに電気的に接続される。画素電極23043としてはアルミニウム合金膜、銅合金膜または銀合金膜など低抵抗な導電膜またはそれらの積層膜を用いることが好ましい。勿論、他の導電膜との積層構造としても良い。

【0224】

また、絶縁膜(好ましくは樹脂)で形成されたバンク23044a、23044bにより形成された溝(画素に相当する)の中に発光層23045が形成される。なお、ここでは一画素しか図示していないが、R(赤)、G(緑)、B(青)の各色に対応した発光層を作り分けても良い。発光層とする有機EL材料としてはπ共役ポリマー系材料を用いる。代表的なポリマー系材料としては、ポリパラフェニレンビニレン(PPV)系、ポリビニルカルバゾール(PVK)系、ポリフルオレン系などが挙げられる。

【0225】

なお、PPV系有機EL材料としては様々な型のものがあるが、例えば「H. Shenk,H.Becker,O.Gelsen,E.Kluge,W.Kreuder,and H.Spreitzer,“Polymers for Light Emitting Diodes”,Euro Display,Proceedings,1999,p.33-37」や特開平10−92576号公報に記載されたような材料を用いれば良い。

【0226】

具体的な発光層としては、赤色に発光する発光層にはシアノポリフェニレンビニレン、緑色に発光する発光層にはポリフェニレンビニレン、青色に発光する発光層にはポリフェニレンビニレン若しくはポリアルキルフェニレンを用いれば良い。膜厚は30〜150nm(好ましくは40〜100nm)とすれば良い。

【0227】

但し、以上の例は発光層として用いることのできる有機EL材料の一例であって、これに限定する必要はまったくない。発光層、電荷輸送層または電荷注入層を自由に組み合わせてEL層(発光及びそのためのキャリアの移動を行わせるための層)を形成すれば良い。

【0228】

例えば、本実施例ではポリマー系材料を発光層として用いる例を示したが、低分子系有機EL材料を用いても良い。また、電荷輸送層や電荷注入層として炭化珪素等の無機材料を用いることも可能である。これらの有機EL材料や無機材料は公知の材料を用いることができる。

【0229】

本実施例では発光層23045の上にPEDOT(ポリチオフェン)またはPAni(ポリアニリン)でなる正孔注入層23046を設けた積層構造のEL層としている。そして、正孔注入層23046の上には透明導電膜でなる陽極23047が設けられる。本実施例の場合、発光層23045で生成された光は上面側に向かって(TFTの上方に向かって)放射されるため、陽極は透光性でなければならない。透明導電膜としては酸化インジウムと酸化スズとの化合物や酸化インジウムと酸化亜鉛との化合物を用いることができるが、耐熱性の低い発光層や正孔注入層を形成した後で形成するため、可能な限り低温で成膜できるものが好ましい。

【0230】

陽極23047まで形成された時点でEL素子23005が完成する。なお、ここでいうEL素子23005は、画素電極(陰極)23043、発光層23045、正孔注入層23046及び陽極23047で形成されたコンデンサを指す。図39(A)に示すように画素電極23043は画素の面積にほぼ一致するため、画素全体がEL素子として機能する。従って、発光の利用効率が非常に高く、明るい画像表示が可能となる。

【0231】

ところで、本実施例では、陽極23047の上にさらに第2パッシベーション膜23048を設けている。第2パッシベーション膜23048としては窒化珪素膜または窒化酸化珪素膜が好ましい。この目的は、外部とEL素子とを遮断することであり、有機EL材料の酸化による劣化を防ぐ意味と、有機EL材料からの脱ガスを抑える意味との両方を併せ持つ。これによりEL表示装置の信頼性が高められる。

【0232】

以上のように本実施例のEL表示パネルは図38のような構造の画素からなる画素部を有し、オフ電流値の十分に低いスイッチング用TFTと、ホットキャリア注入に強い電流制御用TFTとを有する。従って、高い信頼性を有し、且つ、良好な画像表示が可能なEL表示パネルが得られる。

【0233】

(実施例16)

本実施例では、実施例15に示した画素部において、EL素子23005の構造を反転させた構造について説明する。説明には図40を用いる。なお、図38の構造と異なる点はEL素子の部分と電流制御用TFTだけであるので、その他の説明は省略することとする。

【0234】

図40において、電流制御用TFT23103はPTFTを用いて形成される。

【0235】

本実施例では、画素電極(陽極)23050として透明導電膜を用いる。具体的には酸化インジウムと酸化亜鉛との化合物でなる導電膜を用いる。勿論、酸化インジウムと酸化スズとの化合物でなる導電膜を用いても良い。

【0236】

そして、絶縁膜でなるバンク23051a、23051bが形成された後、溶液塗布によりポリビニルカルバゾールでなる発光層23052が形成される。その上にはカリウムアセチルアセトネートでなる電子注入層23053、アルミニウム合金でなる陰極23054が形成される。この場合、陰極23054がパッシベーション膜としても機能する。こうしてEL素子23101が形成される。

【0237】

本実施例の場合、発光層23052で発生した光は、矢印で示されるようにTFTが形成された基板の方に向かって放射される。

【0238】

(実施例17)

本実施例では、図39(B)に示した回路図とは異なる構造の画素とした場合の例について図41(A)〜(C)に示す。なお、本実施例において、23201はスイッチング用TFT23202のソース配線、23203はスイッチング用TFT23202のゲート配線、23204は電流制御用TFT、23205はコンデンサ、23206、23208は電流供給線、23207はEL素子とする。

【0239】

図41(A)は、二つの画素間で電流供給線23206を共通とした場合の例である。即ち、二つの画素が電流供給線23206を中心に線対称となるように形成されている点に特徴がある。この場合、電源供給線の本数を減らすことができるため、画素部をさらに高精細化することができる。

【0240】

また、図41(B)は、電流供給線23208をゲート配線23203と平行に設けた場合の例である。なお、図41(B)では電流供給線23208とゲート配線23203とが重ならないように設けた構造となっているが、両者が異なる層に形成される配線であれば、絶縁膜を介して重なるように設けることもできる。この場合、電源供給線23208とゲート配線23203とで専有面積を共有させることができるため、画素部をさらに高精細化することができる。

【0241】

また、図41(C)は、図41(B)の構造と同様に電流供給線23208をゲート配線23203と平行に設け、さらに、二つの画素を電流供給線23208を中心に線対称となるように形成する点に特徴がある。また、電流供給線23208をゲート配線23203のいずれか一方と重なるように設けることも有効である。この場合、電源供給線の本数を減らすことができるため、画素部をさらに高精細化することができる。

【0242】

(実施例18)

実施例17に示した図39(A)、図39(B)では電流制御用TFT23003のゲートにかかる電圧を保持するためにコンデンサ23004を設ける構造としているが、コンデンサ23004を省略することも可能である。実施例11の場合、電流制御用TFT23003として、ゲート絶縁膜を介してゲート電極に重なるように設けられたLDD領域を有しているTFTを用いている。この重なり合った領域には一般的にゲート容量と呼ばれる寄生容量が形成されるが、本実施例ではこの寄生容量をコンデンサ23004の代わりとして積極的に用いる点に特徴がある。

【0243】

この寄生容量のキャパシタンスは、上記ゲート電極とLDD領域とが重なり合った面積によって変化するため、その重なり合った領域に含まれるLDD領域の長さによって決まる。

【0244】

また、実施例14に示した図41(A),(B),(C)の構造においても同様に、コンデンサ23205を省略することは可能である。

【発明の効果】

【0245】

本発明の表示装置においては、電圧階調と時間階調とによって階調表示を行うことによって多階調の表示が実現される。また、各サブフレームドット期間に各画素に偏りなく階調電圧が書き込まれることになり、フレーム周波数を上げなくてもフリッカの発生を減少させることができる。

【図面の簡単な説明】

【図1】 本発明の表示装置の概略構成図である。

【図2】 本発明の液晶表示装置のある実施例の概略構成図である。

【図3】 本発明の液晶表示装置のある実施例の画素部、ソースドライバおよびゲートドライバの回路構成図である。

【図4】 本発明の液晶表示装置のある実施例の階調表示レベルを示す図である。

【図5】 本発明の液晶表示装置のある実施例における、画素に出力される階調電圧レベルおよび階調表示レベルを示したタイミングチャートである。

【図6】 本発明の液晶表示装置のある実施例における、画素に出力される階調電圧レベルおよび階調表示レベルを示したタイミングチャートである。

【図7】 本発明の液晶表示装置のある実施例における、画素に出力される階調電圧レベルおよび階調表示レベルを示したタイミングチャートである。

【図8】 本発明の液晶表示装置のある実施例における、画素に出力される階調電圧レベルおよび階調表示レベルを示したタイミングチャートである。

【図9】 本発明の液晶表示装置のある実施例における、画素に出力される階調電圧レベルおよび階調表示レベルを示したタイミングチャートである。

【図10】 本発明の液晶表示装置のある実施例における、画素に出力される階調電圧レベルおよび階調表示レベルを示したタイミングチャートである。

【図11】 本発明の液晶表示装置のある実施例における、画素に出力される階調電圧レベルおよび階調表示レベルを示したタイミングチャートである。

【図12】 本発明の液晶表示装置のある実施例における、画素に出力される階調電圧レベルおよび階調表示レベルを示したタイミングチャートである。

【図13】 本発明の液晶表示装置のある実施例における、画素に出力される階調電圧レベルおよび階調表示レベルを示したタイミングチャートである。

【図14】 本発明の液晶表示装置のある実施例における、画素に出力される階調電圧レベルおよび階調表示レベルを示したタイミングチャートである。

【図15】 本発明の液晶表示装置のある実施例における、画素に出力される階調電圧レベルおよび階調表示レベルを示したタイミングチャートである。

【図16】 本発明の液晶表示装置のある実施例における、画素に出力される階調電圧レベルおよび階調表示レベルを示したタイミングチャートである。

【図17】 本発明の液晶表示装置のある実施例における、画素に出力される階調電圧レベルおよび階調表示レベルを示したタイミングチャートである。

【図18】 本発明の液晶表示装置のある実施例の駆動タイミングチャートを示す図である。

【図19】 本発明の液晶表示装置のある実施例の駆動タイミングチャートを示す図である。

【図20】 本発明の液晶表示装置のある実施例の駆動タイミングチャートを示す図である。

【図21】 本発明の液晶表示装置のある実施例の駆動タイミングチャートを示す図である。

【図22】 本発明の液晶表示装置のある実施例の概略構成図である。

【図23】 本発明の液晶表示装置のある実施例の概略構成図である。

【図24】 本発明の液晶表示装置の作製工程例を示す図である。

【図25】 本発明の液晶表示装置の作製工程例を示す図である。

【図26】 本発明の液晶表示装置の作製工程例を示す図である。

【図27】 本発明の液晶表示装置の作製工程例を示す図である。

【図28】 本発明の液晶表示装置の作製工程例を示す図である。

【図29】 本発明の液晶表示装置を用いた3板式プロジェクタの概略構成

図である。

【図30】 本発明の液晶表示装置を用いた3板式プロジェクタの概略構成図である。

【図31】 本発明の液晶表示装置を用いた単板式プロジェクタの概略構成図である。

【図32】 本発明の液晶表示装置を用いたフロントプロジェクタおよびリアプロジェクタの概略構成図である。

【図33】 本発明のアクティブマトリクス型表示装置を用いたゴーグル型ディスプレイの概略構成図である。

【図34】 本発明のアクティブマトリクス型表示装置を用いた電子機器の例である。

【図35】 反強誘電性混合液晶のV字型の電気光学特性を示すグラフである。

【図36】 実施例13のEL表示装置の構成を示す図である。

【図37】 実施例14のEL表示装置の構成を示す図である。

【図38】 実施例15のEL表示装置の画素部の構成を示す断面図である。

【図39】 実施例16のEL表示装置の画素部の構成を示す上面図及び回路図である。

【図40】 実施例17のEL表示装置の画素部の構成を示す断面図である。

【図41】 実施例18のEL表示装置の画素部の構成を示す回路図である。

【符号の説明】

101 液晶パネル

101−1 アクティブマトリクス基板

101−2 対向基板

101−1−1 ソースドライバ

101−1−2 ゲートドライバ

101−1−3 ゲートドライバ

101−1−4 画素部

102 デジタルビデオデータ時間階調処理回路

103 D/A変換回路

Claims (4)

- 複数の画素TFTがマトリクス状に配置された画素部と、

前記複数の画素TFTを駆動するソースドライバおよびゲートドライバと、

外部から入力されるmビットデジタルビデオデータをnビットデジタルビデオデータに変換する処理回路と(m、nは共に2以上の整数、m>n)、

前記nビットデジタルビデオデータをアナログビデオデータに変換し、前記ソースドライバへ出力するD/A変換回路と、を有する表示装置であって、

前記処理回路は、前記D/A変換回路へ前記nビットデジタルビデオデータをランダムな順序で出力し、

前記nビットデジタルビデオデータによって形成されるサブフレームによって1フレームの映像を形成し、

前記nビットデジタルビデオデータは電圧階調による階調表示に用いられ、且つ、前記mビットデジタルビデオデータのうち(m−n)ビットデジタルビデオデータは時間階調による階調表示に用いられることを特徴とする表示装置。 - 処理回路と、D/A変換回路と、ソースドライバと、画素部と、を有する表示装置であって、

前記処理回路へmビットデジタルビデオデータを入力し、

前記処理回路により前記mビットデジタルビデオデータに基づいてnビットデジタルビデオデータを作成し(m、nは共に2以上の整数、m>n)、

前記処理回路から前記D/A変換回路へ前記nビットデジタルビデオデータをランダムな順序で出力し、

前記D/A変換回路により前記nビットデジタルビデオデータをアナログビデオデータに変換し、

前記D/A変換回路から前記ソースドライバへ前記アナログビデオデータを出力し、

前記ソースドライバから前記画素部へ前記アナログビデオデータを供給し、

前記nビットデジタルビデオデータを電圧階調による階調表示に用い、且つ、前記mビットデジタルビデオデータのうち(m−n)ビットデジタルビデオデータを時間階調による階調表示に用いることを特徴とする表示装置。 - 請求項1又は請求項2において、

前記nビットデジタルビデオデータはシリアルであることを特徴とする表示装置。 - 請求項1乃至請求項3のいずれか一において、

点順次駆動が行われることを特徴とする表示装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000132761A JP4588163B2 (ja) | 1999-05-07 | 2000-05-01 | 表示装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP12774599 | 1999-05-07 | ||

| JP11-127745 | 1999-05-07 | ||

| JP2000132761A JP4588163B2 (ja) | 1999-05-07 | 2000-05-01 | 表示装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001027891A JP2001027891A (ja) | 2001-01-30 |

| JP2001027891A5 JP2001027891A5 (ja) | 2007-06-14 |

| JP4588163B2 true JP4588163B2 (ja) | 2010-11-24 |

Family

ID=26463628

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000132761A Expired - Fee Related JP4588163B2 (ja) | 1999-05-07 | 2000-05-01 | 表示装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4588163B2 (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI221268B (en) | 2001-09-07 | 2004-09-21 | Semiconductor Energy Lab | Light emitting device and method of driving the same |

| JP2008052289A (ja) * | 2001-09-07 | 2008-03-06 | Semiconductor Energy Lab Co Ltd | 発光装置及び電子機器 |

| US7330162B2 (en) | 2002-02-28 | 2008-02-12 | Semiconductor Energy Laboratory Co., Ltd. | Method of driving a light emitting device and electronic equipment |

| US6911781B2 (en) | 2002-04-23 | 2005-06-28 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device and production system of the same |

| JP4526279B2 (ja) * | 2003-05-27 | 2010-08-18 | 三菱電機株式会社 | 画像表示装置および画像表示方法 |

| US8159512B2 (en) * | 2005-05-27 | 2012-04-17 | Chimei Innolux Corporation | Method of driving a display |

| JP2020064159A (ja) * | 2018-10-16 | 2020-04-23 | 株式会社ジャパンディスプレイ | 表示装置 |

-

2000

- 2000-05-01 JP JP2000132761A patent/JP4588163B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001027891A (ja) | 2001-01-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5409581B2 (ja) | 半導体装置の作製方法 | |

| JP4338855B2 (ja) | D/a変換回路およびアクティブマトリクス型表示装置 | |

| JP6276355B2 (ja) | 表示装置、表示モジュール及び電子機器 | |

| US9412309B2 (en) | Image display device and driving method thereof | |

| US6753854B1 (en) | Display device | |

| US6686858B2 (en) | D/A conversion circuit and semiconductor device | |

| JP5088986B2 (ja) | 表示装置 | |

| US6573952B1 (en) | Goggle type display device | |

| JP2010239148A (ja) | 半導体装置 | |

| JP4646351B2 (ja) | 表示装置 | |

| US6590581B1 (en) | Display device | |

| JP4789305B2 (ja) | 表示装置 | |

| JP4588163B2 (ja) | 表示装置 | |

| JP4700190B2 (ja) | 画像表示装置およびその駆動方法 | |

| JP4801239B2 (ja) | 液晶表示装置 | |

| JP4637320B2 (ja) | ゴーグル型表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070423 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070423 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100628 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100706 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100819 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100907 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100908 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4588163 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130917 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130917 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |