JP4540753B2 - グラフィックオブジェクトを画像チャンクにレンダリングして、画像層を表示画像に組み合わせる方法及びシステム - Google Patents

グラフィックオブジェクトを画像チャンクにレンダリングして、画像層を表示画像に組み合わせる方法及びシステム Download PDFInfo

- Publication number

- JP4540753B2 JP4540753B2 JP50860497A JP50860497A JP4540753B2 JP 4540753 B2 JP4540753 B2 JP 4540753B2 JP 50860497 A JP50860497 A JP 50860497A JP 50860497 A JP50860497 A JP 50860497A JP 4540753 B2 JP4540753 B2 JP 4540753B2

- Authority

- JP

- Japan

- Prior art keywords

- pixel

- data

- image

- gsprite

- chunks

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06T—IMAGE DATA PROCESSING OR GENERATION, IN GENERAL

- G06T15/00—3D [Three Dimensional] image rendering

- G06T15/04—Texture mapping

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06T—IMAGE DATA PROCESSING OR GENERATION, IN GENERAL

- G06T11/00—2D [Two Dimensional] image generation

- G06T11/40—Filling a planar surface by adding surface attributes, e.g. colour or texture

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06T—IMAGE DATA PROCESSING OR GENERATION, IN GENERAL

- G06T15/00—3D [Three Dimensional] image rendering

- G06T15/005—General purpose rendering architectures

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Computer Graphics (AREA)

- Image Generation (AREA)

- Controls And Circuits For Display Device (AREA)

- Processing Or Creating Images (AREA)

Description

本発明は、包括的にはグラフィックスレンダリングに関し、特に、改良された、グラフィックオブジェクトをレンダリングする方法及びシステムに関する。

【背景技術】

【0002】

近代生活のあらゆる分野にコンピュータが普及するにつれて、視覚情報を用いてマン・マシン・インターフェイスを改善しようという要求が増している。グラフィック・ソフト及びハードウェアの進歩は、すでにマン・マシン・インターフェイスを急速に改善してきた。例えば、デスクトップ・コンピュータ用のウィンドウ環境のようなインタラクティブ・グラフィックスは、コンピュータの使い勝手とユーザとの相互作用を大きく改善し、今日では当たり前のことになっている。ハードウェアのコストパフォーマンスが改善するにつれて、コンピュータ上で作成されたグラフィックスやアニメの使用がさらに浸透してきている。残念ながら、真にインタラクティブな、リアルな効果を生み出そうとすると、そのコストのために、応用に限界がある。従って、より低いコストで、さらにインタラクティブで、リアルな効果を与えることのできる新しい画像処理技術やアーキテクチャに対しては需要がある。

【0003】

画像処理法の分類法には各種あるが、よくある方法の1つは、画像を、それが表わしたいオブジェクトの次元で描出することである。例えば、あるグラフィックスシステムは、オブジェクトを二次元(例えば、x座標とy座標を持つ)で表わす。この場合は、そのグラフィックスは「二次元性」(2D)であるという。また、三次元(例えば、x、y、及び、z座標を持つ)で表わせば、その場合は、そのグラフィックスは、「三次元性」(3D)であるという。

【0004】

陰極線管(CRT)のような表示装置は、二次元性(2D)であり、コンピュータのグラフィックスシステムによって表示される画像は一般に2Dである。しかしながら、以下にさらに詳しく論ずるように、コンピュータが、三次元空間で画像化されたオブジェクトを表わすグラフィック・モデルを保持している場合、コンピュータは、その表示画像を変えて、3D空間において同じオブジェクトについて種々の遠近像を描くことができる。一方、2Dグラフィック画像は、表示の前に変換する(例えば、拡大・縮小、変換、回転)ことはできるが、コンピュータは、3D空間における種々の遠近像から、そのオブジェクトの画像表現を容易に描写することはできない。

【0005】

現代のコンピュータが、2Dグラフィックス、特に3Dグラフィックスを次第に効率的に扱うことができるようになったために、様々の応用分野が広がっており、同時に、コンピュータとユーザ間のインターフェイス(UI)に基本的な変化が生じている。3Dグラッフィクスの利用可能性は益々重要になってきている。即ち、生産品質のアニメ・フィルムの制作ツールを始め、家庭向きの低解像度のゲームやマルチメディア製品を含めた、娯楽関連性の応用分野が成長しているからである。3Dグラフィックスの関連する他分野について幾つか挙げるならば、教育、テレビ会議、ビデオ編集、インタラクティブ・ユーザ・インターフェイス、コンピュータ支援設計やコンピュータ支援製造(CAD/CAM)、科学・医学画像法、ビジネス応用、及び、電子出版がある。

【0006】

グラフィックス処理システムは、アプリケーション・モデル、アプリケーション・プログラム、グラフィックス・サブシステムを始め、コンピュータの通常のハードウェア、ソフトウェア部分、及び、付属品を含むと考えてよい。

アプリケーション・モデルとは、もちろん画像処理はモデルに基づくと仮定して、データ、即ち、表示されるオブジェクトを表わす。モデルは、オブジェクトの形を規定するプリミティブ、例えば、点、線やポリゴンを始め、オブジェクトの属性(例えば、カラー)に関する情報を含む。アプリケーション・プログラムは、アプリケーション・モデルへ入る入力、モデルから出て行く出力を制御し、アプリケーション・モデルと、グラフィックス・サブシステムとの間の変換手段として有効に機能する。最終的には、グラフィックス・サブシステムは、ユーザ入力をアプリケーション・モデルに送り、また、アプリケーション・モデルによって保持されるディテール情報に基づいて画像を生成する責任を負う。

【0007】

通常のグラフィックス処理システムは、物理的出力装置を備える。これが、画像の出力、即ち、表示を行なう。従来他の形態の表示装置も開発されてはきたが、今日優勢な技術は、ラスター・グラフィックスに依拠している。ラスター・グラフィックス装置は、一連の不連続な点、即ち、画像要素(即ち、画素)を含む。画素は、複数の列と行に構成されて、画像を生成する。CRTにおいては、この画素は、CRTのガラス・画面上に与えられた蛍光体アレイに対応する。このアレイの中の各蛍光体からの光の放射は、それぞれ独立に、このアレイを順々に「走査」する電子ビームによって制御される。このアレイの奇数・偶数列のインターリーブ走査も、例えば、テレビジョン環境では普通に見られる技法である。画面にマップされる画素値のアレイは、ビットマップ、又は、ピックスマップと呼ばれることが多い。

【0008】

ラスター・グラフィックス装置に関連する1つの問題は、たった1つの画像に対するビットマップでも、それを保存するのに必要なメモリが膨大になることである。例えば、1280×1024(即ち、画素行と画素列の数)の表示解像度を維持するのに、この装置は、ランダム・アクセス・メモリの3.75メガバイト(Mb)を必要とすることがある。この情報は、繰り返すが、単一画面の画像を表わすにすぎないものであり、フレームバッファと呼ばれる、コンピュータの表示記憶装置の一部に蓄えられる。

CRTのような従来のラスター・グラフィックス装置に関するもう1つの問題は、この装置から発せられる光が比較的速やかに減衰することである。そのため、画像の「フリッカ」を避けるためには、通常、60Hz以上もの表示速度で、「リフレッシュ」してやらなければならない(すなわち、ラスターの再走査)。このため、グラフィックス処理システムは、画像データを一定速度で供給するという厳しい要求をつきつけられることになる。2つのフレームバッファを用いてこの問題に対応しようとする幾つかのシステムがある。即ち、フレームバッファのうちの一方は、次の画像フレームに対応するピックスマップ情報で更新され、他方のバッファは、現在の画像フレームのピックスマップで画面を更新するのに用いられる。

【0009】

グラフィックス処理システムに対する要求は、情報の複雑さによってさらに悪化される。そのような情報は、アプリケーション・モデルによって保持されるオブジェクトからの画像をレンダリングするように、幾度も処理しなければならないからである。例えば、三次元サーフェイスモデルそれ自体が、複雑なタスクとなる。サーフェイスモデルは、アプリケーション・モデルによって実行され、ポリゴンメッシュ、パラメトリック曲面、又は、方形面が用いられる。平面ポリゴンのメッシュによって、曲面を表現できるが、レンダリング画像におけるその画像表現の「滑らかさ」は、表示面の解像度、及び、サーフェイスモデルに用いられた個々のポリゴンの数、の双方に依存する。ポリゴンメッシュに基づく複雑な面についての高解像度のモデル化に伴って、そのサーフェイスモデルの複雑な計算は、リソースを極端に集約させる。

【0010】

上に紹介したように、よりリアルな、よりインタラクティブな画像を生成したいという要求がある。「リアルタイム」という用語は、通常、インタラクティブで、リアルな画像処理システムを云う場合に用いられる。「リアルタイム」装置においては、ユーザは、ある場面内のオブジェクトの連続的な動きを感ずることができなければならない。リアルタイム機能を持つビデオゲームにおいては、活動的キャラクタと視点は、ユーザの入力に対して極小の遅延で反応し、かつ、滑らかに動く必要がある。

【0011】

そのようなリアルタイム効果を実現するためには、画像レンダリングシステムは、十分に高速で新しい画像を生成し、それによって、ユーザが、ある場面内のオブジェクトの連続的な動きを感知できるほどになっていなければならない。新たな画像を表示するために計算される速度は、“計算”レート又は“計算フレーム”レートと称する。リアル効果を実現するために必要とされる計算レートは、オブジェクトが場面内でどのくらいの速さで動き回るか、及び、遠近像の視点がどのくらい急速に変化するか、によって変わる。通常のアプリケーションでは、リアルタイムグラフィックスシステムは、新画像を1秒当たり少なくとも12個計算し、それによって、連続する動きをシミュレートする一連の画像を生成する。高品質アニメ・アプリケーションでは、計算レートは、それよりもはるかに高くなければならない。

【0012】

リアルタイム装置に関するもう1つの問題は、伝達遅延である。伝達遅延とは、ユーザからの入力、即ち、場面内のあるキャラクタを動かすためのジョイスティックの動きに対して画像を計算して表示するのに必要な時間である。伝達遅延時間がユーザにとって目立つものであればあるほど、その程度に応じて、「リアルタイム」の相互作用性は損なわれる。理想的には、ユーザに、伝達遅延を気づかせてはならない。しかしながら、実際には、新しい入力に対して、ある場面のオブジェクトをレンダリングし表示画像を生成するのに必要な、幾らかの遅延が必ず存在する。リアルタイム相互作用性の改善は、データを切り落とすことなく達成できれば極めて望ましい。なぜなら、データの切り落としは、画像品質を損なうからである。

【0013】

始めに紹介したように、通常のグラフィックスシステムは、一般に、フレームバッファを備える。画像を生成するためには、グラフィックスシステムは、ある場面内のオブジェクトの全てをレンダリングし、得られた画像をこのフレームバッファに蓄える。次に、その装置は、レンダリングした画像データを表示装置に転送する。通常のグラフィックス・アーキテクチャであれば、フレームバッファの全内容は消去され、場面は再レンダリングされ、新たなフレーム画像を生成する。このタイプの装置では、各オブジェクトは、フレームごとに再レンダリングされる。なぜなら、フレームバッファは、フレームとフレームの間において空にされるためである。従って、各オブジェクトは、同じ速度で最新画像に更新される。これは、その画像が、その場面内で現実にどのような動きをしているか、又は、特定の用途に対して、それがどのような重要性持つか、には無関係に行なわれる。

【0014】

この通常のアーキテクチャは、高度にリアルで、インタラクティブなグラフィックスを生成しようとすると、幾つかの障害に直面する。第一に、ある特定のフレームに関して、ある場面内の各オブジェクトが全て同じ優先性で、同じ更新速度でレンダリングされる。従って、ほとんどディテールを持たず、動いてもいない背景のオブジェクトも、より早く動き、より細かい面ディテールを持つ前景のオブジェクトと同じ速度で再レンダリングされる。そのため、その処理や、その記憶のためのリソースが、背景オブジェクトの再レンダリングのために消費されることになる。しかも、これら背景オブジェクトは、フレームごとにほとんど大した変化をしないのに、である。

【0015】

この従来のアーキテクチャに関するもう1つの欠点は、場面における各オブジェクトが全て同じ解像度でレンダリングされるということである。その結果、この種のやり方で消費されるレンダリング・リソースは、そのオブジェクトが、場面全体に対して占める重要性ではなく、そのオブジェクトが占める画面面積の大きさに比例することになる。この問題を明らかにするには実例が役立つ。典型的なビデオゲームの場合、前景の、フレームごとに変化する活動的なキャラクタと、フレームごとにほとんど変化しない背景とがある。メモリ消費という点でのコストは、背景を生成する方が、活動的なキャラクタを生成するのに要するものよりもはるかに高い。なぜならば、背景の方が、画面上において、より大きな面積を占めるからである。画像データは、背景オブジェクトが占める各画素位置について保存されていなければならない。一方、より小さい、活動的なキャラクタの方は、画素データは、小型のキャラクタの占める画素に対してだけ、生成・保存される。その結果、背景は、場面内の重要性はずっと低いにも拘わらず、より大きなメモリを占有する。さらに、通常のアーキテクチャでは、背景全体が、各フレームに再レンダリングされ、貴重な処理用リソースを消費することになる。

フレームバッファ法の主要利点は、その出力装置の空間的解像度及び輝度解像度によってしか制限されないという条件で、任意の数のプリミティブオブジェクトを、物理的出力装置において、1つの任意の画像を構成するように用いることができることである。しかしながら、フレームバッファを用いるグラフィックシステムには幾つかの弱点がある。

【0016】

フレームバッファは、高価なメモリを大量(例えば、64−128Mb)に使う。標準のランダム・アクセス・メモリ(RAM)では、アクセス・スピードが遅いので、フレームバッファには適しない。例えば、1024×1024画面において、万の桁の画素を空にするには、各メモリ・サイクルが250ナノ秒を要すると仮定して、1/4秒かかる。従って、さらに高速の、さらに高価な、ビデオRAM(VRAM)、又は、ダイナミックRAM(DRAM)が、通常、フレームバッファには使われる。高性能装置ともなれば、2個の高価なフレームバッファを備えているものも多い。即ち、一方のフレームバッファは、現在の画面を表示するのに用いられ、他方は、次のフレームをレンダリングするのに用いられる。この大容量の専用メモリは、グラフィックスシステムのコストを大幅に増大させる。

【0017】

フレームバッファのメモリバンド幅がさらに問題である。各画素に蓄えられたテクスチャ(texture)、カラー、及び、深度の情報によって画像処理を実行するのをサポートするためには、30Hzで画像処理するとして、約1.7ギガバイト/秒のバンド幅が必要である。通常のDRAMは、僅か50Mb/秒しか持っていないので、所望のバンド幅が得られるように、フレームバッファを並行処理法で処理される多くのDRAMから構成させなければならない。

【0018】

リアルタイムな、インタラクティブな効果を実現するために、高品質グラフィックスシステムは、並行レンダリングエンジンを用いる。大きなフレームバッファに関わる問題に対処するために、従来、3つの基本的な並行ストラテジが開発されている。(1)レンダリング処理を複数のプロセッサに分配するパイプライン方式、(2)フレームバッファ・メモリを、各々独自のプロセッサを備えたメモリ・チップ・グループに分割する分割方式、及び、(3)フレームバッファ・メモリ・チップ上の処理回路と高密度メモリ回路とを組み合わせる組み合わせ方式、である。これらの方式は、大型フレームバッファを用いるグラフィックスシステムの処理法を改善したが、このシステムのコストをも飛躍的に増大させた。

【0019】

高価な並行処理法を用いてさえ、高度なアンチエイリアシング法をサポートするのは極めて難しい。アンチエイリアシング法というのは、連続面を不連続な画素で表わすことによって生じる、レンダリング画像におけるアーティファクトを減少させるための処理を云う。通常の、フレームバッファ・アーキテクチャでは、ある全体フレームにおける画素値は、任意の順序で計算される。従って、高度なアンチエイリアシングを実行するためには、アンチエイリアシングを始める前に、全フレームの画素データが生成されていなければならない。リアルタイム装置においては、画素データに対してアンチエイリアシングを実行するのに十分な時間が残されていない。処理を実行すれば必ず伝達遅延が更に加わることになる。更に、アンチエイリアシングは、画素フラグメントを保存するためのメモリをさらに必要とする。フレームバッファは、すでに大容量の高価なメモリを含んでいるから、アンチエイリアシングをサポートするために、更に専用メモリを加えることは、フレームバッファシステムを更に一段と高価なものにする。

【0020】

画像圧縮法も、画像処理にフレームバッファを用いるグラフィックスシステムにおいては、容易に使用できるものではない。フレームバッファによるグラフィックスシステムにおいて、処理速度を上げるために用いられる並行処理法は、圧縮法を導入しようという試みに幾つかの障害をもたらす。並行処理中、フレームバッファのどの部分に対しても、どの時点においても、ランダムにアクセスすることができる。一方、多くの画像圧縮法では、画像データは、圧縮処理中は変化しないことを要求する。それによって、後になって、画像データを復元できるようにするためである。

【0021】

フレームバッファ・アーキテクチャでは、高価なメモリや並行処理用ハードウェアは、常にあまり使用されずに放置されがちであった。なぜなら、ある任意の時点においては、フレームバッファ・メモリ、又は、並行処理ユニットのごく小部分のみが実際に使用されるにすぎないからである。従って、フレームバッファ・アーキテクチャは、大量の高価なメモリや処理用ハードウェアを備えているが、このハードウェアは十分に活用されていない。

【発明の開示】

【課題を解決するための手段】

【0022】

発明の概要

本発明は、幾何形状プリミティブのようなグラフィック・データをレンダリングして、表示画像を生成するための方法、及び、システムを提供する。本発明は、3Dグラフィックスをリアルタイムでレンダリングするのに特に好適であるが、他のグラフィックスや画像処理アプリケーションにも同様に適用できる。

グラフィックス・レンダリングシステムの1つの態様として、本システムは、グラッフィクオブジェクトを、gスプライト(gsprite)と呼ばれる画像層に別々にレンダリングし、次に、このgスプライトを合成して表示画像に仕立てあげる。さらに具体的に言うと、本システムは、gスプライトをオブジェクトに割り当て、次に、各オブジェクト(単数又は複数)を、対応するgスプライトにレンダリングする。gスプライトをレンダリングするために、本システムは、画像領域、即ち、gスプライトのチャンクを連続的にレンダリングする。本システムは、gスプライトを、チャンクに分割し、これらのチャンクの間でオブジェクトの大きさをソートし、次に、そのチャンクを連続的にレンダリングする。本システムは、gスプライトを合成して表示画像に仕立てあげる。

【0023】

本発明の一態様として、3Dオブジェクトの動きをシミュレートするように、及び、レンダリング・オーバーヘッドを低減させるように、gスプライトを変換させることができる。一実現例では、本システムは、ある場面内のオブジェクトを、別々のgスプライトにレンダリングする。あるオブジェクトをあるgスプライトにレンダリングした後、本システムは、そのオブジェクトを再レンダリングする代わりに、次のフレーム用のgスプライトを再利用する。これを実行するために、本システムは、gスプライトの表わす3Dオブジェクトの動きをシミュレートするアフィン変換式を算出する。本システムは、gスプライト上でアフィン変換を実行し、このgスプライトと他のgスプライトとを合成し、表示画像を生成する。

【0024】

本発明の別の態様として、本システムは、画像データのチャンクのために画素フラグメントを処理する手法にある。本システムは、チャンク用のプリミティブをラスタライズし、全体的に、又は、部分的にプリミティブでカバーされる画素位置用の画素データを生成する。あるプリミティブが、画素位置を部分的にカバーする場合、又は、半透明性である場合、本システムは、画素フラグメントを生成し、この画素フラグメントをフラグメントバッファに蓄える。あるプリミティブが、画素位置を完全にカバーし、かつ、不透明性である場合、本システムは、そのカラーデータを画素バッファに蓄える。本システムは、チャンク用のプリミティブをラスタライズし、次に、後処理ステップにおいてチャンク用の画素データを解析する。チャンクをレンダリングするアーキテクチャは、一方では、表示画像をリアルタイム速度で生成しながら、他方では、高度なアンチエイリアシングをこの画素データに対して実行することを可能にする。

【0025】

本発明の別の態様は、システム内のラスタライザが、生成された画素フラグメントを、フラグメントバッファに蓄えられたフラグメントとマージすることを試みることによって、フラグメント記録を保存できるようにする手法にある。蓄えられているフラグメントが、生成されたフラグメントの所定の深度及びカラー値の許容範囲内にあれば、本システムの画素エンジンは、これらフラグメントをマージする。画素エンジンは、これらのフラグメントを、一般化フラグメントと蓄えられたフラグメントのカバレッジデータ(例えば、カバレッジマスク)を組み合わせることによって部分的にマージする。マージされた画素フラグメントが、完全にカバーされ、且つ、不透明性であれば、画素エンジンは、その画素フラグメントを対応する画素バッファ・エントリに移し、フラグメント記録をフラグメントメモリから解放する。

【0026】

本発明のさらに別の態様は、サブシステムが、フラグメント記録のリストを解析する手法にある。一手法として、フラグメント解析サブシステムは、画素の各サブ画素位置に対して別々のカラー値及びアルファ値のアキュムレータを有し、各サブ画素について別々にカラー値を累積する。このサブシステムは、各サブ画素位置の累積されたカラー値を組み合わせるロジックを備え、最終的な出力画素を計算する。別の手法として、フラグメント解析サブシステムは、深度値でソートしたリストにおいて各フラグメント記録を解析する際に、共通の累積したアルファ値を持つサブ画素領域を追跡し続ける。リストの中の各フラグメントを解析した後、二つの手法で得られた出力は、ただ一組のカラー値(RGB)、及び、可能であれば、1つのアルファ値を有する出力画素となる。各画素位置に対し、例えば、RGBカラー値とアルファ値を含む解析した画素値を計算するために、フラグメント解析サブシステムは、画素バッファ内のカラー値を、関連するフラグメントリスト内のフラグメント記録におけるいずれかのフラグメントと組み合わせる。

【0027】

本発明のさらに別の態様は、異方性フィルタを実行する方法にある。一般にテクスチャ・マッピングにおいて、グラフィックス・レンダリングシステムは、幾何形状プリミティブの面に対して、テクスチャ・マップをマップする。この特定の方法においては、本システムはまず、ビュー空間内の画素位置の一点をどのようにテクスチャ・マップにマップさせるかを決定する。概念的には、本システムは、フィルタ・フットプリントをどのようにテクスチャ・マップにマップさせるかを決定する。透過マッピングにおいては、等方性フィルタ・フットプリントをテクスチャ・マップにマップさせることは、異方性の方向においては歪んだ形を与える。したがって、テクスチャを等方性フィルタでフィルタすることは、高品質の結果を得るには十分ではない。ある特定の実施例では、本システムは、フィルタ・フットプリントをテクスチャにマップさせる手法について、テクスチャ座標にマップされたビュー空間座標(例えば、画面座標)における画素位置に対する逆ヤコビアン行列を計算することによって決定する。

【0028】

次に、本システムは、マップされたフィルタ・フットプリントから異方性直線を決め、特に、この特定の一実施例においては、逆ヤコビアン行列によって異方性直線を決める。概念的には、異方性直線は、ビュー空間からテクスチャ空間へとマップされた点の座標を通過する直線であり、マップされたフィルタ・フットプリントの最大伸長方向に方向付けされる直線である。本システムは、異方性直線に沿ってフィルタリングを、テクスチャ・マップからのサンプル数値に対し、繰り返し適用する。この繰り返しフィルタリング・ステップによる出力は、最終のテクスチャ値を計算するために、フィルタリングされ、累積される。この手法に関しては、多くの変形がある。ある特定の実施例では、本システムは、異方性直線に沿ってトライ・リニア補間を実行する。次に、このトライ・リニアフィルタの出力は、画素位置に対する一組のカラー値を計算するように組み合わせられる。この態様においては、テクスチャフィルタ・エンジンは、例えば、三角形又は台形の形を持つ一次元フィルタを、異方性直線に沿ってトライ・リニア補間の出力に適用する。しかしながら、異方性直線に沿って適用されるフィルタに関しては、この方法を用いて多くの変形が可能である。

【0029】

本発明の別の態様は、ある画像が、フラグメントメモリからオーバフローした場合に、本システムは、その画像の小部分のレンダリングを実行する手法にある。一実施例では、本システムは、フラグメントメモリの使用状況を追跡し、フラグメント・エントリの数がある所定値に達した場合、画像領域を、小部分にサブ分割することができる。本システムは、画素フラグメントを生成しながら、フラグメントバッファへのエントリの数を追跡し続ける。エントリの数が所定値に達したならば、画像領域はさらに小領域にサブ分割され、このサブ分割した小領域について1回に1つずつレンダリングする。これによって、各サブ分割した小領域をレンダリングするのに十分なフラグメントメモリが確保される。本システムは、フラグメント・エントリの数が所定値に達したならば、小領域をさらに小さい画像領域にサブ分割することができる。従って、本システムは、フラグメントメモリの容量を越えることがないことを確実とするように、レンダリングされる画像領域をサブ分割することができる。これによって、上記の工夫を持たなかったならば、フラグメントメモリがオーバフローしてしまうような場合でも、本システムであれば、フラグメントを捨て去ることなく、より小さいフラグメントメモリを用いることができる。

【0030】

本発明の別の態様は、本システムは、高いレイテンシを有する環境において、テクスチャ・フェッチ動作を実行する手法にある。例えば、テクスチャ・マッピング、シャドウイング、マルチパス・レンダリングなどの動作においては、それら動作を実行するためにテクスチャデータをフェッチする際に、高いレイテンシを有する場合がしばしばある。このレイテンシは、メモリからデータを読み取る際に生ずる遅延、テクスチャデータを復元する際に生ずる遅延、又は、その双方によって生じるものである。

【0031】

一実施例においては、入力データ・ストリームの中の幾何形状プリミティブは、メモリから1ブロックのテクスチャデータをフェッチする際のレイテンシを十分吸収できる長さのプリミティブキューに蓄えられる。プリラスタライザが、このプリミティブキュー内の幾何形状プリミティブを、テクスチャブロック参照データにレンダリングし、これが、第2のキューに蓄えられる。この第2のキューで参照データとされたテクスチャブロックは、メモリからフェッチされ、テクスチャキャッシュに置かれる。ポストラスタライザは、このキュー内のプリミティブを1つずつラスタライズする。各プリミティブがラスタライズされるにつれて、現在のプリミティブ用の出力画素の計算のために、テクスチャデータが必要に応じてテクスチャキャッシュから取り出される。プリミティブは、ラスタライズされた後、このキューから除去される。

【0032】

別の一実施例では、プリミティブがラスタライズされることにより、得られた画素データは、テクスチャブロック・フェッチ・ユニットのレイテンシを吸収するのに十分な長さのキューに置かれる。ある特定の態様では、キューへのエントリは、画素アドレス、そのアドレスに対するカラーデータ、及び、テクスチャ要求を含む。テクスチャ要求はさらに、テクスチャ・マップ座標におけるテクスチャサンプルの中心点を含む。テクスチャ要求は、テクスチャブロック・アドレスに変換され、このテクスチャブロックは、フェッチされ、テクスチャキャッシュに置かれる。キューにおけるエントリは、キューから取り出され、この時点でテクスチャキャッシュにある関連するテクスチャデータは、出力画素を計算するのに用いられる。双方の実施例とも2組のテクスチャ要求を生成し、その内の一方の組は、他方の組のために遅延させられる。第1の組は、テクスチャデータを実際にフェッチし、可能であれば、それを復元するのに用いられ、第2の組は、テクスチャキャッシュからテクスチャデータを取り出すのに用いられる。

【0033】

本発明の、更なる特徴及び利点に関しては、下記の詳細な説明と図面を参照することによって明らかになる。

【実施例】

【0034】

装置概観

下記の詳細な説明の中で、画像処理システムに関して、幾つかの実施例を説明する。

この画像処理システムは、グラフィックスとビデオ処理の双方に対して、リアルタイム画像のレンダリングと生成をサポートする。本システムに用いられる新規のアーキテクチャと画像処理法によって、本システムは、従来のグラフィックスシステムに比べて、高度なリアルタイム3Dアニメーションを、はるかに低いコストで生成することができる。画像処理に加えて、本システムは、ビデオ編集アプリケーションのようなビデオ処理をサポートし、また、ビデオとグラッフィクスを組み合わせることもできる。例えば、本システムは、ビデオをグラッフィクオブジェクトに適用するように、又は、ビデオデータにグラッフィクオブジェクトを加えるように用いることもできる。

【0035】

本システムは、広範なインタラクティブ・アプリケーションをサポートする。本システムは、高度のリアルタイム・アニメーションをサポートできるために、ゲームや、教育用アプリケーション、及び、多くのインタラクティブ・アプリケーションに好適である。本システムは、3Dグラッフィクス、及び、グラフィックスとビデオの組み合わせを含む、高度なユーザ・インターフェイスをサポートする。従来の、パソコン用ウィンドウ環境の制限されたグラフィックス能力を改良し、本システムは、改良された、アプリケーション用3Dグラフィック・ユーザ・インターフェイスをサポートする。そのアプリケーションは、デスクトップ・コンピュータ上のオフィス・インフォメーション処理用のものから、セット・トップ・ボックスにおけるインタラクティブ・テレビジョン用アプリケーションのものまで広範に渡る。本システムは、メモリと処理時間を極めて効率よく利用するので、アプリケーションの性能や、ユーザ・アクションに対するユーザ・インターフェイスの反応性を不当に妨げることなく、際立った画像処理能力及び表示能力をもたらす。

【0036】

図1は、本画像処理システム100のブロック図である。本画像処理システムは、画像データ供給・保存装置102、画像前処理装置104、画像処理装置106、及び、レンダリングされた画像を直ちに表示したい場合の表示装置108からなる。本システムの各構成要素は、システム・インターフェイス110を通じて互いに接続されている。画像データ供給・保存装置102は、画像データを本システムに供給し、かつ、画像データ及び各種命令を保存する。画像前処理装置104は、画像データを操作して、レンダリングできるように調整する。前処理機能の例としては、オブジェクトを幾何形状モデルで規定すること、ライティング及びシャドウイング形成モデルを規定すること、オブジェクト位置を決めること、視点と光源の位置を決めること、幾何学処理、がある。

画像処理装置106は、画像をレンダリングし、表示装置108に表示されるべき表示画像を生成する。レンダリングとは、モデルから画像を生成する処理を指し、幾つか挙げるならば、幾何学処理(幾何学処理は、前処理機能でもあることに注意)、可視面の決定、走査変換、及び、ライティングなどの機能を含む。画像、又は、画像の一部をレンダリングした後、画像処理装置106は、レンダリングした画像データを、表示用の表示装置に転送する。

【0037】

以下に、画像処理システム100の幾つかの特質を、特定のハードウェア・ソフトウェア・アーキテクチャを参照しながら詳細に説明する。しかしながら、下記の画像処理システムは、各種のアーキテクチャに実装可能であることを理解しておくことが重要である。

【0038】

画像処理システム100は、本発明者にとって既知の従来の高品質3Dグラフィックスシステムに対して、はるかに優るコストパフォーマンス上の改善を達成した。コンピュータ・グラッフィクスにおける幾つかの進歩がこの改善の達成に貢献している。そのような進歩としては、合成画像層、画像圧縮、チャンキング、及び、マルチパス・レンダリングがある。ここに、これらの進歩を紹介し、以下にさらに詳細に、これらの進歩、並びに、他の進歩を説明する。

【0039】

合成画像層(gスプライト)

本システムにおいては、多数の、独立の画像層がビデオ速度で合成されて、出力ビデオ信号を生成する。この画像層を、一般化したスプライト(generalized sprite)、即ちgスプライト(gsprite)と呼ぶことにするが、これらは、独立にレンダリング及び操作することができる。本システムは、包括的には、場面における各非貫通性のオブジェクトに対して、個々のgスプライトを用いる。これによって、各オブジェクトを、独立に更新することができるので、オブジェクトの更新速度を、場面の優先性に応じて最適化することができる。例えば、はるか遠くの背景において動きあるオブジェクトについては、前景オブジェクトほどには、頻繁に、又は、それほど正確に更新する必要はない。

【0040】

gスプライトは任意のサイズ及び形状とすることができる。ある実現例では、方形のgスプライトを用いた。gスプライトの画素は、その画素に関連するカラー及びアルファ(不透明度)情報を持っており、そのために、多数のgスプライトが合成されて全体場面を構成できるようになっている。

gスプライトに対しては、拡大・縮小、回転、サブ画素位置づけ、アフィン・ワープのような小さな動きに対する変換を含む、幾つかの異なる動作をビデオ速度で実行することができる。従って、gスプライトの更新速度を変える一方で、gスプライトの変換(動きなど)は、完全なビデオ速度で実現可能なので、更新速度の保証を持たない従来の3Dグラフィックスシステムで達成できるレベルをはるかに越えた流動力学を実現する。

【0041】

多くの3D変換は、2D画像処理演算によってシミュレートすることができる。例えば、後退するオブジェクトは、gスプライトの大きさを拡大・縮小させることによってシミュレートすることができる。中間フレームに対しては、前にレンダリングした画像に対して2Dレンダリングを実行することによって、全体の処理要求を大きく低減させることができるので、3Dレンダリング性能を、最高品質の画質を生成することが要求される場合に用いることができる。これは、ディテール管理の時間レベルの態様である。

【0042】

gスプライトの拡大・縮小を用いることによって、ディテールの空間レベルも、場面の優先性に適合するように調整することができる。例えば、背景オブジェクト(曇った空など)は、小さなgスプライト(低解像度)へとレンダリングでき、次に、そのgスプライトを、表示用に適当な大きさに拡大・縮小する。高品質フィルタリング機能を用いることによって、典型的な低解像度アーティファクトも目立たなくなる。

通常の、3Dグラッフィクス・アプリケーション(特にインタラクティブ・ゲーム)は、高度のアニメーション速度を達成するために、ディテールの幾何学的レベルをトレードオフにしている。gスプライトによって、本システムは、付加的に、2つの場面パラメータを利用することができる。即ち、ディテールの時間レベルと、ディテールの空間レベルである。そして、それらによって、ユーザから見たときの性能を効果的に最適なものとする。あるオブジェクトの画像がレンダリングされる時の空間解像度は、そのレンダリングの際に画面解像度に適合させる必要はない。さらに、本システムは、アプリケーション側のサポートを必要とせず、自動的にこれらトレードオフを管理することができる。

【0043】

画像圧縮

グラフィックスシステムのコストパフォーマンスの決定において、最上位の要素は恐らくメモリであろう。例えば、従来の高性能3Dグラフィックスシステムは、フレームバッファ(ダブルバッファ)、深度バッファ、テクスチャバッファ、及び、アンチエイリアシングバッファを含めて、30メガバイトを越えるメモリを持つ。そして、この多くは、専用メモリであって、DRAMよりもずっと高価である。メモリバンド幅は常に致命的なボトルネックとなる。高性能グラフィックスシステムのコストに関して、画素及びテクスチャデータ・アクセスのために十分なバンド幅をもたらすように、インターリーブ・メモリの多数のバンクを設ける必要性に駆り立てられることが多い。

【0044】

本システムは、この問題を解決するために、画像圧縮技術を広く用いている。画像圧縮は、従来、グラフィックスシステムには使用されなかった。これは、高品質を実現するのに要求される計算上の複雑さのためであり、また、圧縮技術そのものが、従来のグラフィックス・アーキテクチャに容易に適合しないためでもあった。そこで、チャンキング(後述)と呼ぶ概念を用いることによって、画像やテクスチャに対して圧縮を効果的に適用することができ、それによって、コストパフォーマンス面において著しい改善を実現することができた。

【0045】

一態様においては、グラフィックスシステムは従来から、フレームバッファ・メモリに対して圧縮を用いてきた。高性能グラフィックスシステムは、三つのカラー成分のそれぞれに対して8ビットを用い、さらに、8ビットのアルファ値を含めることも多い。低性能グラフィックスシステムは、情報を捨てることによって、及び/又は、カラー・パレットを用いることによって、画素当たり32ビットを4ビットまで圧縮し、同時に表示可能なカラーの数を少なくすることによって実行する。この圧縮は、極めて目立つアーティファクトを生じさせ、データ要求に対して十分な抑制ができず、それでいて、アプリケーション及び/又はドライバに、広範な画素フォーマットに対処するように強制する。

【0046】

本システムで使用される圧縮は、高画質を実現しながら、10:1以上の圧縮比を与える。本システムの別の利点は、全てのアプリケーションに対して、単一の高品質の画像フォーマットしか使用しないということである。これは、空間解像度とカラー値・深度値との間のトレードオフを必要としていた標準のPCグラフィックス・アーキテクチャとは、明確に異なる点である。

【0047】

チャンキング

本システムの、別の重要な進歩を、チャンキングと呼ぶ。従来の3Dグラフィックスシステム(その点に限って言えばどのフレームバッファでも)ランダムにアクセスが可能である(されている)。画面上の任意の画素に対して、ランダムな順序でアクセスすることができる。圧縮アルゴリズムは、相当に大きな数の隣接画素へのアクセス性に依存するので(空間コヒーレンスを利用するために)、圧縮は、グラフィックス・アルゴリズムによって用いられるランダム・アクセス・パターンの性質のために、全ての画素の更新がなされて始めて実行可能となる。このため、圧縮技術を、表示バッファに対して適用することは実用的でなくなる。

【0048】

また、このようなランダム・アクセス・パターンは、画素単位の隠れ面消去や、アンチエイリアシング・アルゴリズムを導入した場合、画面上の各画素に対して、余分の情報を維持しなければならなくなることを意味している。これは、メモリ・サイズ要求を飛躍的に増大させ、さらに性能上のボトルネックを加えることになる。

本システムは、別の方法を取る。ある場面、又は、場面の一部は、チャンクと呼ばれる画素領域に分割される(ある特定の実現例では32×32画素)。一実現例では、システムは、gスプライトに割り当てられた幾何形状を複数のチャンクに分割するが、別の実現例では、gスプライトを用いずにチャンキングを実行する。この幾何形状は、どのチャンクにレンダリングされるかに基づいてビンに予めソートする。この処理をチャンキングと呼ぶ。チャンク境界をオーバーラップする幾何形状は、オーバーラップが見られる各チャンクを参照することが好ましい。場面が活発に変化するにつれて、本システムによれば、データ構造を、1つのチャンクから別のチャンクへと移動する幾何形状に対して調整するように修正する。

【0049】

チャンキングによって、幾つかの著しい利点が得られる。チャンキングの使用によって、効果的な態様の圧縮を提供することができる。1つのチャンク内の幾何形状は全て、後続するチャンクに進む前にレンダリングされるため、深度バッファは、僅か、単一チャンクだけの大きさを持つだけでよい。32×32画素のような比較的小さなチャンク・サイズを用いることによって、深度バッファを、グラフィックス・レンダリング・チップに直接実装させることができる。これによって、かなりの量のメモリを削減することができ、さらに、深度バッファを、専用メモリ・アーキテクチャを用いて実現することもできる。即ち、そのメモリ・アーキテクチャは、きわめて高いバンド幅をもってアクセスすることができ、かつ、ダブルバッファ動作時には空にすることができるので、フレーム間のオーバーヘッドを無くすことで、従来のフレームバッファ・メモリを削減することができる。

【0050】

アンチエイリアシングも相当に簡単になる。なぜなら、各チャンクは、独立に処理できるからである。アンチエイリアシング機能を備える、ほとんどの高性能Zバッファグラフィックスシステムは、大量の付加メモリを利用しながら、比較的単純なフィルタリングしか実行できない。しかしながら、チャンキングを用いれば、必要とされるデータ量は、かなり少ない(1000の桁)ので、さらに高度なアンチエイリアシング・アルゴリズムの実装を可能にする。

【0051】

Zバッファ処理やアンチエイリアシングに加えてさらに、本システムは、適正な、シームレスの態様で半透明処理をサポートする。あるチャンクを形成中、本システムは、もう1つのチャンクでアンチエイリアシングと半透明処理の計算を行なう。換言すれば、ある1つのチャンクを形成するのに必要な時間内で、本システムは、もう1つのチャンクでアンチエイリアシングと半透明処理を実行することができる。本システムは、チャンク間をピンポンのように往復することができるので、リアルタイム・アプリケーション用に画像を処理するにあたって、遅延を加えることなく高度の処理を実行することができる。

【0052】

さらに別の利点は、チャンキングは、ブロック性の画像圧縮を可能にすることである。一旦チャンクがレンダリングされた(かつ、アンチエイリアシングされた)ならば、次にそのチャンクは、ブロック変換ベースの圧縮アルゴリズムによって圧縮される。したがって、チャンクを別々にチャンキングすることによって実行される圧縮に加えて、チャンキングがさらに高度な、適応性の高い圧縮方式をサポートすることになる。

【0053】

マルチパス・レンダリング

本システムのアーキテクチャのもう1つの利点は、3Dインタラクティブ・アプリケーションが、1970年代終わりに見られるCADグラフィックスシステムの画像表現―あの、飽き飽きする、フォン・ハイライト(Phong highlight)を備えた、ランバーティアン・グーローシェーディングによるポリゴン群(lambertian Gouraud-shaded polygons)―から抜け出すためのきっかけを与えることである。カラー値のテクスチャ・マッピングは、この画像表現を改善するばかりでなく、アプリケーション上ではさらにもう1つ独特の画像表現を呈する。1980年代に、プログラム可能なシェーダ(shader)や、処理用テクスチャ・マップのアイデアが、レンダリング処理に新たな飛躍をもたらした。これらのアイデアは、オフライン・レンダリングの世界を一掃し、今日、映画の特殊効果に見るような高品質画像を生成させる。

【0054】

今日における通常の高性能3D画像ワークステーションの、厳密なレンダリング・パイプラインモード、及び、固定のレンダリングモードは、このような効果を実現した場合、必ずリアルタイム性能を急激に低下させる結果を招く。そのため、リアルタイム表示を要求するユーザは、狭く制限されたレンダリングの融通の利く範囲内に甘んずるを得ない。

【0055】

上に概説した方法を用いてバンド幅要求を下げることによって、本発明のシステムは、単一の共用メモリを、圧縮テクスチャの保存、及び、圧縮gスプライトの保存を含む、全てのメモリ要求を満たすように用いることができる。このアーキテクチャは、レンダリング処理で生成されたデータが、テクスチャ処理装置に戻され、新たなgスプライトのレンダリングのためのデータとして使用されることになる。このようなフィードバック・サポートのために、本システムは効率的なマルチパス・レンダリングを実行することができる。

【0056】

効率的なマルチパス・レンダリングを、様々の合成モードと柔軟性のあるシェーディング言語とを組み合わせることによって、本システムは、以前はオフ・ライン・ソフトウェア・レンダリングの領域であった、各種のレンダリング効果をリアルタイムで供給することができる。そのようなものとして、シャドウ(複数光源によるシャドウイングを含む)、環境マップの反映オブジェクト、スポット・ライト、地上の霞、リアルな水中シミュレーションなどの機能のサポートがある。

【0057】

一実施例においては、画像処理システム(100)は、ソフトウェアとハードウェアの組み合わせを含む。次節で、ハードウェアとソフトウェア・アーキテクチャを参照しながら、システム環境について述べる。可能な限り、別態様のアーキテクチャについても述べる。しかしながら、ソフトウェアとハードウェアは変更が可能であるから、後述する特定の実施例には限定されない。

本画像処理システム、又は、その部分は、デスクトップ・コンピュータ、セット・トップ・ボックス、及び、ゲームシステムを含む、幾つかの異なるプラットフォームに実装することができる。

【0058】

図2は、本画像処理システムが実装されるホスト・コンピュータシステム130のブロック図である。ホスト・コンピュータシステム130は、プロセッサ132、メイン・メモリ134、メモリ制御装置136、二次保存装置138、入力装置(単数又は複数)、表示装置142、及び、画像処理ハードウェア144を含む。メモリ制御装置136は、プロセッサ132とメイン・メモリ134との間のインターフェイスとなる。メモリ制御装置はさらに、プロセッサ132とメイン・メモリ134が、バス146に接する時のインターフェイスとしても働く。

【0059】

図2に示したと同一、又は、同様のアーキテクチャを持つコンピュータシステムは様々ある。そのようなシステム内部のプロセッサも変動し得る。さらに、1個以上のプロセッサを含むコンピュータシステムもある。幾つか挙げるならば、プロセッサ132は、インテル社のペンティアム、又は、ペンチティアム・プロであってもよいし、シリコン・グラフィックス社のMIPS系列から成る小型プロセッサであってもよいし、モトローラ社のパワーPCであってもよい。

【0060】

メイン・メモリ134は、高速メモリであって、ほとんどの通常のコンピュータシステムでは、ランダム・アクセス・メモリ(RAM)が装備されている。メイン・メモリは、既知の技術のどのような変種においても、プロセッサ及びバスとインターフェイスを形成する。メイン・メモリ134は、コンピュータのオペレーティング・システムや、現に実行するアプリケーション・プログラムのようなプログラムを保存する。以下に、コンピュータシステムによって実行される命令のシンボル表現を参照しながら、一実施例の様々な態様を述べる。この命令は、コンピュータ実行とも呼ばれる場合がある。この実施例のこれらの態様は、コンピュータ読み取り可能な媒体に保存された一連の命令からなる、1つのプログラム又は複数のプログラムとして実現することもできる。コンピュータ読み取り可能な媒体は、メイン・メモリ又は二次保存装置と組み合わされる、ここに説明する装置等のいずれであっても、又は、それら装置等の組み合わせであってもよい。

【0061】

バス146は、メモリ制御装置136、二次保存装置138、及び、画像処理ハードウェア144を互いに結び付ける。ある実現例では、例えば、バスはPCIバスである。PCI標準は既知であり、この標準をサポートするように設計されたコンピュータシステムのボードはいくつかある。例としては、ISAバス、EISAバス、VESAローカル・バス、及び、NuBusがある。

表示装置142は、カラー表示装置であって、画像を表示するために連続的に更新される。一実施例の表示装置は、陰極線管(CRT)を用いた表示装置であるが、これは、液晶表示(LCD)であっても、その他の表示装置であってもよい。

二次保存装置138は、各種の保存媒体を含む。例えば、二次保存装置は、フロッピー(登録商標)・ディスク、ハードディスク、テープ、CD−ROMなどを含んでいてよく、また、電気的、磁気的、光学的、又は、他の記録材料を用いる装置であってもよい。

【0062】

入力装置(単数又は複数)140は、キーボード、マウスや、ジョイスティックのようなカーソルポジショニング装置の他に、各種市販の入力装置を含む。

下記に詳述する1つの実現例においては、画像処理ハードウェア144は、コンピュータシステムと、PCIバスを通して結合するボードに実装される。

また別の実現例では、画像処理ハードウェアは、プロセッサや、他の画像処理ハードウェアやメモリと共にシステム・ボードに置かれる。例えば、あるゲームシステムでは、画像処理ハードウェアは、通常、マザー・ボード上に置かれる。同様に、セット・トップ・ボックスの画像処理ハードウェアもマザー・ボード上に置いてもよい。

【0063】

コンピュータシステムのアーキテクチャを概説したからといって、本発明を、図2に示したシステム・アーキテクチャに限定するつもりはない。本画像処理システムは、ゲームシステム、セット・トップ・ボックス、ビデオ編集装置などに実装することができる。以下に、図2に示したシステム・アーキテクチャの環境における画像処理システムの実施例を説明する。下記の説明全体を通じて、別態様の実施例を述べるが、他に考えられる可能な実現例の完全なリストを与えるつもりで、これら別態様の実施例を説明するものではない。下記の詳細な説明に基づけば、当業者であれば、本画像処理システムを、別のプラットフォームに実現することは可能である。

【0064】

図3は、一実施例におけるソフトウェアとハードウェアの間の関係を示すブロック図である。この実施例においては、画像処理システムは、ホスト・コンピュータのプロセッサと、画像処理ハードウェア144の処理リソースに基づいて実現される。画像処理ハードウェア144は、プロセッサ(例えば、ディジタル信号プロセッサ166)と画像処理回路168を含む拡張ボード上に実装される。ホスト・コンピュータシステム130と、画像処理ボードのプロセッサは、画像処理演算を共同で行なう。以下に、ホスト・コンピュータシステム130と画像処理ボード174によって実行される機能を概説する。

【0065】

グラッフィクス・サポート・ソフトウェア160は、ホスト・コンピュータシステム130の上で実行され、ハードウェア抽象化層(HAL)162を通じて画像処理ボード164と情報を交換する。画像処理ボード164は、DSPと呼ばれるプログラム可能なディジタル信号プロセッサ166と、以下に詳述する別の画像処理ハードウェア168を含む。

【0066】

グラフィックス・サポート・ソフトウェア160は、メモリ管理、視体積の選択、深度のソーティング、チャンキングの他に、gスプライトの割り当て、変換、及び、ディテールのレベルをサポートする機能を含む。グラフィックス・サポート・ソフトウェアは、ここに挙げる機能を実行するために、グラフィックス・アプリケーション類のアクセス可能な、一群のグラフィックス機能を含んでいてもよい。

【0067】

グラフィックス・サポート・ソフトウェア160は、上に紹介したgスプライト・パラダイムをサポートする機能を含む。上に示したように、gスプライトは独立にレンダリングされるが、フレームごとにレンダリングする必要はない。むしろ、gスプライトの位置の変化は、アフィン変換、又は、その他の変換で近似させてもよい。グラフィックス・サポート・ソフトウェア160は、1つのオブジェクト、又は、複数のオブジェクトを、1つのgスプライトに割り当てることを助ける機能と、そのgスプライトの位置と動きを記述する移動データを追跡する機能とを備える。さらに、グラフィックス・サポート・ソフトウェアは、レンダリングされたgスプライトを更新すべき時を決める機能を備える。gスプライトを更新する必要のある場合は、オブジェクトの動き、視点の動き、ライティングの変化、及び、オブジェクトの衝突に応じて変化する。

以下に、グラフィック・サポート・ソフトウェアの機能に関してさらに詳細を述べる。画像処理ボード164は、変換、ライティング、及び、シェーディング、テクスチャリング、アンチエイリアシング、半透明処理などを含む低レベルの幾何学処理を実行する。一実施例では、DSP166が、フロントエンド幾何学処理とライティング計算を実行するが、この機能のうちいくつかは、プロセッサ132に実行させてもよい。

【0068】

画像処理ボードの概観

図4Aは、画像処理ボード174を示すブロック図である。この画像処理ボード174は、ホスト・コンピュータと、バス146を介して連絡する。この画像処理ボード174は、DSP176、タイラー200、共用メモリ216、gスプライト・エンジン204、合成バッファ210、及び、ディジタル・アナログ変換器(DAC)212を含む。ホストからの命令に応じて、画像処理ボード174は、画像をレンダリングし、表示用画像を、DAC212を介して表示装置142(図2)に転送する。

【0069】

図2〜4Aに示す実施例では、プロセッサ132とDSP166は、図1の画像前処理装置104の機能を共有している。画像処理装置106は、タイラー200、gスプライト・エンジン204、合成バッファ210及びDAC212から成る。以下に、これらの構成要素についてさらに詳細を述べる。しかしながら、画像処理システムの実現は変更可能であることに留意すべきである。

【0070】

共用メモリ216は、画像処理ボード174上において、画像データ及び画像処理命令を蓄える。一実施例では、共用メモリは、gスプライトとテクスチャデータを圧縮した形で蓄えるように用いられ、各種バッファは、処理サブシステム間にデータを転送するように用いられる。

DSP176は、ビデオ圧縮・復元と、フロントエンド画像処理(変換、ライティング、など)を行なう。できれば、DSPは、1000 MFLOPS/MOPSを越える浮動小数点と積分計算をサポートするものであることが好ましい。

タイラー200は、VLSIチップであって、マルチパス・レンダリングのために、走査変換、陰影階調、テクスチャリング、隠れ面の消去、アンチエイリアシング、半透明処理、シェーディング、及び、マルチパス・レンダリングを行なう。次に、この結果生じるレンダリングしたgスプライト・チャンクを圧縮し、圧縮した形で共用メモリに蓄える。タイラーはさらに、ビデオ、及び、ウィンドウ演算をサポートするために、gスプライト・データの復元及び再圧縮を行なう。

【0071】

gスプライト・エンジン204は、ビデオ速度で、gスプライトのチャンク・データに接触し、これを圧縮し、一般のアフィン変換(これには、拡大・縮小、画素以下の精度を持つ変換、回転、反射及びせん断(shearing)が含まれる)のために必要な画像処理を行なう。フィルタリング後に得られた画素(アルファ値を含む)は、合成バッファに送られ、ここで表示画素データが求められる。

【0072】

gスプライト・チャンク・データは、表示のために、1回に走査線の数だけ処理される。一実施例では、チャンク・データは、1回に32本の走査線分処理される。合成バッファ(210)は、二種の、32走査線カラーバッファを含み、これら二種を、表示と合成動作の二つの間で交互に切り替える。合成バッファはさらに32走査線アルファ・バッファを含む。このバッファは、各画素に対するアルファ値を累積するように用いられる。

DAC212は、RGBビデオDACと対応するビデオ・ポート214から、ビデオ編集装置までを含む。個々の成分は、DACの機能性を実現するために用いられる。

【0073】

システムの動作

図5A及び図5Bは、本画像処理システムにおいて画像をレンダリングする際に実行されるステップを示すフローチャートである。画像処理装置106が、ビュー空間に対して画像をレンダリングする前に、画像前処理装置104は、オブジェクトと視点の位置を決める(240)。図2及び図3で示した実施例では、ホスト・コンピュータシステム130で実行するグラフィックス・サポート・ソフトウェア160が、グラッフィクス・アプリケーションから供給されるデータに基づいて、オブジェクトと視点の位置を決める。プロセッサ132で実行するグラフィックス・アプリケーションは、関係するオブジェクトを表わすモデルを規定し、モデル変換を供給して、そのオブジェクトを、他のオブジェクトと共に「ワールド座標」の中に位置づけるように使用される。

【0074】

次に、画像前処理装置104は、潜在的に可視のオブジェクトを選び出す(242)。画像前処理装置104は、視体積に基づいて、潜在的に可視のオブジェクトを決める。視体積とは、ワールド座標における三次元空間であって、場面に対して境界を与える。画像前処理装置104は、オブジェクトをトラバースすることによって、潜在的に可視のオブジェクトを選び出し、その境界が、視体積と交差するかどうかを決める。視体積と交差するオブジェクトは、幾何学的又は空間的な意味で、潜在的に可視であることなる。

【0075】

ある場合には、場面の将来の変化を予測するために、現在の視体積の外部に、「時間的に」、潜在的に可視のオブジェクトを決めておくことが有利なことがある。こうすれば、本システムは、視体積の急激な変化にも対応していくことができる。通常の3Dグラフィックスシステムでは、このような急激な変化に対応する唯一の手法は、変更された入力に基づいて新たな場面を完全に生成させることであり、そのため、その間に相当な伝達遅延を生ずることになる。そのような長い遅延は、ユーザに否定的効果を及ぼし、調整過度や気分のむかつきのような問題を生じさせる。この遅延を低減させるために、本発明の画像前処理装置104は、可視域の外側へと拡大した範囲に置かれるオブジェクトの位置を計算することができ、かつ、画像処理装置106は、この拡大範囲の中の画像をレンダリング及び保存することができる。本システムのアフィン変換機能に基づき、次のフレームに対する視点の入力を、この伝達遅延を低減させる拡大範囲からのgスプライトを、計算フレームにして2フレーム未満に再配置するように用いることができる。そのような短い伝達遅延は、本発明者にとって既知の従来の3Dグラッフィクス・ハードウェアシステムでは到達不可能なものであり、さらに高品質なシミュレーションを可能にし、したがって、ユーザをさらに心地よく画面に没頭させることができる。

【0076】

画像前処理装置104は、画像に対するgスプライトの構成を決定する(244)。このステップは、潜在的に可視のオブジェクトをgスプライトにマップする方法を見つけ出すステップを含む。この処理の一部として、画像前処理装置104は、gスプライトの割り当てを行なって、gスプライトのデータ構造を生成し、それによって1つ以上の潜在的に可視のオブジェクトに対応する画像データを蓄えることを含む。処理用リソースが許すならば、場面内の非貫通性オブジェクトの各々は、独立のgスプライトに割り当てられる。非貫通性、又は、自己遮蔽オブジェクトは、単一のgスプライトとして処理される。

【0077】

画像前処理装置104は、画像処理装置106が、これらgスプライトを所望の計算フレームレートで合成する能力を持たない場合、あるいは、それらgスプライトを蓄えるほど十分なシステムメモリがない場合、これらgスプライトを合体させることができる。別々のgスプライトにレンダリングすることは、必ず計算上効率が高くなるので、システムにメモリ能力や、合成能力があるならば、非交差性オブジェクトを、別々のgスプライトにレンダリングする。システムが、gスプライトの現在の割り当てに基づいて表示画像を保存ないし生成できない場合には、幾つかのgスプライトを合体して、この問題を緩和する。

【0078】

1つのオブジェクト、又は、複数のオブジェクトをgスプライトに割り当てた後で、画像処理装置106は、gスプライトを、「チャンク」と呼ばれる画像領域に分割する(248)。画像前処理装置104が、gスプライトに対しループ(繰り返し演算)を実行し、このgスプライトをチャンクに分割する(246、248)。一実施例では、この処理は、ビュー空間に対するオブジェクトの境界ボリュームを変換し、この変換された境界ボリュームを包む方形の画像領域を見つけ出すことを含む。この画像領域は、gスプライトのオブジェクト(単数又は複数)がレンダリングされる二次元空間におけるgスプライトの大きさを定める。gスプライトは、この方形画像領域をチャンクに分割することにより、それらチャンクをgスプライト・データ構造と関連付けて、チャンクに分割される。

【0079】

最適化の1つの手法として、変換された境界ボリュームを拡大・縮小し、及び/又は、回転させ、それによって、gスプライト変換に必要なチャンクの数が極小になるようにしてもよい。このように変換(拡大・縮小、あるいは、回転)をさらに加えることから、gスプライトに割り当てられたオブジェクトの空間は、必ずしも画面空間である必要はない。この空間を、gスプライト空間と云う。表示画像を生成する処理で、gスプライトを再び変換して画面空間に戻さなければならない。

【0080】

次のステップは、オブジェクトの大きさを、チャンク間にどのように分割するかを決めることである(250)。画像処理装置106は、幾何形状プリミティブ(例えば、ポリゴン)が、チャンク間にどのように分割されるかを、そのポリゴンを2D空間(252)に変換し、そのポリゴンがどのチャンク(単数又は複数)に投影するかを求めることにより、決定する。ポリゴンを切り取るのは高コストであるから、好ましい方法は、チャンクの端にあるポリゴンは切り取らないことである。むしろ、チャンクは、その端を重ねる複数のポリゴンを含む。例えば、1つのポリゴンが、2つのチャンクの境界を超えて延在している場合は、この方法では、ポリゴンの頂点が、各チャンクに含まれることになる。

【0081】

次に、画像前処理装置104は、チャンク・データを、タイリングのためにキューする。タイリングとは、1つ以上のポリゴンで全体に、又は、部分的にカバーされる画素位置の、カラー値やアルファ値のような画素値を決める処理を云う。

決定ステップ(254)(図5B)、及び、それに続くステップ(256)は、チャンク内でポリゴンのタイリングを行なう処理を表わす。画像処理装置106は、現在のチャンクの境界に重なるポリゴンを含む一方、同チャンク内にある画素しか生成しない。生成された画素は、アンチエイリアシング(フラグメント記録)のための情報を含み、フラグメント記録は、全ての画素が生成されるまで保存される。

【0082】

チャンクのポリゴンのタイリングが終了した後、画像処理装置106は、画素のためのアンチエイリアシングデータ(フラグメント記録など)を解析する(258)。一実施例では、タイラー200は、ダブルバッファを用い、次のタイリングを行なっている間に、その前のチャンクを解析する。また別のやり方として、タイラーは、フリー・リストを有する共用バッファを用いることができる。フリー・リストとは、共有バッファ内の空のメモリを表わし、これは、新しいフラグメント記録が生成されると割り当てられ、フラグメント記録が解析されると、また加えられるものである。ダブルバッファ法と共有メモリの組み合わせを用いても同様の効果が期待できる。

【0083】

画像処理装置106は、後述する圧縮法を用いて、この解析されたチャンクを圧縮する。画像処理装置106は、1ブロックの画素を解析すると同時に、別のブロックを圧縮してもよい。画像処理装置106は、共用メモリにこの圧縮チャンクを蓄える(262)。

図6は、画像を表示するために実行されるステップを示すフローチャートである。上述の画像処理ボード174上において、画像は、共用メモリ216から読み取られ、gスプライト・エンジン204によって、物理的出力装置座標に変換され、合成バッファ210において合成され、DAC212に転送され、次にその出力装置に転送される。

【0084】

表示処理において、画像処理装置106は、現在のフレームに表示されるべき一連のgスプライトにアクセスする。gスプライト形態を決定する処理において、画像前処理装置104は、gスプライトの深度の桁を決める(280)。前述したように、1つのgスプライトには1つのオブジェクトを割り当てるのが好ましい。しかしながら、画像前処理装置104は、例えば、本システムで使用される、特定の画像処理装置の処理限界を受け容れるために、1つのgスプライトに対して1個以上のオブジェクトを割り当ててもよい。画像前処理装置は、オブジェクトを、Z順に、即ち、視点からの距離として、オブジェクトをソートする。オブジェクトをソートするのに加えて、さらに、gスプライトを深度順にソートし、この深度データをgスプライト・データ構造に蓄える。

【0085】

図6の決定ステップ(282)は、表示処理におけるgスプライトに対するループを表わす。このループ内のステップとしては、1)レンダリングしたgスプライト用の変換を求めること、2)如何にgスプライトを表示するかを制御するためのgスプライト表示リストを形成すること、がある。これらのステップについては後述する。

潜在的に可視範囲のgスプライトに関しては、画像処理装置106は、gスプライト変換を求める。gスプライト変換とは、レンダリングされた2Dのgスプライトにおける変換を云う。一実施例では、画像処理装置106は、レンダリング・オーバーヘッドを低減するようにgスプライトに対して変換を実行する。フレームごとに各オブジェクトをレンダリングするのでなく、画像処理装置106は、レンダリングされたgスプライトを再利用することによって、レンダリング・オーバーヘッドを低減させる。

【0086】

画像データの各フレームにgスプライト変換を計算する必要はない。例えば、gスプライトが、画像データの現在フレームに対してレンダリングされたのであれば、そのgスプライトを変換する必要はない。これは、例えば、そのgスプライトをレンダリングして、境界ボックスをそのオブジェクトによりよく適合させようという要求がない限りそうである。さらに、再レンダリングや変換を要しないgスプライトがある。即ち、そのgスプライトに割り当てられたオブジェクト(単数又は複数)が変化しない場合や、動かない場合である。そのような場合、gスプライトを変換するステップは、実行してもよいし、しなくともよい。

gスプライトの位置が変化しない場合には、このgスプライトに、単位行列をかけてもよい。これは、例えば、画像処理装置106が、現在のフレームのためにgスプライトをレンダリングした場合、あるいは、始めにレンダリングされて以来、gスプライトの位置が変化しない場合に適用される。

【0087】

gスプライトの表示法を特定するために、画像処理装置106は、gスプライト表示リストを生成する。表示リストとは、どのgスプライトを、表示画面に表示すべきかを規定する1つのリスト、又は、複数のリストを云う。この表示リストの概念は、1フレームの画像データを表示するための他の出力装置にも適用することができる。画像処理装置106は、表示リストを、レンダリングされたgスプライトを物理的出力装置座標にマップし、さらに合成するのに用いる。表示を構成させるステップは、gスプライトに対するループの一部として示されているが、このリスト(単数又は複数)は、特にこのループ内に生成される必要はない。

【0088】

表示リストは、一連のgスプライト・リスト、又は、バンド幅単位の、一連のgスプライト・リストであってもよい。「バンド幅」とは、表示画面の水平走査線領域である。例えば、一実施例では、バンド幅は、32走査線高×1344画素幅である。表示リストは、各バンド幅で別々のgスプライト・リストを含んでいてもよく、その場合、バンド幅リストは、それぞれのバンド幅に照射するgスプライトを記述する。また別法として、表示・リストは、どのバンド幅にgスプライトが照射するのかを特定できるようにgスプライトに名札をつけて実行される、そのような単一リストからなるものであってもよい。

【0089】

ここに示した実施例の表示リストは、ダブルバッファ方式である。ダブルバッファを持つことによって、本システムは、他方のデータ・リストを読み取っている間に、一方のデータ・リストを生成することができる。本システムが1つのフレームに対するgスプライトの変換を求め、表示リストを構成している間に、別のフレームの表示リストを読み取り、このリストの中の画像データを表示する。

ダブルバッファであるために、図6に示したステップは重複する。即ち、画像処理装置106は、あるフレームに対しては、ステップ(280−286)を実行する一方で、別のフレームに対してはステップ(290−298)を実行する。

【0090】

図7は、上記ステップのタイミングを示すブロック図である。本システムが、フレーム310に対してステップ(280−286)(図6)を完了すると、本システムは、フレーム同期信号(垂直点線)を待ち、それからバッファ交換を実行する。次に、本システムが生成したばかりの表示リストを用いて、現在フレーム312に表示すべきgスプライトを決める。この表示リストを処理している間に312、gスプライト変換が計算され、かつ、次のフレームのための表示リストが構成される314。次のフレームにおいて、前のフレーム314で生成されたgスプライト変換と表示リストが用いられ、表示画像316を生成する。

【0091】

画像処理装置106は、表示リストの中のgスプライトのリストに基づいて、gスプライトを出力装置座標に変換する。画像処理装置106は、カラー値、アルファ値、及び、gスプライトの位置を特定するデータを含むgスプライト・データを共用メモリから読み取る。このデータに基づいて、画像処理装置106は、そのgスプライトによってカバーされる画素のカラーとアルファを決める。

一実施例においては、画像処理装置106は、各バンド幅にループ制御を行ない、gスプライト表示リストに従って、そのバンド幅に照射するgスプライトを変換する。以下に、この表示処理については、さらに詳細に述べる。

【0092】

gスプライト・データを変換した後、画像処理装置106は、得られた画素データを合成する。この中には、gスプライト変換に基づいて、出力装置座標で表わした画素に対するカラー値とアルファ値を計算することを含まれる。画像処理装置106は、表示リストの中のgスプライトに対する画素データを変換し、次に、その変換した画素データを合成する。この処理は、ある画素位置について、それをカバーするgスプライトの1つ以上の画素値の組み合わせに基づいて、その位置のカラー値とアルファ値を決定することを含む。

【0093】

一実施例では、画像処理装置106は、バンド幅にループ制御を実行し、各バンド幅に画素データを合成する。画像処理装置106は、画素データをダブルバッファリングで扱う。即ち、1つのバッファにおいてあるバンド幅のgスプライトを変換及び合成する一方で、別のバンド幅に対しては、合成済み画素データを表示する。

画素データを合成した後、画像処理装置106は、合成画素データを物理的出力装置に転送する。画素データを表示するためには、それは、表示と適合するフォーマットに変換されていなければならない。

【0094】

一実施例のシステムの全体動作を説明し終えたので、次に、画像処理ボードについてさらに詳細に述べる。

画像処理ボード

一実施例では、共用メモリ216は、4メガバイトのRAMを含む。これは、2本の8ビットRAMバス・チャンネルによって実行される。しかしながら、メモリの量及び型は変更可能である。

【0095】

図8は、画像処理ボード174におけるDSP336を示すブロック図である。DSP336は、プロセッサ132からの命令ストリームを取りまとめ、若干のビデオ処理とフロントエンド幾何学処理を実行する。DSPは、3Dグラフィックスに用いられるフロントエンド幾何学処理、及び、ライティング計算を実行する。この中には、モデル変換及びビューイング変換や、クリッピング、及び、ライティングが含まれる。gスプライトの動き外挿のような、gスプライト・アニメーション処理の部分もDSPで処理される。

【0096】

レンダリング命令は、メインメモリ・バッファに保存され、PCIバスを通り、PCIバス制御装置342を経由して画像処理ボード174にDMA化される。次に、これらの命令は、ボードの共用メモリ216に、DSP336(図8)に要求されるまで、蓄えられる。

DSPコア338は、上述の画像処理計算を実行するためのプロセッサを含む。さらにDSPコアは、スケジュール設定、及び、リソース管理を実行する。

【0097】

メモリ・インターフェイス340は、高速のデータ転送、例えば、80MHzにおいて64ビットをサポートする。これは、通常のDRAMやSDRAM装置とインターフェイスを形成するように設計されている。タイラー200は、このバスに直接接続するように設計されており、DSPによって要求されるメモリ・タイミングをシミュレートする。

【0098】

DSPにおけるデータ・フォーマッタ及びコンバータ346は、タイラーに対するレンダリング命令をフォーマットする。このブロックは、浮動小数点カラー成分を、整数に変換し、それらを、タイラー専用データ構造にパッキングする。さらに、全命令を蓄え、これを直接共用メモリ中のメモリ・バッファにDMAする。このレンダリング命令は後に、動作実行の態勢が整った時に、タイラーによって読み取られる。

【0099】

フォーマットするタスクの間で、データ・フォーマッタとコンバータ346は、タイラーに対して三角形・命令データをフォーマットする。DSP(336)によって浮動小数点として計算されたRGB∝(アルファ値)データは、8ビットの整数に変換される。座標情報は、浮動小数点から12.4の固定点に変換される。このデータは、64ビット語にパックされ、一連のブロックとして、共用メモリに転送され、これにより、最適なバンド幅が得られる。

【0100】

表示メモリ管理部(MMU)334は、デスクトップ表示メモリのために使用される。表示メモリ管理部(MMU)334は、デスクトップ表示メモリとして割り当てられた、ラインアドレス範囲内のPCIアクセスをトラップする。次に、このアクセスを、共用メモリに蓄えられた画像ブロックにマップする。

画像処理ボード174(図4A)のアーキテクチャは、特定のDSPからは比較的独立している。しかしながら、DSPは、顕著な浮動小数点性能を持っていることが好ましい。適当なDSPとしては、サムスン社(Samsung)製の半導体のMSP−1、及び、フィリップス社(Phillips)製の半導体のトリメディア(Trimedia)が挙げられる。これら特定のDSPは、十分な浮動小数点性能を与えるDSPの二つの例である。

【0101】

図9Aは、画像処理ボード174におけるタイラー200のブロック図である。タイラーは、2D及び3Dグラッフィクスの加速と、共用メモリ調整を実行する。画像処理ボード174のブロック図で示したように、タイラーは直接DSP176(図4)、gスプライト・エンジン204、及び、共用メモリ216に接続する。

【0102】

上記ブロック図の機能ブロックは、この節に記載される。

タイラー378は、プリミティブ・レンダリングのために多くの構成要素を含む。命令・メモリ制御装置380は、共用メモリ216、gスプライト・エンジン204、及び、DSP176とインターフェイスを形成する。タイラー、DSP、及び、gスプライト・エンジンからの、メモリに対するアクセスは、このブロックによって判断される。キューが、バッファ読み取りアクセスに対して与えられる。

【0103】

セットアップブロック382は、三角形の面を横切るエッジ、カラー、及び、テクスチャ座標の補間を決める直線方程式を求める。この方程式はまた、この三角形をレンダリングするにはどのテクスチャブロックが必要とされるかを決めるのにも用いられる。エッジ方程式はさらに走査変換ブロック394にも送られ、走査変換エンジン398に要求されるまで、プリミティブレジスタ396に蓄えられる。

【0104】

セットアップブロック382は、三つの構成要素を含む。頂点入力処理装置384、頂点制御レジスタ386、及び、セットアップ・エンジンである。頂点入力処理装置384は、DSPからの命令ストリームを集める。頂点制御レジスタ386は、ポリゴン、又は、その他の幾何形状プリミティブを処理するのに必要な情報を蓄える。この特定の実施例では三角形の処理が用いられ、かつ、タイラー200は、三角形の処理のダブルバッファ対応を実行するために、6頂点(各三角形につき三つずつ)のレジスタを含む。セットアップ・エンジン388は、カラー、深度、エッジに対する微分と、三角系の面を横切るテクスチャ座標の補間を計算する。これらの方程式はまた、この三角形をレンダリングするにはどのテクスチャブロックが使ったらよいかを決めるのにも用いられる。セットアップ・エンジンはさらにテクスチャチャンクをあらかじめフェッチし、それによって、走査変換エンジン398に要求された場合にいつでも利用可能なようにしておく。

【0105】

セットアップ・エンジン388はさらにテクスチャ読み取りキュー390、及び、テクスチャアドレス生成装置392と連絡する。テクスチャ読み取りキュー390は、共用メモリのテクスチャブロック読み取り要求を保存する。ここで、メモリから画像データブロックを取り出すために用いられるタイラーの部分を指して「テクスチャ」という用語を使用する時は、この用語は、マルチパス・レンダリング動作で用いられるテクスチャ・マップ、シャドウマップ、及び、その他の画像データを云うこともあり得るということを了解しなければならない。テクスチャアドレス生成装置392は、要求されたチャンクの、メモリ内部のアドレスを決め、テクスチャ読み取り要求を、命令・メモリ制御装置380に送る。このテクスチャアドレス生成装置392は、画像データの、テクスチャキャッシュへの書き込みを制御するメモリ管理部を含む。

【0106】

走査変換ブロック394は、セットアップブロックから微分値とその他の頂点データを受け取り、画素データを生成する。走査変換ブロック394は、プリミティブレジスタ396と、走査変換エンジン398とを含む。プリミティブレジスタ396は、各三角形のパラメータに対する方程式パラメータを蓄える。プリミティブレジスタは、複数組の方程式を蓄えるためのレジスタを含み、それによって、走査変換エンジンが、テクスチャデータを待ち続けて停止することがないようにする。

【0107】

走査変換エンジン398は、ポリゴンを変換する。この場合、ポリゴンは三角形である。走査変換ブロック394は、移動エッジ用、又は、カラー、深度などを評価用の補間器を含む。カラー、深度を備えた画素アドレス、及び、アンチエイリアシング包括情報は、画素エンジンに転送され、処理される。

走査変換エンジン398は、テクスチャアドレスを、テクスチャデータを算出するテクスチャフィルタ・エンジン400に送出する。テクスチャフィルタ・エンジン400は、レンダリングしたポリゴンの画素のカラー値及びアルファ値を求める。図に示したテクスチャフィルタ・エンジンは、レンダリングした三角形のZ勾配と方向、及び、テクスチャ要求の中心に基づいてフィルタ・カーネルを計算する(1点のSとT座標がテクスチャにマップされる)。フィルタリングは、パイプライン方式によって、各サイクルに新しい画素が生成されるように二段階で実施される。フィルタ・カーネルは、異方性フィルタであってもよいし、等方性フィルタであってもよい。異方性が要求されない場合は、フィルタ・カーネルは、トライ・リニア補間で可能とされる場合よりも更に鋭いテクスチャを可能とするネガティブローブ(negative lobes)フィルタを用いてもよい。テクスチャフィルタ・エンジン400はさらに、シャドウに対する効果を計算するようにZ比較動作を処理する。

【0108】

テクスチャキャッシュ402は、復元画像データのブロックを蓄える。一実現例では、テクスチャキャッシュ402は、16個の、8×8画素・ブロックのテクスチャデータを蓄える。このデータは、16個のテクスチャ要素が、クロック・サイクルごとにアクセスされるようにまとめられる。

【0109】

復元エンジン404は、テクスチャデータを復元し、これを、テクスチャキャッシュ402に転送する。本実施例においては、復元エンジンは、2つの復元器を含む。一方は、テクスチャのような連続階調画像に対して、離散コサイン変換(DCT)準拠アルゴリズムを実行するもので、他方は、デスクトップ・画素データ用に脱落のないアルゴリズムを実行する。DCT準拠アルゴリズムは、二つの、並行な復元ブロックによって実行され、しかも、このブロックは各々クロック・サイクルごとに8画素要素(即ち、2画素)を生成できる。

【0110】

圧縮キャッシュ416は、復元エンジン404が圧縮データを復元し、テクスチャキャッシュ402に転送するまでは、その圧縮データを蓄えるのに使用される。

走査変換エンジン398は、画素データを画素エンジン406に転送する。画素エンジン406は、混合、及び、深度のバッファリングを含む画素レベルの計算を実行する。画素エンジンはさらにシャドウに必要なZ比較動作を処理する。最適性能を発揮するためには、画素エンジンは、クロック・サイクルごとに1画素ずつ動作することが好ましい。

【0111】

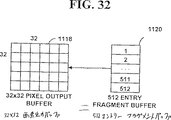

画素エンジン406は、ラスタライゼーションバッファへの画素データの転送を制御する。ここに示した実施例では、ラスタライゼーションバッファは、画素バッファ408とフラグメントバッファ410を含む。画素バッファ408は、ダブルバッファリングをサポートするために2個のバッファを含む。この画素バッファを実現例において、各画素エントリは、カラー成分(RGB)当たり8ビット、アルファ成分用に8ビット、Zバッファ用に24ビット、ステンシル・バッファ用に8ビット、フラグメントバッファ用に9ビット・ポインタを蓄える。これは、画素当たり合計73ビットになる。一方の画素バッファが画素エンジン406で使用されている時、他方は、アンチエイリアシング・エンジン412によって使用される。

【0112】

フラグメントバッファ410は、画素フラグメントと呼ばれる、部分的にカバーされる画素のフラグメントを蓄える。このようなフラグメントは、ポリゴンのエッジが、ある画素を跨る場合、又は、ポリゴンが、半透明性を持つ画素である場合である。フラグメントバッファは、図9Aに示した実現例では単一バッファ処理で実行される。フラグメントのフリー・リストの保持は次のように行なわれる。即ち、フラグメントが解析されるにつれて、それらはフリー・リストに加えられ、フラグメントが生成されるにつれて、そのフラグメントは、フリー・リストからのエントリを利用する。また、別法として、フラグメントバッファはダブルバッファリング方式であってもよい。それによって、他方のフラグメントバッファが、並行的に画素エンジンによって処理がいっぱいとされた際に、一方のフラグメントバッファをアンチエイリアシング・エンジンによって解析することができる。

【0113】

一実施例では、フラグメント記録は、画素バッファ・エントリに、4×4マスクを加えたものと同じデータを含む。9ビット・ポインタは、リストの終端を示すリザーブ値を有する、リンク化したエントリのリストを形成するように用いられる。この実施例では、フラグメントバッファ410は、合計512個のエントリを含むが、その大きさは変動してもよい。

【0114】

アンチエイリアシング・エンジン412は、1個以上のポリゴンによって悪影響を被る画素におけるカラーとアルファ成分を求める。このようなことは、複数のポリゴンが、その画素領域をほんの部分的にしかカバーしない時(即ち、ポリゴンのエッジがその画素を横切る時)、又は、ポリゴンが半透明性を持つときに起こる。アンチエイリアシング・エンジン412は、解析された画素データを圧縮エンジン414に転送する。この実施例では、圧縮エンジン414は、二つの圧縮器を含む。即ち、一方は、連続階調の画像用のDCT準拠のものであり、他方は、デスクトップ・画素データ用のロスレス・タイプのものである。DCT準拠アルゴリズムは、クロック・サイクル当たり8画素要素を圧縮できる圧縮器によって実行される。圧縮エンジン414は、結果として生じるレンダリングしたgスプライトを圧縮し、この圧縮データを命令・メモリ制御装置380に転送し、これは、共用メモリ216に保存される(図4)。タイラーも、圧縮データをキャッシュに換える圧縮キャッシュ416を持つ。

【0115】

図10及び図11は、画素生成処理において、メモリから画像データにアクセスするに当たって、二つの別態様の実施例を示したものである。画素生成中にメモリから画像データにアクセスしなければならない場合がいくつかある。そのような例としては、例えば、テクスチャ・マッピング動作中にテクスチャ・マップにアクセスすること、シャドウイング動作中にシャドウマップにアクセスすること、及び、マルチパス・レンダリング動作中に、カラー値、及び/又は、アルファ値にアクセスすることが挙げられる。簡単のために、メモリ中の画像データを、「テクスチャ」又は「テクスチャデータ」と呼ぶ。しかしながら、ここに述べる方法ならびにシステムは、画素生成中に、メモリから画像データにアクセスする他のタイプにも応用できることを了解しなければならない。

【0116】

図10及び図11に示した実現例は、タイラーに対しテクスチャキャッシュを効率よくロードし、利用するための別法を紹介するものである。この方法の大きな利点は、テクスチャデータを高いレイテンシを有するメモリに保存でき、本システムの性能を損なうことなく、圧縮形式でさえ保存することができる。従って、専用とすることなく、低コストのメモリを、高性能のレンダリング用ハードウェアに実装するように用いることができる。

【0117】

メモリからのテクスチャデータは、「ブロック」と呼ばれる単位ごとにアクセスされ、キャッシュされる。このブロックは、通常、効率的なフェッチや、キャッシュに好適な小さな方形領域である。通常のブロックの大きさは、8×8サンプルである。例えば、テクスチャ・マップの場合では、通常のブロックは、8×8テクセルである。

【0118】

図10は、一実施例において、このようなテクスチャデータのブロックにアクセスする態様を示す機能的ブロック図である。この実施例は、テクスチャデータ要求を含むラスタライザ417からの画素データを、テクスチャ参照データ・キュー418に蓄えることによってレイテンシ問題を解決している。このキューは、テクスチャ参照データ・キュー418がなければテクスチャブロックにアクセスする際に(また、可能であれば、復元する際に)、生じるレイテンシを吸収するに十分なエントリを含んでいるために、レンダリング処理はフル・スピードで実行することができる。例えば、1つのテクスチャブロックをフェッチするのに100サイクルを要し、タイラーが、クロック・サイクル当たり1画素を生成できるとするならば、テクスチャ参照データ・キュー418は、少なくとも100個のエントリを含むことになる。

【0119】

図10に示した装置においてデータの流れは、下記のように進行する。先ず、幾何形状プリミティブが、ブロック416に示すようにラスタライズのためにセットアップされる。セットアップ処理としては、例えば、三角形のような幾何形状プリミティブに対して頂点を読み取ること、及び、その三角形の面を横切ってカラー、深度とエッジの微分を求めること、が挙げられる。この計算によって得られるパラメータを次にラスタライザ417に入力する。

【0120】

ラスタライザ417は、各プリミティブに対して方程式パラメータ・データを読み取り、画素データを生成する。ラスタライザは、テクスチャ座標とフィルタ・データを含む画素データを生成し、このデータを、テクスチャ参照データ・キュー418に蓄える。テクスチャ・フェッチ・ブロック420は、テクスチャ参照データ・キュー418に蓄えられるテクスチャ参照データを読み取り、かつ、メモリ419から適当なテクスチャブロックをフェッチする。

【0121】

本実現例のテクスチャ参照データ・キュー418に蓄えられる画素データは下記を含む。即ち、計算された、画素の宛先アドレス(X,Y)、深度データ(Z)、カバレッジマスク、カラー値と半透明性データ、テクスチャ要求の中心座標(S,T)、及び、テクスチャフィルタ・データである。深度データ、カバレッジマスクのデータは、画素の高度なアンチエイリアシングを望む場合にのみ、テクスチャ参照データ・キューにおいて要求される。隠れ面消去処理やアンチエイリアシングをラスタライザ内で実行する場合、深度データや、カバレッジマスクのデータは、テクスチャ参照データ・キュー418内に保存する必要はない。テクスチャフィルタ・データは、例えば、MIPマッピング用の一定レベルのディテールのパラメータを含んでいてもよいし、或いは、さらに高度なテクスチャフィルタのための異方性フィルタ・データを含んでいてもよい。

【0122】

テクスチャブロック・フェッチ・ユニット420は、データ・キューに蓄えられるテクスチャ参照データを読み取り、メモリ419から対応するテクスチャデータを取り出す。テクスチャ・マップ・アクセスの場合、テクスチャブロック・フェッチ・ユニットは、テクスチャ要求の中心(S,T)とテクスチャフィルタ・データを、テクスチャフィルタ動作を満足に実行するのに必要なブロックのアドレスに変換する。画像データブロックは、最近使用したキャッシュ(LRU)、又は、その他の適当なキャッシュ置換アルゴリズムを用いてフェッチすることができる。メモリアクセスの回数を抑えるために、テクスチャブロック・フェッチ・ユニットは、テクスチャキャッシュ421にすでに蓄えられているテクスチャブロックを追跡し続けており、同じブロックを1回よりも多く要求するのを避ける。この能力によって、高品質のテクスチャフィルタを実行するのに必要なバンド幅を大幅に下げることができる。なぜなら、テクスチャブロックを取り出す際のレイテンシが、画像を計算する時の1回だけしか起こらないからである。

【0123】

テクスチャブロック・フェッチ・ユニットは、タイラーのテクスチャフィルタ・ユニットでまだ必要とされているテクスチャブロックの書き込みすぎを防止するために、抑制機構を備える。このような抑制機構を実行する1つの手法は、各テクスチャブロックと参照カウントを関連させ、テクスチャフィルタ・ユニットが、特定のテクスチャブロックを用いたかどうかを追跡し続けることである。この参照カウントは、ブロックに対するテクスチャ要求を、テクスチャブロック・フェッチ・ユニットが受け取る度ごとに増加し、そのブロックがテクスチャフィルタ・ユニットによって使用される度ごとに減少する。従って、テクスチャブロック・フェッチ・ユニットは、対応する参照カウントがゼロのブロック同士を交換すればよい。

【0124】

抑制機構を実行するまた別の方法として、テクスチャブロック・フェッチ・ユニットからのテクスチャブロック出力のために、テンポラリバッファを割り当てることがある。この方法では、画像ブロックは、最初に、テンポラリバッファに書き込まれる。テクスチャブロック・フェッチ・ユニットが、このテンポラリバッファへの画像ブロックの書き込みを完了した後で、この画像ブロックはテクスチャキャッシュに転送される。画像ブロックは、テクスチャフィルタ・ユニット422に最初に要求された時に、テクスチャキャッシュと交換される。

【0125】

テクスチャ・マッピング動作の場合、テクスチャフィルタ・ブロック422は、テクスチャキャッシュ421からテクスチャサンプルと、さらに、テクスチャ参照データ・キュー418に蓄えられている画素データを読み取り、そのテクスチャサンプル・データから画素カラー値及び、可能であれば、アルファ値を計算する。

テクスチャ・マッピング動作の他にも、この方法は、シャドウイングや、マルチパス・レンダリング動作にも同様に適用できる。例えば、テクスチャ参照データ・キューを用いて、メモリの中にあるシャドウの深度マップを取り出すことができる。また別法として、テクスチャ参照データ・キューは、マルチパス動作のライティング及びシャドウイングで使用されたカラー値、及び/又は、アルファ値を取り出すように用いることができる。テクスチャ・マッピング、シャドウイング、及び、マルチパス動作についてはさらに詳細に以下に述べる。

【0126】

前記の方法で画素データを保存すると幾つかの利点が得られる。1つの大きな利点は、画像データを、あまり特別でない(比較的大きなアクセス時間のものでもよい)メモリに保存することができることである。これは、システム全体のコストを下げる。さらに、テクスチャを含む画像データを、圧縮フォーマットで保存でき、従って、テクスチャフィルタのような高度な画素の処理を実行できるほどに高速でアクセスすることができることである。このため、本システムは、テクスチャデータにアクセスするに当たって、既知の方法に比べて、より低いコストでより向上した性能を発揮することができる。

【0127】

この方法の別の利点は、テクスチャ参照データ・キューが、メモリからどの画像ブロックにアクセスしなければならないかを正確に予測することができることである。そのため、本システムは、メモリアクセスのために必要以上のレイテンシを生じさせない。一旦画像データブロックがテクスチャキャッシュの中に入ったならば、要求される画像ブロックをテクスチャキャッシュに書き込むのに十分なメモリバンド幅とテクスチャ・フェッチのスループットがある限り、テクスチャフィルタ・ユニットは、ラスタライザをフル・スピードで実行することができる。

【0128】

テクスチャ参照を、テクスチャ要求の中心でキューすること、及び、テクスチャ参照データをフィルタリングすることは、テクスチャ参照データ・キューが、同じテクスチャフィルタ重量のままでテクセルをキューした場合よりも、極めて小さくすることができる。

【0129】

図11は、もう一実施例において、メモリから画像データにアクセスするステップを示す機能的ブロック図である。この方法では、幾何形状プリミティブは、キューされ、プリラスタライザ426において、画素生成処理で生じたテクスチャブロック・フェッチ・ユニットのレイテンシをマスクするように処理される。一例を挙げて説明すると、この概念が具体的に明らかになるであろう。平均的なプリミティブが、ラスタライズするのに25サイクルを要し、かつ、メモリからテクスチャブロックをフェッチするのに100クロック・サイクルを要するとするならば、このプリミティブキューは、少なくとも4つ分のプリミティブの長さとなる。ポストラスタライザ427の単純型としてのプリラスタライザは、メモリからアクセスするのに必要な画像データブロックを決める回路を含む。一旦テクスチャデータがフェッチされたならば、ポストラスタライザは、メモリからブロックをフェッチする際に生ずるレイテンシをも生ずることなく、テクスチャデータを用いて画素データを生成することができる。

【0130】

この実現例全体を通ずるデータの流れは下記のようになる。前記の実現例同様、幾何形状プリミティブは、セットアップブロック425で処理され、ラスタライズされる。しかしながら、この特定の実現例では、セットアップブロック425は、前例よりもより多くのプリミティブを蓄えることのできる大きなプリミティブキューを含む。プリラスタライザ426は速やかにこれらプリミティブを、一連のテクスチャブロック・リストに変換し、一連のテクスチャブロック・リストは、プリミティブによってカバーされる全ての画素に対して、それらブロックがポストラスタライザ427によって必要とされる順に、テクスチャフィルタリング要求を満たすのに必要とされるものである。プリラスタライザ426は、ポストラスタライザ427の単純型、又は、前述した別の実施例のラスタライザ417の単純型である。この方法では、プリラスタライザは、テクスチャデータ・アドレスを計算し、かつ、テクスチャ要求を決めるだけでよい。

【0131】

プリラスタライザもテクスチャブロック・キャッシュのモデルを保持し、キャッシュ置換アルゴリズム、例えば、最近使用したキャッシュ(LRU)方式を実行し、テクスチャブロック・キャッシュの大きさを越えないようにする。キャッシュ置換アルゴリズムの一部として、プリラスタライザは、テクスチャブロック・フェッチ・ユニットへの単一のテクスチャブロックに対する繰り返し要求を、ただ1つの要求に圧縮する。

【0132】

テクスチャブロック・フェッチ・キュー428は、テクスチャブロック要求を蓄えるエントリを備える。テクスチャブロック・フェッチ・ユニット429は、テクスチャブロック・フェッチ・キューからのテクスチャ要求を読み取り、メモリ430から適当なブロックを取り出す。

【0133】

ポストラスタライザ427は、セットアップブロック425でキューされたプリミティブをラスタライズし、ある画素位置に対する画素データを生成する。画像データを、画素生成処理中に、メモリからアクセスする必要があれば、ポストラスタライザは、必要なテクスチャブロックがテクスチャブロック・キャッシュ431に転送されるのと同一の速さで、このプリミティブをラスタライズする。ポストラスタライザが、セットアップブロックでキューされたプリミティブをラスタライズし終えると、プリミティブは除去され、入力データ・ストリームからの別のプリミティブと交換される。プリラスタライザ及びポストラスタライザが、画素生成処理において待ち続けて停止することないように、このセットアップブロックは、プリミティブで満たされるキューを保持する責任を有する。

【0134】

前述した別態様の実施例の場合と同様に、テクスチャブロック・フェッチ・ユニット429は、ポストラスタライザ427によってまだ必要とされているテクスチャブロックの超過することを防ぐための抑制機構を含むことが好ましい。前述の2個の抑制機構は、この実施例でも使用できる。特に、画像ブロックがいつ要求され、そして、いつ使用されるかを追跡し続けるように、参照カウントを用いることができる。その場合、参照カウントは、ブロックに対するテクスチャ要求を、プリラスタライザ426が受け取る度ごとに増加し、ポストラスタライザ427が使用する度ごとに減少する。従って、テクスチャブロック・フェッチ・ユニット429は、テクスチャキャッシュのブロック同士を、その参照カウントが0の場合にのみ交換すればよい。

【0135】

また、別法として、バッファを、テクスチャ・フェッチ・ブロック420によるテクスチャブロック出力の一時的保存のために割り当ててもよい。テクスチャ・フェッチ・ブロック420が、このテンポラリバッファへのテクスチャブロックの書き込みを完了すると、そのテクスチャブロックは、ポストラスタライザ427によって要求される場合、テクスチャブロック・キャッシュ431に転送される。ポストラスタライザ427が最初にテンポラリバッファ中のテクスチャブロックを要求すると、そのテクスチャブロックは、テクスチャブロック・キャッシュ431に転送される。

【0136】

この方法にはいくつか利点がある。先ず、テクスチャデータを、あまり専用化されていないメモリに保存しても、高度なテクスチャフィルタをサポートするのに十分な速度でアクセスすることができる。それに関連する重要な利点として、テクスチャデータは、圧縮フォーマットで保存することができ、かつ、画素生成処理で使用の際に復元されることである。

【0137】

この方法のもう1つの利点は、メモリに対する要求が予測できるために、メモリアクセスによるレイテンシを、場面をレンダリングする各テクスチャブロックに対して、ただ一度だけしか生じさせないで済むということである。一旦、最初のテクスチャブロックがテクスチャキャッシュの中に格納されたならば、ポストラスタライザ427は、メモリバンド幅を有し、キャッシュの流れを保持するためのテクスチャ・フェッチスループットを有する限り、フル・スピードで実行することができる。

【0138】

図9Bは、図10に示した本システムの実現例をさらに詳細に図示したものである。図9Bのセットアップブロック381は、図10のセットアップブロック416に相当する。図9Aのセットアップブロック382と違って、この別種実現例のセットアップブロック381は、テクスチャ読み取り要求を生成しない。代わりに、走査変換ブロック395が、テクスチャ参照データを含む画素データを生成する。このデータは、テクスチャ参照データ・キュー399に蓄えられる。

【0139】

図9Bの走査変換ブロック395は、図10のラスタライザのある特異な実現例である。走査変換ブロック395は、Z値、カバレッジマスク、カラー・半透明性データ、及び、テクスチャ座標で表わされたテクスチャ要求の中心を計算する。幾つかのテクスチャ・マッピング動作では、このブロックは、さらにディテールのレベルのデータや、異方性フィルタ・データも計算する。テクスチャフィルタ・エンジン401は、テクスチャ要求と、通常、テクスチャ参照データ・キュー399に保存されているテクスチャフィルタ・データを読み取り、テクスチャキャッシュの中の適当なテクスチャサンプルにアクセスする。このテクスチャデータから、テクスチャフィルタ・エンジンは、テクスチャがどの程度、画素カラー値及びアルファ値に関与するかを計算する。テクスチャフィルタ・エンジンは、テクスチャ参照データ・キュー399の中のカラー値及びアルファ値を、テクスチャからのカラー値及びアルファ値と組み合わせて、画素値を生成し、その画素値を画素エンジン406に送出する。

テクスチャキャッシュ制御装置391、テクスチャ読み取りキュー393、及び、命令メモリ制御装置380は、図10のテクスチャブロック・フェッチ・ユニット420の特異な実現例である。さらに、圧縮テクスチャブロックに対しては、圧縮キャッシュ416と復元エンジン404が、テクスチャブロック・フェッチ・ユニット420の一部となる。

図9Cは、図11に示した本システムのさらに詳細な実現例を示す。この実現例では、図11のブロック425及びブロック426に関連して説明する機能は、セットアップブロック383内部に実装される。特に、セットアップブロック383は、プリラスタライザ426を含む。セットアップブロック383はさらに、追加のプリミティブを含む付加的な頂点制御レジスタ387を含む。そのために、プリラスタライザは、プリミティブを速やかに変換し、テクスチャデータ要求を発することができる。セットアップ・エンジンとプリラスタライザ383は、テクスチャブロックに対する要求を、図9Cに示したテクスチャキャッシュ制御装置391に送出する。

【0140】

テクスチャキャッシュ制御装置391は、要求されたテクスチャブロックが、必要な時には、テクスチャキャッシュ402に入っていることを確かめる。テクスチャ読み取りキュー・バッファは、テクスチャデータブロックに対する要求を読み取り、共用メモリに送る。命令・メモリ制御装置380は、共用メモリへのアクセスを判定するが、さらに、メモリからのデータを蓄えるためのバッファをも含む。テクスチャキャッシュ制御装置391、テクスチャ読み取りキュー393、及び、命令・メモリ制御装置380は、図11のテクスチャブロック・フェッチ・ユニット429の特異な実現例である。圧縮されたテクスチャブロックに対しては、圧縮キャッシュ416及び復元エンジン404が、テクスチャブロック・フェッチ・ユニット429の一部となる。テクスチャキャッシュ制御装置391は、復元エンジン404を介して、圧縮キャッシュ416からテクスチャキャッシュ402へと向かうテクスチャブロックの流れを管理する。

【0141】

走査変換ブロック397及びテクスチャフィルタ・エンジン403は、図11のポストラスタライザの特異な実現例である。走査変換ブロック397及びテクスチャフィルタ・エンジン403は、前述の、図9Aに示した同類と同じように動作する。

【0142】

テクスチャキャッシュ制御装置

テクスチャ・フェッチ動作にとって高いレイテンシを有する環境で、ラスタライズする2つの手法を説明した。次にテクスチャキャッシュ制御装置の特徴を詳細に説明する。

【0143】

テクスチャキャッシュ制御装置方式では、ラスタライザはテクスチャ・マップ・フェッチ制御のレイテンシが短いにも関わらずテクスチャ・マッピング中にフル・スピードで機能することができる。タイラーにおいて、このレイテンシは、共用メモリ(例えばRAMBUS)からの未圧縮データを読み取るのに要する時間と、テクスチャ・マップのブロックを復元するのに要する時間を加算したものである。共用メモリからgスプライトブロックをフェッチし、可能であればこれを復元し、さらにgスプライト空間の画素データをビュー空間(具体的には画面座標)に変換するgスプライト・エンジンに応用される。

【0144】

テクスチャキャッシュ制御装置方式は、時間内にオフセットされるテクセル(又はgスプライト画素)要求の同一のストリームを2つ作成することを基本的に前提としている。最初の(早いほうの)ストリームはいずれのテクスチャデータも戻されることのないプリフェッチ要求で、また第2の(遅いほう)ストリームはテクセルデータを戻すための実際の要求である。この2つのストリームの時間差を、テクスチャデータの読み込みや復元の際のレイテンシが表れなくなるように用いる。

【0145】

上記の時間分離要求を生成させる2つの方法は、(1)ともに単一のプリミティブFIFO(図11及び図9C)からデータを読み出す一対のラスタライザと、(2)画素FIFO(図10及び図9B)がその後に続く単一のラスタライザである。

【0146】

(1)の方法では、第1のラスタライザはプリミティブFIFOの入力側又はその近辺の位置からプリミティブを読み取ってプリミティブのラスタライズを行なうので、テクスチャ要求を作成することができるが、テクセルを受信することや、画素を作成することはない。第2のラスタライザはFIFO出力からプリミティブを取り除いて後で同一の要求を作成し、テクスチャキャッシュ制御装置からテクセルを受信し、画素を作成する。各プリミティブ当たりの画素数と組合わされたプリミティブキューの深度が、2つの要求ストリーム間の潜在的な時間差を決める。

【0147】

(2)の方法では、単一のラスタライザがプリミティブの処理を行ってテクスチャ要求を作成し、部分的に完全な画素データを画素FIFOに出力する。この一部の画素データには、一旦テクスチャ要求が受諾された後で画素の計算を完了させるのに必要なデータ全てが含まれる。画素FIFOの出力側には、部分画素が全てあり、これを元に同一のテクスチャ要求のストリームが作成され、テクセルを受信し、完全画素を作成する。画素キューの深度が、2つの要求ストリームの潜在的な時間差を決める。

【0148】

テクスチャキャッシュ制御装置

テクスチャキャッシュ制御装置には、仮想キャッシュと物理キャッシュの2つの概念キャッシュがある。仮想キャッシュは最初の(プリフェッチ)要求ストリームに関連しており、キャッシュエントリに直接伴うデータは有していない(このキャッシュへの要求によりデータが戻ることはない)。物理キャッシュは第2の(実際の)要求ストリームに関連しており、各キャッシュエントリに伴う実際のテクスチャデータを有している(従ってデータは要求元に戻る)。これらのキャッシュのエントリ数は同一である。

【0149】

仮想キャッシュは物理キャッシュの後の内容の制御と追跡を行なう。従って、その要求ストリームのいずれの位置でも、物理キャッシュが(後に)その要求ストリームの中の同じ相対位置で有するのと同じ一対のキャッシュキーとエントリを有している。

【0150】

要求を受けると(新規の「キー」)、仮想キャッシュがその現在のキーの組に対して比較を行なう。要求されたキーが仮想キャッシュになければ、キャッシュ置換動作が行われる。仮想キャッシュ置換動作では、1)(LRU又はその他のアルゴリズムによって)置換するエントリを選択し、2)そのエントリに対するキーを置換し、3)(メモリと)復元システムを起動してそのキーに関連するデータのフェッチと復元を行なう。図9B及び図9Cに示す特定の方法では、復元サブシステムは、命令・メモリ制御装置380、圧縮キャッシュ416、復元エンジン404から構成される。

【0151】

復元サブシステムの出力は、後に物理キャッシュのエントリ(例えばテクスチャキャッシュ402)の内容となるテクスチャデータのブロックである。図9B及び図9Cに示すタイラーにおいて、復元サブシステムが行なう処理は順序が保たれているマルチエントリパイプラインで実行される。

ちなみに要求されたキーがすでに仮想キャッシュに存在していた場合、関連データは第2の要求ストリームから要求があった時には物理キャッシュに存在しているので何も実行されない。

【0152】

物理キャッシュに要求があると、同様のキーの比較を行って要求されたデータがすでにキャッシュに存在しているか確認する。同一のキーが見つかると、関連データが戻される。同一のキーがない場合は、復元サブシステムが出力する次のデータが確実に所望のデータとなる。なお、この新規データに置換される物理キャッシュは、仮想キャッシュ制御装置で計算されたキャッシュエントリの「目標」インデックスに基づき仮想キャッシュから命令を受け、要求されたデータと共に復元サブシステムを通過する。

【0153】

この方式を適切に機能させるには、復元サブシステムと物理キャッシュとの間のインターフェイスに対してフロー制御を行なう必要がある。復元されたデータをすぐに物理キャッシュの中の目的のエントリに上書きすることが可能な場合、そのキャッシュエントリの以前の内容に関連するもの全てが完全にそろっていないことが考えられる。(ちなみに、物理キャッシュ制御装置も復元サブシステムがデータを出力するまで待機しなければならない。)

【0154】

前のエントリの内容を上書きする前に新しいエントリが要求されるまで待機することによって、このフロー制御は行われる。テクスチャキャッシュへの新規データ書き込みは、それが必要となる最後の瞬間まで常に延期される。

この置換は必要となるときまで延期されるので、物理キャッシュへのデータ書き込みに要する時間により、レイテンシは第2の要求ストリームを制御する処理に加算される。このレイテンシを低減させる2つの方法は次の通りである。

最初の方法では、物理キャッシュのバッファデータを2倍にする。これにより、復元サブシステムはそのダブルバッファ側に各エントリのデータを即座に書き込み、また物理キャッシュ制御装置はバッファスワップ(通常、高速)を行ってデータをそのキャッシュ側にマップさせることが可能になる。書き込まれるエントリに空きがなく、まだスワップされていない場合は、復元サブシステムは待機するのみである。ちなみに、仮想キャッシュ制御装置が使用するキャッシュ置換アルゴリズムは同じエントリに繰り返し書き込みを行なう傾向があるので、キャッシュエントリへの書き込みを「拡張」する必要がある。

【0155】

第2の方法では、複数の「キー化した」エントリの他に1つ又は複数の「追加」エントリを物理キャッシュに設ける。キー化したエントリの数は、存在するキャッシュキーの数と同じであり、仮想キャッシュのエントリ数と一致する。追加エントリの数は、アンマップされた(即ち、現在データの書き込まれていない)エントリの数を表している。このようなエントリの総数は、物理キャッシュのデータエントリの総数となる。

第2の方法では、キャッシュエントリは全て(キーに関連して)何度もアンマップ又はマップされる。アンマップされたエントリの集合は、復元サブシステムがデータの完全ブロックを書き込むエントリのFIFOを形成している。分離FIFO構造は、このようなアンマップされたエントリに関連する目標インデックスのために維持される。物理キャッシュへの要求があったが一致するキーがない場合は、アンマップされたエントリのキューの最初のエントリが目標となるインデックスにマップされてそのキーに対応させられる。置換されたエントリはアンマップされ、アンマップ状態のキューの最後に配置される(空)。

【0156】

キャッシュキー生成

この方式は同一の要求ストリームが2つ生成されることを基本的に前提としている。しかしながら、このような要求に対応する特定のキーは同一である必要はない。

第1の(早いほうの)要求ストリームを形成するキャッシュキーは、テクスチャデータの読み出しとその後の復元を制御するのに使用される。このようなキーは、要求されたデータ(メモリアドレス等)に直接関連していなければならない。

【0157】

第2の(遅いほうの)要求ストリームを形成するキャッシュキーは、最初のストリームの内容と正確に一致する必要はない。両者の間に他と異なる1対1のマッピング関係が成立していることのみ必要となる。これは第2のストリームのキーが既存のキャッシュエントリのマッチングのためだけに使用され、データフェッチ動作には使用されないためである。ここにおいては、新しいデータが物理キャッシュにマップされたときに物理キャッシュのキーとキャッシュエントリとの間の関係が成立し、また対応するエントリのインデックスが仮想キャッシュによって計算されて復元サブシステムを通過するということが重要である。

【0158】

このことは、ストリームのキーが他と異なってさえすれば「正確」である必要はないため、第2の要求ストリームキーを生成する処理の制御を簡素化するのに利用できる。

【0159】

図12Aは画像処理ボード174上のgスプライト・エンジン436を示すブロック図である。gスプライト・エンジン436は収集したgスプライトから出力されるグラフィックスを生成する。gスプライト・エンジン436はタイラー・メモリ・インタフェースユニットとのインターフェイスを確立して、共用メモリの中のgスプライト・データ構造にアクセスする。gスプライトはgスプライト・エンジンによって変換され(回転、縮小拡大など)、合成バッファに送られて他のgスプライトから成る画素と合成される。

【0160】

インターフェイス制御部438は、タイラーを介してgスプライト・エンジンと共用メモリとの間にインターフェイスを確立するのに使用される。このブロックはFIFOを有しており、メモリからのアクセスがgスプライト・エンジンで分散される前にバッファする。

【0161】

表示制御処理装置440は、ビデオ表示の更新制御に使用される。これは、ビデオ表示のリフレッシュを制御し、またgスプライトアクセスを制御するのに必要なタイミング信号を生成するビデオタイミングジェネレータを有している。また、このブロックはgスプライト表示データ構造をトラバースして、所定の32走査線帯に対して読み出す必要のあるgスプライトを決定する。

【0162】

gスプライト・ヘッダ・レジスタ442は、画像処理アドレスジェネレータ(ラスタライザ)454とgスプライトフィルタエンジン456が使用するGスプライト・ヘッダを保存して、各gスプライトでの変換を決定する。またgスプライト・ヘッダデコーダ444もこのレジスタを使用して、各バンド幅でgスプライトを与えるに必要なブロック(この場合、8×8圧縮ブロック)を決定する。

【0163】

gスプライト・ヘッダデコーダ444は、各gスプライトからのブロックが32走査線帯で可視状態になるブロックを決定し、gスプライト読み出しキュー446に転送されるブロック読み出し要求を生成させる。このブロックも、gスプライト・エッジ方程式パラメータを使用してgスプライトを現在のバンド幅にクリップする。この処理を以下に詳しく説明する。

【0164】

gスプライト読み出しキュー446はgスプライトブロックの読み出し要求をバッファする。本実施例では、このキューは16個のブロックの要求を記憶している。

gスプライト・データアドレスジェネレータ448は要求されたgスプライトブロックのメモリのアドレスを決定し、gスプライト読み出し要求をインターフェイス制御部に送信する。gスプライト・データアドレスジェネレータ448はメモリ管理ユニットを有している。

【0165】

共用メモリ216(図4A)から取り出した圧縮データは、圧縮キャッシュ458に一時的に保存できる。

復元エンジン450には2つのデコンプレッサを備えており、一方は三次元のgスプライトや画像等の連続したトーンの画像に対してDCTに基づいたアルゴリズムを実行し、他方はデスクトップ画素データに対してロスレス・アルゴリズムを実行する。DCTに基づいたアルゴリズムは2つの並行した圧縮ブロックによって実現され、双方のブロックとも、各々のクロック周期ごとに8個の画素要素(即ち、2画素)を生成することができる。

【0166】

gスプライト・キャッシュ452は、8×8の16ブロックに対して復元されたgスプライト・データ(RGB∝)を保存する。データは16個のgスプライト画素がクロック周期ごとにアクセスされるよう構成される。

画像処理アドレスジェネレータ(ラスタライザ)454は、特定のアフィン変換に基づいて各gスプライトを走査し、また各画素のフィルタパラメータを計算するのに使用される。gスプライト・キャッシュアドレスはgスプライト・キャッシュ452のgスプライト・データにアクセスし、それをgスプライトフィルタエンジン456に送るために生成される。画像処理アドレスジェネレータ(ラスタライザ)454も合成バッファを制御する。

【0167】

gスプライトフィルタエンジン456は、フィルタパラメータに基づいて画素位置の画素のカラーとアルファを計算する。このデータは合成バッファに転送されて合成される。このブgスプライトフィルタエンジン456は、画素位置でのgスプライトs−t座標に基づいて4又は16画素フィルタ・カーネルを計算する。例えば、フィルタはバイ・リニア又はさらに優れた余弦の和の関数でよい。16画素フィルタ・カーネルは、バイ・リニア補間法よりも細かなフィルタリングが可能なネガティブローブを有することができる。gスプライトフィルタエンジン456はクロック周期ごとに合成される4つの新しい画素を生成する。これらの画素は2×2パターンで配列される。

【0168】

gスプライト・エンジン436はタイラー200と合成バッファ210とのインターフェイスを確立する。制御信号はビデオタイミングとDAC212へのデータ転送を制御する。

図12Bはgスプライト・エンジン436の他の構成を示すブロック図である。これには、プリラスタライザ449と画像処理アドレスジェネレータ(ラスタライザ)454の双方が含まれているので、gスプライト・エンジンはgスプライト画素データのブロックの検索や復元でレイテンシを生じさせることなくgスプライト空間からの画素データを画面空間に変換することができる。この構成で2つのラスタライザを用いる方法は図11及び9Cを参照して上記に説明したとおりである。

【0169】

gスプライト・エンジン436におけるブロックの動作は、2つのラスタライザを使用してテクスチャデータのブロックをフェッチする方法を採用している点以外は、図12Aで説明したものとほぼ同じである。この構成(図12B)では、gスプライト・ヘッダデコーダ444がgスプライト・ヘッダ・レジスタ442を読み出し、gスプライトを現在の表示バンドにクリップし、さらにgスプライトキュー447にgスプライトを移してラスタライズを行なう。データアドレスジェネレータ又は「プリラスタライザ」449はgスプライト・ヘッダの所定のアフィン変換式に基づいて各gスプライトを走査し、gスプライト・キャッシュ制御部451に対して読み出し要求を発する。テクスチャキャッシュ制御装置に関連して上記に説明した方法を用いれば、画像処理部455が、gスプライト・データのブロックを必要とするときに、その要求されるgスプライト・データが、gスプライト・エンジン436にあり、且つ、特にgスプライト・キャッシュ452にあることを、gスプライト・キャッシュ制御部451によって確実にする。この制御は、復元エンジン450を介しての圧縮キャッシュ458からgスプライト・キャッシュ452へのgスプライト・データのブロックの流れを管理する。読み出しキュー453は共用メモリシステムへのgスプライト・データブロックの要求をバッファする。またインターフェイス制御部438は読み出しキュー453の要求を読み出し、共用メモリへのアクセスを制御し、gスプライト・データブロックを圧縮キャッシュ458に入れる。

【0170】

gスプライト・エンジンの復元サブシステムは圧縮キャッシュ458と復元エンジン450を有している。gスプライト・キャッシュ制御部451は、テクスチャキャッシュ制御装置に関連して上記に説明したこの復元サブシステムを介してgスプライトブロックの流れを制御する。

【0171】

画像処理アドレスジェネレータ(ラスタライザ)454は、gスプライト・ヘッダの所定のアフィン変換式に基づいて各gスプライトを走査し、各画素のフィルタパラメータを計算する。また、gスプライト・データのgスプライト・キャッシュアドレスも生成し、これをgスプライトフィルタエンジン456で使用できるようにgスプライト・キャッシュのキャッシュアドレスマップへ送る。キャッシュ構成の一例では、キャッシュアドレスマップはアクティブとなる14画素ブロックと復元エンジンから書き込みされる2つのブロックを選択する。

【0172】

gスプライトフィルタエンジン456は、gスプライト空間の画素位置にあるカラー及びアルファデータを画面空間にマップする。この方法では、2x2又は4x4のフィルタ・カーネルを用いて、画面空間の画素位置にある画素値(カラー又はカラーとアルファの双方)を計算する。合成バッファ制御部457は、画素値、この場合は1クロック周期当たり4画素を合成バッファに送る。合成バッファ制御部457は合成バッファからのレディラインを監視し、gスプライト・エンジン436が合成バッファをオーバーランさせないようにする。画像処理アドレスジェネレータ(ラスタライザ)454は合成バッファ制御部457を制御する。

【0173】

図13は、画像処理ボード174の合成バッファ480を示すブロック図である。合成バッファ480は、gスプライト・エンジンからのgスプライト・データを合成してDAC212へ転送するディジタルビデオデータを生成するのに使用する専用メモリ機器である。合成バッファは一度に32本の走査線で動作する。1つの32走査線帯でgスプライトを合成する間に、前の32本の走査線が表示される。

【0174】

合成ロジック482は、走査線バッファに書き込む画素値を計算する。これは、現在走査線バッファに保存されている画素値と合成バッファに書き込まれている画素値とを混合させることで実行される。この操作は以下に詳しく説明する。一構成例では、合成ロジックが各クロック周期で画素についての4つの並行動作を実行する。

【0175】

メモリ制御部484はアドレスの制御とメモリバンクのサイクリングに使用される。アドレス情報は、通常のDRAMを使用するときのように行と列のフォーマットで送られる。

アルファ・バッファ486は、1344×32画素のそれぞれに対して8ビットの数値を有している。メモリは、連続する4つの画素が各クロック周期で読み出し、又は書き込みされるように構成されている。アルファ・バッファは、32走査線帯の切り替えの間にバッファを迅速にクリアする高速クリア・メカニズムも有している。

【0176】

2つの独立した走査線バッファ488が使用される。走査線バッファは1344×32画素のそれぞれに対して3種類の8ビットカラー値を有している。メモリは、連続する4つの画素が各クロック周期で読み出し、又は書き込みされるように構成されている。一方のバッファは、あるバンドの画素データをDACに転送するのに使用し、他方のバッファは、次のバンドの画素を合成するのに使用する。そのバンド処理が一旦終了すると、その機能はスワップされる。

マルチプレクサは2つの走査線バッファ488のうちいずれかからのデータを選択し、画素表示データをDACに送信する。マルチプレクサは32本の走査線ごとにバッファの切り替えを行なう。

【0177】

合成バッファ480は、gスプライト・エンジン204とのインターフェイスを確立し、画像データをDAC212へ転送する。

図14は画像処理ボード174上のDAC 514を示すブロック図である。DAC 514は、現在市場に一般的に出回っているRAMDACに共通する基本機能を実行する。DACは内部制御レジスタを読み書きし、ビデオ制御信号をパイプライン処理するロジックを有している。その他の機能ブロックについては、以下に説明する。

【0178】

画素データルーティングブロック516は合成バッファからの画素データのルーティングを制御する。通常の動作モードでは、このデータは画素速度で3つのチャネルのそれぞれのカラーLUT 518に送られる。このブロックもDSPからデータを再び読み出して診断することが可能である。

ステレオ画像スプリッタ520は、ヘッドマウント表示システムを用いて立体表示される2つのビデオ信号を支援する。このモードでは、2つのビデオチャネル(522,524)が合成バッファから交互配置されており、DAC 514によってスプリットされなければならない。ステレオ画像スプリッタ520はDAC 514でこの機能を実行する。通常の単一チャネルモードでは、LUTデータが第1DACに直接送られる。

【0179】

その他、単一のビデオ出力を生成するようDAC 514を構成することも可能である。DACは、単一のビデオ出力と共に、走査線インターリーブフォーマットを使用して立体表示を作成することが可能である。この場合、一方の目に対する走査線に、他方の目に対する走査線が続く。結果として生成されたビデオストリームは640x960等のフォーマットを有しており、例えばこれは640x480の画像を表している。

【0180】

クロックジェネレータ526はビデオクロックとオーディオクロックを生成する。これらのクロックは2つの位相固定のクロックジェネレータによって生成され、同期ずれを除去する。クロックジェネレータもメディアチャンネルからの制御信号に従い、画像処理ボードを外部同期ソースに同期させることが可能である。

【0181】

本システムの構造と動作を上記に説明したが、次にシステムの構成部分と特徴について詳細に説明する。まず、上記に説明した概念を実行するためにシステムで使用されるデータ構造を説明する。

【0182】

チャンキング

RAMに大容量のフレームバッファとZバッファを使用してカラー値、深度値、各画素のその他の情報を記憶する従来のグラフィックシステムとは異なり、このシステムはある1画面の中のオブジェクトを「チャンク」と呼ばれる画像領域に分割し、オブジェクト幾何形状をこのようなチャンクに個々にレンダリングする。実施例において、オブジェクトはgスプライトで表示される。gスプライトはチャンクにサブ分割され、チャンクは別個に表示される。この説明は幾つかの特定の実施例について言及しているが、チャンキングは本発明の範囲から逸脱せずに様々に応用することができる。

【0183】

チャンキングの概念を、図例を挙げて説明する。図15Aに示すように、境界ボックス548と呼ばれるボックスで囲まれているグラフィック画面のオブジェクト546は、gスプライト552という画像領域に表示される。境界ボックスを回転、拡大・縮小、拡張、その他の変換(例えばアフィン変換)を行い、画面領域にgスプライトを作成してもよい。境界ボックスが一度作成され、境界ボックスが32画素境界(即ち、チャンク境界)554に収まらないのであれば、境界ボックスをオブジェクトの周囲でX及びY方向に拡張して32画素チャンク・サイズの整数倍になるようにする。図15Bのオブジェクト550から分かるように、図15Aに示すオブジェクト546を囲む境界ボックスは図15Bの32×32画素境界に拡張される。gスプライトはレンダリングされる前に32×32画素「チャンク」556にサブ分割される。しかし、チャンク・サイズはこれよりも小さい又は大きいものを用いることもできるし、また他の形状のチャンクも使用できる。しかし、矩形、より好ましくは四角形のチャンクを図示する。

【0184】

図15Cに示すように、グラフィック画面581は重なり合ったオブジェクト(560,562)を複数有している。これらのオブジェクトは境界ボックスで囲まれており、gスプライト(564,566)に割り当てられる。図15Cの境界ボックスは32画素倍にすでに拡張(及び回転、縮小拡大、その他の変換)されており、32×32チャンク568が生成される。しかし、図15Cから分かるように、gスプライトとそれに対応する32×32画素チャンク境界570は32画素画面境界に正確に配列されないので、チャンクを行っている間にさらにgスプライトを操作してgスプライトが画面空間に収まるようにしなければならない。

【0185】

チャンキングを利用してレンダリングされるgスプライトを作成する1つの方法は、個々のオブジェクト幾何形状を含む小さな個々のgスプライトを複数作成及びレンダリングする代わりに、複数のオブジェクトを組み合わせてより大きな合成gスプライトを作成することである。gスプライトを組み合わせるとレンダリングの際の処理時間が短くなり、また組み合わせたオブジェクトがグラフィック画面の中で頻繁に変わらないのであればこの方法は極めて好ましい。gスプライトを作成する別の方法は、複雑な幾何形状を有するオブジェクトの成分をターゲットとし、これらの複雑な幾何形状成分を複数のgスプライトにサブ分割することである。このようにサブ分割を行なうと処理時間が長くなってしまうおそれがあるが、頻繁に変化する特定の複雑なオブジェクトの出力解像度を向上させることができる。オブジェクトによっては、これら技術を組み合わせて使用してもよい。

【0186】

例として、腕を様々なサイズの複数のスパイクでカバーされているビデオゲームのキャラクタを挙げる。この場合、腕は頻繁に動くものとする。キャラクタの体、頭、その他の部分は頻繁には動かないので、より大きな合成gスプライトに組み合わせることができる。しかし、スパイクでカバーされており、複雑な幾何形状となり、また頻繁に動くキャラクタの腕は、出力解像度を向上させるために複数のgスプライトに分割される。この場合、そのような組み合わせとサブ分割の双方を用いる。このようなキャラクタを図示するのは容易ではなく、また実用的ではないので、より単純なオブジェクトである「コーヒーカップ」を用いてそのような組み合わせとサブ分割を図示する。

【0187】

図16Aは「コーヒーカップ」を表している。この「コーヒーカップ」は実質的に複数の別個のオブジェクトから構成されている。例えば、「コーヒーカップ」は実際にカップ容器と、カップ取っ手と、ソーサーと、カップから立ち上る湯気とで構成されているように見える。図16Aに示すように、1つの方法は個々のオブジェクトを組み合わせてより大きなgスプライト(即ち、「コーヒーカップ」)にするものである。もう1つの方法は、図16Bに示すように、「コーヒーカップ」を複数の小さなオブジェクト(例えばカップ容器、カップ取っ手、ソーサー、湯気)にサブ分割してそれぞれ小さなgスプライトを作るものである。また図16Bは複雑な配置のオブジェクトをサブ分割する方法も示している。

【0188】

図16Aに示すように「コーヒーカップ」574を1つの単純なオブジェクトとすると、オブジェクトの各構成部分(例えばカップ容器、カップ取っ手、ソーサー、湯気)を組み合わせて1つの大きなgスプライトを作成することができる。この場合、境界ボックス576でオブジェクトの周辺を囲み、オブジェクトを画面空間に変換して1つの大きなgスプライトを作成する。画面空間の32×32画素の境界内に収まるgスプライトを作成するために、境界ボックスを回転、拡大・縮小、拡張、その他の変換をさせてもよい。その後、gスプライトは複数の32×32画素チャンク578に分割される。

【0189】

gスプライトをチャンクに分割する1つの方法は、オブジェクトに含まれる幾何形状を全てつなぎ合わせてチャンクにその幾何形状を置くというものである。別の方法では、問題のチャンクを使用する幾何形状の全てを記録しているチャンクをつなぎ合わせる。図に示す実施例では後者の方法を使用しているが、前者やその他の方法も使用できる。図16Aから分かるように、複数のチャンクが空の状態になる(即ち、いずれのオブジェクト幾何形状もチャンクを使用していない)。後で説明するが、これらのチャンクはレンダリングが行われている間は無視される。

【0190】

次に、「コーヒーカップ」を1つの複雑なオブジェクトとした場合、図16Bに示すようにオブジェクトは処理されて複数の小さなgスプライトを作成するより小さなオブジェクト構成部分にサブ分割される。例えば、オブジェクトの「コーヒーカップ」は、取っ手のないカップ容器579と、カップ取っ手580と、ソーサー581と、湯気582というサブオブジェクトから構成される。各下位オブジェクトはそれぞれ583−586に示すように境界ボックスで囲まれて、4つのgスプライトを形成する。4つのgスプライトを含む「コーヒーカップ」も、587で示すように境界ボックスで囲まれる。画面空間の32×32画素境界に収まるgスプライトを作成するために、各境界ボックスを回転、縮小拡大、拡張、その他の変換(例えば、アフィン変換)させてもよい。次に各gスプライトは32×32画素チャンクに分割する。境界ボックス587もチャンクに分割させて、レンダリングの際に無視される空のチャンク588を有するようにさせる。しかし、この境界ボックスのチャンクは図16Bに図示されていない。

【0191】

チャンキングにより、グラフィック画像を単一のフレームとしてレンダリングするわけではなく、後にフレーム又はビュー空間に統合される一連のチャンクとしてレンダリングする。現在描かれている画像の32×32画素チャンクを交差する単一のgスプライト内のオブジェクトのみをレンダリングする。チャンキングにより、フレーム及びZバッファはメモリの小さな物理サイズとでき(即ち、上記に説明した従来のグラフィックシステムよりもはるかに小さなメモリを使用できる)、使用されるメモリの使用頻度が上がり、メモリのバンド幅が増大する。また、チャンク・サイズが小さいことは、フレーム及びZバッファが大きいと効率的に応用することができないような、さらに高度なレンダリング技術を使用することができるようになる。

【0192】

チャンクのレンダリングはタイラーで実行される。しかし、レンダリングは他のハードウェア構成要素上、又はソフトウェアを使用しても実行できる。タイラーチップのVLSIメモリは、現在レンダリングされているフレームの小さなチャンク(32×32画素)を保存するのに使用される。オンチップVLSIメモリは、外部RAMよりも極めて高速でメモリバンド幅も広い。しかし、チャンキング処理が行われるために、フレームバッファ及びZバッファ全体を保存する大量のメモリは不要になる。タイラー内の内部メモリは現在のチャンクの処理のみを行い、後続するチャンクの各々を処理するために繰り返し使用される。そのため、使用可能な内部メモリはグラフィックレンダリング中に頻繁に使用される。

【0193】

また、内部VSLIメモリを使用すると、オフチップ通信や、従来のフレーム及びZバッファに必要な大容量外部メモリに対する読み出しや書き込み動作によるオーバーヘッドが原因で、通常生じるピンドライバの遅延を除去することができる。また、図に示す本実施例では後続するチャンクが計算される前に32×32画素チャンク全体が完全にレンダリングされるので、チャンク・サイズが小さいと、外部メモリの大部分に保存されるフレーム及びZバッファ全体よりもチャンクのほうがより高度なアンチエイリアシング(例えばフラグメントバッファ)及びテクスチャリングを実行することができる。さらにチャンク・サイズが小さい場合、後で詳細に説明する画像圧縮技術を使用する際に便利である。

【0194】

チャンク及び解析されたフラグメントに、交差するポリゴンを全て描出した後、カラーや不透明度を含む画素データが、タイラーチップにおいて圧縮されて、外部メモリに転送される。

【0195】

図17A及び17Bはグラフィック画面のチャンクへの分割方法の概略を詳細に示している。まず、1つ以上の境界ボックスが各オブジェクトに対して作成される(592)(図17A)。オブジェクトが複雑な幾何形状(例えば細かい碁盤目状など)を有する場合(594)、複数の境界ボックスが作成されて(複数のgスプライトを作成するために)、オブジェクトの複雑な各構成部分を囲む(596)。オブジェクトが複雑な幾何形状を有しない場合は、単一の境界ボックスを使用してオブジェクトを囲み、gスプライトを作成することができる(598)。しかし、オブジェクト幾何形状が複雑であれば、単一の境界ボックスが、オブジェクトの複雑な成分を囲むために生成された複数の境界ボックスをも囲むことになる。単一又は複数の境界ボックスが、32画素の整数倍でないならば(600)、このような境界ボックスを32画素の整数倍になるようX又はY方向(又は双方向)に対称に拡張する。次に、オブジェクト(幾何形状が複雑なときはオブジェクト成分)を境界ボックスでセンタリングする(602)。これを図15B及び15Cのgスプライトで示す。拡張は対称に行なうのが好ましいが、必ずしもそうする必要はない。拡張が対称であると、単一のgスプライトにおけるチャンク間の処理のバランスが良くなる。

【0196】

再び図17において、gスプライトは32×32画素チャンクに分割される(604)(図17B)。明らかなように、チャンクはビュー空間の固定位置にあるのではなく、チャンクされたオブジェクトの位置によってはアドレス呼び出しが可能な可変位置に置かれる。gスプライトをチャンクに分割した後、チャンクの処理を行なう。チャンクのレンダリングが完了すると(606)、処理は終了する。チャンクのレンダリングが完了しない場合、まず後続するチャンクが空なのか確認した後このチャンクの処理を始める(608)。チャンクが空の場合、処理は行われず、後続するチャンクの確認が行われる。チャンクが空でない場合は、チャンクを使用しているオブジェクト全てが処理されるまでチャンクのレンダリング(610)をタイラーで続ける。この処理は、各gスプライトの全チャンクと全gスプライトの処理が完了するまで続けられる。

【0197】

gスプライトのサイズは画面の総領域のパーセンテージで表される。背景のgスプライトは極めて大きいが、通常、画面の他の構成部分は画面の総領域よりも小さい。チャンキングの性能はgスプライトのプリミティブの画面空間のサイズによって変わる。そのため、gスプライトの作成に使用するオブジェクトのデータ入力ストリームを適切に調整(例えばキュー)する必要がある。オブジェクトデータ入力ストリームを適切に調整すると、オブジェクトの処理をより高いバンド幅で実行することができ、またシステムのスループットも上昇する。

【0198】

このシステムはコマンドストリームキャッシュを使ってオブジェクトのデータ入力ストリームをキャッシュしている。コマンドストリームキャッシュを使用してgスプライトの全内容をキャッシュし、また全てのチャンクとそれに対応するキャッシュに保存されているgスプライトの関連する幾何形状を繰り返し使用することができる。

またキャッシュは選択キャッシングにも使用できる。例えば、幾何形状プリミティブが所定数のチャンクを使用するときに、これらのプリミティブが自動的にキャッシュされるよう閾値を決める場合である。キャッシュの使用が可能であれば、仮想チャンキングを行なうことができる。仮想チャンキングでは、それぞれが仮想チャンクであるN×Mチャンクの領域に相当するチャンクバケットを作成する。仮想チャンキングにより、gスプライトの内容と幾何形状のサイズに合った仮想チャンクの適応サイズ設定を行なうことができる。

【0199】

キャッシュは修正画面・グラフキャッシングにも使用できる。画面の静的部分をキャッシングして参照するのではなく、キャッシングを行って間接的に画面の動的部分を参照する。例えば、やや複雑な幾何形状のカッコウ時計を含むgスプライトについて考えてみる。時計そのものは極めて複雑であるが、唯一動く部分は鳥、2つのドア、2本の針である。さらに、各幾何形状は、固定されており変化することはない。従って、時計をレンダリングすると、6本の木は静止状態で、また6つの部分が変換される(即ち、時計、鳥、2つのドア、2本の針)。キャッシュの容量が十分大きければ、画面グラフ全体をコマンドストリームに変換する。レンダリングの際には、現在の変換部分はキャッシュされたコマンドストリーム上にパッチされ、その後コマンドストリームはgスプライトの全チャンクに対して発せられる。コマンドストリームのパッチ部分のサイズはレンダリングしても変わらない。さらに順応性ある方法としては、キャッシュした静止画面グラフに呼び出しコマンドを挿入するというものがある。レンダリングの際は、動的部分が可変サイズのメモリに書き込まれ、キャッシュされる。このような動的部分のアドレスは、静止コマンドストリームの対応する呼び出しコマンドにパッチされる。この方法は、動的コマンドのサイズをレンダリングごとに変えることができるため、順応性に優れている。従って、この場合はメモリにキャッシュされたコールバック方法が効果的である。カッコウ時計の例では、6つの変換部分を書き込んで場合によっては鳥の幾何形状を呼び戻すので、ドアが閉じられる場合に鳥部分は空になる。この方法は、バスのバンド幅に対しては極めてコンパクトで、画面グラフを迅速に指定方向に移動することが可能になる。

【0200】

キャッシュメモリに制限があっても、幾何形状や属性によっては何度レンダリングしてもキャッシュされた状態を保つことが可能なものもある。例えば、カーレーシングゲームの場合、車体の幾何形状をキャッシュすると、全体的に時間を大幅に節約することができる。同様に、共通の属性状態(又はサブ属性の状態)は複数のgスプライト又は単一のgスプライトをレンダリングする際に何度も利用される。上記に述べたように、チャンキングでキャッシュを使用すると、時間が大幅に節約される。しかし、gスプライトの各使用チャンクに対してコマンドストリームを迅速に作成することにより、コマンドストリームをキャッシュすることなしで適切なチャンキング性能を実現することができる。

【0201】

図9A〜9Cに示すタイラーの実現例では、複数のチャンクを並行処理装置で同時に使用して計算負荷を共有するのではなく、チャンクを順次使用して1つの処理装置上でフレーム全体をレンダリングする。あまり好ましくはないが、チャンクの逐次又は並行処理を組み合わせて行なうことも可能である。チャンクを完全並行処理する場合、画面上を移動するオブジェクトに対してはそれが移動したときに固定のチャンキング処理を行なうことが必要になる。しかし図に示す本発明の実施例においては、チャンクを逐次処理しているので、オブジェクトはgスプライトのチャンク境界に固定される。従ってオブジェクトが画面上を移動してもチャンキングを行なう必要はない。またチャンクを並行処理でレンダリングしても、チャンクを逐次的にレンダリングする場合のような、高度なアンチエイリアシング及びテクスチャリング方法を各チャンクに応用することはできない。32×32画素チャンク全体は後続するチャンクが計算される前にレンダリングされて即座に圧縮されるので、チャンク・サイズと順次レンダリングは画像圧縮技術にとって極めて重要である。

【0202】

画像の圧縮は、少ないデータで画像を表示し、保存コスト及び/又は送信時間及び送信のコストを減らすために行なう。適切な方法で画像を再構成できる場合、画像を表示するのに必要なデータが少ないほどコストをより下げることができる。また、元の画像を正確に再生するのではなく、元の画像に近づけることでさらに効果的な圧縮を行なうことができる。圧縮量が多くなると、最終画像もより元の画像に近づく(「損失の多い圧縮」)。

【0203】

チャンキングの処理そのものは圧縮技術である。オブジェクトは複数の32×32画素チャンクから作成される1つ以上のgスプライトを使って元の画像に接近させられる。実際のオブジェクトはgスプライトを使って元の画像に近づけ、レンダリングされたgスプライトから再構成される。元のオブジェクトの再構成は、オブジェクトをgスプライトに分割してチャンキングすることでどれほど効果的に元の画像に近づけたかによって変わる(例えば、上記の複雑なオブジェクト幾何形状の分割技術)。

【0204】

各32×32チャンクも画像圧縮技術を使って圧縮される。圧縮された32×32画素チャンクは、使用可能な内部メモリの小さな領域の中であまり多くの空間を占領することはない。32×32画素チャンクは、離散コサイン変換(DCT)を使用する画像圧縮技術で共通して使用されるサイズである16個の8×8画素チャンクに分割される。

【0205】

ある方法では、タイラーの圧縮及び復元エンジン、及びgスプライト・エンジンの復元エンジンは損失の多い圧縮/復元形式とロスレスの圧縮/復元形式の双方をサポートしている。損失の多い形式には、RGBからYUVへのロスレスのカラー変換、DCT、均一又は知覚量子化、エントロピーコーディング(ランレングス及びハフマンコーディング)がある。ロスレス形式には、RGBからYUVへのカラー変換、予測ステージ、損失の多い形式でも実行されるエントロピーコーディングがある。

【0206】

メモリの必要性を大きく減らしてチャンキングによってグラフィック画像を処理するために、図示の実施例では小さなZバッファを使用している(例えば4キロバイト(kb))。特に、この方法でのZバッファは4kbよりもわずかに小さいが、精度のビット数を変化させることが可能である。しかし、他の大きなサイズ又は小さなサイズのZバッファも使用できる。小さな4kbのZバッファを使用すると、1024画素のみがZバッファで一度にレンダリングされる。4kbのZバッファを使用して任意サイズの画面(例えばgスプライトで構成される画面)をレンダリングするためには、所定サイズの32×32画素のチャンクに分割される(通常、1画面にはgスプライトが複数あるが、各gスプライトともチャンクに分割される。)この方法では、画像前処理装置104が適切な幾何形状をgスプライトの各チャンクに送ってZバッファでレンダリングを行なう。

【0207】

チャンクの機能の例として、図18Aに示す8個のオブジェクトとそれに対応する幾何形状を挙げる。簡単に説明するために、8個のオブジェクト612〜619をA〜Dの4つの値のいずれかを有する単一の属性620(例えばカラー)で規定する。図18Bに示すように、8個のオブジェクトはグラフィック画面で重なり合う。各gスプライトとその生成については無視し、図示の関係上、分離した4つのチャンクのみについて説明する。この分離した4つのチャンク621〜624を図18Bに示す。分離した4つのチャンクは、図19Aに示すように幾何形状1〜8と属性A〜Dに接している。チャンク1630(図19A)は幾何形状1,2,5と属性Bに接しており、チャンク2639は属性AからDに接しているがいずれの幾何形状にも接していない。またチャンク3632は幾何形状2,4,7,8と属性A,B,Dに、チャンク4634は幾何形状4,6と属性A,Cに接している。(図18B及び19Aに示すチャンクを使って)画像の前処理によって作成した部分画面グラフの例を図19Bに示す。各チャンクの属性(例えばA〜D,Xで示すカラーなど)は円638で表し、また属性(例えば1〜8で示す様々な形状など)は四角形640で表している。文字Xは属性のデフォルト値を示している。中間ノードは、幾何形状プリミティブに対して実行する属性演算を有している。画面グラフのリーフノードはチャンクに使用される幾何形状プリミティブを有しており、またチャンクが描く幾何形状を取り囲む境界ボリュームも有することがある(境界ボリュームを有するリーフノードについては以下に説明する)。

【0208】

チャンキングを行なう1つの方法では、各チャンクを繰り返し使用して完全な幾何形状を毎回送信する。さらに最適な別な方法では、現在のチャンクで可視状態の幾何形状のみを送信する(ちなみに、この最適な方法では不明瞭又は目で確認できない幾何形状は省いている)。該システムで使用されている32×32画素ブロックのgスプライトをチャンクする実際の方法は、上記2つの極端な方法の中間に位置するものでバケットチャンキングと呼ばれている。しかし、これら2つの方法に含まれるあるいは中間に位置するような他の方法を用いて、チャンクを作成し、チャンキングを行なうことも可能である。

【0209】

バケットチャンキングは2つのパスで構成される。まず第1のパスは画面グラフを移動させながら、現在の変換部分をビュー空間に維持させ、最終的には各チャンクの記述コマンドストリームをビュー空間に構築する。ビュー空間はN×Mのチャンクバケットに分割され、このチャンクバケットは最終的にはそれぞれのチャンクに対応する幾何形状のリストをそれぞれ有するようになる。幾何形状プリミティブノードがあると、現在の変換部分が境界ボリュームに適用されて2Dの「フットプリント」がビュー空間に生成される。フットプリントに接する各チャンクに、幾何形状(及び累積属性状態)が該当するバケットに付加される。この最初のパスの終了時には、各バケットとも該当するチャンクをレンダリングするのに必要なデータを有しているはずである。ちなみに、このチャンキング方法は算出されたフットプリントの品質に左右され、オブジェクトの領域があまり正確でなければ生成されるフットプリントはより大きくなる。従って、周囲を囲まれた幾何形状に接していないチャンクとなる。オブジェクトの領域が正確であると生成されるフットプリントは小さくなるので、ほとんどのチャンクが周囲を囲まれた幾何形状に接することになる。

【0210】

第1のパスの例として、図19Aに示す幾何形状1〜8、属性A〜D,Xによって描かれる互いに重なり合うオブジェクトを含む4つのチャンクの部分集合について考察する。パス1の中で画面グラフを移動させる1つの方法として、各チャンクの現在の状態を維持し、所定のチャンクに収まらない幾何形状を省くというものがある。これにより、各チャンクのどの幾何形状の属性内容も最新のものに更新される。図19Bの画面グラフでこの方法を用いると、パス1の後でチャンクバケットに以下のようなコマンドストリームができる。

チャンク1バケット:X,A,B,1,2,5,A,X,C,D,C,X

チャンク2バケット:X,A,B,A,X,C,D,C,X

チャンク3バケット:X,A,B,2,7,8,A,4,X,D,3,C,X

チャンク4バケット:X,A,B,A,4,X,C,6,D,C,X

また、現在の属性状態を維持し、容認された各幾何形状を送信する前にこの状態を送る方法もある。これにより、チャンクバケットに以下のコマンドストリームができる。

チャンク1バケット:B,1,B,2,B,5

チャンク2バケット:<空き>

チャンク3バケット:B,2,B,7,B,8,A,4,D,3

チャンク4バケット:A,4,C,6

第2の方法は第1の方法を改良したものである。ちなみに属性Bは幾何形状2及び5の前に指定された第2及び第3の不要な時間である。この動作は、幾何形状7及び8のBに対するチャンク3でも行われる。実際には、現在の属性状態がどの属性も各幾何形状に対して再指定されることを表しているので、状況はここに説明する以上に悪くなってしまう。つまり、テクスチャ変換行列が全画面グラフに対して変化しなくても、全チャンクの各幾何形状を送る前に行列が送信されてしまう。

【0211】

従って、この特有の方法は、優先属性(overriding attribute)、又はその代わりの構成属性(composing attribute)として、属性を維持する。拡散カラーは優先属性である。画像グラフを作成する画像前処理装置(例えば、画像前処理装置等で実行される画像前処理ソフトウェア)で規定されるように、赤(青(立方体))に使用される属性から赤の立方体ができる。これは、最も近い属性をオブジェクトに結び付ける画像前処理装置のグラフィックインターフェイスとは対称的である。最も近い属性を赤(青(立体))のオブジェクトに結び付けると、青の立方体ができる。

最も遠い属性を優先属性として使用すると、属性維持が極めて簡素化する。画面グラフの移動中に、属性ノードに遭遇すると、画面グラフの中のそのノードよりも下にあるその属性タイプのノード全てを無視することができる。これは最上位の属性が他よりも優先されるためである。

局部変換は構成属性である。従って、現在の値は前の値と新しい値によって規定される。構成属性には、画面グラフが移動して前の数値を保存する際にある種のスタックが必要になる。

【0212】

バケットチャンキング方法では以下の構造を用いる:

・ 現在の値を有する属性ノード。

・ 移動に関するコンテクスト。これは、各優先属性に対して現在の属性値を示すポインタを有する構造である。

・ それぞれコマンドストリームバッファと広域移動に関するコンテクストとして同種のバケットコンテクスト構造を有するバケットのグリッド。

・ それぞれ移動に関するコンテクストによって参照可能なデフォルト属性値のリスト。

初期化するために、コンテクストはデフォルト状態になるので、属性は全てデフォルトコンテクストを表す。デフォルト値は、各チャンクにレンダリング命令を送る前にひとまとめにダンプされるのではなく、ゆっくりとロードされる。

次に所定の属性ノードの処理方法を説明する。

幾何形状ノードを扱う処理により、現在の移動状態が各バケットの属性状態と同期する。

移動中にスタックを維持するということを除けば、構成属性は優先属性と同様の働きをする。これは、スタック値を保存するためのノードを使用することで可能となる。この方法には以下の構造が必要となる。

・以前の値と新しい値の組み合わせを有する現在の属性ノード。

・移動に関するコンテクスト。これは、全ての構成属性のために、現在の属性ノードを示すポインタを有する構造である。

・それぞれ移動に関するコンテクストによって参照されるデフォルト属性値のリスト。

・それぞれコマンドストリームバッファと広域移動に関するコンテクストと同じタイプのバケットコンテクスト構造を有するバケットのグリッド。

構成属性の初期化は優先属性の初期化と同様と思われる。

【0213】

構成属性の処理を行なうと、移動範囲の中にある現在のノードよりも前に新しい値と全ての数値の組み合わせが作成される。ちなみに値のスタックを作成する場合は、以前の値を保存し元に戻せるようにする必要がある。

バケットチャンキングの第2のパスは、バケットのグリッドを反復させて対応するコマンドストリームを発する。空でない全てのバケットについては、そのバケットに保存されている情報から該当するチャンクがレンダリングされる。ちなみに、画面の中に空のバケットがある場合もあり、これはgスプライトの全てのチャンクがレンダリングされるわけではないことを意味している。活発に動くgスプライトのほとんどは、透明な背景上の不透明なオブジェクトから構成され、多数のチャンクが空である必要がある。

【0214】

上記の属性状態を維持する方法は、チャンクした状態で幾何形状をレンダリングするのに特に適している。チャンクすることにより幾何形状の集合が、最初に指定されたものとは異なる順序でレンダリングされる。例えば、チャンクのレンダリングにおいて、レンダリングシステムはチャンクと交差しない幾何形状の集合を省く。従って、チャンクした幾何形状のレンダリングのレベルが低い状態では、多くても次の2つの状態レベルを維持するのがよい。1)タイラー又は他のレンダリングハードウェアとの互換性があり幾何形状のレンダリングが可能なフォーマットでの広域状態。2)幾何形状の集合にのみ適用されるその集合内の小域状態でのオーバーレイ。この方法では、幾何形状の各集合は他の集合とは別にレンダリング可能であり、また幾何形状の集合のレンダリングに副次的作用は生じない。

画像圧縮

上記に述べたように、チャンク・サイズと順次レンダリングは画像圧縮技術にとって重要な事である。それは、32×32画素チャンク全体が、後続するチャンクの計算が行われる前に完全にレンダリングされ、即座に圧縮することが可能なためである。タイラーは損失の多い圧縮形式とロスレスの圧縮形式の双方をサポートして、チャンクの圧縮を行なう。損失の多い圧縮形式及びロスレスの圧縮形式は共に8×8画素から成る独立ブロックのチャンクを圧縮するので、圧縮された各32×32画素チャンクは16個の圧縮ブロックから構成されることになる。

【0215】

画像の圧縮を行なうと、必要なメモリ・サイズが小さくなり、また必要なメモリバンド幅も大幅に減少する。この設計ではキャッシングと、プリフェッチ・ストラレジと、チャンクとを組み合わせて利用することにより、圧縮とブロックアクセスで生じるレイテンシとオーバーヘッドを減少させている。画像全体は32×32画素バッファで計算されるので、gスプライト画像圧縮は最小オーバーヘッドで行われる。圧縮アーキテクチャの概念的レイアウトを図20に示す。

変換エンジン660(図20)はモデル及び表示変換、クリッピング、ライティング等を計算し、この情報をタイラー662に送信する。タイラーは変換情報を処理すると、テクスチャメモリ664からテクスチャデータを読み出す。テクスチャブロックが必要となるので、テクスチャデータは圧縮フォーマットで保存されている。テクスチャブロックはタイラー復元エンジン666で復元され、タイラーのオンチップ・テクスチャキャッシュにキャッシュされる。タイラーは、画素データを解析すると、解析されたデータをタイラー圧縮エンジン668に送る。ここで解析されたデータは圧縮され、さらに圧縮されたデータはgスプライトメモリ670に保存される。表示制御装置672は圧縮されたgスプライト・データが必要になると、gスプライト復元エンジン674を使ってgスプライトメモリ664からのgスプライト・データを復元し、オンチップgスプライト・キャッシュにデータをキャッシュする。実際のハードウェアでは、テクスチャメモリ664とgスプライトメモリ670は同一である(即ち、圧縮データは様々なエンジンが共有する1つのメモリに保存される)。使用する圧縮方法及び復元方法に互換性があれば、共有する共用メモリは不要である。またgスプライト・データはデータベースやその他の画像供給源676から取り込んで、テクスチャメモリ664及びgスプライトメモリ670に保存することも可能である。

【0216】

本発明の一実施例では、損失の多い画素ブロック圧縮及び復元とロスレスの画素ブロック圧縮及び復元の双方をサポートしている。

損失の多い画像圧縮形式には、損失の多い第1ステージとロスレスの第2ステージの2つのステージがある。損失の多い圧縮形式は、赤、緑、青(R,G,B)カラー値から輝度(Y)及びクロミナンス(U及びV、またCr及びCbとも言う)値への任意のカラー空間変換で始まる。損失の多いステージでは、離散コサイン変換(DCT)と所定の周波数成分を減少させる量子化が行われる。

第2ステージは、ハフマンコーディング及びランレングスエンコーディング(RLE)から成るロスレスの圧縮形式であるハフマンコーディングの代わりに、算術コーディングなどの他のコーディング方法も使用できる。

損失の多い復元方法では、デコーディング、圧縮データの逆量子化、逆DCT、YUVからRGBへの任意のカラー空間変換が行われる。

ロスレスの圧縮形式では、RGBからYUVへのロスレスの任意のカラー空間変換、予測ステージ、ロスレスのエンコーディングステージより構成される。このエンコーディングステージは、損失の多い圧縮形式のエントロピーコーディングステージと同じであってもよい。このロスレスの復元方法は、デコーディング、各カラー成分を逆予測するステージ、YUVからRGBへの任意のカラー空間変換から成り立っている。

損失の広い圧縮/復元

タイラーの圧縮エンジン414(図9A〜9C)における損失の多い圧縮方法の1つは、次の4又は5つのステップで行われる。

1.RGBデータ入力をYUVのような輝度クロミナンス系へ変換する(任意)。

2.各カラー成分をそれぞれ別個に二次元離散コサイン変換(DCT)させる。

3.二次元のDCT係数をおおよその頻度の増加順に並べる。

4.DCT係数を量子化する:均一の除数又は周波数依存性の除数で除算する。

5.求めた係数を、固定コード表を有するハフマンエンコーディングによってエンコードする。

【0217】

ロスレスの復元は以下の4又は5つのステップで行われる。

1.圧縮データ入力を、固定コード表を使用するハフマンデコーディングによってデコードする。

2.圧縮データを逆量子化する:圧縮の量子化ステップで使用した均一の乗数又は周波数依存性の乗数で乗算する。

3.線形アレイのデータを適切なDCT係数の二次元順序に並べる。

4.各カラー成分に対して二次元の逆DCTをそれぞれ別個に実行する。

5.対応する任意のステップが圧縮処理に含まれる場合、YUVのような輝度クロミナンス系のカラーをRGBカラーに変換する。

【0218】

カラー空間変換

カラー空間変換は、輝度座標Yと色差座標U及びVに基づいてRGBカラーを輝度クロミナンス系に変換する。この輝度クロミナンス系は標準のカラー空間ではない。カラー座標は輝度の圧縮に必要なビットのほんの一部のみを必要とするため、この系を使用すると圧縮の度合いが向上する。ロスレスの可逆変換は各画素に対して別個に実行され、アルファ値を変えることはない。

【0219】

RGBからYUV(圧縮の場合)

正数のRGB値から正数のYUV値への変換では、次のような変換式を使用する。

Y=(4R+4G+4B)/3-512

U=R-G

V=(4B-2R-2G)/3

YUVからRGB(復元の場合)

正数のYUV値から正数のRGB値への変換では、次のような変換式を使用する。

R=(((Y+512)-V)/2+U+1)/2

G=(((Y+512)-V)/2-U+1)/2

B=((Y+512)/2+V+1)/2

【0220】

離散コサイン変換

画像とテクスチャは、3原色の振幅と不透明度の振幅を含む画素である。画素の位置は画像又はテクスチャ・マップ中の空間位置に相当する。この形式の画像やテクスチャは空間ドメインの中にある。画像やテクスチャの場合、離散コサイン変換(DCT)でDCTの基底係数を乗じる係数を計算する。画像やテクスチャにDCTを実行すると、画像やテクスチャを同等に表す係数の集合が求まる。この形式の画像やテクスチャは周波数ドメインの中に存在する。

【0221】

DCTでは、8×8画素ブロックのカラーと不透明度の振幅が空間ドメインと周波数ドメインとの間でマッピングされる。周波数ドメインでは、隣接する係数はあまり互いに関連することなく、また圧縮処理で圧縮効率を落とすことなく各関数をそれぞれ別個に処理する。

DCTでは空間ドメインから周波数ドメインへのマッピングが行われ、逆に逆DCTでは周波数ドメインから空間ドメインへのマッピングが行われる。DCT又は逆DCTを適切に行なう1つの方法として、1990年サンディエゴ、Academic Press Inc. 発行、Rao, K. R.及びP. Yip. 著”Discrete Cosine Transform”の図A.1.1及びA.1.2に開示されている方法がある。

【0222】

二次元DCTにより、各カラー成分を表す周波数ドメインの係数の二次元アレイが生成される。ジグザグの順でその係数が再構成されるので、線形アレイの低い位置で、DCTの低周波数成分が生じる傾向がある。このジグザグ順において、係数がゼロになる確率は、おおよそ線形アレイでの位置の単調増加関数になる(線形インデックスによる)。このジグザグ順により、知覚量子化及びLODフィルタリングが簡素化され、ランレングスエンコーディング(RLE)も大幅に向上する。

【0223】

量子化

量子化を行なうと、係数を正数で除算することでジグザグ順のDCT係数が有することのできる互いに異なる値の数が減少する。圧縮タイプのパラメータの値によっても異なるが、量子化は均一量子化又は知覚量子化となる。いずれの場合もDC頻度の係数が変わるが(インデックス=0)、そのままこの係数を送信する。

【0224】

量子化処理は、画像又は画像の一部の量子化係数の指定から始まる。この場合、量子化係数は32×32画素チャンクに対して指定される。量子化インデックス(Qインデックス)はチャンクで使用するための該当する量子化係数(Q係数)を指定する。次の表はQインデックスとQ係数との関係を表している。

【0225】

【表1】

【0226】

各カラー面はチャンクQインデックスの異なる数値を有している。15のQインデックスは4096のQ係数を選択し、これにより量子化及び逆量子化の際にゼロが生成される。量子化処理では、Q係数で各係数を除算し、さらに四捨五入して正数にする。逆量子化処理では、各係数をQ係数で乗算する。量子化及び逆量子化によってDC頻度成分が変化することはない。

【0227】

ブロック量子化係数

Qインデックス及びQ係数はブロック(8×8画素)ごとに変化させることが可能である。あるブロックのQインデックスは、チャンクのQインデックスをブロック圧縮タイプに埋め込まれている数値でインクリメントすることで求められる。

【0228】

ブロックQインデックス=チャンクQインデックス+(ブロック圧縮タイプ−3)これはチャンクQインデックスを1、2、3又は4インクリメントするものである。考えられる最大のQインデックス数値は15なので、インクリメントした結果15を越える数値は15に設定される。

量子化の種類が知覚量子化である場合、Qインデックス及びQ係数は係数ごとに(アレイインデックスごとに)変化させることも可能である。

均一量子化の場合は、係数QインデックスはブロックQインデックスに等しいので、該当するQ係数はブロック中の各係数を乗算(逆量子化)又は除算(量子化)する。

【0229】

知覚量子化の場合、係数Qインデックスは線形アレイのインデックスの数値(0...63)によって変化する。以下の表はアレイインデックス数値の関数として求めた係数Qインデックスを示している。

係数Qインデックス アレイインデックス

ブロックQインデックス インデックス<12

ブロックQインデックス+1 12≦インデックス<28

ブロックQインデックス+2 28≦インデックス<52

ブロックQインデックス+3 52≦インデックス

エントロピーコーディング

【0230】

ハフマン/RLEコーディングは量子化されたDCT係数を以下の方法で処理する。

1.(DCT係数は互いに関連していないため)ゼロ以外の係数を存在しうる最低ビットで別個にエンコードする。

2.(ジグザグ順であるため)特に線形アレイの最後にあるゼロの数値で連続する種類の係数を最適にエンコードする。

ハフマン/RLEコーディング処理を適切に行なう方法としては、既知のJPEG静止画像圧縮標準のAC係数で使用されるハフマン/RLEコーディング処理がある。

【0231】

ブロックにランダムアクセスするために、この方法ではDCの周波数係数(インデックス=0)をエンコードしないが、数値を変えずにこれを送信する。

アルゴリズムは、以下を表す一連の可変長コードを計算する。

1.次のゼロ以外の係数の前の一続きのゼロの1から15までの長さ。

2.次のゼロ以外の係数の符号と仮数を指定するのに必要な追加ビット数。

コード語の後にゼロ以外の係数の符号と仮数が書き込まれる。ある1つの指定コードは、ブロックの残りの係数が全てゼロであることを表す。

【0232】

エンコーディング

全ブロックをエンコードする場合、ISO国際標準10918の付録K、セクションK.3.2に記載されている代表的なAC係数のハフマン表を使用する。これには、輝度(Y)AC係数の表K.5とクロミナンス(U及びV)AC係数の表K.6が示されている。

【0233】

デコーディング

全ブロックをデコードする場合、エンコード処理として同一の一定表を使用する。従って、データを書き込んだハフマン表を保存する必要はなく、移動させる必要もない。

【0234】

ロスレスの圧縮/復元

タイラーの圧縮エンジン414では、次の2つのステージでロスレスの圧縮が行われる。

1.入力されたRGBデータからYUVのような輝度クロミナンス系への変換(任意)。

2.各カラー成分に対して微分予測計算を行なう。固定コード表を使用するハフマンエンコーディングにより、求めた係数をエンコードする。

タイラーの復元エンジン404,450及びgスプライト・エンジンでは、次のような2又は3つのステージでロスレスの復元が行われる。

1.固定コード表を使用するハフマンデコーディングにより、入力される圧縮データをデコードする。

2.各カラー成分に対して逆の微分予測(再構成)計算を行なう。

3.圧縮処理にYUVのような輝度クロミナンス系のカラーをRGBカラーに変換する任意のステップが含まれる場合、この変換処理を行なう。

【0235】

カラー空間変換

カラー空間変換は、RGBカラーを輝度座標Yとカラー座標U及びVに基づく輝度クロミナンス系に逆変換する。これはYUV系以上に圧縮の度合いを上げることのできる他と異なるカラー空間であるハフマン/RLEエンコーダへの入力数が少なく、さらなる圧縮が可能となるためである。各画素はそれぞれ別個にカラー空間変換され、またこの変換によってアルファの値が変化することはない。

【0236】

RGBからYUV(圧縮の場合)

正数のRGB値から正数のYUV値へ変換する場合、次のような変換式を使用する。

Y=G

U=R-G

V=B-G

【0237】

YUVからRGB(復元の場合)

正数のYUV値から正数のRGB値へ変換する場合、次のような変換式を使用する。

R=Y+U

G=Y

B=Y+V

【0238】

カラー空間変換の実行中、アルファ情報は変化しない。

カラー空間変換を回避することも可能である。gスプライト制御データ構造でフラグを用いて、カラー変換を回避することをデコンプレッサに知らせる。

カラー空間変換後に予測が行われる。予測は、大部分の元画像、特に空き空間と水平及び垂直線を多く含む画像のエントロピーを減少させるロスレスの可逆処理である。

【0239】

圧縮の予測処理及び復元の逆予測処理においては、以下のような値が使用される。

1.p(x,y)は、コンプレッサに入力され、また復元エンジンから出力される画素値である。

2.d(x,y)は、圧縮エンジンの次段のコーダへ入力され、また復元エンジンのコーダの反対側から出力される差分値である。

【0240】

予測は次のように計算される。

x=0,y=0のとき、d(x,y)=p(x,y)

x=0,y>0のとき、d(x,y)=p(x,y)-p(x,y-1)

x>0のとき、d(x,y)=p(x,y)-p(x-1,y)

復元エンジンでの逆予測は次のように計算される。

x=0,y=0のとき、p(x,y)=d(x,y)

x=0,y>0のとき、p(x,y)=p(x,y-1)+d(x,y)

x>0のとき、p(x,y)=p(x-1,y)+d(x,y)

ハフマン/RLEコーディング及びデコーディングは、本実施例の損失の多い圧縮/復元形式で行われるものと同一である。

【0241】