JP4511475B2 - Game machine - Google Patents

Game machine Download PDFInfo

- Publication number

- JP4511475B2 JP4511475B2 JP2006006628A JP2006006628A JP4511475B2 JP 4511475 B2 JP4511475 B2 JP 4511475B2 JP 2006006628 A JP2006006628 A JP 2006006628A JP 2006006628 A JP2006006628 A JP 2006006628A JP 4511475 B2 JP4511475 B2 JP 4511475B2

- Authority

- JP

- Japan

- Prior art keywords

- payout

- circuit

- random number

- value

- abnormality

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Pinball Game Machines (AREA)

Description

本発明は、遊技媒体を用いて遊技者が所定の遊技を行うことが可能であり、遊技領域における入賞領域に遊技媒体が入賞したことにもとづいて景品として景品遊技媒体を払い出す遊技機に関する。 The present invention relates to a gaming machine in which a player can play a predetermined game using a game medium, and pays out a prize game medium as a prize based on the winning of the game medium in a prize area in the game area.

遊技機として、遊技球などの遊技媒体を発射装置によって遊技領域に発射し、遊技領域に設けられている入賞口などの入賞領域に遊技媒体が入賞すると、所定個の賞球が遊技者に払い出されるものがある。 As a gaming machine, a game medium such as a game ball is launched into a game area by a launching device, and when a game medium wins a prize area such as a prize opening provided in the game area, a predetermined number of prize balls are paid out to the player. There is something to be done.

遊技機における遊技進行は、マイクロコンピュータ等による遊技制御手段によって制御される。賞球払出の制御を行う払出制御手段が、遊技制御手段が搭載されている遊技制御基板(主基板)とは別の払出制御基板に搭載されている場合、遊技の進行は主基板に搭載された遊技制御手段によって制御されるので、入賞にもとづく賞球個数は遊技制御手段によって決定され、賞球個数を示す制御コマンドが払出制御基板に送信される。そして、払出制御手段は、遊技制御手段からの制御コマンドにもとづいて、入賞にもとづく個数の賞球を払い出す処理を行う。 Game progress in the gaming machine is controlled by game control means such as a microcomputer. When the payout control means for controlling the prize ball payout is mounted on a payout control board different from the game control board (main board) on which the game control means is mounted, the progress of the game is mounted on the main board. Therefore, the number of winning balls based on the winning is determined by the gaming control means, and a control command indicating the number of winning balls is transmitted to the payout control board. Then, the payout control means performs a process of paying out the number of prize balls based on the winning based on the control command from the game control means.

また、全入賞計数スイッチの検出信号(排出処理装置のスイッチの検出信号)を払出制御手段に入力して、払出制御手段が賞球数の過不足の判定を行うものがある(例えば、特許文献1参照)。特許文献1に記載された遊技機では、各入賞口への遊技球の入賞を検出する入賞検出スイッチの検出信号を遊技制御基板に入力し、入賞にもとづく賞球個数が遊技制御手段によって決定され、賞球個数を示す制御コマンドが払出制御基板に送信される。また、払出制御手段は、入賞数カウンタの値に基づいて賞球数の過不足の判定を行う。そして、払出制御手段は、警告処理を行うことによって、賞球数の過不足の判定結果を報知する。

In addition, there is a technique in which a detection signal of the all winning counting switch (a detection signal of the switch of the discharge processing device) is input to the payout control means, and the payout control means determines whether the number of winning balls is excessive or insufficient (for example, Patent Literature) 1). In the gaming machine described in

しかし、特許文献1に記載された遊技機では、各入賞検出スイッチの検出信号を遊技制御基板に入力し遊技制御手段が賞球数を管理している一方で、払出制御基板に全入賞計数スイッチの検出信号を入力し払出制御手段が賞球数を管理している。そのため、遊技制御手段が管理する賞球数と払出制御手段が管理する賞球数との間で数にズレが生じる虞がある。

However, in the gaming machine described in

例えば、遊技制御手段は、賞球数の総数を記憶する総賞球バッファを用いて賞球数を管理する。遊技制御手段は、払い出しが行われると、総賞球数バッファが記憶する総賞球数から、払出カウントスイッチによって検出された払出数を減算する。また、遊技制御手段は、入賞を検出すると、総賞球数バッファから総賞球数を読み出し、読み出した総賞球数に、各入賞検出スイッチによって検出された賞球数を加算する。そして、遊技制御手段は、加算後の総賞球数を再び総賞球数バッファに書き込む。この場合、総賞球数バッファから総賞球数を読み出してから再び書き込むまでの間に払い出しが行われると、遊技制御手段は、払い出しに基づく減算処理を実行した後に、加算後の総賞球数(減算分が反映されていない総賞球数)を総賞球バッファに上書きしてしまうことになる。そのため、払い出しによる減算分を総賞球数に正しく反映できなくなり、遊技制御手段が管理する賞球数と払出制御手段が管理する賞球数との間で数にズレが生じてしまう虞がある。 For example, the game control means manages the number of prize balls using a total prize ball buffer that stores the total number of prize balls. When paying out, the game control means subtracts the payout number detected by the payout count switch from the total prize ball number stored in the total prize ball number buffer. In addition, when the game control means detects a winning, it reads the total number of winning balls from the total winning ball number buffer, and adds the number of winning balls detected by each winning detection switch to the read total number of winning balls. Then, the game control means again writes the total number of winning balls after the addition to the total winning ball number buffer. In this case, if payout is performed between the time of reading the total number of winning balls from the total number of winning balls buffer and the time of writing again, the game control means executes the subtraction processing based on the payout and then adds the total number of winning balls The number (the total number of winning balls not reflecting the subtraction) is overwritten in the total winning ball buffer. For this reason, the amount of subtraction due to payout cannot be correctly reflected in the total number of winning balls, and there is a risk that the number of winning balls managed by the game control means and the number of winning balls managed by the payout control means may be misaligned. .

そこで、本発明は、遊技制御手段と払出制御手段とが別個に設けられ、遊技領域における入賞領域に遊技媒体が入賞したことにもとづいて景品として景品遊技媒体を払い出す遊技機において、遊技制御手段が管理する賞球数と払出制御手段が管理する賞球数との間のズレの発生を防止できるようにすることを目的とする。 Therefore, the present invention provides a game control means in a gaming machine in which a game control means and a payout control means are provided separately, and a prize game medium is paid out as a prize based on the winning of a game medium in a prize area in the game area. It is an object of the present invention to prevent a deviation between the number of prize balls managed by the player and the number of prize balls managed by the payout control means.

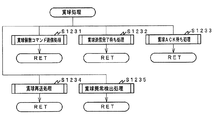

本発明による遊技機は、遊技媒体(例えば、遊技球)を用いて遊技者が所定の遊技を行うことが可能であり、遊技領域における入賞領域(例えば、可変入賞球装置15、入賞口29,30,33,39、大入賞口)に遊技媒体が入賞したことにもとづいて景品として景品遊技媒体を払い出す遊技機であって、入賞領域に遊技媒体が入賞したことを検出して入賞検出信号を出力する入賞検出手段(例えば、始動口スイッチ14a、カウントスイッチ23、入賞口スイッチ29a,30a,33a,39a)と、入賞検出手段からの入賞検出信号が入力され、遊技の進行を制御する遊技制御手段(例えば、遊技制御用マイクロコンピュータ560)と、景品遊技媒体の払い出しを行う払出手段(例えば、球払出装置97)と、払出手段によって景品遊技媒体が払い出されたことを検出して払出検出信号を出力する払出検出手段(例えば、払出個数カウントスイッチ301)と、払出手段を制御する払出制御手段(例えば、払出制御用マイクロコンピュータ370)とを備え、遊技制御手段は、所定のメイン処理を繰り返し実行するメイン処理実行手段(例えば、遊技制御用マイクロコンピュータ560においてステップS17〜S19hの処理を繰り返し実行する部分)と、所定時間毎に発生するタイマ割込の設定を行うタイマ割込設定手段(例えば、遊技制御用マイクロコンピュータ560においてステップS16の処理を実行する部分)と、タイマ割込が発生したときに、メイン処理の実行を中断してタイマ割込処理を実行するタイマ割込処理実行手段(例えば、遊技制御用マイクロコンピュータ560においてステップS20〜S27の処理を実行する部分)と、タイマ割込処理の実行中に、入賞検出信号の入力に応じて、払い出すべき景品遊技媒体の数を特定可能な払出数データ(例えば、カウント値)を払出数記憶手段(例えば、賞球コマンド出力カウンタ)に記憶させる払出数登録手段(例えば、遊技制御用マイクロコンピュータ560においてステップS2124の処理を実行する部分)と、メイン処理の実行中に、払出数記憶手段に記憶された払出数データにもとづいて、払い出すべき景品遊技媒体の数を特定可能な払出数コマンド(例えば、図53に示す賞球個数コマンド「03」,「0A」,「0F」)を、払出制御手段に送信する払出数送信手段(例えば、遊技制御用マイクロコンピュータ560においてステップS1254の処理を実行する部分)と、払い出すべき景品遊技媒体であって払出手段による払い出しが完了していない景品遊技媒体の総数を示す総未払出数(例えば、総賞球数)を記憶する総未払出数記憶手段(例えば、総賞球数格納バッファ)と、メイン処理の実行中に、総未払出数記憶手段から総未払出数を読み出す読出手段(例えば、遊技制御用マイクロコンピュータ560においてステップS1282の処理を実行する部分)と、払出数送信手段によって送信された払出数コマンドに示される景品遊技媒体の数を、読出手段が読み出した総未払出数に加算する払出数加算手段(例えば、遊技制御用マイクロコンピュータ560においてステップS1283の処理を実行する部分)と、払出数加算手段により加算された総未払出数を、総未払出数記憶手段に書き込む払出数書込手段(例えば、遊技制御用マイクロコンピュータ560においてステップS1284の処理を実行する部分)と、読出手段が総未払出数を読み出す前にタイマ割込処理の実行を禁止する割込禁止手段(例えば、遊技制御用マイクロコンピュータ560においてステップS1281の処理を実行する部分)と、払出数書込手段によって総未払出数が総未払出数記憶手段に書き込まれると、タイマ割込処理の実行を許可する割込許可手段(例えば、遊技制御用マイクロコンピュータ560においてステップS1285の処理を実行する部分)とを含み、タイマ割込処理の実行中に、払出検出信号にもとづいて、払出手段によって払い出された景品遊技媒体の数を、総未払出数記憶手段が記憶する総未払出数から減算する総未払出数減算手段(例えば、遊技制御用マイクロコンピュータ560においてステップS2131の処理を実行する部分)と、払出数加算手段によって払出数コマンドに示される景品遊技媒体の数が総未払出数に加算されると、払出数コマンドに示される景品遊技媒体の数が加算された総未払出数が所定の範囲内であるか否かを判定する払出数判定手段(例えば、遊技制御用マイクロコンピュータ560においてステップS1305の処理を実行する部分)とを含むことを特徴とする。

In the gaming machine according to the present invention, a player can play a predetermined game using a game medium (for example, a game ball), and a winning area in the gaming area (for example, a variable winning

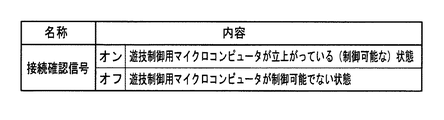

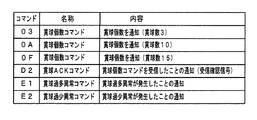

遊技制御手段は、払出数判定手段によって所定の範囲内でないと判定されると、払出手段による景品遊技媒体の払い出しに異常が発生したことを示す異常発生コマンド(例えば、図53に示す賞球過多異常コマンド「E1」,賞球過少異常コマンド「E2」)を、払出制御手段に送信する対払出異常発生コマンド送信手段(例えば、遊技制御用マイクロコンピュータ560においてステップS1306で賞球過多異常コマンド「E1」を払出制御基板37に送信する部分、遊技制御用マイクロコンピュータ560においてステップS1305bで賞球過少異常コマンド「E2」を払出制御基板37に送信する部分)を含み、払出制御手段は、遊技制御手段から受信した異常発生コマンドにもとづいて、払出手段による景品遊技媒体の払い出しに異常が発生したことを報知する払出側異常報知手段(例えば、払出制御用マイクロコンピュータ370において、ステップS829で賞球過多異常エラービットをセットしたことにもとづいて、ステップS759でエラー表示用LED374に「9」を表示させる部分、払出制御用マイクロコンピュータ370において、ステップS832で賞球過少異常エラービットをセットしたことにもとづいて、ステップS759でエラー表示用LED374に「A」を表示させる部分)を含むように構成されていてもよい。

When the game control means determines that the payout number determination means does not fall within the predetermined range, the game control means indicates an abnormality occurrence command (for example, excessive prize balls shown in FIG. 53) indicating that an abnormality has occurred in the payout means. An abnormal command “E1” and an award ball underabnormality command “E2”) are transmitted to the payout control unit, for example, in a payout abnormality occurrence command transmitting means (for example, in the

遊技機は、演出用の電気部品(例えば、スピーカ27や各ランプ25,28a,28b,28c、可変表示装置9)を制御して遊技演出を実行する演出制御手段(例えば、音/ランプ制御用マイクロコンピュータ100b、図柄制御用マイクロコンピュータ100a)を備え、遊技制御手段は、払出数判定手段によって所定の範囲内でないと判定されると、払出手段による景品遊技媒体の払い出しに異常が発生したことを示す異常発生コマンドを、演出制御手段に送信する対演出異常発生コマンド送信手段(例えば、遊技制御用マイクロコンピュータ560においてステップS1306で賞球過多異常コマンドを音/ランプ制御基板80bに送信する部分、遊技制御用マイクロコンピュータ560においてステップS1305bで賞球過少異常コマンドを音/ランプ制御基板80bに送信する部分)を含み、演出制御手段は、遊技制御手段から受信した異常発生コマンドにもとづいて、払出手段による景品遊技媒体の払い出しに異常が発生したことを報知する演出側異常報知手段(例えば、音/ランプ制御用マイクロコンピュータ100bにおいてステップS790でスピーカ27や各ランプ25,28a,28b,28cを用いて報知する部分、図柄制御用マイクロコンピュータ100aにおいて可変表示装置9を用いて報知する部分)を含むように構成されていてもよい。

The gaming machine controls production electrical parts (for example, the

払出数判定手段は、払出数加算手段によって払出数コマンドに示される景品遊技媒体の数が加算された総未払出数にもとづいて、払い出すべき景品遊技媒体の数よりも多い遊技媒体が払い出される異常である払出過多異常が発生したか否かを判定する払出過多異常判定手段(例えば、遊技制御用マイクロコンピュータ560において、ステップS1305で総賞球数が−499よりも小さいと判断したことにもとづいて賞球過多異常が発生したと判定する部分)と、払出数加算手段によって払出数コマンドに示される景品遊技媒体の数が加算された総未払出数にもとづいて、総未払出数が所定の払出過少判定値を超えた状態の異常である払出過少異常が発生したか否かを判定する払出過少異常判定手段(例えば、遊技制御用マイクロコンピュータ560において、ステップS1305aで総賞球数が2000よりも大きいと判断したことにもとづいて賞球過少が発生したと判定する部分)とを含み、対払出異常発生コマンド送信手段は、払出過多異常判定手段によって払出過多異常が発生したと判定されると、払出過多異常が発生したことを示す払出過多異常コマンド(例えば、図53に示す賞球過多異常コマンド「E1」)を、払出制御手段に送信する対払出過多異常コマンド送信手段(例えば、遊技制御用マイクロコンピュータ560においてステップS1306で賞球過多異常コマンド「E1」を払出制御基板37に送信する部分)と、払出過少異常判定手段によって払出過少異常が発生したと判定されると、払出過少異常が発生したことを示す払出過少異常コマンド(例えば、図53に示す賞球過少異常コマンド「E2」)を、払出制御手段に送信する対払出過少異常コマンド送信手段(例えば、遊技制御用マイクロコンピュータ560においてステップS1305bで賞球過少異常コマンド「E2」を払出制御基板37に送信する部分)とを含み、払出側異常報知手段は、遊技制御手段から受信した払出過多異常コマンドにもとづいて、払出過多異常が発生したことを報知する払出側過多報知手段(例えば、払出制御用マイクロコンピュータ370において、ステップS829で賞球過多異常エラービットをセットしたことにもとづいて、ステップS759でエラー表示用LED374に「9」を表示させる部分)と、遊技制御手段から受信した払出過少異常コマンドにもとづいて、払出過少異常が発生したことを報知する払出側過少報知手段(例えば、払出制御用マイクロコンピュータ370において、ステップS832で賞球過少異常エラービットをセットしたことにもとづいて、ステップS759でエラー表示用LED374に「A」を表示させる部分)とを含むように構成されていてもよい。

The number-of-payout determination means pays out more game media than the number of prize game media to be paid out based on the total number of payout game media added by the number of prize game media indicated by the number-of-payout command by the number-of-payout addition means. Excessive payout abnormality determining means for determining whether or not an abnormal excessive payout abnormality has occurred (for example, based on determining that the total number of winning balls is smaller than −499 in step S1305 in the gaming control microcomputer 560). And the number of premium game media indicated by the number-of-payout command added by the number-of-payout command is added to the predetermined number. A payout underabnormality judging means (for example, a game controlling microcomputer) for judging whether or not an underpayment abnormality that is an abnormality in a state exceeding the payout underdetermination value has occurred. The

払出数判定手段は、払出数加算手段によって払出数コマンドに示される景品遊技媒体の数が加算された総未払出数にもとづいて、払い出すべき景品遊技媒体の数よりも多い遊技媒体が払い出される異常である払出過多異常が発生したか否かを判定する払出過多異常判定手段(例えば、遊技制御用マイクロコンピュータ560において、ステップS1305で総賞球数が−499よりも小さいと判断したことにもとづいて賞球過多異常が発生したと判定する部分)と、払出数加算手段によって払出数コマンドに示される景品遊技媒体の数が加算された総未払出数にもとづいて、総未払出数が所定の払出過少判定値を超えた状態の異常である払出過少異常が発生したか否かを判定する払出過少異常判定手段(例えば、遊技制御用マイクロコンピュータ560において、ステップS1305aで総賞球数が2000よりも大きいと判断したことにもとづいて賞球過少が発生したと判定する部分)とを含み、対演出異常発生コマンド送信手段は、払出過多異常判定手段によって払出過多異常が発生したと判定されると、払出過多異常が発生したことを示す払出過多異常コマンドを、演出制御手段に送信する対演出過多異常コマンド送信手段(例えば、遊技制御用マイクロコンピュータ560においてステップS1306で賞球過多異常コマンドを音/ランプ制御基板80bに送信する部分)と、払出過少異常判定手段によって払出過少異常が発生したと判定されると、払出過少異常が発生したことを示す払出過少異常コマンドを、演出制御手段に送信する対演出過少異常コマンド送信手段(例えば、遊技制御用マイクロコンピュータ560においてステップS1305bで賞球過少異常コマンドを音/ランプ制御基板80bに送信する部分)とを含み、演出側異常報知手段は、遊技制御手段から受信した払出過多異常コマンドにもとづいて、払出過多異常が発生したことを報知する演出側過多報知手段(例えば、音/ランプ制御用マイクロコンピュータ100bにおいてステップS790でスピーカ27や各ランプ25,28a,28b,28cを用いて報知する部分、図柄制御用マイクロコンピュータ100aにおいて可変表示装置9を用いて図99(A)の画面を表示する部分)と、遊技制御手段から受信した払出過少異常コマンドにもとづいて、払出過少異常が発生したことを報知する演出側過少報知手段(例えば、音/ランプ制御用マイクロコンピュータ100bにおいてステップS790でスピーカ27や各ランプ25,28a,28b,28cを用いて報知する部分、図柄制御用マイクロコンピュータ100aにおいて可変表示装置9を用いて図99(B)の画面を表示する部分)とを含むように構成されていてもよい。

The number-of-payout determination means pays out more game media than the number of prize game media to be paid out based on the total number of payout game media added by the number of prize game media indicated by the number-of-payout command by the number-of-payout addition means. Excessive payout abnormality determining means for determining whether or not an abnormal excessive payout abnormality has occurred (for example, based on determining that the total number of winning balls is smaller than −499 in step S1305 in the gaming control microcomputer 560). And the number of premium game media indicated by the number-of-payout command added by the number-of-payout command is added to the predetermined number. A payout underabnormality judging means (for example, a game controlling microcomputer) for judging whether or not an underpayment abnormality that is an abnormality in a state exceeding the payout underdetermination value has occurred. The

遊技制御手段は、払出数判定手段によって払出手段による景品遊技媒体の払い出しに異常が発生したと判定されると、払出数送信手段による払出数コマンドの送信を禁止する払出数送信禁止手段(例えば、遊技制御用マイクロコンピュータ560において、ステップS1241,S1261,S1271,S1291で賞球過多異常エラーフラグまたは賞球過少異常エラーフラグがセットされていることにもとづいて処理を終了する部分)を含むように構成されていてもよい。

When it is determined by the payout number determination means that an abnormality has occurred in the payout of the prize game medium by the payout number determination means, the game control means prohibits transmission of a payout number command by the payout number transmission means (for example, The

払出制御手段は、払出検出手段から払出検出信号を入力する払出検出信号入力手段(例えば、払出制御用マイクロコンピュータ370において入力ポート1(図5に示すI/Oポート372f)から払出個数カウントスイッチ301の検出信号を入力する部分)と、払出検出信号入力手段によって入力された払出検出信号を遊技制御手段に出力する払出検出信号出力手段(例えば、払出制御用マイクロコンピュータ370において、ステップS603aで出力ポート0(図5に示すI/Oポート372a)から払出個数カウントスイッチ301の検出信号を出力する部分)と、払出検出信号の入力に応じて、払出手段によって払い出された景品遊技媒体の数を示す信号を外部出力する外部出力手段(例えば、払出制御用マイクロコンピュータ370においてターミナル基板160から賞球情報を出力する部分)とを含み、総未払出数減算手段は、払出制御手段から入力した払出検出信号の入力に応じて、払出手段によって払い出された景品遊技媒体の数を、総未払出数記憶手段が記憶する総未払出数から減算する(例えば、遊技制御用マイクロコンピュータ560において、払出制御用マイクロコンピュータ370を経由して入力した払出個数カウントスイッチ301の検出信号にもとづいて、ステップS2131の処理を実行する)ように構成されていてもよい。

The payout control means is a payout detection signal input means that inputs a payout detection signal from the payout detection means (for example, the

請求項1記載の発明では、払出手段によって景品遊技媒体の払い出しが行われると、タイマ割込処理において、払い出された景品遊技媒体の数を総未払出数から減算する。また、メイン処理において、払出数コマンドに示される景品遊技媒体の数を総未払出数に加算する際に、総未払出数記憶手段から総未払出数を読み出すと、再び総未払出数を総未払出数記憶手段に書き込むまでタイマ割込処理の実行を禁止する。そのため、総未払出数記憶手段から総未払出数を読み出してから再び書き込むまでの間に、払い出された景品遊技媒体の数を総未払出数から減算する処理を実行しないようにすることができ、払い出された景品遊技媒体の数を遊技制御手段が把握できなくなる事態を防止できる。従って、遊技制御手段が管理する賞球数と払出制御手段が管理する賞球数との間のズレの発生を防止することができる。

In the invention of

請求項2記載の発明では、遊技制御手段によって景品遊技媒体の払い出しに異常が発生したことを示す異常発生コマンドが払出制御手段に送信され、払出制御手段が、受信した異常発生コマンドにもとづいて報知するように構成されているので、景品遊技媒体の払い出しのエラー状態を報知することができる。

In the invention according to

請求項3記載の発明では、遊技制御手段によって景品遊技媒体の払い出しに異常が発生したことを示す異常発生コマンドが演出制御手段に送信され、演出制御手段が、受信した異常発生コマンドにもとづいて報知するように構成されているので、景品遊技媒体の払い出しのエラー状態を報知することができる。 According to the third aspect of the present invention, an abnormality occurrence command indicating that an abnormality has occurred in payout of prize game media is transmitted to the effect control means by the game control means, and the effect control means notifies based on the received abnormality occurrence command. Therefore, it is possible to notify the error state of the payout of the prize game medium.

請求項4記載の発明では、景品遊技媒体の払い出しの異常が払出過多異常であるか、または払出過少異常であるかを区別して判定し、払出過多異常であることと払出過少異常であることとを区別して報知するように構成されているので、払出制御手段は、払い出すべき景品遊技媒体の数よりも多い遊技媒体を払い出してしまった状態であるか、または払い出すべき景品遊技媒体の数よりも少ない遊技媒体を払い出してしまった状態であるかを区別して、景品遊技媒体の払い出しのエラー状態を報知することができる。

In the invention according to

請求項5記載の発明では、景品遊技媒体の払い出しの異常が払出過多異常であるか、または払出過少異常であるかを区別して判定し、払出過多異常であることと払出過少異常であることとを区別して報知するように構成されているので、演出制御手段は、払い出すべき景品遊技媒体の数よりも多い遊技媒体を払い出してしまった状態であるか、または払い出すべき景品遊技媒体の数よりも少ない遊技媒体を払い出してしまった状態であるかを区別して、景品遊技媒体の払い出しのエラー状態を報知することができる。

In the invention according to

請求項6記載の発明では、景品遊技媒体の払い出しに異常が発生したことが検出されると、払出数コマンドの送信を禁止するように構成されているので、不正に景品遊技媒体が払い出されてしまうことを防止できる。特に、払い出すべき景品遊技媒体の数よりも多い遊技媒体を払い出してしまう払出過多状態を確実に防止できるので、景品遊技媒体を多く払い出されてしまう不正を防止することができる。

In the invention described in

請求項7記載の発明では、払出検出手段からの払出検出信号を払出制御手段に入力し、さらに払出制御手段に入力された払出検出信号を遊技制御手段に入力するように構成されているので、払出検出信号を出力するための配線を、払出検出手段から遊技制御手段および払出制御手段の両方に設ける必要がなくなる。そのため、払出検出手段から払出検出信号を出力するための配線を削減することができる。

In the invention of

実施の形態1.

以下、本発明の一実施形態を図面を参照して説明する。

まず、遊技機の一例であるパチンコ遊技機の全体の構成について説明する。図1はパチンコ遊技機を正面からみた正面図、図2は遊技盤の前面を示す正面図である。なお、以下の実施の形態では、パチンコ遊技機を例に説明を行うが、本発明による遊技機はパチンコ遊技機に限られず、スロット機などの他の遊技機に適用することもできる。

Hereinafter, an embodiment of the present invention will be described with reference to the drawings.

First, the overall configuration of a pachinko gaming machine that is an example of a gaming machine will be described. FIG. 1 is a front view of a pachinko gaming machine as viewed from the front, and FIG. 2 is a front view showing the front of the game board. In the following embodiments, a pachinko gaming machine will be described as an example. However, the gaming machine according to the present invention is not limited to a pachinko gaming machine, and can be applied to other gaming machines such as a slot machine.

パチンコ遊技機1は、縦長の方形状に形成された外枠(図示せず)と、外枠の内側に開閉可能に取り付けられた遊技枠とで構成される。また、パチンコ遊技機1は、遊技枠に開閉可能に設けられている額縁状に形成されたガラス扉枠2を有する。遊技枠は、外枠に対して開閉自在に設置される前面枠(図示せず)と、機構部品等が取り付けられる機構板と、それらに取り付けられる種々の部品(後述する遊技盤を除く。)とを含む構造体である。

The

図1に示すように、パチンコ遊技機1は、額縁状に形成されたガラス扉枠2を有する。ガラス扉枠2の下部表面には打球供給皿(上皿)3がある。打球供給皿3の下部には、打球供給皿3に収容しきれない遊技球を貯留する余剰球受皿4と遊技球を発射する打球操作ハンドル(操作ノブ)5が設けられている。ガラス扉枠2の背面には、遊技盤6が着脱可能に取り付けられている。なお、遊技盤6は、それを構成する板状体と、その板状体に取り付けられた種々の部品とを含む構造体である。また、遊技盤6の前面には遊技領域7が形成されている。

As shown in FIG. 1, the

遊技領域7の中央付近には、それぞれが演出用の飾り図柄を可変表示する複数の可変表示部を含む可変表示装置(飾り図柄表示装置)9が設けられている。可変表示装置9には、例えば「左」、「中」、「右」の3つの可変表示部(図柄表示エリア)がある。可変表示装置9は、特別図柄表示器8による特別図柄の可変表示期間中に、装飾用(演出用)の図柄としての飾り図柄の可変表示を行う。飾り図柄の可変表示を行う可変表示装置9は、図柄制御基板に搭載されている図柄制御用マイクロコンピュータによって制御される。

Near the center of the

可変表示装置9の下部には、始動入賞口14に入った有効入賞球数すなわち保留記憶(始動記憶または始動入賞記憶ともいう。)数を表示する4つの特別図柄保留記憶表示器18が設けられている。特別図柄保留記憶表示器18は、保留記憶数を入賞順に4個まで表示する。特別図柄保留記憶表示器18は、始動入賞口14に始動入賞があるごとに、点灯状態のLEDの数を1増やす。そして、特別図柄保留記憶表示器18は、特別図柄表示器8で可変表示が開始されるごとに、点灯状態のLEDの数を1減らす(すなわち1つのLEDを消灯する)。具体的には、特別図柄保留記憶表示器18は、特別図柄表示器8で可変表示が開始されるごとに、点灯状態をシフトする。なお、この例では、始動入賞口14への入賞による始動記憶数に上限数(4個まで)が設けられているが、上限数を4個以上にしてもよい。

At the bottom of the

可変表示装置9の上部には、識別情報としての特別図柄を可変表示する特別図柄表示器(特別図柄表示装置)8が設けられている。この実施の形態では、特別図柄表示器8は、例えば0〜9の数字を可変表示可能な簡易で小型の表示器(例えば7セグメントLED)で実現されている。特別図柄表示器8は、遊技者に特定の停止図柄を把握しづらくさせるために、0〜99など、より多種類の数字を可変表示するように構成されていてもよい。また、可変表示装置9は、特別図柄表示器8による特別図柄の可変表示期間中に、装飾用(演出用)の図柄としての飾り図柄の可変表示を行う。

A special symbol display (special symbol display device) 8 that variably displays a special symbol as identification information is provided on the

可変表示装置9の下方には、始動入賞口14を形成する可変入賞球装置15が設けられている。始動入賞口14に入った入賞球は、遊技盤6の背面に導かれ、始動口スイッチ14aによって検出される。可変入賞球装置15は、ソレノイド16によって開状態にされる。

Below the

可変入賞球装置15の下部には、特定遊技状態(大当り状態)においてソレノイド21によって開状態に制御される開閉板を用いた特別可変入賞球装置20が設けられている。特別可変入賞球装置20は大入賞口を開閉する手段である。特別可変入賞球装置20に入賞し遊技盤6の背面に導かれた入賞球のうち一方(V入賞領域:特別領域)に入った入賞球はV入賞スイッチ22で検出された後カウントスイッチ23で検出され、他方の領域に入った遊技球は、そのままカウントスイッチ23で検出される。遊技盤6の背面には、大入賞口内の経路を切り換えるためのソレノイド21Aも設けられている。

Below the variable winning

遊技球がゲート32を通過しゲートスイッチ32aで検出されると、普通図柄表示器10の表示の可変表示が開始される。この実施の形態では、左右のランプ(点灯時に図柄が視認可能になる)が交互に点灯することによって可変表示が行われ、例えば、可変表示の終了時に左側のランプが点灯すれば当たりになる。そして、普通図柄表示器10における停止図柄が所定の図柄(当り図柄)である場合に、可変入賞球装置15が所定回数、所定時間だけ開状態になる。普通図柄表示器10の近傍には、ゲート32を通過した入賞球数を表示する4つのLEDによる表示部を有する普通図柄始動記憶表示器41が設けられている。ゲート32への遊技球の通過があるごとに、普通図柄始動記憶表示器41は点灯するLEDを1増やす。そして、普通図柄表示器10の可変表示が開始されるごとに、点灯するLEDを1減らす。

When the game ball passes through the

遊技盤6には、複数の入賞口29,30,33,39が設けられ、遊技球の入賞口29,30,33,39への入賞は、それぞれ入賞口スイッチ29a,30a,33a,39aによって検出される。各入賞口29,30,33,39は、遊技媒体を受け入れて入賞を許容する領域として遊技盤6に設けられる入賞領域を構成している。なお、始動入賞口14や大入賞口も、遊技媒体を受け入れて入賞を許容する入賞領域を構成する。遊技領域7の左右周辺には、遊技中に点滅表示される装飾ランプ25が設けられ、下部には、入賞しなかった遊技球を吸収するアウト口26がある。また、遊技領域7の外側の左右上部には、効果音を発する2つのスピーカ27が設けられている。遊技領域7の外周には、天枠ランプ28a、左枠ランプ28bおよび右枠ランプ28cが設けられている。さらに、遊技領域7における各構造物(大入賞口等)の周囲には装飾LEDが設置されている。天枠ランプ28a、左枠ランプ28bおよび右枠ランプ28cおよび装飾用LEDは、遊技機に設けられている装飾発光体の一例である。

The

そして、この例では、左枠ランプ28bの近傍に、賞球払出中に点灯する賞球ランプ51が設けられ、天枠ランプ28aの近傍に、補給球が切れたときに点灯する球切れランプ52が設けられている。さらに、プリペイドカードが挿入されることによって球貸しを可能にするプリペイドカードユニット(以下、「カードユニット」という。)50が、パチンコ遊技機1に隣接して設置されている。

In this example, a

カードユニット50には、例えば、使用可能状態であるか否かを示す使用可表示ランプ、カードユニットがいずれの側のパチンコ遊技機1に対応しているのかを示す連結台方向表示器、カードユニット内にカードが投入されていることを示すカード投入表示ランプ、記録媒体としてのカードが挿入されるカード挿入口、およびカード挿入口の裏面に設けられているカードリーダライタの機構を点検する場合にカードユニットを解放するためのカードユニット錠が設けられている。

The

遊技者の操作により打球発射装置から発射された遊技球は、打球レールを通って遊技領域7に入り、その後、遊技領域7を下りてくる。遊技球が始動入賞口14に入り始動口スイッチ14aで検出されると、図柄の可変表示を開始できる状態であれば、特別図柄表示器8において特別図柄が可変表示(変動)を始める。図柄の可変表示を開始できる状態でなければ、保留記憶数を1増やす。

A game ball launched from the ball striking device by the player's operation enters the

特別図柄表示器8における特別図柄の可変表示は、一定時間が経過したときに停止する。停止時の特別図柄(停止図柄)が大当り図柄(特定表示結果)であると、大当り遊技状態に移行する。すなわち、特別可変入賞球装置20が、一定時間経過するまで、または、所定個数(例えば10個)の遊技球が入賞するまで開放する。そして、特別可変入賞球装置20の開放中に遊技球がV入賞領域に入賞しV入賞スイッチ22で検出されると、継続権が発生し特別可変入賞球装置20の開放が再度行われる。継続権の発生は、所定回数(例えば15ラウンド)許容される。また、V入賞領域を設けずに、特別可変入賞球装置20の開放を常に決定されたラウンド数の最後のラウンドまで(例えば、15ラウンドまで)許容するようにしてもよい。

The variable display of the special symbol on the

停止時の特別図柄表示器8における特別図柄が確率変動を伴う大当り図柄(確変図柄)である場合には、次に大当りになる確率が高くなる。すなわち、確変状態という遊技者にとってさらに有利な状態になる。

When the special symbol on the

遊技球がゲート32を通過すると、普通図柄表示器10において普通図柄が可変表示される状態になる。また、普通図柄表示器10における停止図柄が所定の図柄(当り図柄)である場合に、可変入賞球装置15が所定時間だけ開状態になる。

When the game ball passes through the

次に、パチンコ遊技機1の裏面の構造について図3を参照して説明する。図3は、遊技機を裏面から見た背面図である。

Next, the structure of the back surface of the

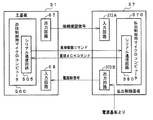

図3に示すように、遊技機裏面側では、可変表示装置9を制御する図柄制御用マイクロコンピュータが搭載された図柄制御基板80aを含む可変表示制御ユニット49、遊技制御用マイクロコンピュータ等が搭載された遊技制御基板(主基板)31が設置されている。また、球払出制御を行う払出制御用マイクロコンピュータ等が搭載された払出制御基板37が設置されている。なお、可変表示制御ユニットは、図柄制御基板80aとともに、各種装飾LED、装飾ランプ25、枠側に設けられている天枠ランプ28a、左枠ランプ28bおよび右枠ランプ28cを点灯制御し、スピーカ27からの音発生を制御する音/ランプ制御用マイクロコンピュータが搭載された音/ランプ制御基板を含む。

As shown in FIG. 3, on the back side of the gaming machine, a variable

さらに、DC30V、DC21V、DC12VおよびDC5Vを作成する電源回路が搭載された電源基板910やタッチセンサ基板91が設けられている。電源基板910は、大部分が主基板31と重なっているが、主基板31に重なることなく外部から視認可能に露出した露出部分がある。この露出部分には、遊技機1における主基板31および各制御基板(音/ランプ制御基板、図柄制御基板80aおよび払出制御基板37)や遊技機に設けられている各電気部品(電力が供給されることによって動作する部品)への電力供給を実行あるいは遮断するための電力供給許可手段としての電源スイッチが設けられている。さらに、露出部分における電源スイッチの内側(基板内部側)には、交換可能なヒューズが設けられている。

Further, a

なお、各制御基板には、制御用マイクロコンピュータを含む制御手段が搭載されている。制御手段は、遊技制御手段等からのコマンドとしての指令信号(制御信号)に従って遊技機に設けられている電気部品(遊技用装置:球払出装置97、可変表示装置9、ランプやLEDなどの発光体、スピーカ27等)を制御する。以下、主基板31を制御基板に含めて説明を行うことがある。その場合には、制御基板に搭載される制御手段は、遊技制御手段と、遊技制御手段等からの指令信号に従って遊技機に設けられている電気部品を制御する手段とのそれぞれを指す。また、主基板31以外のマイクロコンピュータが搭載された基板をサブ基板ということがある。

Each control board is equipped with control means including a control microcomputer. The control means is an electrical component (game device:

遊技機裏面において、上方には、各種情報を遊技機外部に出力するための各端子を備えたターミナル基板160が設置されている。ターミナル基板160には、少なくとも、球切れ検出スイッチ167の出力を導入して外部出力するための球切れ用端子、賞球情報(賞球個数信号)を外部出力するための賞球用端子および球貸し情報(球貸し個数信号)を外部出力するための球貸し用端子が設けられている。また、中央付近には、主基板31からの各種情報を遊技機外部に出力するための各端子を備えた情報端子基板(情報出力基板)36が設置されている。

On the back side of the gaming machine, a

貯留タンク38に貯留された遊技球は誘導レール39を通り、カーブ樋を経て払出ケース40Aで覆われた球払出装置に至る。球払出装置の上部には、遊技媒体切れ検出手段としての球切れスイッチ187が設けられている。球切れスイッチ187が球切れを検出すると、球払出装置の払出動作が停止する。球切れスイッチ187は遊技球通路内の遊技球の有無を検出するスイッチであるが、貯留タンク38内の補給球の不足を検出する球切れ検出スイッチ167も誘導レール39における上流部分(貯留タンク38に近接する部分)に設けられている。球切れ検出スイッチ167が遊技球の不足を検知すると、遊技機設置島に設けられている補給機構から遊技機に対して遊技球の補給が行われる。

The game balls stored in the

入賞にもとづく景品としての遊技球や球貸し要求にもとづく遊技球が多数払い出されて打球供給皿3が満杯になると、遊技球は、余剰球通路を経て余剰球受皿4に導かれる。さらに遊技球が払い出されると、感知レバー(図示せず)が貯留状態検出手段としての満タンスイッチ(図示せず)を押圧して、貯留状態検出手段としての満タンスイッチがオンする。その状態では、球払出装置内の払出モータの回転が停止して球払出装置の動作が停止するとともに打球発射装置の駆動も停止する。

When a large number of game balls as prizes based on winning a prize and game balls based on a ball lending request are paid out and the hitting

図4は、主基板(遊技制御基板)31における回路構成の一例を示すブロック図である。なお、図4には、払出制御基板37、音/ランプ制御基板80bおよび図柄制御基板80a等も示されている。主基板31には、プログラムに従ってパチンコ遊技機1を制御する遊技制御用マイクロコンピュータ(遊技制御手段に相当)560が搭載されている。遊技制御用マイクロコンピュータ560は、ゲーム制御(遊技進行制御)用のプログラム等を記憶するROM54、ワークメモリとして使用される記憶手段としてのRAM55、プログラムに従って制御動作を行うCPU56およびI/Oポート部57を含む。この実施の形態では、ROM54およびRAM55は遊技制御用マイクロコンピュータ560に内蔵されている。すなわち、遊技制御用マイクロコンピュータ560は、1チップマイクロコンピュータである。1チップマイクロコンピュータには、少なくともRAM55が内蔵されていればよく、ROM54は外付けであっても内蔵されていてもよい。また、I/Oポート部57は、外付けであってもよい。

FIG. 4 is a block diagram showing an example of the circuit configuration of the main board (game control board) 31. FIG. 4 also shows a

なお、遊技制御用マイクロコンピュータ560においてCPU56がROM54に格納されているプログラムに従って制御を実行するので、以下、遊技制御用マイクロコンピュータ560(またはCPU56)が実行する(または、処理を行う)ということは、具体的には、CPU56がプログラムに従って制御を実行することである。このことは、主基板31以外の他の基板に搭載されているマイクロコンピュータについても同様である。

In the

また、ゲートスイッチ32a、始動口スイッチ14a、カウントスイッチ23、V入賞スイッチ22および各入賞口スイッチ29a,30a,33a,39aからの検出信号を基本回路53に与える入力ドライバ回路58も主基板31に搭載され、可変入賞球装置15を開閉するソレノイド16、特別可変入賞球装置を開閉するソレノイド21、および大入賞口内の経路を切り換えるためのソレノイド21Aを基本回路53からの指令に従って駆動する出力回路59も主基板31に搭載され、電源投入時に遊技制御用マイクロコンピュータ560をリセットするためのシステムリセット回路(図示せず)や、大当り遊技状態の発生を示す大当り情報等の情報出力信号をホールコンピュータ等の外部装置に対して出力する情報出力回路(図示せず)も主基板31に搭載されている。

Further, an

この実施の形態では、音/ランプ制御基板80bに搭載されている音/ランプ制御手段(音/ランプ制御用マイクロコンピュータで構成される。)が、中継基板77を介して遊技制御用マイクロコンピュータ560からの演出制御コマンドを受信し、図柄制御用基板80aに転送する。そして、図柄制御基板80aに搭載されている図柄制御手段(図柄制御用マイクロコンピュータで構成される。)が、音/ランプ制御手段から演出制御コマンドを受信し、飾り図柄を可変表示する可変表示装置9の表示制御を行う。

In this embodiment, the sound / lamp control means (configured by a sound / lamp control microcomputer) mounted on the sound /

図5は、払出制御基板37および球払出装置97などの払出に関連する構成要素を示すブロック図である。図5に示すように、払出制御基板37には、払出制御用CPU371を含む払出制御用マイクロコンピュータ370が搭載されている。この実施の形態では、払出制御用マイクロコンピュータ370は、1チップマイクロコンピュータであり、少なくともRAMが内蔵されている。払出制御用マイクロコンピュータ370、RAM(図示せず)、払出制御用プログラムを格納したROM(図示せず)およびI/Oポート等は、払出制御手段を構成する。すなわち、払出制御手段は、払出制御用CPU371、RAMおよびROMを有する払出制御用マイクロコンピュータ370と、I/Oポートとで実現される。また、I/Oポートは、払出制御用マイクロコンピュータ370に内蔵されていてもよい。払出制御用マイクロコンピュータ370におけるRAMの少なくとも一部は、電源基板910に搭載されているバックアップ電源によって電源バックアップされている。この実施の形態では、全てのRAM領域が電源バックアップされているとする。よって、遊技機に対して電力供給がなされていないときにも、所定期間(バックアップ電源としてのコンデンサが放電してバックアップ電源が電力供給不能になるまで)は、RAMの記憶内容は保存される。

FIG. 5 is a block diagram showing components related to payout, such as the

球切れスイッチ187、満タンスイッチ48および払出個数カウントスイッチ301からの検出信号は、中継基板72を介して払出制御基板37のI/Oポート372fに入力される。なお、この実施の形態では、払出個数カウントスイッチ301からの検出信号は、払出制御用マイクロコンピュータ370に入力されたあと、I/Oポート372aおよび出力回路373Bを介して主基板31に出力される。

Detection signals from the ball break

また、払出モータ位置センサ295からの検出信号は、中継基板72を介して払出制御基板37のI/Oポート372eに入力される。払出モータ位置センサ295は、払出モータ289の回転位置を検出するための発光素子(LED)と受光素子とによるセンサであり、遊技球が詰まったこと、すなわちいわゆる球噛みを検出するために用いられる。払出制御基板37に搭載されている払出制御用マイクロコンピュータ370は、球切れスイッチ187からの検出信号が球切れ状態を示していたり、満タンスイッチ48からの検出信号が満タン状態を示していると、球払出処理を停止する。

A detection signal from the payout

さらに、満タンスイッチ48からの検出信号が満タン状態を示していると、払出制御用マイクロコンピュータ370は、打球発射装置からの球発射を停止させるために、発射基板90に対してローレベルの満タン信号を出力する。発射基板90のAND回路91が出力する発射モータ94への発射モータ信号は、発射基板90から発射モータ94に伝えられる。払出制御用マイクロコンピュータ370からの満タン信号は、発射基板90に搭載されたAND回路91の入力側の一方に入力され、駆動信号生成回路92からの駆動信号は、AND回路91の入力側の他方に入力される。そして、AND回路91の発射モータ信号が発射モータ94に入力される。すなわち、払出制御用マイクロコンピュータ370が満タン信号を出力している間は、発射モータ94への発射モータ信号の出力が停止される。

Further, when the detection signal from the full tank switch 48 indicates a full state, the

入賞口への遊技球の入賞があると、遊技制御用マイクロコンピュータ560のシリアル通信回路505(図7,54参照)から、払出指令信号として、払い出すべき賞球個数を示す賞球個数コマンドが出力(送信)される。賞球個数コマンドは、8ビットのデータ(2進8桁のデータ)によって構成され、非同期シリアル通信によって出力される。

When a game ball is won at the winning opening, a prize ball number command indicating the number of prize balls to be paid out is issued as a payout command signal from the serial communication circuit 505 (see FIGS. 7 and 54) of the

賞球個数コマンドは、シリアル通信回路380(図54参照)に入力される。払出制御用マイクロコンピュータ370は、シリアル通信回路380を介して賞球個数コマンドを入力すると、賞球個数コマンドが示す個数の遊技球を払い出すために球払出装置97を駆動する制御を行う。なお、主基板31の出力回路67からは、主基板31が接続されていることを示す接続確認信号も出力される。また、賞球個数コマンドは、払出数を指定する払出指令信号に相当する。

The award ball number command is input to the serial communication circuit 380 (see FIG. 54). When a prize ball number command is input via the serial communication circuit 380, the

また、電源基板910から、電源電圧が所定値以下の低下したことを示す電源断信号、およびRAMの内容をクリアするためのクリアスイッチが操作されたことを示すクリア信号とが、入力ポート372gに入力される。電源断信号とクリア信号とは、出力回路373Bを介して主基板31に出力される。そして、主基板31において、入力回路68およびI/Oポート57を介して遊技制御用マイクロコンピュータ560に入力される。

Also, a power-off signal indicating that the power supply voltage has dropped below a predetermined value and a clear signal indicating that a clear switch for clearing the contents of the RAM has been operated are supplied to the input port 372g from the

払出制御用マイクロコンピュータ370は、出力ポート372bを介して、賞球払出数を示す賞球情報信号および貸し球数を示す球貸し個数信号をターミナル基板(枠用外部端子基板と盤用外部端子基板とを含む)160に出力する。なお、出力ポート372bの外側に、ドライバ回路が設置されているが、図5では記載省略されている。

The

また、払出制御用マイクロコンピュータ370は、出力ポート372cを介して、7セグメントLEDによるエラー表示用LED374にエラー信号を出力する。さらに、出力ポート372bを介して、点灯/消灯を指示するための信号を賞球LED51および球切れLED52に出力する。なお、払出制御基板37の入力ポート372fには、エラー状態を解除するためのエラー解除スイッチ375からの検出信号が入力される。エラー解除スイッチ375は、ソフトウェアリセットによってエラー状態を解除するために用いられる。

Also, the

さらに、払出制御用マイクロコンピュータ370からの払出モータ289への駆動信号は、出力ポート372aおよび中継基板72を介して球払出装置97の払出機構部分における払出モータ289に伝えられる。なお、出力ポート372aの外側に、ドライバ回路(モータ駆動回路)が設置されているが、図6では記載省略されている。

Further, a drive signal from the

遊技機に隣接して設置されているカードユニット50には、カードユニット制御用マイクロコンピュータが搭載されている。また、カードユニット50には、使用可表示ランプ、連結台方向表示器、カード投入表示ランプおよびカード挿入口が設けられている。インタフェース基板(中継基板)66には、打球供給皿3の近傍に設けられている度数表示LED60、球貸し可LED61、球貸しスイッチ62および返却スイッチ63が接続される。

A card unit control microcomputer is mounted on the

インタフェース基板66からカードユニット50には、遊技者の操作に応じて、球貸しスイッチ62が操作されたことを示す球貸しスイッチ信号および返却スイッチ63が操作されたことを示す返却スイッチ信号が与えられる。また、カードユニット50からインタフェース基板66には、プリペイドカードの残高を示すカード残高表示信号および球貸し可表示信号が与えられる。カードユニット50と払出制御基板37の間では、接続信号(VL信号)、ユニット操作信号(BRDY信号)、球貸し要求信号(BRQ信号)、球貸し完了信号(EXS信号)およびパチンコ機動作信号(PRDY信号)が入力ポート372fおよび出力ポート372dを介して送受信される。カードユニット50と払出制御基板37の間には、インタフェース基板66が介在している。よって、接続信号(VL信号)等の信号は、図5に示すように、インタフェース基板66を介してカードユニット50と払出制御基板37の間で送受信されることになる。

A card lending switch signal indicating that the ball lending switch 62 has been operated and a return switch signal indicating that the return switch 63 has been operated are provided to the

パチンコ遊技機1の電源が投入されると、払出制御基板37に搭載されている払出制御用マイクロコンピュータ370は、カードユニット50にPRDY信号を出力する。また、カードユニット制御用マイクロコンピュータは、電源が投入されると、VL信号を出力する。払出制御用マイクロコンピュータ370は、VL信号の入力状態によってカードユニット50の接続状態/未接続状態を判定する。カードユニット50においてカードが受け付けられ、球貸しスイッチが操作され球貸しスイッチ信号が入力されると、カードユニット制御用マイクロコンピュータは、払出制御基板37にBRDY信号を出力する。この時点から所定の遅延時間が経過すると、カードユニット制御用マイクロコンピュータは、払出制御基板37にBRQ信号を出力する。

When the power of the

そして、払出制御用マイクロコンピュータ370は、カードユニット50に対するEXS信号を立ち上げ、カードユニット50からのBRQ信号の立ち下がりを検出すると、払出モータ289を駆動し、所定個の貸し球を遊技者に払い出す。そして、払出が完了したら、払出制御用マイクロコンピュータ370は、カードユニット50に対するEXS信号を立ち下げる。その後、カードユニット50からのBRDY信号がオン状態でないことを条件に、遊技制御手段から払出指令信号を受けると賞球払出制御を実行する。

Then, the

カードユニット50で用いられる電源電圧AC24Vは払出制御基板37から供給される。すなわち、カードユニット50に対する電源基板910からの電力供給は、払出制御基板37およびインタフェース基板66を介して行われる。この例では、インタフェース基板66内に配されているカードユニット50に対するAC24Vの電源供給ラインに、カードユニット50を保護するためのヒューズが設けられ、カードユニット50に所定電圧以上の電圧が供給されることが防止される。

The power supply voltage AC24V used in the

また、この実施の形態では、カードユニット50が遊技機とは別体として遊技機に隣接して設置されている場合を例にするが、カードユニット50は遊技機と一体化されていてもよい。また、コイン投入に応じてその金額に応じた遊技球が貸し出されるような場合でも本発明を適用できる。

In this embodiment, the case where the

図6は、中継基板77、音/ランプ制御基板80bおよび図柄制御基板80aの回路構成例を示すブロック図である。この実施の形態では、音/ランプ制御基板80bは、音出力装置27の音出力制御、各ランプ25,28a,28b,28cの表示制御を行う。また、図柄制御基板80aは、可変表示装置9の表示制御を行う。また、この実施の形態では、「演出制御」とは、可変表示装置9の表示制御や、スピーカ27の音出力制御、各ランプ25,28a,28b,28cの表示制御を行うことによって、遊技演出などの演出を行うことをいう。また、演出制御手段は、可変表示装置9の表示制御を行う図柄制御用マイクロコンピュータ100aと、スピーカ27の音出力制御、および各ランプ25,28a,28b,28cの表示制御を行う音/ランプ制御用マイクロコンピュータ100bとによって実現される。なお、この実施の形態では、音/ランプ制御用マイクロコンピュータ100bと図柄制御用マイクロコンピュータ100aの両方またはいずれか一方を指して、演出制御手段ということがある。また、音/ランプ制御基板80bおよび図柄制御基板80aを設けずに、演出制御に関して演出制御基板のみを設けてもよい。

FIG. 6 is a block diagram showing a circuit configuration example of the

音/ランプ制御基板80bは、音/ランプ制御用CPU101bおよびRAMを含む音/ランプ制御用マイクロコンピュータ100bを搭載している。なお、RAMは外付けであってもよい。音/ランプ制御基板80bにおいて、音/ランプ制御用CPU101bは、内蔵または外付けのROM(図示せず)に格納されたプログラムに従って動作し、中継基板77を介して入力される主基板31からの取込信号(演出制御INT信号)に応じて、入力ドライバ102および入力ポート103を介して演出制御コマンドを受信する。

The sound /

演出制御コマンドおよび演出制御INT信号は、音/ランプ制御基板80bにおいて、まず、入力ドライバ102に入力する。入力ドライバ102は、中継基板77から入力された信号を音/ランプ制御基板80bの内部に向かう方向にしか通過させない(音/ランプ制御基板80bの内部から中継基板77への方向には信号を通過させない)信号方向規制手段としての単方向性回路でもある。

The effect control command and the effect control INT signal are first input to the

中継基板77には、主基板31から入力された信号を音/ランプ制御基板80bに向かう方向にしか通過させない(音/ランプ制御基板80bから中継基板77への方向には信号を通過させない)信号方向規制手段としての単方向性回路74が搭載されている。単方向性回路として、例えばダイオードやトランジスタが使用される。図6には、ダイオードが例示されている。また、単方向性回路は、各信号毎に設けられる。さらに、単方向性回路である出力ポート571を介して主基板31から演出制御コマンドおよび演出制御INT信号が出力されるので、中継基板77から主基板31の内部に向かう信号が規制される。すなわち、中継基板77からの信号は主基板31の内部(遊技制御用マイクロコンピュータ560側)に入り込まない。なお、出力ポート571は、図4に示されたI/Oポート部57の一部である。また、出力ポート571の外側(中継基板77側)に、さらに、単方向性回路である信号ドライバ回路が設けられていてもよい。

A signal that allows the signal input from the

さらに、音/ランプ制御用CPU101bは、ランプドライバ352に対してランプを駆動する信号を出力する。ランプドライバ352は、ランプを駆動する信号を増幅して天枠ランプ28a、左枠ランプ28b、右枠ランプ28cなどの枠側に設けられている各ランプに供給する。また、枠側に設けられている装飾ランプ25に供給する。

Further, the sound /

また、音/ランプ制御用CPU101bは、音声合成用IC173に対して音番号データを出力する。音声合成用IC173は、音番号データに応じた音声や効果音を発生し増幅回路175に出力する。増幅回路175は、音声合成用IC173の出力レベルを、ボリューム176で設定されている音量に応じたレベルに増幅した音声信号をスピーカ27に出力する。音声データROM174には、音番号データに応じた制御データが格納されている。音番号データに応じた制御データは、所定期間(例えば飾り図柄の変動期間)における効果音または音声の出力態様を時系列的に示すデータの集まりである。

Further, the sound /

なお、ランプを駆動する信号および音番号データは、音/ランプ制御用CPU101bとランプドライバ352および音声合成IC173との間で、双方向通信(信号受信側から送信側に応答信号を送信するような通信)によって伝達される。

The signal for driving the lamp and the sound number data are communicated between the sound /

また、音/ランプ制御用マイクロコンピュータ100bは、演出制御コマンド(例えば、変動パターンコマンド)にもとづいて、可変表示装置9を用いて行う演出内容を決定する。例えば、音/ランプ制御用マイクロコンピュータ100bは、可変表示装置9を用いて予告演出を行うか否かを決定する。また、例えば、音/ランプ制御用マイクロコンピュータ100bは、可変表示装置9を用いて行う予告演出の種類を決定する。

In addition, the sound /

なお、「予告演出」とは、大当りとなるまたはその可能性があることを事前(可変表示装置9において飾り図柄の停止図柄が導出表示される前に)に遊技者に報知するための演出をいう。例えば、変動中に異なった態様(速度や回転方向等)の変動を行ったりキャラクタ等を登場させたりすることにより大当りになる可能性があることを遊技者に報知する。 The “notice effect” is an effect for informing the player in advance (before the decorative symbol stop symbol is derived and displayed on the variable display device 9) that it is a big hit or is likely to be a big hit. Say. For example, the player is informed that there is a possibility of a big hit by changing a different mode (speed, direction of rotation, etc.) or making a character appear during the change.

また、音/ランプ制御用マイクロコンピュータ100bは、主基板31からの演出制御コマンド(例えば、表示結果指定コマンド)を、入出力ポート104を介して図柄制御基板80aに転送(送信)する。また、音/ランプ制御用マイクロコンピュータ100bは、決定した演出内容(予告演出を行うか否かや、予告演出の種類)を示す演出内容指定コマンドを生成する。また、音/ランプ制御用マイクロコンピュータ100bは、生成した演出内容指定コマンドを、入出力ポート104を介して図柄制御基板80aに送信する。

In addition, the sound /

なお、音/ランプ制御用マイクロコンピュータ100bは、決定した演出内容(予告演出を行うか否かや、予告演出の種類)を、演出制御コマンド(変動パターンコマンドや表示結果指定コマンド)に付加してもよい。そして、音/ランプ制御用マイクロコンピュータ100bは、演出内容を付加した演出制御コマンドを、入出力ポート104を介して図柄制御基板80aに送信してもよい。

Note that the sound /

図柄制御基板80aは、図柄制御用CPU101aおよびRAMを含む図柄制御用マイクロコンピュータ100aを搭載している。なお、RAMは外付けであってもよい。図柄制御基板80aにおいて、図柄制御用CPU101aは、内蔵または外付けのROM(図示せず)に格納されたプログラムに従って動作する。また、図柄制御用CPU101aは、音/ランプ制御用基板80bから受信した演出制御コマンドにもとづいて、VDP(ビデオディスプレイプロセッサ)109に、LCDを用いた可変表示装置9の表示制御を行わせる。

The

図柄制御用CPU101aは、受信した演出制御コマンドに従ってキャラクタROM(図示せず)から必要なデータを読み出す。キャラクタROMは、可変表示装置9に表示される画像の中でも使用頻度の高いキャラクタ画像データ、具体的には、人物、文字、図形または記号等(飾り図柄を含む)をあらかじめ格納しておくためのものである。図柄制御用CPU101aは、キャラクタROMから読み出したデータをVDP109に出力する。VDP109は、図柄制御用CPU101aから入力されたデータにもとづいて表示制御を実行する。

The symbol control CPU 101a reads necessary data from a character ROM (not shown) in accordance with the received effect control command. The character ROM stores character image data frequently used among images displayed on the

この実施の形態では、可変表示装置9の表示制御を行うVDP109が図柄制御基板80aに搭載されている。VDP109は、図柄制御用マイクロコンピュータ100aとは独立したアドレス空間を有し、そこにVRAMをマッピングする。VRAMは、VDPによって生成された画像データを展開するためのバッファメモリである。そして、VDP109は、VRAM内の画像データを可変表示装置9に出力する。なお、可変表示装置の数に対応した数のVDPを図柄制御基板80aに搭載するようにしてもよい。

In this embodiment, the

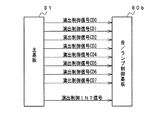

図7は、主基板31における回路構成および主基板31から音/ランプ制御基板80bに送信される演出制御コマンドの信号線を示すブロック図である。図7に示すように、この実施の形態では、主基板31が搭載する遊技制御用マイクロコンピュータ560は、演出制御信号送信用の8本の信号線CD0〜CD7を用いて、演出制御コマンドを音/ランプ制御基板80bに送信する。また、主基板31と音/ランプ制御基板80bとの間には、ストローブ信号を送受するための演出制御INT信号の信号線も配線されている。

FIG. 7 is a block diagram showing a circuit configuration of the

主基板31には、図7に示すように、始動口スイッチ14aからの配線が接続されている。また、主基板31には、大入賞口である特別可変入賞球装置20や、その他の入賞口への遊技球の入賞等を検出するための各種スイッチ29a,30a,33a,39aからの配線も接続されている。さらに、主基板31には、可変入賞球装置15を開閉するソレノイド16、特別可変入賞球装置20を開閉するソレノイド21および大入賞口内の経路を切り換えるためのソレノイド21Aへの配線が接続されている。

As shown in FIG. 7, wiring from the

主基板31は、遊技制御用マイクロコンピュータ560、入力ドライバ回路58および出力回路59を搭載する。遊技制御用マイクロコンピュータ560は、クロック回路501、システムリセット手段として機能するリセットコントローラ502、乱数回路503a,503b、ゲーム制御用のプログラム等を記憶するROM54、ワークメモリとして使用されるRAM55、プログラムに従って動作するCPU56、CPU56に割込要求信号(タイマ割込による割込要求信号)を送出するCTC504、払出制御基板37や音/ランプ制御基板80bが備えるマイクロコンピュータと非同期シリアル通信を行うシリアル通信回路505およびI/Oポート部57を内蔵する。

The

なお、この実施の形態では、シリアル通信回路505を内蔵するマイクロコンピュータを搭載した基板(例えば、主基板31)とは異なる基板(例えば、払出制御基板37や音/ランプ制御基板80b)のマイクロコンピュータとの通信にシリアル通信回路505を用いる場合を説明するが、シリアル通信回路505は、シリアル通信回路505を内蔵するマイクロコンピュータを搭載した基板が備える別のマイクロコンピュータとシリアル通信を行ってもよい。例えば、同じ構成の2つのマイクロコンピュータが同じ基板に搭載されている場合に、各マイクロコンピュータが内蔵するシリアル通信回路が相互にシリアル通信を行ってもよい。

In this embodiment, the microcomputer on a board (for example, the

クロック回路501は、システムクロック信号を27(=128)分周して生成した所定の周期の基準クロック信号CLKを、各乱数回路503a,503bに出力する。リセットコントローラ502は、ローレベルの信号が一定期間入力されたとき、CPU56および各乱数回路503a,503bに所定の初期化信号を出力して、遊技制御用マイクロコンピュータ560をシステムリセットする。

The

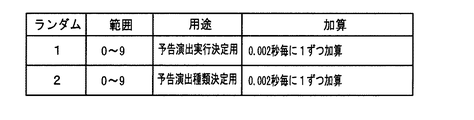

また、この実施の形態では、図7に示すように、遊技制御用マイクロコンピュータ560は、発生可能な乱数の値の範囲が異なる2つの乱数回路503a,503bを搭載する。乱数回路503aは、12ビットの疑似乱数を発生する乱数回路(以下、12ビット乱数回路ともいう)である。12ビット乱数回路503aは、12ビットで発生できる範囲(すなわち、0から4095までの範囲)の値の乱数を発生する機能を備える。また、乱数回路503bは、16ビットの疑似乱数を発生する乱数回路(以下、16ビット乱数回路ともいう)である。16ビット乱数回路503bは、16ビットで発生できる範囲(すなわち、0から65535までの範囲)の値の乱数を発生する機能を備える。なお、この実施の形態では、遊技制御用マイクロコンピュータ560が2つの乱数回路を内蔵する場合を説明するが、遊技制御用マイクロコンピュータ560は、3以上の乱数回路を内蔵してもよい。また、この実施の形態では、12ビット乱数回路503aおよび16ビット乱数回路503bを包括的に表現する場合、または、12ビット乱数回路503aと16ビット乱数回路503bとのうちいずれかを指す場合に、乱数回路503という。

Further, in this embodiment, as shown in FIG. 7, the

次に、乱数回路503の構成について説明する。図8は、乱数回路503の構成例を示すブロック図である。なお、この実施の形態において、12ビット乱数回路503aと16ビット乱数回路503bとの基本的な構成は同じである。図8に示すように、乱数回路503は、カウンタ521、比較器522、カウント値順列変更回路523、クロック信号出力回路524、カウント値更新信号出力回路525、乱数値読取信号出力回路526、乱数更新方式選択信号出力回路527、セレクタ528、乱数回路起動信号出力回路530、乱数値記憶回路531、反転回路532、ラッチ信号生成回路533およびタイマ回路534とを含む。

Next, the configuration of the

この実施の形態では、乱数回路503は、複数種類の識別情報の可変表示の表示結果を特定の表示結果とするか否か(例えば、特別図柄表示装置8の表示図柄の組み合わせを大当り図柄の組み合わせとするか否か)を判定するための大当り判定用の乱数を発生する。そして、遊技制御用マイクロコンピュータ560のCPU56は、乱数回路503が発生した乱数にもとづいて特定の表示結果とすると判定すると、遊技状態を遊技者にとって有利な特定遊技状態(例えば、大当り遊技状態)に移行させる。

In this embodiment, the

カウンタ521は、セレクタ528によって選択された所定の信号を入力し、セレクタ528から入力する信号に応答してカウント値Cを出力する。この場合、カウンタ521は、所定の初期値を入力し、カウント値Cを一定の規則に従って初期値から所定の最終値まで循環的に更新して出力する。また、カウンタ521は、カウント値Cを最終値まで更新すると、カウント値Cを最終値まで更新した旨を示す通知信号をCPU56に出力する。この実施の形態では、カウンタ521から通知信号が出力されると、CPU56によって初期値が更新される。

The counter 521 receives the predetermined signal selected by the

この実施の形態において、カウンタ521は、セレクタ528から信号を入力するごとに(セレクタ528からの信号における立ち上がりエッヂが入力されるごとに)、カウント値Cを「0」から「4095」まで1ずつカウントアップする。また、カウンタ521は、カウント値Cを「4095」までカウントアップすると、カウント値Cを最終値まで更新した旨を示す通知信号をCPU56に出力する。すると、CPU56は、カウンタ521から通知信号を入力し、初期値を更新する。そして、カウンタ521は、CPU56によって更新された初期値から「4095」まで、再びカウント値Cをカウントアップする。また、「4095」までカウントアップすると、カウンタ521は、再び「0」からカウントを開始する。そして、カウンタ521は、更新後の初期値の1つ前の値(最終値)までカウントアップすると、通知信号をCPU56に出力する。なお、この実施の形態では、比較器522は、後述するように、全てのカウント値を入力すると通知信号をカウンタ521に出力する。この場合、カウンタ521は、比較器522から通知信号を入力すると、カウント値をリセットして「0」にする。

In this embodiment, every time a signal is input from the selector 528 (every time a rising edge in the signal from the

なお、比較器522は、入力したカウント値が乱数最大値設定レジスタ535に設定されている乱数最大値より大きいか否かを判断し、カウント値が乱数最大値より大きい(乱数最大値を超えた)と判断すると、通知信号をカウンタ521に出力してもよい。この場合、例えば、比較器522は、カウント値が乱数最大値を超えたと判断すると、クロック信号出力回路524が次に乱数発生用クロック信号SI1を出力する前に、通知信号をカウンタ521に出力する。例えば、乱数最大値設定レジスタ535に乱数最大値「256」が設定されている場合を考える。この場合、カウンタ521が「0」から「256」までカウントアップし、さらにカウント値「257」を出力すると、比較器522は、入力したカウント値「257」が乱数最大値「256」を超えたと判断し、カウンタ521に通知信号を出力する。比較器522から通知信号を入力すると、カウンタ521は、クロック信号出力回路524からの乱数発生用クロック信号SI1の入力を待つことなく、カウント値を「258」に更新し出力する。以上の処理を繰り返し実行することによって、比較器522は、カウント値「257」から「4095」まで入力している間、カウント値が乱数最大値を超えていると判断して、繰り返しカウンタ521に通知信号を出力する。そして、カウンタ521は、比較器522から通知信号を入力している間、クロック信号出力回路524からの乱数発生用クロック信号SI1の入力を待つことなく、カウント値を繰り返し更新し出力する。そのようにすることによって、クロック信号出力回路524が次に乱数発生用クロック信号SI1を出力するまでの間に、「257」から「4095」までカウント値を高速にカウントアップさせるように制御し、「257」から「4095」までの乱数値を読み飛ばす(乱数値記憶回路531に記憶させない)ように制御する。

The comparator 522 determines whether the input count value is larger than the random number maximum value set in the random number maximum

カウント値順列変更回路523は、カウント値順列変更レジスタ(RSC)536、更新規則選択レジスタ(RRC)542および更新規則メモリ543を含む。カウント値順列変更レジスタ536は、カウンタ521がカウントアップするカウント値Cの更新順である順列(初期値から最終値までの並び順)を変更させるためのカウント値順列変更データ「01h」を格納する。カウント値順列変更回路523は、カウント値順列変更レジスタ536に数値順列変更データ「01h」が格納されているとき、カウンタ521がカウントアップして更新するカウント値Cの順列を、カウント値順列変更データ「01h」が格納されていないときとは異なる順列に変更する。この場合、カウント値順列変更回路523は、数値順列変更データ「01h」が格納されているとき、カウント値の順列の変更に用いる更新規則を切り換える。また、カウント値の順列の変更に用いる更新規則を切り換えた後に、カウンタ521がカウント値の更新を開始すると、カウント値順列変更レジスタ536のカウント値順列変更データは、CPU56によって、「01h」から初期値である「0(=00h)」に戻される(クリアされる)。

The count value

なお、CPU56によってカウント値順列変更データをクリアするのでなく、乱数回路503側でカウント値順列変更データをクリアするようにしてもよい。例えば、カウント値順列変更レジスタ536にカウント値順列変更データ「01h」が書き込まれたことにもとづいて、更新規則選択レジスタ(RRC)542にレジスタ値が設定されると、カウント値順列変更回路523は、カウント値順列変更レジスタ536のレジスタ値をクリアするようにしてもよい。

Instead of clearing the count value permutation data by the

図9は、更新規則選択レジスタ542の例を示す説明図である。更新規則選択レジスタ542は、カウンタ521が出力するカウント値の並び順の並べ替え(順列の変更)に用いる更新規則を設定するレジスタである。この実施の形態では、更新規則選択レジスタ542にレジスタ値が設定されることによって、カウンタ521が出力するカウント値の順列の変更に用いる更新規則が設定される。図9に示すように、更新規則選択レジスタ542は、8ビットレジスタであり、初期値が「0(=00h)」に設定されている。また、更新規則選択レジスタ542は、ビット0〜ビット3が書込および読出ともに可能な状態に構成されている。また、更新規則選択レジスタ542は、ビット4〜ビット7が書込および読出ともに不可能な状態に構成されている。したがって、更新規則選択レジスタ542のビット4〜ビット7に値を書き込む制御を行っても無効とされ、ビット4〜ビット7から読み出す値は全て「0(=0000b)」である。

FIG. 9 is an explanatory diagram illustrating an example of the update

更新規則選択レジスタ542の値(レジスタ値)は、カウント値順列変更レジスタ536にカウント値順列変更データ「01h」が書き込まれたことに応じて、レジスタ値が「0(=00h)」から「15(=0Fh)」まで循環的に更新される。すなわち、カウント値順列変更レジスタ536にカウント値順列データ「01h」が書き込まれるごとに、更新規則選択レジスタ542のレジスタ値は、「0」から「1」ずつ加算され、「15」になると再び「0」に戻る。

The value (register value) of the update

図10は、更新規則メモリ543の例を示す説明図である。図10に示すように、更新規則メモリ543は、更新規則選択レジスタ542の値(レジスタ値)と、カウント値の更新規則とを対応付けて格納している。図10に示す例では、例えば、更新規則選択レジスタ542にレジスタ値1が設定されている場合、更新規則Bを用いて、カウンタ521が出力するカウント値の順列が変更されることが分かる。なお、図10において、更新規則Aは、カウンタ521がカウント値Cを更新する規則と同一の更新規則であり、レジスタ値「0」に対応づけて更新規則メモリ543に格納される。また、更新規則メモリ543には、カウンタ521がカウント値Cを更新する更新規則とは異なる更新規則B〜Pが、レジスタ値「1」〜「15」に対応づけて格納される。

FIG. 10 is an explanatory diagram showing an example of the

カウント値順列変更回路523は、カウント値順列変更レジスタ536にカウント値順列変更データ「01h」が書き込まれている場合、まず、カウンタ521からカウント値の最終値「4095」が最初に入力されるまで、現在設定されている更新規則に従って、そのままカウント値を出力する。そして、カウント値順列変更回路523は、カウンタ521からカウント値の最終値「4095」を入力すると、カウント値の更新規則を変更する。なお、CPU56によって初期値が変更されている場合には、カウント値順列変更回路523は、カウンタ521から変更後の最終値(初期値の1つ前の値)まで入力すると、カウント値の更新規則を変更することになる。

When the count value permutation change data “01h” is written in the count value permutation change register 536, the count value

カウント値順列変更回路523は、更新規則選択レジスタ542のレジスタ値に対応する更新規則を更新規則メモリ543から選択し、カウント値の順列の変更に用いる更新規則として設定する。また、カウント値順列変更回路523は、カウンタ521によって再び初期値「0」から順にカウント値の更新が開始されると、設定した更新規則に従って、カウント値の初期値から最終値までの順列を変更する。なお、CPU56によって初期値が変更されている場合には、カウント値順列変更回路523は、カウンタ521によって変更後の初期値から順にカウント値の更新が開始されると、設定した更新規則に従って、カウント値の初期値から最終値までの順列を変更することになる。そして、カウント値順列変更回路523は、変更した順列に従ってカウント値を出力する。

The count value

なお、この実施の形態では、後述する乱数最大値設定レジスタ535に乱数最大値が設定されていることによって、発生させる乱数の最大値が制限されている場合、カウント値順列変更回路523は、カウント値Cを乱数最大値以下に制限して順列を変更して出力する。例えば、乱数最大値設定レジスタ535に乱数最大値「256」が設定されているものとし、カウント値順列変更回路523が、更新規則Aから更新規則Bに変更して、カウント値の順列を変更するものとする。この場合、カウント値順列変更回路523は、比較器522の乱数最大値設定レジスタ535に設定されている乱数最大値「256」にもとづいて、更新規則Bに従って、カウント値の順列を「256→255→・・・→0」に変更して出力する。

In this embodiment, when the maximum random number to be generated is limited by setting the random number maximum value in a random number maximum

以上のように、カウント値順列変更回路523は、カウント値順列変更レジスタ536にカウント値順列変更データ「01h」が書き込まれている場合、更新規則を切り替えて用いることによって、カウント値Cの順列を変更して出力する。そのため、乱数回路503が生成する乱数のランダム性を向上させることができる。

As described above, when the count value permutation change data “01h” is written in the count value permutation change register 536, the count value

図11は、カウント値順列変更回路523が、カウンタ521が出力するカウント値の順列を変更する場合の例を示す説明図である。図11に示すように、CPU56は、所定のタイミングで、カウント値順列変更データ「01h」をカウント値順列変更レジスタ536に書き込む。すると、更新規則選択レジスタ542のレジスタ値が1加算される。例えば、更新規則選択レジスタ542のレジスタ値が「0」から「1」に更新される。レジスタ値が更新されると、カウント値順列変更回路523は、カウンタ521から最初にカウント値の最終値「4095」が入力されるまで、更新前のレジスタ値「0」に対応する「更新規則A」に従ってカウント値を更新して出力する。このとき、カウント値順列変更回路523は、更新規則Aに従って、「0→1→・・・→4095」の順列でカウント値を出力する。

FIG. 11 is an explanatory diagram illustrating an example in which the count value

カウンタ521からカウント値の最終値「4095」が入力されると、カウント値順列変更回路523は、更新規則メモリ543から、更新後のレジスタ値「1」に対応する「更新規則B」を選択して設定する。カウント値順列変更回路523は、カウンタ521から再び初期値「0」以降のカウント値の入力を開始すると、選択設定した「更新規則B」に従って、カウント値の順列を変更して出力する。本例では、カウント値順列変更回路523は、順列を「0→1→・・・→4095」から「4095→4094→・・・→0」に変更して、カウント値を出力する。

When the final value “4095” of the count value is input from the counter 521, the count value

その後、カウント値順列変更レジスタ536は、後述するように、カウント値順列変更回路523が切り替え後の更新規則に従ってカウント値の更新動作を開始したことに応じてリセットされる。そして、次にカウント値順列変更データ「01h」がカウント値順列変更レジスタ536に書き込まれるまで、カウント値順列変更回路523は、「4095→4094→・・・→0」のままの順列で、カウント値を出力し続ける。

Thereafter, the count value permutation change register 536 is reset in response to the count value

CPU56によってカウント値順列変更データ「01h」がカウント値順列変更レジスタ536に再度書き込まれると、カウント値順列変更レジスタ536のレジスタ値が「1」から「2」に更新される。そして、カウンタ521からカウント値の最終値「4095」を入力すると、カウント値順列変更回路523は、更新規則メモリ543から、レジスタ値「2」に対応する「更新規則C」を選択して設定する。カウント値順列変更回路523は、カウンタ521から再び初期値「0」以降のカウント値の入力を開始すると、選択設定した「更新規則C」に従って、カウント値の順列を更新して出力する。本例では、カウント値順列変更回路523は、順列を「4095→4094→・・・→0」から「1→3→…→4095→0→・・・→4094」に変更して、カウント値を出力する。

When the count value permutation change data “01h” is written again to the count value permutation change register 536 by the

以上のように、カウント値順列変更レジスタ536をリセットした後、カウント値順列データ「01h」をカウント値順列変更レジスタ536に再度書き込むことによって、カウント値の順列をさらに変更することができる。 As described above, after the count value permutation change register 536 is reset, the count value permutation data “01h” is written again in the count value permutation change register 536, so that the count value permutation can be further changed.

図12は、カウント値順列変更レジスタ536の例を示す説明図である。カウント値順列変更レジスタ536は、カウンタ521がカウントアップするカウント値の順列を変更させるためのカウント値順列変更データ「01h」を設定するレジスタである。図12に示すように、カウント値順列変更レジスタ536は、読出可能な8ビットレジスタであり、初期値が「0(=00h)」に設定されている。また、カウント値順列変更レジスタ536は、ビット0だけが書込および読出ともに可能な状態に構成されている。すなわち、カウント値順列変更レジスタ536は、ビット1〜ビット7が書込および読出ともに不可能な状態に構成されている。したがって、カウント値順列変更レジスタ536のビット1〜ビット7に値を書き込む制御を行っても無効とされ、ビット1〜ビット7から読み出す値は全て「0(=0000000b)」である。

FIG. 12 is an explanatory diagram illustrating an example of the count value permutation change register 536. The count value permutation change register 536 is a register that sets count value permutation change data “01h” for changing the permutation of count values counted up by the counter 521. As shown in FIG. 12, the count value permutation change register 536 is a readable 8-bit register, and the initial value is set to “0 (= 00h)”. Further, count value permutation change register 536 is configured such that only bit 0 can be written and read. That is, count value permutation change register 536 is configured such that

なお、カウント値順列変更レジスタ536の値は、カウント値順列変更回路523が切り替え後の更新規則に従ってカウント値の更新動作を開始したことに応じて、CPU56によってリセットされる。この場合、CPU56は、カウント値順列変更レジスタ536に書き込まれている値を、カウント値順列変更データ「01h」から初期値である「0(=00h)」に戻す。

Note that the value of the count value permutation change register 536 is reset by the

比較器522は、ランダムRの最大値(乱数最大値)を指定するための乱数最大値設定データを格納する乱数最大値設定レジスタ(RMX)535を備える。比較器522は、乱数最大値設定レジスタ535に格納されている乱数最大値設定データに示される乱数最大値に従って、カウンタ521が更新するカウント値の更新範囲を制限する。この実施の形態では、比較器522は、カウンタ521から入力するカウント値と乱数最大値設定レジスタ535に格納されている乱数最大値設定データ(例えば「00FFh」)に示される乱数最大値(例えば「256」)とを比較する。そして、比較器522は、入力したカウント値が乱数最大値以下であると判断すると、入力したカウント値を乱数値記憶回路531に出力する。

The comparator 522 includes a random number maximum value setting register (RMX) 535 that stores random number maximum value setting data for designating the maximum value of random R (random number maximum value). The comparator 522 limits the update range of the count value updated by the counter 521 in accordance with the random number maximum value indicated in the random number maximum value setting data stored in the random number maximum

この実施の形態では、比較器522は、具体的には、以下のような制御を行う。比較器522は、カウント値の初期値更新の際に、CPU56からカウント値の初期値をもらい、初期値から乱数最大値までのカウント値の個数を求める。例えば、カウント値の初期値が「157」であり乱数最大値が「256」である場合、比較器522は、初期値から乱数最大値までのカウント値の個数を「100個」と求める。また、比較器522は、カウント値順列変更回路523からカウント値を入力するに従って、初期値からカウント値をいくつ入力したかをカウントアップする。初期値からカウント値を入力した回数が「100回」に達すると、比較器522は、初期値「157」から最大値「256」までの全てのカウント値を入力したと判断する。そして、比較器522は、全てのカウント値を入力した旨の通知信号をカウンタ521に出力する。カウント値の個数で判断することによって、カウント値順列変更回路523によってカウント値の順列が変更されている場合であっても、比較器522は、カウント値の更新範囲を乱数最大値以下に制限し、全てのカウント値を入力した際にカウンタ521に通知信号を出力することができる。

In this embodiment, the comparator 522 specifically performs the following control. The comparator 522 obtains the initial value of the count value from the

カウント値の更新範囲を比較器522が制限する動作について説明する。なお、本例では、カウント値順列変更回路523が更新規則Aを選択し、乱数最大値設定レジスタ535に乱数最大値「256」が設定されている場合を説明する。

An operation in which the comparator 522 limits the update range of the count value will be described. In this example, a case where the count value

カウンタ521が「0」から「256」までカウント値を更新している間、カウント値順列変更回路523は、乱数最大値設定レジスタ535に設定されている乱数最大値「256」にもとづいて、更新規則Aに従って、「0」から「256」までのカウント値をそのまま比較器522に出力する。この場合、カウント値順列変更回路523は、比較器522から乱数最大値「256」の値をもらい、カウンタ521から入力するカウント値が乱数最大値より大きいか否かを判断し、更新規則が変更されているとき(例えば、更新規則B)であっても、乱数最大値設定レジスタ535に設定されている乱数最大値「256」にもとづいて、「257」から「4095」までのカウント値を比較器522に出力しない。カウンタ521は、例えば、初期値が「0」と設定されているときに、最終値「256」までカウント値を更新すると、通知信号をCPU56に出力する。通知信号を出力すると、CPU56によって、カウンタ521のカウント値の初期値が変更される。本例では、CPU56によって、初期値が「50」に変更されるものとする。

While the counter 521 is updating the count value from “0” to “256”, the count value

なお、カウント値が乱数最大値「256」より大きいか否かをカウント値順列変更回路523が判断するのでなく、比較器522が判定するようにしてもよい。この場合、例えば、比較器522は、カウント値が乱数最大値設定レジスタ535に設定されている乱数最大値より大きいか否かを判断し、カウント値が乱数最大値より大きいと判断すると、通知信号をカウンタ521に出力する。そして、比較器522は、カウント値が乱数最大値を超えたと判断すると、クロック信号出力回路524が次に乱数発生用クロック信号SI1を出力する前に、通知信号をカウンタ521に出力する。そのようにすることによって、比較器522は、クロック信号出力回路524が次に乱数発生用クロック信号SI1を出力するまでの間に、「257」から「4095」までカウント値を高速にカウントアップさせるようにカウンタ521を制御する。そのようにすることによって、カウント値順列変更回路523からの値が「257」未満のときだけカウント値を乱数値記憶回路531に出力するようにし、カウント値順列変更回路523からの値が「257」以上のときにはカウント値を高速で更新させるようにすることができる。

Note that the comparator 522 may determine whether the count value is greater than the maximum random number “256”, instead of the count value

更新規則Aにもとづいて、カウント値順列変更回路523から、「0」から「255」までカウント値を入力している間、比較器522は、入力するカウント値が乱数最大値「256」以下であるので、入力したカウント値をそのまま乱数値記憶回路531に出力する。次に、カウント値順列変更回路523から入力するカウント値が「256」に達すると、比較器522は、入力したカウント値を乱数値記憶回路531に出力するとともに、初期値から最大値までの全てのカウント値を入力した旨の通知信号をカウンタ521に出力する。具体的には、比較器522は、カウント値の初期値変更の際に、CPU56からカウント値の初期値(本例では、「0」)をもらい、初期値「0」から乱数最大値(本例では、「256」)までのカウント値の個数(本例では、「257個」)を求める。そして、カウント値順列変更回路523から入力したカウント値の個数が257個に達すると、全てのカウント値を入力した旨の通知信号をカウンタ521に出力する。なお、本例では、CPU56によって初期値が「50」に変更されるので、カウンタ521は、比較器522から通知信号を入力しても、カウント値をリセットするとなく、変更後の初期値「50」からカウント値の更新を行う。

Based on the update rule A, while the count value is input from “0” to “255” from the count value

カウンタ521が変更後の初期値「50」から「256」までカウント値を更新している間、カウント値順列変更回路523は、乱数最大値設定レジスタ535に設定されている乱数最大値「256」にもとづいて、更新規則Aに従って、「50」から「256」までのカウント値をそのまま比較器522に出力する。また、カウント値順列変更回路523は、乱数最大値設定レジスタ535に設定されている乱数最大値「256」にもとづいて、「257」から「4095」までのカウント値を比較器522に出力せず、カウンタ521の更新するカウント値が1周したとき(257回更新したとき)に、カウント値順列変更レジスタ536にカウント値順列変更データが書き込まれた場合には、カウント値順列変更回路523は、カウント値の順列を変更して出力する。例えば、更新規則が更新規則Bに変更された場合、カウント値順列変更回路523は、カウント値の順列を「256→255→・・・→50」に変更して出力する。

While the counter 521 updates the count value from the changed initial value “50” to “256”, the count value

カウント値順列変更回路523から、「256」から「50」までカウント値を入力している間、比較器522は、入力したカウント値をそのまま乱数値記憶回路531に出力する。次に、カウント値順列変更回路523から入力するカウント値が「50」に達すると、比較器522は、入力したカウント値を乱数値記憶回路531に出力するとともに、初期値から最大値までの全てのカウント値を入力した旨の通知信号をカウンタ521に出力する。具体的には、比較器522は、カウント値の初期値変更の際に、CPU56からカウント値の初期値(本例では、「50」)をもらい、初期値「50」から乱数最大値(本例では、「256」)までのカウント値の個数(本例では、「207個」)を求める。そして、カウント値順列変更回路523から入力したカウント値の個数が207個に達すると、全てのカウント値を入力した旨の通知信号をカウンタ521に出力する。

While the count values from “256” to “50” are input from the count value

なお、カウント値順列変更回路523がカウント値の順列を変更した場合であっても、比較器522は、カウント値の個数が207個に達すると、通知信号をカウンタ521に出力する。そのようにすることによって、カウント値の順列が変更された場合であっても、初期値「50」から最大値「256」までの全てのカウント値を入力したことにもとづいて、通知信号をカウンタ521に出力できる。

Even when the count value

比較器522から通知信号を入力すると、カウンタ521は、カウント値の初期値をリセットし「0」に戻す。そして、カウンタ521は、「0」からカウント値の更新を行う。カウンタ521の値が「0」から再び更新がされると、カウンタ521からのカウント値にもとづいて、カウント値順列変更回路523は「49」〜「0」までのカウント値を比較器522に出力し、比較器522はカウント値順列変更回路523からのカウント値の入力にもとづいて乱数値記憶回路531にカウント値を出力する。そして、カウンタ521は、最終値(本例では、「49」)までカウント値を更新すると、通知信号をCPU56に出力する。通知信号を出力すると、CPU56によって、カウンタ521のカウント値の初期値が再び変更される。

When the notification signal is input from the comparator 522, the counter 521 resets the initial value of the count value and returns it to “0”. Then, the counter 521 updates the count value from “0”. When the value of the counter 521 is updated again from “0”, the count value

以上のような動作を繰り返すことにより、比較器522は、カウンタ521に、「0」から乱数最大値「256」まで連続的にカウント値をカウントアップさせ、「0」から「256」までの値を乱数値記憶回路531にランダムR(乱数値)として記憶させる。すなわち、比較器522は、カウント値の更新範囲を乱数最大値「256」以下に制限して、カウンタ521にカウント値を更新させる。 By repeating the operation as described above, the comparator 522 causes the counter 521 to continuously count up the count value from “0” to the maximum random number “256”, and the value from “0” to “256”. Is stored in the random value storage circuit 531 as a random R (random number value). That is, the comparator 522 limits the update range of the count value to the random number maximum value “256” or less, and causes the counter 521 to update the count value.

図13は、乱数最大値設定レジスタ535の例を示す説明図である。図13(a)は、12ビット乱数回路503aが搭載する乱数最大値設定レジスタ535の例を示す。また、図13(b)は、16ビット乱数回路503bが搭載する乱数最大値設定レジスタ535の例を示す。まず、12ビット乱数回路503aが搭載する乱数最大値設定レジスタ535について説明する。図13(a)に示すように、12ビット乱数回路503aにおいて、乱数最大値設定レジスタ535は、16ビットレジスタであり、初期値が「4095(=0FFFh)」に設定されている。乱数最大値設定レジスタ535は、ビット0〜ビット11が書込および読出ともに可能な状態に構成されている。また、乱数最大値設定レジスタ535は、ビット12〜ビット15が書込および読出ともに不可能な状態に構成されている。したがって、12ビット乱数回路503aにおいて、乱数最大値設定レジスタ535のビット12〜ビット15に値を書き込む制御を行っても無効とされ、ビット12〜ビット15から読み出す値は全て「0(=0000b)」である。

FIG. 13 is an explanatory diagram illustrating an example of the random number maximum

また、乱数最大値設定レジスタ535に設定される乱数最大値は、所定の下限値が定められている。この実施の形態では、乱数最大値設定レジスタ535に下限値「256」より小さい値を指定する乱数最大値設定データ「0000h」〜「00FEh」が書き込まれた場合、CPU56は、乱数最大値設定レジスタ535に、初期値「4095」を指定する乱数最大値設定データ「0FFFh」を設定しなおす。すなわち、乱数最大値設定レジスタ535に設定可能な乱数最大値は「256」から「4095」までであり、CPU56は、下限値「256」より小さい値が設定されていると判断すると、乱数最大値を所定値「4095」に設定しなおす。なお、CPU56は、リセットコントローラ502によって遊技制御用マイクロコンピュータ560がシステムリセットされるまで、乱数最大値設定データが書き込まれた乱数最大値設定レジスタ535を書込不可能に制御する。なお、CPU56により書込不可能に制御するのでなく、乱数最大値設定レジスタ535は、データが書き込まれた後にリセット信号を入力するまで書込不可能となるように形成されていてもよい。

The random number maximum value set in the random number maximum

次に、16ビット乱数回路503bが搭載する乱数最大値設定レジスタ535について説明する。図13(b)に示すように、16ビット乱数回路503bにおいて、乱数最大値設定レジスタ535は、16ビットレジスタであり、初期値が「65535(=FFFFh)」に設定されている。また、16ビット乱数回路503bにおいて、乱数最大値設定レジスタ535は、ビット0〜ビット15の全てのビットが書込および読出ともに可能な状態に構成されている。

Next, the random number maximum

また、乱数最大値設定レジスタ535に下限値「512」より小さい値を指定する乱数最大値設定データ「0000h」〜「00FEh」が書き込まれた場合、CPU56は、乱数最大値設定レジスタ535に、初期値「65535」を指定する乱数最大値設定データ「FFFFh」を設定しなおす。すなわち、乱数最大値設定レジスタ535に設定可能な乱数最大値は「512」から「65535」までであり、CPU56は、下限値「512」より小さい値が設定されていると判断すると、乱数最大値を所定値「65535」に設定しなおす。なお、CPU56は、リセットコントローラ502によって遊技制御用マイクロコンピュータ560がシステムリセットされるまで、乱数最大値設定データが書き込まれた乱数最大値設定レジスタ535を書込不可能に制御する。この場合、CPU56により書込不可能に制御するのでなく、乱数最大値設定レジスタ535は、データが書き込まれた後にリセット信号を入力するまで書込不可能となるように形成されていてもよい。

When random number maximum value setting data “0000h” to “00FEh” for designating a value smaller than the lower limit value “512” is written in the random number maximum

クロック信号出力回路524は、セレクタ528および反転回路532に出力するクロック信号の周期(すなわち、カウント値の更新周期)を指定するための周期設定データを格納する周期設定レジスタ(RPS)537を備える。クロック信号出力回路524は、周期設定レジスタ537に格納されている周期設定データに基づいて、遊技制御用マイクロコンピュータ560が搭載するクロック回路501から入力する基準クロック信号CLKを分周して、乱数回路503内部で乱数値の生成に用いるクロック信号(乱数発生用クロック信号SI1)を生成する。そのようにすることによって、クロック信号出力回路524は、クロック信号を所定回数入力したことを条件に、カウント値Cを更新させるための乱数発生用クロック信号SI1をカウンタ521に出力するように動作する。なお、周期設定データとは、クロック回路501から入力した基準クロック信号CLKを何分周させるかを設定するためのデータである。また、クロック出力回路524は、生成した乱数発生用クロック信号SI1をセレクタ528および反転回路532に出力する。例えば、周期設定レジスタ537に周期設定データ「0Fh(=16)」が書き込まれている場合、クロック信号出力回路524は、クロック回路501から入力する基準クロック信号CLKを16分周して乱数発生用クロック信号SI1を生成する。この場合、クロック信号出力回路524が生成する乱数発生用クロック信号SI1の周期は、「システムクロック信号の周期×128×16」となる。

The clock

図14は、周期設定レジスタ537の例を示す説明図である。図14に示すように、周期設定レジスタ537は、8ビットレジスタであり、初期値が「256(=FFh)」に設定されている。また、周期設定レジスタ537は、書込および読出ともに可能な状態に構成されている。

FIG. 14 is an explanatory diagram illustrating an example of the

また、周期設定レジスタ537に設定される周期設定データの値は、所定の下限値が定められている。この実施の形態では、周期設定レジスタ537に下限値「システムクロック信号の周期×128×7」より小さい値を指定する周期設定データ「00h〜06h」が書き込まれた場合、CPU56は、周期設定レジスタ537に下限値「システムクロック信号の周期×128×7」を指定する周期設定データ「07h」を設定しなおす。すなわち、周期設定レジスタ537に設定可能な周期は「システムクロック信号の周期×128×7」から「システムクロック信号の周期×128×256」までであり、CPU56は、下限値より小さい値が設定されていると判断すると、周期設定データを設定しなおす。なお、CPU56は、リセットコントローラ502によって遊技制御用マイクロコンピュータ560がシステムリセットされるまで、周期設定データが書き込まれた周期設定レジスタ537を書込不可能に制御する。なお、CPU56により書込不可能に制御するのでなく、周期設定レジスタ537は、データが書き込まれた後にリセット信号を入力するまで書込不可能となるように形成されていてもよい。

In addition, a predetermined lower limit value is determined for the value of the cycle setting data set in the

なお、周期設定レジスタ537に下限値としての周期設定データを設定することなく、設定された周期設定データに基づいて、例えばクロック信号出力回路524が基準クロック信号CLKをそのままカウンタ521および反転回路532に出力するようにしてもよい。この場合、CPU56は、周期設定レジスタ537に設定される周期設定データの値を下限値と比較して設定しなおす処理を行う必要がなくなる。また、カウンタ521は、クロック信号出力回路524から基準クロック信号CLKを入力する毎にカウント値Cを更新することになる。

Note that, without setting the cycle setting data as the lower limit value in the

カウント値更新信号出力回路525は、カウント値更新データ「01h」を格納するカウント値更新レジスタ(RGN)538を備える。カウント値更新データとは、カウント値の更新を要求するためのデータである。カウント値更新信号出力回路525は、カウント値更新レジスタ538にカウント値更新データ「01h」が書き込まれたことに応じて、カウント値更新信号SI3をセレクタ528に出力する。

The count value update signal output circuit 525 includes a count value update register (RGN) 538 that stores count value update data “01h”. The count value update data is data for requesting update of the count value. The count value update signal output circuit 525 outputs the count value update signal SI3 to the

図15は、カウント値更新レジスタ538の例を示す説明図である。図15に示すように、カウント値更新レジスタ538は、読出不能な8ビットレジスタであり、ビット0のみが書込可能な状態に構成されている。したがって、カウント値更新レジスタ538のビット1〜ビット7に値を書き込む制御を行っても無効とされる。

FIG. 15 is an explanatory diagram illustrating an example of the count value update register 538. As shown in FIG. 15, the count value update register 538 is an unreadable 8-bit register, and is configured in a state where only bit 0 can be written. Therefore, even if control is performed to write a value to

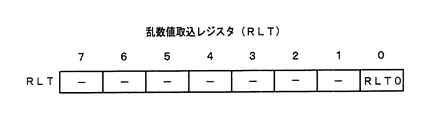

乱数値読取信号出力回路526は、乱数値取込データ「01h」を格納する乱数値取込レジスタ(RLT)539を備える。乱数値取込データとは、乱数値記憶回路531へのカウント値の取込を要求するためのデータである。乱数値読取信号出力回路526は、乱数値取込レジスタ539に乱数値取込データ「01h」が書き込まれたことに応じて、乱数値の読み取りを要求するための乱数値読取信号をラッチ信号生成回路533に出力する。

The random value read signal output circuit 526 includes a random value take-in register (RLT) 539 for storing random value take-in data “01h”. The random value acquisition data is data for requesting acquisition of the count value to the random value storage circuit 531. The random value read signal output circuit 526 generates a latch signal for a random value read signal for requesting reading of the random value in response to the random value fetch data “01h” being written in the random value fetch

図16は、乱数値取込レジスタ539の例を示す説明図である。図16に示すように、乱数値取込レジスタ539は、読出不能な8ビットレジスタである。また、乱数値取込レジスタ539は、ビット0だけが書込可能な状態に構成されている。すなわち、乱数値取込レジスタ539のビット1〜ビット7に値を書き込む制御を行っても無効とされる。

FIG. 16 is an explanatory diagram showing an example of the random value fetch

乱数更新方式選択信号出力回路527は、乱数更新方式選択データを格納する乱数更新方式選択レジスタ(RTS)540を備える。乱数更新方式選択データとは、ランダムRの値を更新する方式である各乱数更新方式のうち、いずれかの乱数更新方式を指定するためのデータである。乱数更新方式選択信号出力回路527は、乱数更新方式選択レジスタ540に乱数更新方式選択データが書き込まれたことに応じて、書き込まれた乱数更新方式選択データにより指定される乱数更新方式に対応する乱数更新方式選択信号を、セレクタ528およびラッチ信号生成回路533に出力する。

The random number update method selection

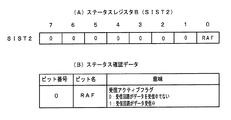

図17(A)は、乱数更新方式選択レジスタ540の例を示す説明図である。図17(A)に示すように、乱数更新方式選択レジスタ540は、8ビットレジスタであり、初期値が「00h」に設定されている。また、乱数更新方式選択レジスタ540は、ビット0〜ビット1が書込および読出ともに可能な状態に構成されている。また、乱数更新方式選択レジスタ540は、ビット2〜ビット7が書込および読出ともに不可能な状態に構成されている。したがって、乱数更新方式選択レジスタ540のビット2〜ビット7に値を書き込む制御を行っても無効とされ、ビット2〜ビット7から読み出す値は全て「0(=000000b)」である。

FIG. 17A is an explanatory diagram illustrating an example of the random number update method selection register 540. As shown in FIG. 17A, the random number update method selection register 540 is an 8-bit register, and the initial value is set to “00h”. The random number update method selection register 540 is configured in a state where

図17(B)は、乱数更新方式選択レジスタ540に書き込まれる乱数更新方式選択データの一例の説明図である。図17(B)に示すように、乱数更新方式選択データは、2ビットのデータから構成される。乱数更新方式選択データ「01b」は、第1の乱数更新方式を指定するために用いられる。また、乱数更新方式選択データ「10b」は、第2の乱数更新方式を指定するために用いられる。なお、この実施の形態では、第1の乱数更新方式とは、カウント値更新信号出力回路525からカウント値更新信号SI3が出力されたことをトリガとして、カウント値を更新する方式である。また、第2の乱数更新方式とは、クロック信号出力回路524から乱数発生用クロック信号SI1が出力されたことをトリガとして、カウント値を更新する方式である。また、乱数更新方式選択データ「01b」または「10b」が乱数更新方式選択レジスタ540に書き込まれた場合、乱数回路503は起動可能な状態となる。一方、乱数更新方式選択データ「00b」または「11b」が乱数更新方式選択レジスタ540に書き込まれた場合、乱数回路503は起動不能な状態となる。

FIG. 17B is an explanatory diagram of an example of random number update method selection data written to the random number update method selection register 540. As shown in FIG. 17B, the random number update method selection data is composed of 2-bit data. The random number update method selection data “01b” is used to specify the first random number update method. The random number update method selection data “10b” is used to specify the second random number update method. In this embodiment, the first random number update method is a method of updating the count value triggered by the output of the count value update signal SI3 from the count value update signal output circuit 525. The second random number update method is a method of updating the count value triggered by the output of the random number generation clock signal SI1 from the clock

セレクタ528は、カウント値更新信号出力回路525から出力されるカウント値更新信号SI3、またはクロック信号出力回路524から出力される乱数発生用クロック信号SI1のいずれかを選択してカウンタ521に出力する。セレクタ528は、乱数更新方式選択信号出力回路527から第1の乱数更新方式に対応する乱数更新方式選択信号(第1の乱数更新方式選択信号ともいう)が入力されると、カウント値更新信号出力回路525から出力されるカウント値更新信号SI3を選択してカウンタ521に出力する。一方、セレクタ528は、乱数更新方式選択信号出力回路527から第2の乱数更新方式に対応する乱数更新方式選択信号(第2の乱数更新方式選択信号ともいう)が入力されると、クロック信号出力回路524から出力される乱数発生用クロック信号SI1を選択してカウンタ521に出力する。なお、セレクタ528は、乱数更新方式選択信号出力回路527から第1の更新方式選択信号が入力されると、カウント値更新信号出力回路525から出力されるカウント値更新信号SI3に応じて、クロック信号出力回路524から出力される乱数発生用クロック信号SI1に同期した数値データの更新を指示する数値更新指示信号を、カウンタ521に出力してもよい。

The

乱数回路起動信号出力回路530は、乱数回路起動データ「80h」を格納する乱数回路起動レジスタ(RST)541を備える。乱数回路起動データとは、乱数回路503の起動を要求するためのデータである。乱数回路起動信号出力回路530は、乱数回路起動レジスタ541に乱数回路起動データ「80h」が書き込まれると、所定の乱数回路起動信号をカウンタ521およびクロック信号出力回路537に出力し、カウンタ521およびクロック信号出力回路524をオンにさせる。そして、カウンタ521によるカウント値の更新動作とクロック信号出力回路524による内部クロック信号の出力動作とを開始させることによって、乱数回路503を起動させる。

The random number circuit activation

図18は、乱数回路起動レジスタ541の例を示す説明図である。図18に示すように、乱数回路起動レジスタ541は、8ビットレジスタであり、初期値が「00h」に設定されている。乱数回路起動レジスタ541は、ビット7だけが書込および読出ともに可能な状態に構成されている。また、乱数回路起動レジスタ541は、ビット0〜ビット6が書込および読出ともに不可能な状態に構成されている。すなわち、乱数回路起動レジスタ541のビット0〜ビット6に値を書き込む制御を行っても無効とされ、ビット0〜ビット6から読み出す値は全て「0(=000000b)」である。

FIG. 18 is an explanatory diagram showing an example of the random number

乱数値記憶回路531は、例えば16ビットレジスタであり、遊技制御処理における大当り判定において用いられる乱数であるランダムRの値を格納する。乱数値記憶回路531は、ラッチ信号生成回路533からラッチ信号SLを入力したことに応じて、カウンタ521から比較器522を介して出力されるカウント値CをランダムRの値として格納する。そして、乱数値記憶回路531は、ラッチ信号生成回路533からラッチ信号SLを入力するごとに、カウンタ521が更新するカウント値Cを読み込んでランダムRの値を記憶する。 The random value storage circuit 531 is a 16-bit register, for example, and stores a random R value that is a random number used in the jackpot determination in the game control process. The random value storage circuit 531 stores the count value C output from the counter 521 via the comparator 522 as a random R value in response to the input of the latch signal SL from the latch signal generation circuit 533. Each time the latch signal SL is input from the latch signal generation circuit 533, the random value storage circuit 531 reads the count value C updated by the counter 521 and stores the random R value.

図19は、乱数値記憶回路531の一構成例を示す回路図である。乱数値記憶回路531は、図19に示すように、2個のAND回路201,203と、2個のNOT回路202,204と、16個のフリップフロップ回路2101〜2116と、16個のOR回路2201〜2216とを含む。

FIG. 19 is a circuit diagram showing a configuration example of the random value storage circuit 531. As shown in FIG. 19, the random value storage circuit 531 includes two AND

図19に示すように、AND回路201の入力端子は、ラッチ信号生成回路533の出力端子とNOT回路204の出力端子とに接続され、出力端子は、NOT回路202の入力端子とフリップフロップ回路2101〜2116のクロック端子Clk1〜Clk16とに接続されている。NOT回路202の入力端子は、AND回路201の出力端子に接続され、出力端子は、AND回路203の一方の入力端子に接続されている。

As shown in FIG. 19, the input terminal of the AND

AND回路203の入力端子は、NOT回路202の出力端子と遊技制御用マイクロコンピュータ560が搭載するCPU56とに接続され、出力端子は、NOT回路204の入力端子に接続されている。NOT回路204の入力端子は、AND回路203の出力端子に接続され、出力端子は、AND回路201の一方の入力端子とOR回路2201〜2216の一方の入力端子とに接続されている。

The input terminal of the AND circuit 203 is connected to the output terminal of the

フリップフロップ回路2101〜2116の入力端子D1〜D16は、比較器522の出力端子に接続されている。フリップフロップ回路2101〜2116のクロック端子Clk1〜Clk16は、AND回路201の出力端子に接続され、出力端子Q1〜Q16は、OR回路2201〜2216の他方の入力端子に接続されている。

The input terminals D1 to D16 of the flip-flop circuits 2101 to 2116 are connected to the output terminal of the comparator 522. The clock terminals Clk1 to Clk16 of the flip-flop circuits 2101 to 2116 are connected to the output terminal of the AND

OR回路2201〜2216の入力端子は、NOT回路204の出力端子とフリップフロップ回路2101〜2116の出力端子とに接続され、出力端子は、遊技制御用マイクロコンピュータ560が搭載するCPU56に接続されている。

The input terminals of the

乱数値記憶回路531の動作について説明する。図20は、乱数値記憶回路531に各信号が入力されるタイミング、および乱数値記憶回路531が各信号を出力するタイミングを示すタイミングチャートである。図20に示すように、遊技制御用マイクロコンピュータ560が搭載するCPU56から出力制御信号SC(本例では、ハイレベル信号)が入力されていない場合(すなわち、AND回路203の一方の入力端子への入力がローレベルの場合)、ラッチ信号生成回路533からラッチ信号SLが入力されると(図20に示す例では、タイミングT1,T2,T7のとき)、AND回路201の2つの入力端子への入力はともにハイレベルとなる。そのため、AND回路201の出力端子から出力される信号SRはハイレベルとなる。そして、AND回路201から出力された信号SRは、フリップフロップ回路2101〜2116のクロック端子Clk1〜Clk16に入力される。

The operation of the random value storage circuit 531 will be described. FIG. 20 is a timing chart showing the timing at which each signal is input to the random value storage circuit 531 and the timing at which the random value storage circuit 531 outputs each signal. As shown in FIG. 20, when the output control signal SC (high level signal in this example) is not input from the

フリップフロップ回路2101〜2116は、クロック端子Clk1〜Clk16から入力される信号SRの立ち上がりエッヂに応答して、比較器522から入力端子D1〜D16を介して入力されるカウント値CのビットデータC1〜C16を乱数値のビットデータR1〜R16としてラッチして記憶する。また、フリップフロップ回路2101〜2116は、記憶するランダムRのビットデータR1〜R16を出力端子Q1〜Q16から出力する。 The flip-flop circuits 2101 to 2116 are responsive to the rising edges of the signal SR input from the clock terminals Clk1 to Clk16, and the bit data C1 to C1 of the count value C input from the comparator 522 via the input terminals D1 to D16. C16 is latched and stored as bit data R1 to R16 of the random value. The flip-flop circuits 2101 to 2116 output random R bit data R1 to R16 to be stored from the output terminals Q1 to Q16.

出力制御信号SCが入力されていない場合(図20に示す例では、タイミングT3までの期間およびタイミングT6以降の期間)、AND回路203の一方の入力端子への入力がローレベルとなるので、AND回路203の出力端子から出力される信号SGはローレベルとなる。AND回路203が出力する信号SGは、NOT回路204において反転され、ハイレベルの信号とされる。そして、OR回路2201〜2216の一方の入力端子に、NOT回路204からハイレベルの信号が入力される。

When the output control signal SC is not input (in the example shown in FIG. 20, the period up to the timing T3 and the period after the timing T6), the input to one input terminal of the AND circuit 203 is at the low level. The signal SG output from the output terminal of the circuit 203 is at a low level. The signal SG output from the AND circuit 203 is inverted in the

以上のように、OR回路2201〜2216の一方の入力端子への入力がハイレベルとなるので、他方の入力端子に入力される信号がハイレベルであるかローレベルであるかに関わらず、OR回路2201〜2216はハイレベルの信号を出力する。すなわち、入力されるランダムRのビットデータR1〜R16の値が「0」であるか「1」であるかに関わらず、OR回路2201〜2216から出力される信号SO1〜SO16は、全てハイレベル(「1」)となる。そのようにすることによって、乱数値記憶回路531から出力される値は、常に「65535(=1111111111111111b)」となり、乱数値記憶回路531からランダムRを読み出すことができない状態となる。すなわち、乱数値記憶回路531から乱数を読み出そうとしても、乱数値記憶回路531から常に同じ値「65535」しか読み出せない状態となり、出力制御信号SCが入力されていない場合、乱数値記憶回路531は、読出不能(ディセイブル)状態となる。なお、16ビット乱数回路503bを用いる場合、乱数値としての値「65535」が用いられる可能性がある。この場合、遊技制御用マイクロコンピュータ560は、値「65535」を読み込んだとしても、その値が乱数であるのか読出不能状態であるのかを判断することができない。そのため、図39に示す各大当り判定用の判定テーブルにおいて、あらかじめランダムRが「65535」である場合には「ハズレ」と判定するように設定しておけばよい。

As described above, since the input to one of the input terminals of the

ラッチ信号生成回路533からラッチ信号SLが入力されていないときに、CPU56から出力制御信号SCが入力されると(図20に示す例では、タイミングT4からタイミングT6までの期間)、AND回路203の2つの入力端子への入力がともにハイレベルとなるので、AND回路203の出力端子から出力される信号SGはハイレベルとなる。AND回路203が出力する信号SGは、NOT回路204において反転され、ローレベルの信号とされる。そして、OR回路2201〜2216の一方の入力端子に、NOT回路204からローレベルの信号が入力される。

When the latch signal SL is not input from the latch signal generation circuit 533 and the output control signal SC is input from the CPU 56 (in the example shown in FIG. 20, the period from the timing T4 to the timing T6), the AND circuit 203 Since the inputs to the two input terminals are both at the high level, the signal SG output from the output terminal of the AND circuit 203 is at the high level. The signal SG output from the AND circuit 203 is inverted in the

以上のように、OR回路2201〜2216の一方の入力端子への入力がローレベルとなるので、他方の入力端子に入力される信号がハイレベルの場合、OR回路2201〜2216の出力端子からハイレベルの信号が出力される。また、OR回路2201〜2216の他方の入力端子に入力される信号がローレベルの場合、OR回路2201〜2216からローレベルの信号が出力される。すなわち、OR回路2201〜2216の他方の入力端子に入力されるランダムRのビットデータR1〜R16の値は、OR回路2201〜2216の出力端子からそのまま(すなわち、ビットデータR1〜R16の値が「1」のときは「1」が、「0」のときは「0」)出力される。そのようにすることによって、乱数値記憶回路531からのランダムRの読出が可能となる。すなわち、出力制御信号SCが入力されている場合、乱数値記憶回路531は、読出可能(イネイブル)状態となる。

As described above, since the input to one input terminal of the

ただし、CPU56から出力制御信号SCが入力される前に、ラッチ信号生成回路533からラッチ信号SLが入力されている場合、AND回路203の一方の入力端子への入力がローレベルとなるので、ラッチ信号SLが入力されている状態のままで、出力制御信号SCが入力されても(図20に示す例では、タイミングT3からタイミングT4の期間)、AND回路203の出力端子から出力される信号SGはローレベルのままとなる。AND回路203が出力する信号SGは、NOT回路204において反転され、ハイレベルの信号とされる。そして、OR回路2201〜2216の一方の入力端子に、NOT回路204からハイレベルの信号が入力される。

However, if the latch signal SL is input from the latch signal generation circuit 533 before the output control signal SC is input from the

以上のように、OR回路2201〜2216の一方の入力端子への入力がハイレベルとなるので、他方の入力端子に入力される信号がハイレベルであるかローレベルであるかに関わらず、OR回路2201〜2216から出力される信号SO1〜SO16は全てハイレベルとなる。そして、出力制御信号SCが入力されているにも関わらず、乱数値記憶回路531からランダムRを読み出すことができない状態のままとなる。すなわち、ラッチ信号SLが入力されている場合、乱数値記憶回路531は、出力制御信号SCを受信不可能な状態となる。なお、16ビット乱数回路503bを用いる場合、乱数値としての値「65535」が用いられる可能性がある。この場合、遊技制御用マイクロコンピュータ560は、値「65535」を読み込んだとしても、その値が乱数であるのか読出不能状態であるのかを判断することができない。そのため、図39に示す各大当り判定用の判定テーブルにおいて、あらかじめランダムRが「65535」である場合には「ハズレ」と判定するように設定しておけばよい。

As described above, since the input to one of the input terminals of the

また、ラッチ信号生成回路533からラッチ信号SLが入力される前に、CPU56から出力制御信号SCが入力されている場合、AND回路201の一方の入力端子への入力がローレベルとなるので、出力制御信号SCが入力されているままの状態で、ラッチ信号SLが入力されても(図20に示す例では、タイミングT5)、AND回路201の出力端子から出力される信号SRはローレベルのままとなる。そのため、フリップフロップ回路2101〜2116のクロック端子Clk1〜Clk16に入力される信号SRは、ローレベルからハイレベルに立ち上がらず、フリップフロップ回路2101〜2116に格納されているランダムRのビットデータR1〜R16は、ラッチ信号SLが入力されているにも関わらず、記憶される乱数は更新されない。すなわち、出力制御信号SCが入力されている場合、乱数値記憶回路531は、ラッチ信号SLを受信不可能な状態となる。

In addition, when the output control signal SC is input from the

反転回路532は、クロック信号出力回路524から入力する乱数発生用クロック信号SI1における信号レベルを反転させることによって、クロック信号の極性を反転させた反転クロック信号SI2を生成する。また、反転回路532は、生成した反転クロック信号SI2をラッチ信号生成回路533に出力する。

The inverting circuit 532 generates the inverted clock signal SI2 in which the polarity of the clock signal is inverted by inverting the signal level in the random number generating clock signal SI1 input from the clock

なお、乱数回路503は、反転回路532に代えて遅延回路を含んでもよい。この場合、遅延回路は、クロック信号出力回路524から入力する乱数発生用クロック信号SI1を遅延させることによって、クロック信号を遅延させた遅延クロック信号を生成する。また、遅延回路は、生成した遅延クロック信号をラッチ信号生成回路533に出力する。従って、ラッチ信号生成回路533は、乱数発生用クロック信号SI1を遅延させた遅延クロック信号に同期して、乱数値記憶回路531にラッチ信号を出力することになる。

Note that the

ラッチ信号生成回路533は、セレクタおよびフリップフロップ回路等を用いて構成される。ラッチ信号生成回路533は、乱数値読取信号出力回路526からの乱数値読取信号と反転回路532からの反転クロック信号SI2とを入力し、乱数値記憶回路531に乱数値を記憶させるためのラッチ信号SLを出力する。また、ラッチ信号生成回路533は、乱数更新方式選択信号出力回路527からの乱数更新方式選択信号によって指定された乱数値更新方式に応じて、ラッチ信号SLを出力する。この場合、ラッチ信号生成回路533は、乱数更新方式選択信号出力回路527から第1の乱数更新方式選択信号が入力された場合、反転回路532から出力される反転クロック信号SI2を選択し、ラッチ信号SLとして乱数値記憶回路531に出力する。一方、ラッチ信号生成回路533は、乱数更新方式選択信号出力回路527から第2の乱数更新方式選択信号が入力された場合、乱数値読取信号出力回路526から出力される乱数値読取信号を、反転回路532から出力される反転クロック信号SI2の立ち上がりエッヂに同期させて、ラッチ信号SLとして乱数値記憶回路531に出力する。

The latch signal generation circuit 533 is configured using a selector, a flip-flop circuit, and the like. The latch signal generation circuit 533 receives the random number read signal from the random number read signal output circuit 526 and the inverted clock signal SI2 from the inversion circuit 532, and latch signal for storing the random value in the random value storage circuit 531. SL is output. The latch signal generation circuit 533 outputs the latch signal SL in accordance with the random value update method designated by the random number update method selection signal from the random number update method selection

タイマ回路534は、始動口14への遊技球の入賞を検出した旨の入賞検出信号SSを始動口スイッチ14aから入力する。また、タイマ回路534は、始動口スイッチ14aから入賞検出信号SSが継続して入力されている時間を計測する。そして、タイマ回路534は、計測時間が所定期間(例えば、3ms)になると、乱数値読取信号出力回路526の乱数値取込レジスタ539に乱数値取込データ「01h」を書き込む。例えば、タイマ回路534は、ハイレベルの信号が入力されたことに応じて起動するアップカウンタまたはダウンカウンタによって構成される。タイマ回路534は、始動口スイッチ14aからの入力がハイレベルとなっている間(すなわち、入賞検出信号SSが継続して入力されている間)、クロック回路501から順次入力する基準クロック信号CLKをアップカウントまたはダウンカウントする。そして、タイマ回路534は、アップカウントまたはダウンカウントするカウント値が3msに対応する値になると、始動口スイッチ14aから入賞検出信号SSが入力されたと判断して、乱数値取込データ「01h」を乱数値取込レジスタ539に書き込む。

The

次に、シリアル通信回路505の構成について説明する。シリアル通信回路505は、全二重方式、非同期方式および標準NRZ(ノンリターンゼロ)符号化を用いたデータフォーマットで、各制御基板(例えば、払出制御基板37や音/ランプ制御基板80b)のマイクロコンピュータとシリアル通信を行う。シリアル通信回路505は、各制御基板のマイクロコンピュータに各種データ(例えば、賞球個数コマンドや演出制御コマンド)を送信する送信部と、各制御基板のマイクロコンピュータからの各種データ(例えば、賞球ACKコマンド)を受信する受信部とを含む。

Next, the configuration of the

図21は、シリアル通信回路505の送信部の構成例を示すブロック図である。また、図22は、シリアル通信回路505の受信部の構成例を示すブロック図である。シリアル通信回路505は、ボーレートレジスタ702、ボーレート生成回路703、2つのステータスレジスタ705,706、3つの制御レジスタ707,708,709、送信データレジスタ710、受信データレジスタ711、送信用シフトレジスタ712、受信用シフトレジスタ713、割り込み制御回路714、送信フォーマット/パリティ生成回路715および受信フォーマット/パリティチェック回路716を含む。また、図21に示すように、シリアル通信回路505の送信部は、これらの構成要素のうち、ボーレートレジスタ702、ボーレート生成回路703、ステータスレジスタA705、制御レジスタ707,708,709、送信データレジスタ710、送信用シフトレジスタ712、割り込み制御回路714および送信フォーマット/パリティ生成回路715によって構成される。また、図22に示すように、シリアル通信回路505の受信部は、これらの構成要素のうち、ボーレートレジスタ702、ボーレート生成回路703、ステータスレジスタ705,706、制御レジスタ707,708,709、受信データレジスタ711、受信用シフトレジスタ713、割り込み制御回路714および受信フォーマット/パリティチェック回路716によって構成される。

FIG. 21 is a block diagram illustrating a configuration example of the transmission unit of the

なお、シリアル通信回路505において、送信部と受信部とは、実際には、共通の回路を用いて構成される。そして、シリアル通信回路505は、上記に示したように、シリアル通信回路505の各構成要素を使い分けて用いることによって、送信回路又は受信回路として機能する。

In the

まず、シリアル通信回路505が各制御基板が搭載するマイクロコンピュータと送受信するデータのデータフォーマットを説明する。図23は、シリアル通信505が各制御基板が搭載するマイクロコンピュータと送受信するデータのデータフォーマットの例を示す説明図である。図23に示すように、シリアル通信回路505が送受信するデータのデータフォーマットは、スタートビット、データおよびストップビットを1フレームとして構成される。また、シリアル通信回路505が送受信するデータのデータ長は、後述するシリアル通信回路設定処理において初期設定を行えば、8ビットまたは9ビットのいずれかに設定できる。図23(a)は、データ長を8ビットに設定した場合のデータフォーマットの例である。また、図23(b)は、データ長を9ビットに設定した場合のデータフォーマットの例である。

First, the data format of data transmitted and received by the

図23に示すように、シリアル通信回路505が送受信するデータのデータフォーマットは、ハイレベル(論理「1」)のアイドルラインのあとに、1フレームの始まりであることを示すスタートビット(論理「0」)を含む。また、データフォーマットは、スタートビットのあとに、8ビットまたは9ビットの送受信データを含む。そして、データフォーマットは、送受信データのあとに、1フレームの終わりであることを示すストップビット(論理「1」)を含む。

As shown in FIG. 23, the data format of data transmitted and received by the

シリアル通信回路505は、図23に示すデータフォーマットに従って、送受信データの最下位ビット(ビット0)から先にデータを送受信する。また、後述するシリアル通信回路設定処理において初期設定を行えば、送受信データにパリティビットを付加するように設定することもできる。パリティビットを付加するように設定した場合、送受信データの最上位ビットがパリティビット(奇数パリティまたは偶数パリティ)として用いられる。例えば、データ長を8ビットに設定した場合、送受信データのビット7がパリティビットとして用いられる。また、例えば、データ長を9ビットに設定した場合、送受信データのビット8がパリティビットとして用いられる。

The

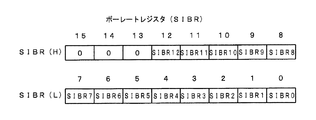

ボーレート生成回路703は、クロック回路501が出力するクロック信号およびボーレートレジスタ702に設定されている設定値(ボーレート設定値ともいう)にもとづいて、シリアル通信回路505が用いるボーレートを生成する。この場合、ボーレート生成回路703は、クロック信号およびボーレート設定値にもとづいて、所定の計算式を用いてボーレートを求める。例えば、ボーレート生成回路703は、式(1)を用いて、シリアル通信回路505が用いるボーレートを求める。

The baud

ボーレート=クロック周波数/(ボーレート設定値×16) 式(1) Baud rate = clock frequency / (baud rate set value x 16) Equation (1)

図24は、ボーレートレジスタ702の例を示す説明図である。ボーレートレジスタ702は、ボーレート生成回路703が生成するボーレートの値を指定するための所定の設定値を設定するレジスタである。例えば、ボーレートレジスタ702が式(1)を用いてボーレートを求めるものとし、クロック周波数が3MHzであるとする。この場合、所望の目標ボーレートが1200bpsであるとすると、ボーレートレジスタ702に設定値「156」を設定する。すると、ボーレート生成回路703は、クロック周波数「3MHz」およびボーレート設定値「156」にもとづいて、式(1)を用いて、ボーレート「1201.92bps」を生成する。ボーレートレジスタ702は、16ビットレジスタであり、初期値が「0(=00h)」に設定されている。また、ボーレートレジスタ702は、ビット0〜ビット12が書込および読出ともに可能な状態に構成されている。また、ボーレートレジスタ702は、ビット13〜ビット15が書込および読出ともに不可能な状態に構成されている。したがって、ボーレートレジスタ702のビット13〜ビット15に値を書き込む制御を行っても無効とされ、ビット13〜ビット15から読み出す値は全て「0(=000b)」である。

FIG. 24 is an explanatory diagram showing an example of the

図25(A)は、制御レジスタA707の例を示す説明図である。制御レジスタA707は、シリアル通信回路505の通信フォーマットを設定するレジスタである。この実施の形態では、制御レジスタA707の各ビットの値が設定されることによって、シリアル通信回路505の通信フォーマットが設定される。制御レジスタA707には、送受信データのデータ形式や各種通信方式等の通信フォーマットを設定するための通信フォーマット設定データが設定される。図25(A)に示すように、制御レジスタA707は、8ビットレジスタであり、初期値が「0(=00h)」に設定されている。また、制御レジスタA707は、ビット0〜ビット4が書込および読出ともに可能な状態に構成されている。また、制御レジスタA707は、ビット5〜ビット7が書込および読出ともに不可能な状態に構成されている。したがって、制御レジスタA707のビット5〜ビット7に値を書き込む制御を行っても無効とされ、ビット5〜ビット7から読み出す値は全て「0(=000b)」である。

FIG. 25A is an explanatory diagram illustrating an example of the control register A707. The control register A 707 is a register for setting the communication format of the

図25(B)は、制御レジスタA707に設定される通信フォーマット設定データの一例の説明図である。図25(B)に示すように、制御レジスタA707のビット4(ビット名「M」)には、送受信するデータのデータ長を設定するための設定データが設定される。図25(B)に示すように、ビット4を「0」に設定することによって、送受信データのデータ長が8ビットに設定される。また、ビット4を「1」に設定することによって、送受信データのデータ長が9ビットに設定される。

FIG. 25B is an explanatory diagram of an example of communication format setting data set in the control register A707. As shown in FIG. 25B, setting data for setting the data length of data to be transmitted and received is set in bit 4 (bit name “M”) of the control register A707. As shown in FIG. 25B, by setting

制御レジスタA707のビット3(ビット名「WAKE」)には、スタンバイ状態の受信回路(シリアル通信回路505の受信部)をウエイクアップする(オンライン状態にさせる)ウエイクアップ方式を設定するための設定データが設定される。図25(B)に示すように、ビット3を「0」に設定することによって、アイドルラインを認識したときにウエイクアップするアイドルラインウエイクアップ方式が設定される。また、ビット3を「1」に設定することによって、所定のアドレスマークを認識することによってウエイクアップするアドレスマークウエイクアップ方式が設定される。

In bit 3 (bit name “WAKE”) of the control register A707, setting data for setting a wake-up method for waking up the receiver circuit (the receiving unit of the serial communication circuit 505) in the standby state. Is set. As shown in FIG. 25 (B), by setting

制御レジスタA707のビット2(ビット名「ILT」)には、受信データのアイドルラインの検出方式を選択するための設定データが設定される。図25(B)に示すように、ビット2を「0」に設定することによって、受信データに含まれるスタートビットの後からアイドルラインを検出する検出方式が設定される。また、ビット2を「1」に設定することによって、受信データに含まれるストップビットの後からアイドルラインを検出する検出方式が設定される。

In bit 2 (bit name “ILT”) of the control register A707, setting data for selecting an idle line detection method of received data is set. As shown in FIG. 25B, by setting

制御レジスタA707のビット1(ビット名「PE」)には、パリティ機能を使用するか否かを設定するための設定データが設定される。図25(B)に示すように、ビット1を「0」に設定することによって、パリティ機能を使用しないように設定される。また、ビット1を「1」に設定することによって、パリティ機能を使用するように設定される。

Setting data for setting whether or not to use the parity function is set in bit 1 (bit name “PE”) of the control register A707. As shown in FIG. 25B, the parity function is not used by setting

制御レジスタA707のビット0(ビット名「PT」)には、パリティ機能を使用すると設定した場合のパリティの種類を設定するための設定データが設定される。図25(B)に示すように、ビット0を「0」に設定することによって、パリティの種類として偶数パリティが設定される。また、ビット0を「1」に設定することによって、パリティの種類として奇数パリティが設定される。

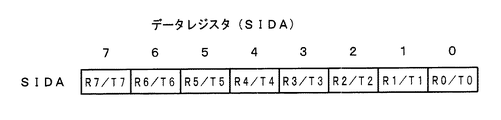

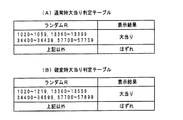

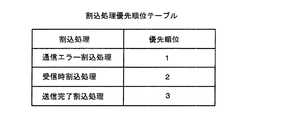

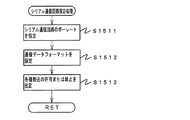

Setting data for setting the type of parity when the parity function is used is set in bit 0 (bit name “PT”) of the control register A707. As shown in FIG. 25B, by setting