本発明は、有機薄膜で覆われてなる複数の薄膜トランジスタ(以下、TFTという)で構成された半導体装置、表示装置、発光装置およびこれらの作製方法に関する。本発明における半導体装置には、CPU(Central Processing unit)、MPU(Micro Processor unit)、メモリー、マイコン、画像処理プロセッサを含み、表示装置には液晶表示装置、PDP(Plasma Display Panel)、FED(Field Emission Display)等を含む。

近年、絶縁表面を有する基板上に形成された半導体薄膜(厚さ数〜数百nm程度)を用いてTFTを形成する技術が注目されている。TFTはICや電気光学装置のような電子デバイスに広く応用されている。

なお、これらのTFTを形成する基板としては、現在、ガラス基板や石英基板が多く使用されているが、割れやすく、重いという欠点がある。また、大量生産を行う上で、これらの基板は大型化が困難であり、不向きである。そのため、可撓性を有する基板、代表的にはフレキシブルなプラスチックフィルムの上にTFTで構成された素子を形成することが試みられている。

しかしながら、プラスチックフィルムの耐熱性が低いためプロセスの最高温度を低くせざるを得ず、結果的にガラス基板上に形成する時ほど良好な電気特性のTFTを形成できないのが現状である。そのため、プラスチックフィルム上に直接TFTを形成して得られた半導体装置、表示装置、または発光装置等は、まだ実現されていない。

これに対して、ガラスや石英などの基板上に薄膜素子を形成した後、基板から薄膜素子(被転写体)を剥離し、プラスチックフィルム等の転写体に転写させる技術が開示されている(例えば、特許文献1参照。)。

なお、このようにプラスチックフィルム等の可撓性を有する基体上に半導体装置、表示装置、または発光装置等を作製することができれば、厚みが薄く軽量であるということに加えて、曲面を有するフレキシブルなディスプレイ等に用いることができ、応用範囲を広げることができる。

上述したような転写技術を用いることにより、プラスチック等の転写体上に良好な電気特性を有するTFTを含む半導体装置(CPU、MPU、メモリー、マイコン、画像処理プロセッサ等)、表示装置(液晶表示装置、PDP、FED等)、または発光装置を含む層(以下、素子形成層という)を形成することができる。しかし、転写体に用いるプラスチック等は有機材料であり、一般に水分や酸素等を透過しやすいことから、このような転写体により被転写体を封止することは、適当ではない。

そこで、本発明では薄膜軽量化、および曲面を有するフレキシブルな構造とするのに加え、素子形成層に対して外部から水分や酸素等が侵入するのを防ぐ構造を有する半導体装置、表示装置、または発光装置、およびそれらの作製方法を提供することを目的とする。

本発明では、上記課題を解決するためにフッ素系樹脂を含む膜で素子形成層が覆われた構造を有し、素子形成層に含まれるTFTを島状の半導体膜により形成することにより、薄膜軽量化とともに曲面を有するフレキシブルな構造を実現し、さらに外部から水分や酸素等の侵入を防ぐことができる半導体装置、表示装置、または発光装置を形成する。

本発明における具体的な構成は、複数のTFTを含む素子形成層を有する半導体装置、表示装置、または発光装置であって、前記素子形成層と接して形成されるフッ素系樹脂を含む膜に覆われていることを特徴とするものである。

なお、上記構成においてフッ素系樹脂を含む膜は、前記素子形成層を覆って形成されており、前記素子形成層に形成されるTFTの他、TFTと接続して形成される発光素子が水分や酸素などの気体によって劣化するのを防ぐ機能を有するものである。さらに、前記素子形成層の一方、または両方の面に接して熱伝導層を有し、かつ前記素子形成層がフッ素系樹脂を含む膜に覆われた構造とすることもできる。

また、別の構成は、第1の絶縁膜上に形成されたソース領域、ドレイン領域、およびチャネル形成領域を有する島状の半導体膜と、前記半導体膜上にゲート絶縁膜を介して形成されたゲート電極とを含むTFTと、前記TFTの前記ソース領域または前記ドレイン領域と電気的に接続された配線を含む素子形成層を有する半導体装置、表示装置、または発光装置であって、前記素子形成層を覆って形成された第2の絶縁膜を有し、前記第1および前記第2の絶縁膜と接して形成されたフッ素系樹脂を含む膜を有することを特徴とする半導体装置、表示装置、または発光装置である。

また、上記表示装置に関する別の構成としては、第1の絶縁膜上に形成されたソース領域、ドレイン領域、およびチャネル形成領域を有する島状の半導体膜と、前記半導体膜上にゲート絶縁膜を介して形成されたゲート電極とを含む薄膜トランジスタと、前記薄膜トランジスタの前記ソース領域または前記ドレイン領域と電気的に接続された配線と、画素部において前記配線と電気的に接続された素子を含む素子形成層を有する表示装置であって、前記素子形成層を覆って形成された第2の絶縁膜を有し、前記第1および前記第2の絶縁膜と接して形成されたフッ素系樹脂を含む膜を有することを特徴とする表示装置である。

また、上記発光装置に関する別の構成としては、第1の絶縁膜上に形成された薄膜トランジスタと層間絶縁膜を介して電気的に接続された第1の電極、前記第1の電極上に形成された電界発光膜、および前記電界発光膜上に形成された第2の電極からなる発光素子を含む素子形成層を有する発光装置であって、前記第1の絶縁膜および前記第2の電極と接して形成されたフッ素系樹脂を含む膜を有することを特徴とする発光装置である。

なお、上記各構成において、ソース領域、ドレイン領域、およびチャネル形成領域を有する半導体膜が島状に形成されていることから、前記半導体膜を覆う前記フッ素系樹脂を含む膜のフレキシブルな性質に反することなく形状の変化に対応することができ、様々な形状の用途に対しても劣化を生じることなく用いることができる。

なお、上記素子形成層には、TFTおよびこれらを組み合わせて形成される半導体装置(CPU、MPU、メモリー、マイコン、画像処理プロセッサ)、表示装置(液晶表示装置、PDP、FED)、または発光装置を含む層(以下、素子形成層という)を形成することができる。

また、上記各構成において前記素子形成層は、その膜厚が50μm以下であることを特徴とする半導体装置、表示装置、または発光装置である。

また、本発明におけるフッ素系樹脂を含む膜とは、フッ素を含むポリエチレン、フッ素を含むポリプロピレン、フッ素を含むポリビニレン等の化合物、または、これらの共重合体からなるターゲットを用いることにより、これらのフッ素系樹脂を含む膜を形成することができる。

上記各構成において、形成された半導体装置、表示装置、または発光装置をプリペイドカード、クレジットカード、免許証、またはウエアラブルコンピュータ等の応用製品に用いることが可能である。

さらに、上記構造を得るための本発明の構成は、第1の基板上に複数のTFTを含む素子形成層を形成し、前記素子形成層と接して第1の接着層を形成し、前記第1の接着層に第2の基板を接着させ、前記素子形成層を前記第1の基板および前記第2の基板で挟み、前記第1の基板を前記素子形成層から物理的手段で分離除去し、露出面に第1のフッ素系樹脂を含む膜を形成し、前記第1のフッ素系樹脂を含む膜と接して第2の接着層を形成し、前記第2の接着層に第3の基板を接着させ、前記第1の接着層および前記第2の基板を前記素子形成層から分離除去し、露出面に第2のフッ素系樹脂を含む膜を形成し、前記第2の接着層および前記第3の基板を前記素子形成層から分離除去することを特徴とする半導体装置の作製方法である。

なお、上記構成において、第1の基板を物理的手法により分離除去するために、第1の基板上に金属層を形成し、前記金属層上に酸化物層を形成し、前記酸化物層上に第1の絶縁膜を形成し、前記第1の絶縁膜上に水素を含み非晶質構造を有する半導体膜を形成し、水素を拡散する加熱処理を行い、前記半導体膜を一部に有する複数のTFTを含む素子形成層が形成されることを特徴とする。

また、本発明において素子形成層の画素部において、TFTと電気的に接続された素子が形成される表示装置の作製方法としては、第1の基板上に金属層を形成し、前記金属層上に酸化物層を形成し、前記酸化物層上に第1の絶縁膜を形成し、前記第1の絶縁膜上に水素を含み非晶質構造を有する半導体膜を形成し、水素を拡散する加熱処理を行い、前記半導体膜を一部に有する複数のTFTを形成し、前記TFTと層間絶縁膜を介して電気的に接続された第1の電極を形成し、前記第1の電極と接して第1の接着層を形成し、前記第1の接着層に第2の基板を接着させ、前記第1の基板および前記金属層を、前記金属層および前記第1の絶縁膜との界面から物理的手段で分離除去し、露出面に第1のフッ素系樹脂を含む膜を形成し、前記第1のフッ素系樹脂を含む膜と接して第2の接着層を形成し、前記第2の接着層に第3の基板を接着させ、前記第1の接着層および前記第2の基板を前記第1の電極表面から分離除去し、露出した前記第1の電極上に前記第1の電極を含む素子を形成し、前記素子上に第2のフッ素系樹脂を含む膜を形成し、前記第2の接着層および前記第3の基板を前記第1のフッ素系樹脂を含む膜から分離除去することを特徴とする表示装置の作製方法である。

また、本発明において素子形成層の画素部において、TFTと電気的に接続された発光素子が形成される発光装置の作製方法としては、第1の基板上に金属層を形成し、前記金属層上に酸化物層を形成し、前記酸化物層上に第1の絶縁膜を形成し、前記第1の絶縁膜上に水素を含み非晶質構造を有する半導体膜を形成し、水素を拡散する加熱処理を行い、前記半導体膜を一部に有する複数のTFTを形成し、前記TFTと層間絶縁膜を介して電気的に接続された第1の電極を形成し、前記第1の電極と接して第1の接着層を形成し、前記第1の接着層に第2の基板を接着させ、前記第1の基板および前記金属層を、前記金属層および前記第1の絶縁膜との界面から物理的手段で分離除去し、露出面に第1のフッ素系樹脂を含む膜を形成し、前記第1のフッ素系樹脂を含む膜と接して第2の接着層を形成し、前記第2の接着層に第3の基板を接着させ、前記第1の接着層および前記第2の基板を前記第1の電極表面から分離除去し、露出した前記第1の電極上に電界発光膜、および前記電界発光膜上に第2の電極を形成し、前記第2の電極上に第2のフッ素系樹脂を含む膜を形成し、前記第2の接着層および前記第3の基板を前記第1のフッ素系樹脂を含む膜から分離除去することを特徴とする発光装置の作製方法である。

上記各構成において、前記第1のフッ素系樹脂を含む膜または、前記第2のフッ素系樹脂を含む膜は、スパッタリング法、スピンコート法などの塗布法により形成されることを特徴とする。

なお、上記各構成において、前記第1のフッ素系樹脂を含む膜と接して第2の接着層を形成する前に、前記第1のフッ素系樹脂を含む膜表面の成膜性を向上させるために逆スパッタ処理をしてもよい。

逆スパッタ処理を行う場合にはArガスを流量20〜500(sccm)で導入しながらスパッタ圧力を0.6〜150(Pa)として行う。なお、この場合において放電を励起するために20kHz〜120MHzの高周波電力を印加して、RF電力0.06〜3.18(W/cm2)で、基板の温度を室温〜200℃以下として1〜20分程度行うのが好ましい。

以上のように、素子形成層がフッ素系樹脂を含む膜で覆われた構造とすることにより、薄膜軽量化、および曲面を有するフレキシブルな構造だけでなく、素子形成層に対して外部から水分や酸素等が侵入するのを防ぐ構造を有する半導体装置、表示装置、または発光装置を提供することができる。

本発明を実施することにより、半導体装置、表示装置、または発光装置の薄膜軽量化、および曲面を有するフレキシブルな構造を得ることができるだけでなく、素子形成層に対して外部から水分や酸素等が侵入するのを防ぐことができるので、素子の特性変動や劣化を防ぐことができる。

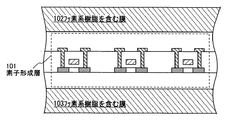

本発明により形成される半導体装置は、図1に示す構造を有する。すなわち、TFTを複数組み合わせることにより構成される素子形成層101がフッ素系樹脂を含む膜102、103により覆われた構造を有する。なお、このような半導体装置の作製方法について、図2〜4を用いて詳細に説明する。

図2(A)には、第1の基板201上に金属層202、酸化物層203が順次積層され、その上に素子形成層204が形成された状態を示す。

第1の基板201としては、ガラス基板、石英基板、セラミック基板などを用いることができる。また、シリコン基板、金属基板またはステンレス基板を用いても良い。

そして、第1の基板201上に形成される金属層202に用いる材料としては、W、Ti、Ta、Mo、Nd、Ni、Co、Zr、Zn、Ru、Rh、Pd、Os、Ir、Ptから選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料からなる単層、またはこれらの積層、或いは、これらの窒化物、例えば、窒化チタン、窒化タングステン、窒化タンタル、窒化モリブデンからなる単層、またはこれらの積層を用いればよい。なお、金属層202の膜厚は10nm〜200nm、好ましくは50nm〜75nmとすればよい。

ここで、スパッタリング法により金属層202を形成する場合には、第1の基板201を固定するため、第1の基板201の周縁部付近における膜厚が不均一になりやすい。そのため、ドライエッチングによって周縁部のみを除去することが好ましいが、その際、第1の基板201もエッチングされないように、基板201と金属層202との間に酸化窒化シリコン膜からなる絶縁膜を100nm程度形成することもできる。

金属層202上に形成される酸化物層203には、酸化シリコン、酸化窒化シリコン、酸化金属材料を用い、スパッタリング法により形成する。酸化物層203の膜厚は、金属層202の約2倍以上であることが望ましい。例えば、酸化シリコンターゲットを用いたスパッタリング法により、酸化シリコン膜を150nm〜200nmの膜厚とするのが好ましい。

また、酸化物層203上に形成される素子形成層204は、TFT(pチャネル型TFT301およびnチャネル型TFT302)を適宜組み合わせることにより半導体装置、表示装置、または発光装置が形成される層のことをいう。ここで示すpチャネル型TFT301およびnチャネル型TFT302は、それぞれ下地膜303、半導体膜の一部に形成された不純物領域304およびチャネル形成領域305の他、ゲート絶縁膜306、ゲート電極307、配線308により構成されている。

また、この素子形成層204を形成する際に、少なくとも水素を含む材料膜(半導体膜または金属膜)を形成した後に水素を含む材料膜中に含まれる水素を拡散するための熱処理を行う。この熱処理は410℃以上であればよく、素子形成層204の形成プロセスとは別途行ってもよいし、兼用させて工程を省略してもよい。例えば、水素を含む材料膜として水素を含むアモルファスシリコン膜を用い、加熱してポリシリコン膜を形成する場合、結晶化させるため500℃以上の熱処理を行えば、ポリシリコン膜を形成すると同時に水素の拡散を行うことができる。

次に、素子形成層204上に窒化物層205を形成する。なお、ここでは、スパッタリング法により50nm程度の膜厚で形成する。

次に、素子形成層204および窒化物層205を固定する支持体となる第2の基板206を第1の接着層207で貼りつける(図2(B))。なお、第2の基板206として、ガラス基板、石英基板、セラミック基板、プラスチック基板の他、シリコン基板を代表とする半導体基板、またはステンレス基板を代表とする金属基板を用いることもできる。また、第2の基板206は、第1の基板201よりも剛性の高いことが好ましい。

また、第1の接着層207に用いる材料としては、反応硬化型接着剤、熱硬化型接着剤、紫外線硬化型接着剤等の光硬化型接着剤、嫌気型接着剤などの各種硬化型接着剤が挙げられる。なお、これらの接着剤が水または有機溶媒に溶ける可溶性、光照射により接着力が低下する感光性を有することが好ましい。これらの接着剤の組成としては、例えば、エポキシ系、アクリレート系、シリコン系等を用いることができる。なお、第1の接着層207は、塗布法等により形成される。また、ここで形成された第1の接着層207は、後の工程で除去される。

本発明の実施の形態では、第1の接着層207に用いる材料として、水または有機溶媒に対して可溶性を有する接着材料を用いる。

なお、第1の接着層207に用いる材料としては、上述した接着剤に限られることはなく両面テープ(光照射により接着力が低下する感光性を有する)等を用いたり、上述した接着剤と両面テープを組み合わせて用いたりすることもできる。

次に、金属層202が設けられている第1の基板201を物理的手段により引き剥がす(図2(C))。酸化物層203の膜応力と、金属層202の膜応力が異なっているため、比較的小さな力で引き剥がすことができる。

こうして、酸化物層203上に形成された素子形成層204を第1の基板201、および金属層202から分離させることができる。

次に、分離により露出した酸化物層203の表面にフッ素系樹脂を含む膜209をスパッタリング法により形成する。(図3(A))。なお、フッ素系樹脂を含む膜209を形成する前に窒化物層208を形成しても良い。

フッ素系樹脂を含む膜209をスパッタリング法により成膜する際の条件としては、材料ガスとしてArガスを流量30(sccm)(さらに流量5(sccm)のO2ガスを併せて用いても良い)で導入しながら、スパッタ圧力を0.4Pa、パワーを400W、基板温度を300℃として、フッ素系樹脂を含む膜209を1〜100μmの膜厚で成膜する。

また、本実施の形態においてフッ素系樹脂を含む膜209は、ポリテトラフルオロエチレン、テトラフルオロエチレン−ヘキサフルオロプロピレン共重合体、ポリクロロトリフルオロエチレン、テトラフルオロエチレン−エチレン共重合体、ポリビニルフルオライド、ポリビニリデンフルオライド等からなるターゲットを用いることにより形成することができる。

また、フッ素系樹脂を含む膜209をスピンコート法などの塗布法により形成する場合には、水を溶媒とするフッ素系樹脂の水溶液(液体フッ素樹脂コーティング剤)を用いて形成することができる。

なお、フッ素系樹脂を含む膜209を形成することにより、素子形成層204に含まれるTFT(ここでは示されていないが、発光素子を有する場合には発光素子)の素子特性に影響を与えたり、劣化を促進させたりする水分や、酸素等の気体の侵入を防ぐことができる。

次に、フッ素系樹脂を含む膜209に第3の基板210を第2の接着層211で貼りつける(図3(B))。なお、第3の基板210としては、第2の基板206に用いたものと同様の材料を用いることができる。また、第2の接着層211に関しても第1の接着層207に用いた材料と同様の材料を用いることができる。なお、ここでは、第2の接着層211として、光照射により接着力が低下する感光性を有する両面テープを用い、フッ素系樹脂を含む膜209に第3の基板210を接着させることとする。

次に、第2の基板206および第1の接着層207を除去する(図3(C))。なお、第1の接着層207に用いた接着剤が水または有機溶媒に溶ける可溶性である場合には、水または有機溶媒による洗浄により接着剤を除去し、第2の基板206を剥がす。また、光照射により接着力が低下する感光性を有する接着剤を用いる場合には、光を照射した後、第2の基板206を剥がす。さらに、両面テープと水溶性の接着剤を組み合わせて用いる場合には、初めに光照射により両面テープの接着力を低下させて第2の基板206と素子形成層204等とを剥がした後、素子形成層204等に接着して残っている水溶性の接着剤を水洗により除去することもできる。

次に、第2の基板206および第1の接着層207を除去して露出した窒化物層205に接してスパッタリング法により、フッ素系樹脂を含む膜212を形成する(図4(A))。なお、ここで形成されるフッ素系樹脂を含む膜212は、先に説明したフッ素系樹脂を含む膜209と同様の材料を用いて、同様の方法により形成することができる。

次に、第3の基板210側から光を照射することにより、両面テープの接着力を低下させて第3の基板210および第2の接着層211を素子形成層204等から剥がすことにより図4(C)に示す構造を有する半導体装置を形成することができる。

以下に、本発明の実施例について説明する。

本発明の実施例について図5、図6を用いて説明する。ここでは、同一基板上にnチャネル型TFT及びpチャネル型TFTを同時に作製する方法について詳細に説明する。

基板500としては、石英基板、半導体基板、セラミックス基板、金属基板等を用いることができるが、本実施例ではガラス基板(#1737)を用いる。そして、基板500上に窒化物層501としてPCVD法により酸化窒化シリコン層を100nmの膜厚で成膜する。

次に、スパッタリング法により金属層502としてタングステン層を50nmの膜厚で成膜し、大気解放せず連続的にスパッタリング法により酸化物層503として酸化シリコン層を200nmの膜厚で成膜する。酸化シリコン層の成膜条件は、RF方式のスパッタリング装置を用い、酸化シリコンターゲット(直径30.5cm)を用い、基板を加熱するために加熱したアルゴンガスを流量30sccmとして流し、基板温度300℃、成膜圧力0.4Pa、成膜電力3kW、アルゴン流量/酸素流量=10sccm/30sccmとする。

次に、基板周縁部または端面をO2アッシングによってタングステン層を除去する。

次に下地絶縁膜504としてプラズマCVD法で成膜温度300℃、原料ガスSiH4、N2Oから作製される酸化窒化シリコン膜(組成比Si=32%、O=59%、N=7%、H=2%)を100nmの厚さに積層形成し、さらに大気解放せず連続的にプラズマCVD法で成膜温度300℃、成膜ガスSiH4で非晶質構造を有する半導体層(ここでは非晶質シリコン層)を54nmの厚さで形成する。この非晶質シリコン層は水素を含んでおり、後の熱処理によって水素を拡散させ、物理的手段で酸化物層の層内、あるいは界面において剥離することができる。

次に、重量換算で10ppmのニッケルを含む酢酸ニッケル塩溶液をスピナーで塗布する。塗布に代えてスパッタ法でニッケル元素を全面に散布する方法を用いてもよい。次いで、加熱処理を行い結晶化させて結晶構造を有する半導体膜(ここではポリシリコン層)を形成する。ここでは脱水素化のための熱処理(500℃、1時間)の後、結晶化のための熱処理(550℃、4時間)を行って結晶構造を有するシリコン膜を得る。また、この脱水素化のための熱処理(500℃、1時間)は、非晶質シリコン層に含まれる水素をタングステン層と酸化シリコン層との界面に拡散する熱処理を兼ねている。なお、ここではシリコンの結晶化を助長する金属元素としてニッケルを用いた結晶化技術を用いるが、他の公知の結晶化技術、例えば固相成長法やレーザー結晶化法を用いてもよい。

次に、結晶構造を有するシリコン膜表面の酸化膜を希フッ酸等で除去した後、結晶化率を高め、結晶粒内に残される欠陥を補修するためのレーザー光(XeCl:波長308nm)の照射を大気中、または酸素雰囲気中で行う。レーザー光には波長400nm以下のエキシマレーザー光や、YAGレーザーの第2高調波、第3高調波を用いる。ここでは、繰り返し周波数10〜1000Hz程度のパルスレーザー光を用い、当該レーザー光を光学系にて100〜500mJ/cm2に集光し、90〜95%のオーバーラップ率をもって照射し、シリコン膜表面を走査させればよい。ここでは、繰り返し周波数30Hz、エネルギー密度470mJ/cm2でレーザー光の照射を大気中で行う。

なお、大気中、または酸素雰囲気中で行うため、レーザー光の照射により表面に酸化膜が形成される。なお、ここではパルスレーザーを用いる例を示したが、連続発振のレーザーを用いてもよく、非晶質半導体膜の結晶化に際し、大粒径に結晶を得るためには、連続発振が可能な固体レーザーを用い、基本波の第2高調波〜第4高調波を適用するのが好ましい。代表的には、Nd:YVO4レーザー(基本波1064nm)の第2高調波(532nm)や第3高調波(355nm)を適用すればよい。連続発振のレーザーを用いる場合には、出力10Wの連続発振のYVO4レーザから射出されたレーザー光を非線形光学素子により高調波に変換する。また、共振器の中にYVO4結晶と非線形光学素子を入れて、高調波を射出する方法もある。そして、好ましくは光学系により照射面にて矩形状または楕円形状のレーザー光に成形して、被処理体に照射する。このときのエネルギー密度は0.01〜100MW/cm2程度(好ましくは0.1〜10MW/cm2)が必要である。そして、10〜2000cm/s程度の速度でレーザー光に対して相対的に半導体膜を移動させて照射すればよい。

次に、上記レーザー光の照射により形成された酸化膜に加え、オゾン水で表面を120秒処理して合計1〜5nmの酸化膜からなるバリア層を形成する。本実施例ではオゾン水を用いてバリア層を形成するが、酸素雰囲気下の紫外線の照射で結晶構造を有する半導体膜の表面を酸化する方法や酸素プラズマ処理により結晶構造を有する半導体膜の表面を酸化する方法やプラズマCVD法やスパッタ法や蒸着法などで1〜10nm程度の酸化膜を堆積してバリア層を形成してもよい。また、バリア層を形成する前にレーザー光の照射により形成された酸化膜を除去してもよい。

次に、バリア層上にスパッタリング法にてゲッタリングサイトとなるアルゴン元素を含む非晶質シリコン膜を10nm〜400nm、ここでは膜厚100nmで成膜する。本実施例では、アルゴン元素を含む非晶質シリコン膜は、シリコンターゲットを用いてアルゴンを含む雰囲気下で形成する。プラズマCVD法を用いてアルゴン元素を含む非晶質シリコン膜を形成する場合、成膜条件は、モノシランとアルゴンの流量比(SiH4:Ar)を1:99とし、成膜圧力を6.665Pa(0.05Torr)とし、RFパワー密度を0.087W/cm2とし、成膜温度を350℃とする。

その後、650℃に加熱された炉に入れて3分の熱処理を行いゲッタリングして、結晶構造を有する半導体膜中のニッケル濃度を低減する。炉に代えてランプアニール装置を用いてもよい。

次に、バリア層をエッチングストッパーとして、ゲッタリングサイトであるアルゴン元素を含む非晶質シリコン膜を選択的に除去した後、バリア層を希フッ酸で選択的に除去する。なお、ゲッタリングの際、ニッケルは酸素濃度の高い領域に移動しやすい傾向があるため、酸化膜からなるバリア層をゲッタリング後に除去することが望ましい。

次いで、得られた結晶構造を有するシリコン膜(ポリシリコン膜とも呼ばれる)の表面にオゾン水で薄い酸化膜を形成した後、レジストからなるマスクを形成し、所望の形状にエッチング処理して島状に分離された半導体層505、506を形成する。半導体層505、506を形成した後、レジストからなるマスクを除去する。

以上の工程で基板500上に窒化物層501、金属層502、酸化物層503、下地絶縁膜504を形成し、結晶構造を有する半導体膜を得た後、所望の形状にエッチング処理して島状に分離された半導体層505、506を形成することができる。

次に、フッ酸を含むエッチャントで酸化膜を除去すると同時にシリコン膜の表面を洗浄した後、ゲート絶縁膜507となる珪素を主成分とする絶縁膜を形成する。本実施例では、プラズマCVD法により115nmの厚さで酸化窒化シリコン膜(組成比Si=32%、O=59%、N=7%、H=2%)で形成する(図5(B)。

さらに、ゲート絶縁膜507上に膜厚20〜100nmの第1の導電膜508と、膜厚100〜400nmの第2の導電膜509とを積層形成する。本実施例では、ゲート絶縁膜507上に膜厚50nmの窒化タンタル膜、膜厚370nmのタングステン膜を順次積層する。

第1の導電膜508及び第2の導電膜509を形成する導電性材料としてはTa、W、Ti、Mo、Al、Cuから選ばれた元素、または前記元素を主成分とする合金材料もしくは化合物材料で形成する。また、第1の導電膜508及び第2の導電膜509としてリン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜や、AgPdCu合金を用いてもよい。また、2層構造に限定されず、例えば、膜厚50nmのタングステン膜、膜厚500nmのアルミニウムとシリコンの合金(Al−Si)膜、膜厚30nmの窒化チタン膜を順次積層した3層構造としてもよい。また、3層構造とする場合、第1の導電膜のタングステンに代えて窒化タングステンを用いてもよいし、第2の導電膜のアルミニウムとシリコンの合金(Al−Si)膜に代えてアルミニウムとチタンの合金膜(Al−Ti)を用いてもよいし、第3の導電膜の窒化チタン膜に代えてチタン膜を用いてもよい。また、単層構造であってもよい。

次に、図5(C)に示すように光露光工程によりレジストからなるマスク510、511を形成し、ゲート電極及び配線を形成するための第1のエッチング処理を行う。第1のエッチング処理では第1及び第2のエッチング条件で行う。エッチングにはICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用いると良い。ICPエッチング法を用い、エッチング条件(コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等)を適宜調節することによって所望のテーパー形状に膜をエッチングすることができる。なお、エッチング用ガスとしては、Cl2、BCl3、SiCl4、CCl4などを代表とする塩素系ガスまたはCF4、SF6、NF3などを代表とするフッ素系ガス、またはO2を適宜用いることができる。

本実施例では、基板側(試料ステージ)にも150WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。なお、基板側の電極面積サイズは、12.5cm×12.5cmであり、コイル型の電極面積サイズ(ここではコイルの設けられた石英円板)は、直径25cmの円板である。この第1のエッチング条件によりW膜をエッチングして第1の導電層の端部をテーパー形状とする。第1のエッチング条件でのWに対するエッチング速度は200.39nm/min、TaNに対するエッチング速度は80.32nm/minであり、TaNに対するWの選択比は約2.5である。また、この第1のエッチング条件によって、Wのテーパー角は、約26°となる。この後、レジストからなるマスク510、511を除去せずに第2のエッチング条件に変え、エッチング用ガスにCF4とCl2とを用い、それぞれのガス流量比を30/30(sccm)とし、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して約30秒程度のエッチングを行った。基板側(試料ステージ)にも20WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。CF4とCl2を混合した第2のエッチング条件ではW膜及びTaN膜とも同程度にエッチングされる。第2のエッチング条件でのWに対するエッチング速度は58.97nm/min、TaNに対するエッチング速度は66.43nm/minである。なお、ゲート絶縁膜上に残渣を残すことなくエッチングするためには、10〜20%程度の割合でエッチング時間を増加させると良い。

上記第1のエッチング処理では、レジストからなるマスクの形状を適したものとすることにより、基板側に印加するバイアス電圧の効果により第1の導電層及び第2の導電層の端部がテーパー形状となる。このテーパー部の角度は15〜45°とすればよい。

こうして、第1のエッチング処理により第1の導電層と第2の導電層から成る第1の形状の導電層512、513(第1の導電層512a、513aと第2の導電層512b、513b)を形成する。ゲート絶縁膜となる絶縁膜507は、10〜20nm程度エッチングされ、第1の形状の導電層512、513で覆われない領域が薄くなったゲート絶縁膜511となる。

次に、レジストからなるマスクを除去せずに第2のエッチング処理を行う。ここでは、エッチング用ガスにSF6とCl2とO2とを用い、それぞれのガス流量比を24/12/24(sccm)とし、1.3Paの圧力でコイル型の電極に700WのRF(13.56MHz)電力を投入してプラズマを生成してエッチングを25秒行う。基板側(試料ステージ)にも10WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。第2のエッチング処理でのWに対するエッチング速度は227.3nm/min、TaNに対するエッチング速度は32.1nm/minであり、TaNに対するWの選択比は7.1であり、絶縁膜511であるSiONに対するエッチング速度は33.7nm/minであり、SiONに対するWの選択比は6.83である。このようにエッチングガス用ガスにSF6を用いた場合、絶縁膜511との選択比が高いので膜減りを抑えることができる。本実施例における絶縁膜511の膜減りは8nm程度である。

この第2のエッチング処理によりWのテーパー角を70°とすることができる。この第2のエッチング処理により第2の導電層514b、515bを形成する。このとき、第1の導電層は、ほとんどエッチングされず、第1の導電層514a、515aとなる。なお、第1の導電層514a、515aは、第1の導電層512a、513aとほぼ同一サイズである。実際には、第1の導電層の幅は、第2のエッチング処理前に比べて約0.3μm程度、即ち線幅全体で0.6μm程度後退する場合もあるがほとんどサイズに変化がない。

また、2層構造に代えて、膜厚50nmのタングステン膜、膜厚500nmのアルミニウムとシリコンの合金(Al−Si)膜、膜厚30nmの窒化チタン膜を順次積層した3層構造とした場合、第1のエッチング処理における第1のエッチング条件としては、BCl3とCl2とO2とを原料ガスに用い、それぞれのガス流量比を65/10/5(sccm)とし、基板側(試料ステージ)に300WのRF(13.56MHz)電力を投入し、1.2Paの圧力でコイル型の電極に450WのRF(13.56MHz)電力を投入してプラズマを生成して117秒のエッチングを行えばよく、第1のエッチング処理における第2のエッチング条件としては、CF4とCl2とO2とを用い、それぞれのガス流量比を25/25/10(sccm)とし、基板側(試料ステージ)にも20WのRF(13.56MHz)電力を投入し、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して約30秒程度のエッチングを行えばよく、第2のエッチング処理としてはBCl3とCl2を用い、それぞれのガス流量比を20/60(sccm)とし、基板側(試料ステージ)には100WのRF(13.56MHz)電力を投入し、1.2Paの圧力でコイル型の電極に600WのRF(13.56MHz)電力を投入してプラズマを生成してエッチングを行えばよい。

次いで、レジストからなるマスクを除去した後、第1のドーピング処理を行って図6(A)の状態を得る。ドーピング処理はイオンドープ法、もしくはイオン注入法で行えば良い。イオンドープ法の条件はドーズ量を1.5×1014atoms/cm2とし、加速電圧を60〜100keVとして行う。n型を付与する不純物元素として、典型的にはリン(P)または砒素(As)を用いる。この場合、第1の導電層及び第2の導電層514、515がn型を付与する不純物元素に対するマスクとなり、自己整合的に第1の不純物領域516、517が形成される。第1の不純物領域516、517には1×1016〜1×1017/cm3の濃度範囲でn型を付与する不純物元素を添加する。ここでは、第1の不純物領域と同じ濃度範囲の領域をn--領域とも呼ぶ。

なお、本実施例ではレジストからなるマスクを除去した後、第1のドーピング処理を行ったが、レジストからなるマスクを除去せずに第1のドーピング処理を行ってもよい。

次に、図6(B)に示すようにレジストからなるマスク518を形成し第2のドーピング処理を行う。マスク518はpチャネル型TFTを形成する半導体層のチャネル形成領域及びその周辺の領域を保護するマスクである。

第2のドーピング処理におけるイオンドープ法の条件はドーズ量を1.5×1015atoms/cm2とし、加速電圧を60〜100keVとしてリン(P)をドーピングする。ここでは、第2の導電層514b、515bをマスクとして各半導体層に不純物領域が自己整合的に形成される。勿論、マスク518で覆われた領域には添加されない。こうして、第2の不純物領域519と、第3の不純物領域520が形成される。第2の不純物領域519には1×1020〜1×1021/cm3の濃度範囲でn型を付与する不純物元素を添加されている。ここでは、第2の不純物領域と同じ濃度範囲の領域をn+領域とも呼ぶ。

また、第3の不純物領域520は第1の導電層515aにより第2の不純物領域519よりも低濃度に形成され、1×1018〜1×1019/cm3の濃度範囲でn型を付与する不純物元素を添加されることになる。なお、第3の不純物領域520は、テーパー形状である第1の導電層515aの部分を通過させてドーピングを行うため、テーパ−部の端部に向かって不純物濃度が増加する濃度勾配を有している。ここでは、第3の不純物領域520と同じ濃度範囲の領域をn-領域とも呼ぶ。

次いで、レジストからなるマスク518を除去した後、新たにレジストからなるマスク521を形成して図6(C)に示すように第3のドーピング処理を行う。

上記第3のドーピング処理により、pチャネル型TFTを形成する半導体層にp型の導電型を付与する不純物元素が添加された第4の不純物領域522及び第5の不純物領域523を形成する。

また、第4の不純物領域522には1×1020〜1×1021/cm3の濃度範囲でp型を付与する不純物元素が添加されるようにする。尚、第4の不純物領域522には先の工程でリン(P)が添加された領域(n--領域)であるが、p型を付与する不純物元素の濃度がその1.5〜3倍添加されていて導電型はp型となっている。ここでは、第4の不純物領域522と同じ濃度範囲の領域をp+領域とも呼ぶ。

また、第5の不純物領域523は第1の導電層515aのテーパー部と重なる領域に形成されるものであり、1×1018〜1×1020/cm3の濃度範囲でp型を付与する不純物元素が添加されるようにする。ここでは、第5の不純物領域523と同じ濃度範囲の領域をp-領域とも呼ぶ。

以上の工程により、それぞれの半導体層にn型またはp型の導電型を有する不純物領域が形成される。導電層514、515はTFTのゲート電極となる。

次に、ほぼ全面を覆う絶縁膜524を形成する。本実施例では、プラズマCVD法により膜厚50nmの酸化シリコン膜を形成する。勿論、この絶縁膜は酸化シリコン膜に限定されるものでなく、他のシリコンを含む絶縁膜を単層または積層構造として用いても良い。

次に、それぞれの半導体層に添加された不純物元素を活性化処理する工程を行う。この活性化工程は、ランプ光源を用いたラピッドサーマルアニール法(RTA法)、或いはYAGレーザーまたはエキシマレーザーを裏面から照射する方法、或いは炉を用いた熱処理、或いはこれらの方法のうち、いずれかと組み合わせた方法によって行う。

また、本実施例では、上記活性化の前に絶縁膜を形成した例を示したが、上記活性化を行った後、絶縁膜を形成する工程としてもよい。

次に、窒化シリコン膜からなる第1の層間絶縁膜525を形成して熱処理(300〜550℃で1〜12時間の熱処理)を行い、半導体層を水素化する工程を行う(図6(D))。この工程は第1の層間絶縁膜525に含まれる水素により半導体層のダングリングボンドを終端する工程である。酸化シリコン膜からなる絶縁膜524の存在に関係なく半導体層を水素化することができる。ただし、本実施例では、第2の導電層としてアルミニウムを主成分とする材料を用いているので、水素化する工程において第2の導電層が耐え得る熱処理条件とすることが重要である。水素化の他の手段として、プラズマ水素化(プラズマにより励起された水素を用いる)を行っても良い。

次に、第1の層間絶縁膜525上に有機絶縁物材料から成る第2の層間絶縁膜526を形成する。本実施例では膜厚1.6μmのアクリル樹脂膜を形成する。次に、各不純物領域に達するコンタクトホールを形成する。本実施例では複数のエッチング処理を順次行う。本実施例では第1の層間絶縁膜525をエッチングストッパーとして第2の層間絶縁膜526をエッチングした後、絶縁膜524をエッチングストッパーとして第1の層間絶縁膜525をエッチングしてから絶縁膜524をエッチングする。

その後、Al、Ti、Mo、Wなどを用いて配線527、528、529、530を形成する。

以上の様にして、nチャネル型TFT601、pチャネル型TFT602を同一基板上に形成することができる(図6)。

なお、これらのnチャネル型TFT601、pチャネル型TFT602を相補的に接続することによりCMOS回路を形成して用いることもできる。

また、本実施例で示すゲート電極と不純物領域の一部が重なる構造(GOLD構造)のTFTを用いる場合は、ゲート絶縁膜が薄くなると寄生容量が増加するが、ゲート電極(第1導電層)のテーパー部となる部分サイズを小さくして寄生容量を低減すれば、f特性(周波数特性)も向上してさらなる高速動作が可能となり、且つ、十分な信頼性を有するTFTとすることができる。

なお、以上のようにして基板500上にnチャネル型TFT601、pチャネル型TFT602形成した後、本発明の実施の形態で説明した工程を用いることにより、これらのTFTが形成された素子形成層がフッ素系樹脂を含む膜に覆われた構造を有する本発明の半導体装置を作製することができる。

但し、本実施例で形成されたTFTを含む素子形成層は、50μm以下の膜厚で形成されることを特徴とする。

本実施例では、本発明の半導体装置としてCPUを作製した場合について図7を用いて説明する。

図7(A)に示すようにフッ素系樹脂を含む膜701上にTFTを複数組み合わせて構成されるCPU705が形成されている。さらに、CPU705上にはフッ素系樹脂を含む膜702が形成されており、本実施例においてはこれらのフッ素系樹脂を含む膜701、702によりCPU705が完全に覆われた構造を有する。このような構造とすることにより、CPU705を外部と完全に遮断することができるので、外部からの水分や酸素等の侵入を防ぐことができる。

しかし、CPU705は、ボンディングワイヤ704等により外部と接続する必要があることから、内部に形成される配線と電気的に接続するための構造が必要となる。

そこで、本実施例では、図7(B)に示す構造とすることによりCPU705内部の配線706を外部接続部713において、ボンディングワイヤ704と接続させる。この場合は、本発明の実施の形態に示した作製方法において、フッ素系樹脂を含む膜712を形成する前に導電性のある金属材料を用いて金属体707を形成し、その後フッ素系樹脂を含む膜712を形成する。

そして、金属体707上に形成されたフッ素系樹脂を含む膜712を一部除去することにより外部接続部713を形成することができる。

その他、図7(C)に示す構成とすることもできる。この場合には、フッ素系樹脂を含む膜721、722により覆われたCPU705に物理的手段を用いて開口部を形成し、その開口部に金属体717を充填することにより、配線716と電気的な接続を有する外部接続部723を形成することができる。

なお、本実施例で示した外部接続部の構造は、好ましい一例であり、本発明の半導体装置の外部接続部分を限定するものではない。すなわち、外部接続部となる配線上にのみフッ素系樹脂を含む膜が形成されない工程を選択することも可能である。

本発明で形成される半導体装置は、薄膜軽量でフレキシブルな構造を有していることから、1つの基板上に複数の半導体装置を組み合わせて用いることもできる。なお、ここでいう基板とはガラスや石英の他、プラスチックフィルム等の可撓性基板も含めるものとする。

すなわち、半導体装置がCPUである場合には、1つの基板上に複数のCPUを組み合わせて集積化させることができる。

なお、1つの基板上に複数の半導体装置を集積化する場合において、本発明の半導体装置は、その表面がフッ素系樹脂を含む膜で形成されていることから、その表面状態を逆スパッタ処理するなどして凹凸形状にした上で、基板上に各半導体装置を接着剤などで貼り付ければよい。

本実施例では、本発明により形成されるアクティブマトリクス型の発光装置について、図8を用いて詳細に説明する。なお、図8(A)は、発光装置を示す上面図、図8(B)は図8(A)をA−A’で切断した断面図である。点線で示された801は駆動回路部(ソース側駆動回路)、802は画素部、803は駆動回路部(ゲート側駆動回路)である。また、804はフッ素系樹脂を含む膜である。

なお、808はソース側駆動回路801及びゲート側駆動回路803に入力される信号を伝送するための配線であり、外部入力端子となるFPC(フレキシブルプリントサーキット)809からビデオ信号、クロック信号、スタート信号、リセット信号等を受け取る。なお、ここではFPCしか図示されていないが、このFPCにはプリント配線基盤(PWB)が取り付けられていても良い。本明細書における発光装置には、発光装置本体だけでなく、それにFPCもしくはPWBが取り付けられた状態をも含むものとする。

次に、断面構造について図8(B)を用いて説明する。フッ素系樹脂を含む膜810上には駆動回路部及び画素部が形成されているが、ここでは、駆動回路部であるソース側駆動回路801と、画素部802が示されている。なお、フッ素系樹脂を含む膜810は、スパッタリング法により形成されており、具体的には、ポリテトラフルオロエチレン、テトラフルオロエチレン−ヘキサフルオロプロピレン共重合体、ポリクロロトリフルオロエチレン、テトラフルオロエチレン−エチレン共重合体、ポリビニルフルオライド、ポリビニリデンフルオライド等のフッ素系樹脂を含む膜を用いることができる。

なお、ソース側駆動回路801はnチャネル型TFT823とpチャネル型TFT824とを組み合わせたCMOS回路が形成される。また、駆動回路を形成するTFTは、公知のCMOS回路、PMOS回路もしくはNMOS回路で形成しても良い。また、本実施例では、フッ素系樹脂を含む膜上の同一表面に駆動回路を形成したドライバー一体型を示すが、必ずしもその必要はなく、外部に形成することもできる。

また、画素部802はスイッチング用TFT811と、電流制御用TFT812とそのドレインに電気的に接続された第1の電極813とを含む複数の画素により形成される。なお、第1の電極813の端部を覆って絶縁物814が形成されている。ここでは、ポジ型の感光性アクリル樹脂膜を用いることにより形成する。

また、カバレッジを良好なものとするため、絶縁物814の上端部または下端部に曲率を有する曲面が形成されるようにする。例えば、絶縁物814の材料としてポジ型の感光性アクリルを用いた場合、絶縁物814の上端部のみに曲率半径(0.2μm〜3μm)を有する曲面を持たせることが好ましい。また、絶縁物814として、感光性の光によってエッチャントに不溶解性となるネガ型、或いは光によってエッチャントに溶解性となるポジ型のいずれも使用することができる。

第1の電極813上には、電界発光層816、および第2の電極817がそれぞれ形成されている。ここで、第1の電極813に用いる材料としては、仕事関数の大きい材料を用いることが望ましい。例えば、窒化チタン膜、クロム膜、タングステン膜、Zn膜、Pt膜などの単層膜の他、窒化チタンとアルミニウムを主成分とする膜との積層、窒化チタン膜とアルミニウムを主成分とする膜と窒化チタン膜との3層構造等を用いることができる。なお、積層構造とすると、配線としての抵抗も低く、良好なオーミックコンタクトがとれ、さらに陽極として機能させることができる。

また、電界発光層816は、蒸着マスクを用いた蒸着法、またはインクジェット法によって形成することができる。

さらに、電界発光層816上に形成される第2の電極(陰極)817に用いる材料としては、仕事関数の小さい材料(Al、Ag、Li、Ca、またはこれらの合金MgAg、MgIn、AlLi、CaF2、またはCaN)を用いればよい。ここでは、発光が透過するように、第2の電極(陰極)817として、膜厚を薄くした金属薄膜と、透明導電膜(ITO(酸化インジウム酸化スズ合金)、酸化インジウム酸化亜鉛合金(In2O3―ZnO)、酸化亜鉛(ZnO)等)との積層を用いる。

また、第2の電極817は全画素に共通の配線としても機能し、接続配線808を経由してFPC809に電気的に接続されている。

また、第2の電極817上には、フッ素系樹脂を含む膜804がスパッタリング法により形成されている。フッ素系樹脂を含む膜804は、先に説明したフッ素系樹脂を含む膜810と同様の材料を用いて形成される。

なお、フッ素系樹脂を含む膜804を形成する前に無機絶縁膜を形成することもできる。具体的には無機絶縁膜として、スパッタリング法、CVD法または蒸着法により得られる窒化珪素膜、酸化珪素膜、酸化窒化珪素膜(SiNO膜(組成比N>O)またはSiON膜(組成比N<O))、炭素を主成分とする薄膜(例えばDLC膜、CN膜)を用いることができる。

以上のように本実施例で示す発光装置は、フッ素系樹脂を含む膜804、810によりその外部が覆われた構造を有している。発光素子818のうち、特に電界発光層は水分や酸素により劣化することから、このようにフッ素系樹脂を含む膜804、810により発光素子818が覆われた構造とすることにより、外部から水分や酸素等の侵入を防ぐことができるため、信頼性の高い発光装置を得ることができる。

なお、本実施例は、本発明の実施の形態に示したフッ素系樹脂を含む膜で素子形成層を覆う方法、実施例1で示したTFTの作製方法を自由に組み合わせることで本実施例を実施することができる。また、FPCとの接続部分について、実施例2に示す接続方法により本実施例を実施することもできる。

本発明の半導体装置、表示装置、または発光装置(本実施例では、半導体装置等と示す)は、ガラスや石英等の基板上に半導体素子を形成して得られる通常の構造と異なり、これらの基板の代わりにフッ素系樹脂を含む膜で外部を覆われているため、外部からの水分や酸素等の侵入を防ぐことができるという効果の他に、薄膜軽量化およびフレキシブルな構造が実現されている。従って、本発明の半導体装置等を用いて様々な応用製品を完成させることができる。

本発明により作製した半導体装置等を用いて作製された応用製品として、プリペイドカード、クレジットカード、免許証、またはウエアラブルコンピュータ(ゴーグル型ディスプレイ、ヘッドマウントディスプレイ)、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)等の記録媒体を再生し、その画像を表示しうる表示装置を備えた装置)などが挙げられる。これら応用製品の具体例を図9に示す。

図9(A)はプリペイドカードであり、本体2001に本発明により作製した半導体装置等を用いることにより作製される。具体的には、カードの使用履歴などを管理させることができる。なお、本発明の半導体装置等は、薄膜軽量化され、フレキシブルな構造を有しており、携帯性に優れていることからプリペイドカードへの使用に適している。

図9(B)は免許証であり、本体2201に本発明により作製した半導体装置等を用いることにより作製される。具体的には、所有者の運転履歴などを管理させることができる。なお、本発明の半導体装置等は、薄膜軽量化され、フレキシブルな構造を有しており、携帯性に優れていることから免許証への使用にも適している。

図9(C)はデジタルスチルカメラであり、本体2101、表示部2102、受像部2103、操作キー2104、外部接続ポート2105、シャッター2106等を含む。本発明により作製した半導体装置等をその表示部2102に用いることにより作製される。

図9(D)はモバイルコンピュータであり、本体2301、表示部2302、スイッチ2303、操作キー2304、赤外線ポート2305等を含む。本発明により作製した半導体装置等をその表示部2302に用いることにより作製される。

図9(E)はゴーグル型ディスプレイ(ヘッドマウントディスプレイ)であり、本体2501、表示部2502、アーム部2503を含む。本発明により作製した半導体装置等をその表示部2502に用いることにより作製される。

図9(F)はビデオカメラであり、本体2601、表示部2602、筐体2603、外部接続ポート2604、リモコン受信部2605、受像部2606、バッテリー2607、音声入力部2608、操作キー2609、接眼部2610等を含む。本発明により作製した半導体装置等をその表示部2602に用いることにより作製される。

ここで図9(G)は携帯電話であり、本体2701、筐体2702、表示部2703、音声入力部2704、音声出力部2705、操作キー2706、外部接続ポート2707、アンテナ2708等を含む。本発明により作製した半導体装置等をその表示部2703に用いることにより作製される。

以上の様に、本発明により作製された半導体装置の適用範囲は極めて広く、本発明の半導体装置等をあらゆる分野の応用製品に適用することが可能である。

本実施では、本発明において用いるフッ素系樹脂を含む膜の特性について測定した結果を示す。なお、測定に用いたフッ素系樹脂を含む膜としては、Arを材料ガスとして30(sccm)導入し、スパッタ圧力を0.4Pa、パワーを400W、基板温度を300℃としてポリテトラフルオロエチレンをターゲットに用いたスパッタリング法により、100nmの膜厚で成膜した膜である。

図10には、X線光電子分光法であるESCA(photonelectron spectroscopy for chemical analysis:)により得られたスペクトルを示すものである。なお、この場合におけるサンプル中の成分元素の組成比は、フッ素(F):酸素(O):炭素(C)=61:<1:38であり、珪素(Si)は検出されなかった。

また、同様の測定方法により、成膜条件の異なる膜を測定した結果を図11に示す。なお、この場合には、材料ガスとしてArを30(sccm)、O2を5(sccm)導入している。組成比に関しては、図10の条件の場合と同様であった。

また、図12には、フーリエ変換赤外分光法(Fourier transform infrared spectroscopy:FT−IR)による定性分析結果を示す。なお、図12中に示す(a)〜(c)からは、CF(1100〜1000cm-1)、CF2(1250〜1070cm-1)、およびCF3(1360〜1150cm-1)に由来のピークが確認されていると考えられる。その中でも特に(b)のピークが特徴的であるため、CF2が高い割合で含まれると考えられる。

本発明では、図13に示すように素子形成層1301と、これを覆うフッ素系樹脂を含む膜1302、1303との間に素子形成層1301で発生する熱を放散させるための熱伝導層1304、1305を設けることもできる。

図13に示すように複数のTFTで構成された半導体装置、表示装置、または発光装置を含む素子形成層1301と接して熱伝導層1304、1305が形成されている。

なお、熱導電層1304は、熱導電性を有する膜で形成され、窒化アルミニウム(AlN)、窒化酸化アルミニウム(AlNxOy(X>Y))、隣化硼素(BP)、窒化硼素(BN)または、DLC(Diamond Like Carbon)により形成される。また、これらの膜を組み合わせた積層膜を用いて熱伝導層1304を形成してもよい。

また、熱伝導層1304の形成方法としては、スパッタリング法、蒸着法、CVD法等を用いることができる。

例えば、熱伝導層1304をAlNで形成する場合には、窒化アルミニウム(AlN)ターゲットを用い、アルゴンガスと窒素ガスが混合した雰囲気下にて成膜する。なお、アルミニウム(Al)ターゲットを用い、窒素ガス雰囲気下にて成膜することもできる。

なお、本実施例で示す熱伝導層1304、1305の形成は、フッ素系樹脂を含む膜1302を形成する直前に熱伝導層1304を形成し、フッ素系樹脂を含む膜1303を形成する直前に熱伝導層1305を形成するものとする。

また、図13では、素子形成層1301を挟んで両側に熱伝導層1304、1305が形成される場合について示したが、どちらか一方に形成されていても良い。

本発明の半導体装置の構造を説明する図。

本発明の半導体装置の作製方法を説明する図。

本発明の半導体装置の作製方法を説明する図。

本発明の半導体装置の作製方法を説明する図。

TFTの作製工程を説明する図。

TFTの作製工程を説明する図。

本発明の半導体装置の外部接続構造を説明する図。

本発明の発光装置について説明する図。

本発明の半導体装置等を用いた応用製品を説明する図。

フッ素系樹脂を含む膜についてのESCA測定結果を説明する図。

フッ素系樹脂を含む膜についてのESCA測定結果を説明する図。

フッ素系樹脂を含む膜についてのIR測定結果を説明する図。

本発明の半導体装置の構造を説明する図。

符号の説明

101 素子形成層

102、103 フッ素系樹脂を含む膜