JP4425897B2 - 高電源レベルを有するプログラマブルロジックデバイスメモリ要素 - Google Patents

高電源レベルを有するプログラマブルロジックデバイスメモリ要素 Download PDFInfo

- Publication number

- JP4425897B2 JP4425897B2 JP2006307333A JP2006307333A JP4425897B2 JP 4425897 B2 JP4425897 B2 JP 4425897B2 JP 2006307333 A JP2006307333 A JP 2006307333A JP 2006307333 A JP2006307333 A JP 2006307333A JP 4425897 B2 JP4425897 B2 JP 4425897B2

- Authority

- JP

- Japan

- Prior art keywords

- power supply

- programmable

- memory element

- supply voltage

- data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/02—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components

- H03K19/173—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components

- H03K19/177—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components arranged in matrix form

- H03K19/17748—Structural details of configuration resources

- H03K19/1776—Structural details of configuration resources for memories

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/02—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components

- H03K19/173—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components

- H03K19/177—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components arranged in matrix form

- H03K19/1778—Structural details for adapting physical parameters

- H03K19/17784—Structural details for adapting physical parameters for supply voltage

Landscapes

- Physics & Mathematics (AREA)

- Mathematical Physics (AREA)

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Computing Systems (AREA)

- General Engineering & Computer Science (AREA)

- Logic Circuits (AREA)

Description

コアロジック電源電圧において電力供給されたプログラマブルコアロジックと、

該プログラマブルコアロジックを構成する出力を有するメモリ要素のアレイと、

該アレイ内の該メモリ要素をアドレスするための複数のアドレスラインと、

該メモリ要素にプログラマブルロジックデバイスコンフィギュレーションデータをロードするために、該コアロジック電源電圧より大きい電圧レベルを有するアドレス信号を該アドレスラインに印加するデータローディング・読み取り回路網と

を備える、プログラマブルロジックデバイス集積回路。

前記メモリ要素に電力供給する時間変化メモリ要素電源電圧を提供する電力調節器回路網をさらに備え、前記データローディング・読み取り回路網が前記プログラマブルロジックデバイスコンフィギュレーションデータをロードするために前記アドレス信号を前記アドレスラインに印加した場合、該時間変化メモリ要素電源電圧は前記コアロジック電源電圧と等しく、該時間変化メモリ要素電源電圧は、通常動作の間、該コアロジック電源電圧より大きい、項目1に記載のプログラマブルロジックデバイス集積回路。

前記メモリ要素の通常動作の間、前記コアロジックの正の電源電圧より大きいメモリ要素電源電圧において該メモリ要素に電力供給する電力調節器回路網をさらに備える、項目1に記載のプログラマブルロジックデバイス集積回路。

前記メモリ要素の各々は相互結合インバータを含み、前記データローディング・読み取り回路網は該メモリ要素からプログラマブルロジックデバイスコンフィギュレーションデータを読み取るためにアドレス信号を前記アドレスラインに印加し、該プログラマブルロジックデバイスコンフィギュレーションデータを読み取るために使用される該アドレス信号は、該プログラマブルロジックデバイスコンフィギュレーションデータを該メモリ要素にロードするときに使用される該アドレス信号の電圧レベルより少ない電圧レベルを有する、項目1に記載のプログラマブルロジックデバイス集積回路。

複数のアドレストランジスタをさらに備え、該アドレストランジスタの各々は、前記メモリ要素のアレイ内のそれぞれのメモリ要素に関連してかつゲートを有し、該ゲートは前記アドレスラインによって制御され、該ゲートは、前記プログラマブルロジックデバイスコンフィギュレーションデータが該メモリ要素にロードされるデータ書き取り動作の間に第1の電圧レベルにおいてアドレス信号を受信し、該プログラマブルロジックデバイスコンフィギュレーションデータが前記データローディング・読み取り回路網によって該メモリ要素から読み取られるデータ読み取り動作の間に第2の電圧レベルにおいてアドレス信号を受信し、該第1の電圧レベルは、前記コアロジック電源電圧より大きく、該第2の電圧レベルは、該コアロジック電源電圧と等しい、項目1に記載のプログラマブルロジックデバイス集積回路。

複数のアドレストランジスタであって、該アドレストランジスタの各々は、前記メモリ要素のアレイ内のそれぞれのメモリ要素に関連してかつゲートを有し、該ゲートは前記アドレスラインによって制御され、該ゲートは、前記プログラマブルロジックデバイスコンフィギュレーションデータが該メモリ要素にロードされるデータ書き取り動作の間に第1の電圧レベルにおいてアドレス信号を受信し、該プログラマブルロジックデバイスコンフィギュレーションデータが前記データローディング・読み取り回路網によって該メモリ要素から読み取られるデータ読み取り動作の間に第2の電圧レベルにおいてアドレス信号を受信し、該第1の電圧レベルは、前記コアロジック電源電圧より大きく、該第2の電圧レベルは、該コアロジック電源電圧と等しい、複数のアドレストランジスタと、

該メモリ要素の通常動作の間、該第1の電圧レベルと等しい電源電圧において該メモリ要素に電力供給する電力調節器回路網と

をさらに備える、項目1に記載のプログラマブルロジックデバイス集積回路。

データローディング動作の間にコンフィギュレーションデータが書き込まれ、コンフィギュレーションデータが読み取り動作の間に読み取られるプログラマブルロジックデバイスメモリ要素を有するプログラマブルロジックデバイス集積回路であって、該プログラマブルロジックデバイス集積回路は、

プログラマブルコアロジック電源電圧において電力供給されたプログラマブルコアロジックと、

該プログラマブルコアロジックを構成する通常動作の間、制御信号を該プログラマブルコアロジックに供給する該メモリ要素のアレイと、

読み取り動作の間とは異なる電圧レベルをデータローディング動作の間に該メモリ要素をアドレスするアドレス信号を生成するデータローディング・読み取り回路網と

を備える、プログラマブルロジックデバイス集積回路。

前記アドレス信号は、データローディング動作の間に前記プログラマブルコアロジック電源電圧より大きく、読み取り動作の間に該プログラマブルコアロジック電源電圧と等しい電圧レベルを有し、該プログラマブルロジックデバイス集積回路は、メモリ要素電源電圧において前記メモリ要素に電力供給する電力調節器回路網をさらに含む、項目7に記載のプログラマブルロジックデバイス集積回路。

前記アドレス信号は、データローディング動作の間に前記プログラマブルコアロジック電源電圧より大きく、読み取り動作の間に該プログラマブルコアロジック電源電圧と等しい電圧レベルを有し、該プログラマブルロジックデバイス集積回路は、データローディング動作の間の該アドレス信号の該電圧レベルと等しいメモリ要素電源電圧において前記メモリ要素に電力供給する電力調節器回路網をさらに含む、項目7に記載のプログラマブルロジックデバイス集積回路。

前記アドレス信号は、データローディング動作の間に前記プログラマブルコアロジック電源電圧より大きく、読み取り動作の間に該プログラマブルコアロジック電源電圧と等しい電圧レベルを有し、該プログラマブルロジックデバイス集積回路は、第1および第2の電圧レベルを有する時間変化メモリ要素電源電圧を生成するダイナミックな電力調節器回路網をさらに含み、該第1の電圧レベルは、データローディング動作の間に生成され、該第2の電圧レベルは、通常動作の間に生成され、該第1の電圧は、該プログラマブルコアロジック電源電圧と等しく、該第2の電圧レベルは、該第1の電圧より大きい、項目7に記載のプログラマブルロジックデバイス集積回路。

プログラマブルロジックデバイス集積回路におけるプログラマブルロジックデバイスメモリ要素のアレイを使用する方法であって、プログラマブルロジックデバイスコンフィギュレーションデータは、データローディング動作の間に前記メモリ要素に書き込まれ、該プログラマブルロジックデバイスコンフィギュレーションデータは、データ読み取り動作の間に該メモリ要素から読み取られ、該方法は、

データローディング動作の間とデータ読み取り動作との間に異なる電圧レベルを有する該プログラマブルロジックデバイスメモリ要素のアレイをアドレス信号に印加することと、

通常動作の間、該プログラマブルロジックデバイスメモリ要素が該プログラマブルロジックデバイスコンフィギュレーションデータを用いてロードされた後、該プログラマブルロジックデバイス集積回路上にプログラマブルコアロジックを構成するために該プログラマブルコアロジックに該プログラマブルロジックデバイスメモリ要素からの出力信号を印加することと

を包含する、方法。

前記アドレス信号を印加することは、データ読み取り動作の間の該アドレス信号の電圧レベルより大きい電圧レベルを有するアドレス信号をデータローディング動作の間に印加することを含む、項目11に記載の方法。

前記アドレス信号を印加することは、第1の電圧レベルを有するアドレス信号をデータローディング動作の間に印加することと、第2の電圧レベルを有するアドレス信号をデータ読み取り動作の間に印加することとを含み、該第1の電圧レベルは、該第2の電圧レベルより大きく、前記方法は、

該第2の電圧レベルと等しいプログラマブルコアロジック電源電圧において該プログラマブルコアロジックに電力供給することをさらに包含する、項目11に記載の方法。

前記アドレス信号を印加することは、第1の電圧レベルを有するアドレス信号をデータローディング動作の間に印加することと、第2の電圧レベルを有するアドレス信号をデータ読み取り動作の間に印加することとを含み、該第1の電圧レベルは、該第2の電圧レベルより大きく、前記方法は、

該第2の電圧レベルと等しいプログラマブルコアロジック電源電圧において該プログラマブルコアロジックに電力供給することと、

通常動作の間、該プログラマブルコアロジック電源電圧より大きい電源電圧を用いて前記メモリ要素に電力供給することと

をさらに包含する、項目11に記載の方法。

プログラマブルコアロジック電源電圧において前記プログラマブルコアロジックに電力供給することと、

通常動作の間、該プログラマブルコアロジック電源電圧より大きい電源電圧を用いて前記メモリ要素に電力供給することと

をさらに包含する、項目11に記載の方法。

プログラマブルコアロジック電源電圧において前記プログラマブルコアロジックに電力供給することと、

通常動作の間、該プログラマブルコアロジック電源電圧より大きい電源電圧を用いて前記メモリ要素に電力供給することと、

データローディング動作の間、通常動作の間に該メモリ要素に電力供給するために使用される電源電圧より少ない電源電圧を用いて該メモリ要素に電力供給することと

をさらに包含する、項目11に記載の方法。

プログラマブルコアロジック電源電圧において前記プログラマブルコアロジックに電力供給することと、

通常動作の間、該プログラマブルコアロジック電源電圧より大きい電源電圧を用いて前記メモリ要素に電力供給することと、

データローディング動作の間、該プログラマブルコアロジック電源電圧と等しい電源電圧を用いて該メモリ要素に電力供給することと

をさらに包含する、項目11に記載の方法。

前記メモリ要素の各々は、2つの相互結合されたインバータを含み、該インバータの各々は、正の電源端子と接地端子との間に直列に接続されたpチャネル酸化金属半導体トランジスタおよびnチャネル酸化金属半導体トランジスタを有し、前記方法は、

プログラマブルコアロジック電源電圧において前記プログラマブルコアロジックに電力供給することと、

通常動作の間、該正の電源端子においては正の電源電圧を、かつ該接地端子においては接地電圧を印加することによって、該プログラマブルコアロジック電源電圧より大きい電源電圧を用いて前記メモリ要素に電力供給することであって、データ書き込み動作の間の前記アドレス信号の前記電圧レベルは、該正の電源電圧と等しい、ことと

をさらに包含する、項目11に記載の方法。

前記アドレス信号を印加することは、第1の電圧レベルを有するアドレス信号をデータローディング動作の間に印加することと、第2の電圧レベルを有するアドレス信号をデータ読み取り動作の間に印加することとを含み、該第1の電圧レベルは、該第2の電圧レベルより大きく、前記方法は、

プログラマブルコアロジック電源電圧において該プログラマブルコアロジックに電力供給することと、

通常動作の間、該プログラマブルコアロジック電源電圧より大きく、該第1の電圧レベルと等しい電源電圧を用いて前記メモリ要素に電力供給することと

をさらに包含する、項目11に記載の方法。

前記アドレス信号を印加することは、第1の電圧レベルを有するアドレス信号をデータローディング動作の間に印加することと、第2の電圧レベルを有するアドレス信号をデータ読み取り動作の間に印加することとを含み、該第1の電圧レベルは、該第2の電圧レベルより大きく、前記方法は、

該第2の電圧レベルと等しいプログラマブルコアロジック電源電圧において該プログラマブルコアロジックに電力供給することと、

通常動作の間、該プログラマブルコアロジック電源電圧より大きく、該第1の電圧レベルと等しい電源電圧を用いて前記メモリ要素に電力供給することと

をさらに包含する、項目11に記載の方法。

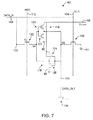

20、82 メモリ要素

96 データローディング・読み取り回路網

Claims (20)

- コアロジック電源電圧において電力供給されたプログラマブルコアロジックと、

該プログラマブルコアロジックを構成する出力を有するメモリ要素のアレイと、

該アレイ内の該メモリ要素をアドレスするための複数のアドレスラインと、

該メモリ要素にプログラマブルロジックデバイスコンフィギュレーションデータをロードするために、該コアロジック電源電圧より大きい電圧レベルを有するアドレス信号を該アドレスラインに印加するデータローディング・読み取り回路網と

を備える、プログラマブルロジックデバイス集積回路。 - 前記メモリ要素に電力供給する時間変化メモリ要素電源電圧を提供する電力調節器回路網をさらに備え、前記データローディング・読み取り回路網が前記プログラマブルロジックデバイスコンフィギュレーションデータをロードするために前記アドレス信号を前記アドレスラインに印加した場合、該時間変化メモリ要素電源電圧は前記コアロジック電源電圧と等しく、該時間変化メモリ要素電源電圧は、通常動作の間、該コアロジック電源電圧より大きい、請求項1に記載のプログラマブルロジックデバイス集積回路。

- 前記メモリ要素の通常動作の間、前記コアロジックの正の電源電圧より大きいメモリ要素電源電圧において該メモリ要素に電力供給する電力調節器回路網をさらに備える、請求項1に記載のプログラマブルロジックデバイス集積回路。

- 前記メモリ要素の各々は相互結合インバータを含み、前記データローディング・読み取り回路網は該メモリ要素からプログラマブルロジックデバイスコンフィギュレーションデータを読み取るためにアドレス信号を前記アドレスラインに印加し、該プログラマブルロジックデバイスコンフィギュレーションデータを読み取るために使用される該アドレス信号は、該プログラマブルロジックデバイスコンフィギュレーションデータを該メモリ要素にロードするときに使用される該アドレス信号の電圧レベルより少ない電圧レベルを有する、請求項1に記載のプログラマブルロジックデバイス集積回路。

- 複数のアドレストランジスタをさらに備え、該アドレストランジスタの各々は、前記メモリ要素のアレイ内のそれぞれのメモリ要素に関連してかつゲートを有し、該ゲートは前記アドレスラインによって制御され、該ゲートは、前記プログラマブルロジックデバイスコンフィギュレーションデータが該メモリ要素にロードされるデータ書き取り動作の間に第1の電圧レベルにおいてアドレス信号を受信し、該プログラマブルロジックデバイスコンフィギュレーションデータが前記データローディング・読み取り回路網によって該メモリ要素から読み取られるデータ読み取り動作の間に第2の電圧レベルにおいてアドレス信号を受信し、該第1の電圧レベルは、前記コアロジック電源電圧より大きく、該第2の電圧レベルは、該コアロジック電源電圧と等しい、請求項1に記載のプログラマブルロジックデバイス集積回路。

- 複数のアドレストランジスタであって、該アドレストランジスタの各々は、前記メモリ要素のアレイ内のそれぞれのメモリ要素に関連してかつゲートを有し、該ゲートは前記アドレスラインによって制御され、該ゲートは、前記プログラマブルロジックデバイスコンフィギュレーションデータが該メモリ要素にロードされるデータ書き取り動作の間に第1の電圧レベルにおいてアドレス信号を受信し、該プログラマブルロジックデバイスコンフィギュレーションデータが前記データローディング・読み取り回路網によって該メモリ要素から読み取られるデータ読み取り動作の間に第2の電圧レベルにおいてアドレス信号を受信し、該第1の電圧レベルは、前記コアロジック電源電圧より大きく、該第2の電圧レベルは、該コアロジック電源電圧と等しい、複数のアドレストランジスタと、

該メモリ要素の通常動作の間、該第1の電圧レベルと等しい電源電圧において該メモリ要素に電力供給する電力調節器回路網と

をさらに備える、請求項1に記載のプログラマブルロジックデバイス集積回路。 - データローディング動作の間にコンフィギュレーションデータが書き込まれ、コンフィギュレーションデータが読み取り動作の間に読み取られるプログラマブルロジックデバイスメモリ要素を有するプログラマブルロジックデバイス集積回路であって、該プログラマブルロジックデバイス集積回路は、

プログラマブルコアロジック電源電圧において電力供給されたプログラマブルコアロジックと、

該プログラマブルコアロジックを構成する通常動作の間、制御信号を該プログラマブルコアロジックに供給する該メモリ要素のアレイと、

読み取り動作の間とは異なる電圧レベルにおいてデータローディング動作の間に該メモリ要素をアドレスするアドレス信号を生成するデータローディング・読み取り回路網と

を備える、プログラマブルロジックデバイス集積回路。 - 前記アドレス信号は、データローディング動作の間に前記プログラマブルコアロジック電源電圧より大きく、読み取り動作の間に該プログラマブルコアロジック電源電圧と等しい電圧レベルを有し、該プログラマブルロジックデバイス集積回路は、メモリ要素電源電圧において前記メモリ要素に電力供給する電力調節器回路網をさらに含む、請求項7に記載のプログラマブルロジックデバイス集積回路。

- 前記アドレス信号は、データローディング動作の間に前記プログラマブルコアロジック電源電圧より大きく、読み取り動作の間に該プログラマブルコアロジック電源電圧と等しい電圧レベルを有し、該プログラマブルロジックデバイス集積回路は、データローディング動作の間の該アドレス信号の該電圧レベルと等しいメモリ要素電源電圧において前記メモリ要素に電力供給する電力調節器回路網をさらに含む、請求項7に記載のプログラマブルロジックデバイス集積回路。

- 前記アドレス信号は、データローディング動作の間に前記プログラマブルコアロジック電源電圧より大きく、読み取り動作の間に該プログラマブルコアロジック電源電圧と等しい電圧レベルを有し、該プログラマブルロジックデバイス集積回路は、第1および第2の電圧レベルを有する時間変化メモリ要素電源電圧を生成するダイナミックな電力調節器回路網をさらに含み、該第1の電圧レベルは、データローディング動作の間に生成され、該第2の電圧レベルは、通常動作の間に生成され、該第1の電圧は、該プログラマブルコアロジック電源電圧と等しく、該第2の電圧レベルは、該第1の電圧より大きい、請求項7に記載のプログラマブルロジックデバイス集積回路。

- プログラマブルロジックデバイス集積回路におけるプログラマブルロジックデバイスメモリ要素のアレイを使用する方法であって、プログラマブルロジックデバイスコンフィギュレーションデータは、データローディング動作の間に前記メモリ要素に書き込まれ、該プログラマブルロジックデバイスコンフィギュレーションデータは、データ読み取り動作の間に該メモリ要素から読み取られ、該方法は、

データローディング動作の間とデータ読み取り動作の間とで異なる電圧レベルを有する該プログラマブルロジックデバイスメモリ要素のアレイにアドレス信号を印加することと、

通常動作の間、該プログラマブルロジックデバイスメモリ要素が該プログラマブルロジックデバイスコンフィギュレーションデータを用いてロードされた後、該プログラマブルロジックデバイス集積回路上にプログラマブルコアロジックを構成するために該プログラマブルコアロジックに該プログラマブルロジックデバイスメモリ要素からの出力信号を印加することと

を包含する、方法。 - 前記アドレス信号を印加することは、データ読み取り動作の間の該アドレス信号の電圧レベルより大きい電圧レベルを有するアドレス信号をデータローディング動作の間に印加することを含む、請求項11に記載の方法。

- 前記アドレス信号を印加することは、第1の電圧レベルを有するアドレス信号をデータローディング動作の間に印加することと、第2の電圧レベルを有するアドレス信号をデータ読み取り動作の間に印加することとを含み、該第1の電圧レベルは、該第2の電圧レベルより大きく、前記方法は、

該第2の電圧レベルと等しいプログラマブルコアロジック電源電圧において該プログラマブルコアロジックに電力供給することをさらに包含する、請求項11に記載の方法。 - 前記アドレス信号を印加することは、第1の電圧レベルを有するアドレス信号をデータローディング動作の間に印加することと、第2の電圧レベルを有するアドレス信号をデータ読み取り動作の間に印加することとを含み、該第1の電圧レベルは、該第2の電圧レベルより大きく、前記方法は、

該第2の電圧レベルと等しいプログラマブルコアロジック電源電圧において該プログラマブルコアロジックに電力供給することと、

通常動作の間、該プログラマブルコアロジック電源電圧より大きい電源電圧を用いて前記メモリ要素に電力供給することと

をさらに包含する、請求項11に記載の方法。 - プログラマブルコアロジック電源電圧において前記プログラマブルコアロジックに電力供給することと、

通常動作の間、該プログラマブルコアロジック電源電圧より大きい電源電圧を用いて前記メモリ要素に電力供給することと

をさらに包含する、請求項11に記載の方法。 - プログラマブルコアロジック電源電圧において前記プログラマブルコアロジックに電力供給することと、

通常動作の間、該プログラマブルコアロジック電源電圧より大きい電源電圧を用いて前記メモリ要素に電力供給することと、

データローディング動作の間、通常動作の間に該メモリ要素に電力供給するために使用される電源電圧より少ない電源電圧を用いて該メモリ要素に電力供給することと

をさらに包含する、請求項11に記載の方法。 - プログラマブルコアロジック電源電圧において前記プログラマブルコアロジックに電力供給することと、

通常動作の間、該プログラマブルコアロジック電源電圧より大きい電源電圧を用いて前記メモリ要素に電力供給することと、

データローディング動作の間、該プログラマブルコアロジック電源電圧と等しい電源電圧を用いて該メモリ要素に電力供給することと

をさらに包含する、請求項11に記載の方法。 - 前記メモリ要素の各々は、2つの相互結合されたインバータを含み、該インバータの各々は、正の電源端子と接地端子との間に直列に接続されたpチャネル酸化金属半導体トランジスタおよびnチャネル酸化金属半導体トランジスタを有し、前記方法は、

プログラマブルコアロジック電源電圧において前記プログラマブルコアロジックに電力供給することと、

通常動作の間、該正の電源端子においては正の電源電圧を、かつ該接地端子においては接地電圧を印加することによって、該プログラマブルコアロジック電源電圧より大きい電源電圧を用いて前記メモリ要素に電力供給することであって、データ書き込み動作の間の前記アドレス信号の前記電圧レベルは、該正の電源電圧と等しい、ことと

をさらに包含する、請求項11に記載の方法。 - 前記アドレス信号を印加することは、第1の電圧レベルを有するアドレス信号をデータローディング動作の間に印加することと、第2の電圧レベルを有するアドレス信号をデータ読み取り動作の間に印加することとを含み、該第1の電圧レベルは、該第2の電圧レベルより大きく、前記方法は、

プログラマブルコアロジック電源電圧において該プログラマブルコアロジックに電力供給することと、

通常動作の間、該プログラマブルコアロジック電源電圧より大きく、該第1の電圧レベルと等しい電源電圧を用いて前記メモリ要素に電力供給することと

をさらに包含する、請求項11に記載の方法。 - 前記アドレス信号を印加することは、第1の電圧レベルを有するアドレス信号をデータローディング動作の間に印加することと、第2の電圧レベルを有するアドレス信号をデータ読み取り動作の間に印加することとを含み、該第1の電圧レベルは、該第2の電圧レベルより大きく、前記方法は、

該第2の電圧レベルと等しいプログラマブルコアロジック電源電圧において該プログラマブルコアロジックに電力供給することと、

通常動作の間、該プログラマブルコアロジック電源電圧より大きく、該第1の電圧レベルと等しい電源電圧を用いて前記メモリ要素に電力供給することと

をさらに包含する、請求項11に記載の方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US73786805P | 2005-11-17 | 2005-11-17 | |

| US11/335,437 US7277351B2 (en) | 2005-11-17 | 2006-01-18 | Programmable logic device memory elements with elevated power supply levels |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007143151A JP2007143151A (ja) | 2007-06-07 |

| JP2007143151A5 JP2007143151A5 (ja) | 2009-12-17 |

| JP4425897B2 true JP4425897B2 (ja) | 2010-03-03 |

Family

ID=37745961

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006307333A Expired - Fee Related JP4425897B2 (ja) | 2005-11-17 | 2006-11-14 | 高電源レベルを有するプログラマブルロジックデバイスメモリ要素 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7277351B2 (ja) |

| EP (2) | EP2464011B1 (ja) |

| JP (1) | JP4425897B2 (ja) |

| CN (2) | CN1967719B (ja) |

Families Citing this family (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7411853B2 (en) | 2005-11-17 | 2008-08-12 | Altera Corporation | Volatile memory elements with elevated power supply levels for programmable logic device integrated circuits |

| US7430148B2 (en) * | 2005-11-17 | 2008-09-30 | Altera Corporation | Volatile memory elements with boosted output voltages for programmable logic device integrated circuits |

| US7266028B1 (en) * | 2006-02-16 | 2007-09-04 | Altera Corporation | Method and apparatus for bit mapping memories in programmable logic device integrated circuits during at-speed testing |

| US7859301B2 (en) * | 2007-04-30 | 2010-12-28 | Altera Corporation | Power regulator circuitry for programmable logic device memory elements |

| US7911826B1 (en) | 2008-03-27 | 2011-03-22 | Altera Corporation | Integrated circuits with clearable memory elements |

| US7957177B2 (en) * | 2008-06-05 | 2011-06-07 | Altera Corporation | Static random-access memory with boosted voltages |

| US8355292B2 (en) | 2008-10-01 | 2013-01-15 | Altera Corporation | Volatile memory elements with soft error upset immunity |

| US8081503B1 (en) | 2009-02-27 | 2011-12-20 | Altera Corporation | Volatile memory elements with minimized area and leakage current |

| US7872903B2 (en) * | 2009-03-19 | 2011-01-18 | Altera Corporation | Volatile memory elements with soft error upset immunity |

| US8072237B1 (en) | 2009-06-04 | 2011-12-06 | Altera Corporation | Computer-aided design tools and memory element power supply circuitry for selectively overdriving circuit blocks |

| US8411491B1 (en) | 2011-01-03 | 2013-04-02 | Altera Corporation | Memory array with distributed clear transistors and variable memory element power supply |

| US8633731B1 (en) * | 2011-08-09 | 2014-01-21 | Altera Corporation | Programmable integrated circuit with thin-oxide passgates |

| US8483006B1 (en) | 2011-09-16 | 2013-07-09 | Altera Corporation | Programmable addressing circuitry for increasing memory yield |

| US8611137B2 (en) * | 2011-11-23 | 2013-12-17 | Altera Corporation | Memory elements with relay devices |

| DE112013002281T5 (de) * | 2012-05-02 | 2015-03-05 | Semiconductor Energy Laboratory Co., Ltd. | Programmierbare Logikvorrichtung |

| KR102059218B1 (ko) | 2012-05-25 | 2019-12-24 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 프로그래머블 로직 디바이스 및 반도체 장치 |

| CN102969019B (zh) * | 2012-12-04 | 2015-10-28 | 西安华芯半导体有限公司 | 一种增强静态随机存储器写操作的电路 |

| US9444460B1 (en) * | 2013-11-22 | 2016-09-13 | Altera Corporation | Integrated circuits with programmable overdrive capabilities |

| US9419622B2 (en) * | 2014-03-07 | 2016-08-16 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US10121534B1 (en) | 2015-12-18 | 2018-11-06 | Altera Corporation | Integrated circuit with overdriven and underdriven pass gates |

| KR102511901B1 (ko) * | 2016-04-11 | 2023-03-20 | 에스케이하이닉스 주식회사 | 넓은 동작 영역을 갖는 불휘발성 메모리 소자 |

| US10269426B2 (en) * | 2017-06-15 | 2019-04-23 | Intel Corporation | Integrated circuits with complementary non-volatile resistive memory elements |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0513714A (ja) | 1990-01-25 | 1993-01-22 | Texas Instr Inc <Ti> | 溝型トランジスタ使用の双安定論理デバイス |

| US20020130681A1 (en) | 1991-09-03 | 2002-09-19 | Cliff Richard G. | Programmable logic array integrated circuits |

| JPH08111094A (ja) | 1994-10-12 | 1996-04-30 | Nec Corp | スタチック型半導体記憶装置 |

| US5717340A (en) | 1996-01-17 | 1998-02-10 | Xilink, Inc. | Circuit for testing pumped voltage gates in a programmable gate array |

| US6147511A (en) | 1996-05-28 | 2000-11-14 | Altera Corporation | Overvoltage-tolerant interface for integrated circuits |

| US6025737A (en) | 1996-11-27 | 2000-02-15 | Altera Corporation | Circuitry for a low internal voltage integrated circuit |

| US5801551A (en) | 1996-08-01 | 1998-09-01 | Advanced Micro Devices, Inc. | Depletion mode pass gates with controlling decoder and negative power supply for a programmable logic device |

| US6018476A (en) * | 1996-09-16 | 2000-01-25 | Altera Corporation | Nonvolatile configuration cells and cell arrays |

| US6232893B1 (en) | 1998-05-27 | 2001-05-15 | Altera Corporation | Method and apparatus for programmably providing a power supply voltage to an integrated circuit |

| US6114843A (en) | 1998-08-18 | 2000-09-05 | Xilinx, Inc. | Voltage down converter for multiple voltage levels |

| US6108266A (en) * | 1999-10-28 | 2000-08-22 | Motorola, Inc. | Memory utilizing a programmable delay to control address buffers |

| GB0103837D0 (en) * | 2001-02-16 | 2001-04-04 | Nallatech Ltd | Programmable power supply for field programmable gate array modules |

| JP2002368135A (ja) | 2001-06-12 | 2002-12-20 | Hitachi Ltd | 半導体記憶装置 |

| US7430148B2 (en) * | 2005-11-17 | 2008-09-30 | Altera Corporation | Volatile memory elements with boosted output voltages for programmable logic device integrated circuits |

| US7411853B2 (en) * | 2005-11-17 | 2008-08-12 | Altera Corporation | Volatile memory elements with elevated power supply levels for programmable logic device integrated circuits |

-

2006

- 2006-01-18 US US11/335,437 patent/US7277351B2/en not_active Expired - Fee Related

- 2006-11-14 JP JP2006307333A patent/JP4425897B2/ja not_active Expired - Fee Related

- 2006-11-16 EP EP12158267.0A patent/EP2464011B1/en not_active Ceased

- 2006-11-16 EP EP06255868.9A patent/EP1788706B1/en not_active Ceased

- 2006-11-17 CN CN200610148491XA patent/CN1967719B/zh not_active Expired - Fee Related

- 2006-11-17 CN CN201110183540.4A patent/CN102290098B/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| EP1788706A1 (en) | 2007-05-23 |

| JP2007143151A (ja) | 2007-06-07 |

| EP1788706B1 (en) | 2014-07-30 |

| EP2464011B1 (en) | 2019-08-21 |

| EP2464011A3 (en) | 2014-02-26 |

| EP2464011A2 (en) | 2012-06-13 |

| CN102290098B (zh) | 2015-02-11 |

| CN1967719A (zh) | 2007-05-23 |

| CN1967719B (zh) | 2011-08-17 |

| US20070109899A1 (en) | 2007-05-17 |

| CN102290098A (zh) | 2011-12-21 |

| US7277351B2 (en) | 2007-10-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4425897B2 (ja) | 高電源レベルを有するプログラマブルロジックデバイスメモリ要素 | |

| US7411853B2 (en) | Volatile memory elements with elevated power supply levels for programmable logic device integrated circuits | |

| US7430148B2 (en) | Volatile memory elements with boosted output voltages for programmable logic device integrated circuits | |

| US8085063B2 (en) | Power regulator circuitry for programmable logic device memory elements | |

| US20190018063A1 (en) | Programmable integrated circuits with in-operation reconfiguration capability | |

| US8873278B1 (en) | Volatile memory elements with soft error upset immunity | |

| US20080169836A1 (en) | Configuration random access memory | |

| US7358764B1 (en) | Preset and reset circuitry for programmable logic device memory elements | |

| US7705659B1 (en) | Power regulator circuitry with power-on-reset control | |

| US7911826B1 (en) | Integrated circuits with clearable memory elements | |

| US8705300B1 (en) | Memory array circuitry with stability enhancement features | |

| US7839713B1 (en) | Reading and writing data to a memory cell in one clock cycle | |

| CN110189782B (zh) | 半导体器件 | |

| US9767892B1 (en) | Memory elements with dynamic pull-up weakening write assist circuitry | |

| CN110782925A (zh) | 电力供应控制 | |

| US9984734B2 (en) | Programmable integrated circuits with in-operation reconfiguration capability | |

| US7319619B1 (en) | Programmable logic device memory blocks with adjustable timing | |

| US7868605B1 (en) | Mixed mode power regulator circuitry for memory elements | |

| US8081503B1 (en) | Volatile memory elements with minimized area and leakage current |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091030 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20091030 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20091030 |

|

| TRDD | Decision of grant or rejection written | ||

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20091130 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20091202 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20091209 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4425897 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121218 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131218 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |