JP4425248B2 - 広帯域高周波スリップリング・システム - Google Patents

広帯域高周波スリップリング・システム Download PDFInfo

- Publication number

- JP4425248B2 JP4425248B2 JP2006206446A JP2006206446A JP4425248B2 JP 4425248 B2 JP4425248 B2 JP 4425248B2 JP 2006206446 A JP2006206446 A JP 2006206446A JP 2006206446 A JP2006206446 A JP 2006206446A JP 4425248 B2 JP4425248 B2 JP 4425248B2

- Authority

- JP

- Japan

- Prior art keywords

- ring

- slip ring

- dielectric material

- ground plane

- rings

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01R—ELECTRICALLY-CONDUCTIVE CONNECTIONS; STRUCTURAL ASSOCIATIONS OF A PLURALITY OF MUTUALLY-INSULATED ELECTRICAL CONNECTING ELEMENTS; COUPLING DEVICES; CURRENT COLLECTORS

- H01R39/00—Rotary current collectors, distributors or interrupters

- H01R39/02—Details for dynamo electric machines

- H01R39/08—Slip-rings

- H01R39/10—Slip-rings other than with external cylindrical contact surface, e.g. flat slip-rings

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01P—WAVEGUIDES; RESONATORS, LINES, OR OTHER DEVICES OF THE WAVEGUIDE TYPE

- H01P1/00—Auxiliary devices

- H01P1/06—Movable joints, e.g. rotating joints

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01R—ELECTRICALLY-CONDUCTIVE CONNECTIONS; STRUCTURAL ASSOCIATIONS OF A PLURALITY OF MUTUALLY-INSULATED ELECTRICAL CONNECTING ELEMENTS; COUPLING DEVICES; CURRENT COLLECTORS

- H01R39/00—Rotary current collectors, distributors or interrupters

- H01R39/02—Details for dynamo electric machines

- H01R39/18—Contacts for co-operation with commutator or slip-ring, e.g. contact brush

- H01R39/24—Laminated contacts; Wire contacts, e.g. metallic brush, carbon fibres

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01R—ELECTRICALLY-CONDUCTIVE CONNECTIONS; STRUCTURAL ASSOCIATIONS OF A PLURALITY OF MUTUALLY-INSULATED ELECTRICAL CONNECTING ELEMENTS; COUPLING DEVICES; CURRENT COLLECTORS

- H01R12/00—Structural associations of a plurality of mutually-insulated electrical connecting elements, specially adapted for printed circuits, e.g. printed circuit boards [PCB], flat or ribbon cables, or like generally planar structures, e.g. terminal strips, terminal blocks; Coupling devices specially adapted for printed circuits, flat or ribbon cables, or like generally planar structures; Terminals specially adapted for contact with, or insertion into, printed circuits, flat or ribbon cables, or like generally planar structures

- H01R12/50—Fixed connections

- H01R12/51—Fixed connections for rigid printed circuits or like structures

- H01R12/52—Fixed connections for rigid printed circuits or like structures connecting to other rigid printed circuits or like structures

- H01R12/523—Fixed connections for rigid printed circuits or like structures connecting to other rigid printed circuits or like structures by an interconnection through aligned holes in the boards or multilayer board

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01R—ELECTRICALLY-CONDUCTIVE CONNECTIONS; STRUCTURAL ASSOCIATIONS OF A PLURALITY OF MUTUALLY-INSULATED ELECTRICAL CONNECTING ELEMENTS; COUPLING DEVICES; CURRENT COLLECTORS

- H01R35/00—Flexible or turnable line connectors, i.e. the rotation angle being limited

- H01R35/02—Flexible line connectors without frictional contact members

- H01R35/025—Flexible line connectors without frictional contact members having a flexible conductor wound around a rotation axis

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01R—ELECTRICALLY-CONDUCTIVE CONNECTIONS; STRUCTURAL ASSOCIATIONS OF A PLURALITY OF MUTUALLY-INSULATED ELECTRICAL CONNECTING ELEMENTS; COUPLING DEVICES; CURRENT COLLECTORS

- H01R39/00—Rotary current collectors, distributors or interrupters

- H01R39/02—Details for dynamo electric machines

- H01R39/08—Slip-rings

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01R—ELECTRICALLY-CONDUCTIVE CONNECTIONS; STRUCTURAL ASSOCIATIONS OF A PLURALITY OF MUTUALLY-INSULATED ELECTRICAL CONNECTING ELEMENTS; COUPLING DEVICES; CURRENT COLLECTORS

- H01R39/00—Rotary current collectors, distributors or interrupters

- H01R39/64—Devices for uninterrupted current collection

Description

一般に、フラット形状ブラシ接点を利用することは、高周波スリップリングに関しては、丸線接点や他の接点形状と比較して大きなメリットがある。これらには、表皮効果の低減(表面積が大きくなるほど、高周波損失が低減される傾向がある)、インダクタンスの低減(断面がフラットなので、インダクタンス及び高周波損失が低減される傾向がある)、サージ・インピーダンスの低減(スリップリング差動インピーダンスとの親和性が高くなる)、コンプライアンスの増大(ばねレートの低下)(スリップリング・プラッタの軸方向の心振れに対して耐性がある)、表面実装PCB技術との親和性、横剛性が高い(フラット・リング・システム上でブラシを正確に走らせることが可能)などのメリットがある。

フラットなインターデジット式ブラシ接点システムを有する広帯域スリップリング・プラッタを実装するシステムは、一般には多層PCB技術を利用して実装されるが、他の技術も利用可能である。高周波性能を向上させるには、低誘電率の基材を使用したり、マイクロストリップ、ストリップライン、平面内導波路、及び同様の技術を利用して、インピーダンスを制御された伝送線を使用したりする。さらに、電磁放射及び妨害感受性、並びにコモンモード干渉を制御する視点からは、平衡差動伝送線を用いることが重要な手段になる。マイクロストリップ、ストリップライン、及び他のマイクロ波構造技術はさらに、高周波デジタル・シグナリングに必要な広い帯域幅に不可欠の要素である、伝送線構造物の正確なインピーダンス制御を推進する。個々の実装は、所望のインピーダンス及び帯域幅の要件に第1に依存する。

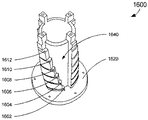

図16及び17は、複数のスリップリング・プラッタ・アセンブリ100を受け止める回転シャフト1600を示している。回転シャフト1600は、スリップリングの構築を容易にしながら、これらの装置の製造で直面する3つの典型的な問題に対処するよう有利に設計される。シャフトは、プラッタの軸方向の位置決めを、公差が蓄積されないように制御すること、プラッタ・スリップリングの半径方向の位置決めを制御すること、及びワイヤとリードを管理することを考慮して設計されている。スリップリング・プラッタを回転シャフトに取り付ける際の難題は、スリップリング取り付け方法の多く(例えば、スペーサを用いる方法)につきものの交差の蓄積を避けることである。また、プラッタを追加するたびにワイヤの輻輳が増えるので、ワイヤ及びリードの管理も、ほとんどのスリップリングの製造に必ずついてまわる問題である。図16に明示するように、回転シャフト1600は、上述の問題に対処する何段かのステップを含む。

従来の構造又はプリント回路基板(PCB)構造のいずれにおいても、プラッタ式のスリップリング全体に差動信号を伝送するためには、伝送線を構成する2つ以上の導体の異なるリング半径(2つの場合は、図18のR1及びR2)の問題に対処することが必要になる可能性がある。一般的なプラッタ式スリップリングでは、リングごとに半径が異なる導電リングが実装される。したがって、結果として得られるリング・ペアの各リングは、異なる物理的円周を有し、したがって、同じでない2つの経路長で構成される伝送線を形成する。リングの物理的な長さが異なれば、それらのリングの電気的な長さも異なり、結果として、リングによって搬送される差動信号は、リング周囲を伝搬する間に位相がずれる。そのように構築された伝送線は、差動平衡の劣化、伝送線からの輻射の増加、コモンモード信号の脆弱性の増加、ジッタの増加、及びデジタル・データ・レートの低下を含む、多くの電気的不利益をこうむる。

スリップリングを実装する際の信号の保全性の問題については、インピーダンス不連続点からの反射を制御するために、受動部品を用いてスリップリングの伝送線を終端することが必要になる可能性がある。それらの終端装置をPCBの構造に組み込むために、PCBスリップリング構築手法を用いることも可能である。これには、様々な手法があり、例えば、PC基板S/Rの表面又は内部にLCRネットワーク用表面実装部品、埋め込み受動(LCR)部品を実装すること、及び/又はPCB基材を用いてLCRネットワークを作成するストリップライン手法などがある。

102 PCBスリップリング・プラッタ

104 フレキシブル回路

106A リング

106B リング

200 フラット・ブラシ接点

202 ブラシ

204 ブラシ

206 PCB

208 中央はと目又はバイア

210 接地面

212 給電線

700 多層PCB

702 フラット・ブラシ接点(中央給電ブラシ構造物)

704 フラット・ブラシ接点(中央給電ブラシ構造物)

705 マイクロチップ構造物

710 接地面

712 埋め込みマイクロストリップ

714 逃げ領域

800 接触構造物

802 「クロス給電」伝送線

804 「クロス給電」伝送線

806 整相線

810 整相線

900 漸変インピーダンス伝送線

902 パターン

904 パターン

1002 クロス給電線

1004 クロス給電線

1006 0度整相線

1010 0度整相線

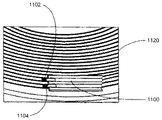

1100 マイクロストリップ接点

1102 接点

1104 接点

1120 スリップリング・プラッタ

1300 スリップリング・プラッタ

1302A 導電リング

1302B 導電リング

1304 PCB誘電材料

1306A 埋め込みマイクロストリップ

1306B 埋め込みマイクロストリップ

1310 接地面

1320 凹形障壁

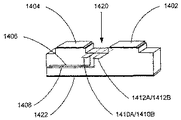

1400 給電システム

1401 点

1402 リング

1403 点

1404 リング

1406 クロス給電伝送線

1408 クロス給電伝送線

1410A 整相線

1410B 整相線

1412A 整相線

1412B 整相線

1600 回転シャフト

1602 取り付けランド/パッド

1604 取り付けランド/パッド

1606 取り付けランド/パッド

1608 取り付けランド/パッド

1610 取り付けランド/パッド

1612 取り付けランド/パッド

1640 ワイヤ・ウェイ

1650 配線

1660 キャビティ

1670 外形

1800 差動プラッタ・スリップリング

1801 回転軸

1802 接地面

1804 誘電体

1806 追加接地面

1808 内側リング

1810 外側リング

1812 溝

1900 平面内導波路

1901 回転軸

1902 接地面

1906 内側リング

1908 中間リング

1910 外側リング

1912 溝

1912A 溝

1912B 溝

2000 シングルエンデッド・スリップリング

2002 抵抗ネットワーク

2004 抵抗ネットワーク

2006 抵抗

2008 抵抗

2100 差動スリップリング

2101 抵抗ネットワーク

2104 抵抗ネットワーク

2200 スリップリング

2202 PCB

2204 バイア

2206 シャント素子

2300 スリップリング

2302 PCB

2304 パターン

2306 埋め込み受動部品

Claims (16)

- 第1の側と第2の側とを有する第1の誘電材料と、

前記第1の誘電材料の前記第1の側に配置された、内側リングと外側リングとを含む、複数の同軸配置導電リングと、

前記第1の誘電材料の前記第2の側に配置された第1の接地面とを備え、前記内側リングの幅が前記外側リングの幅より大きく、

前記内側リングと前記第1の接地面との間の前記第1の誘電材料の中に形成される第2の接地面を備え、前記第2の接地面が前記内側リングの信号伝搬速度を下げ、

前記内側リング及び外側リングの電気的な長さがほぼ等しくなるように、前記内側リング及び外側リングの幅が選択される接触リング・システム。 - 前記外側リングの信号伝搬速度を上げるために、前記外側リングの少なくとも一方の側の前記第1の誘電材料に溝が形成される、請求項1に記載のシステム。

- 前記内側リング及び外側リングが伝送線の差動ペアを提供する、請求項1に記載のシステム。

- 前記内側リング及び外側リングの厚さが異なる、請求項1に記載のシステム。

- 前記内側リング及び外側リングの表面仕上げが異なる、請求項4に記載のシステム。

- 前記内側リング及び外側リングが非差動の伝送線を提供する、請求項1に記載のシステム。

- 前記非差動の伝送線が平面内導波路である、請求項6に記載のシステム。

- インピーダンス不連続に起因する反射を減らすために配置された複数の終端装置をさらに備える、請求項1に記載のシステム。

- 前記終端装置がバイア内に位置決めされる、請求項8に記載のシステム。

- 前記終端装置が、表面実装部品、埋め込み受動部品、又はストリップライン手法により作成された部品のうちの少なくともいずれかである、請求項8に記載のシステム。

- 前記終端装置が埋め込み受動部品であり、前記埋め込み受動部品が薄膜部品である、請求項10に記載のシステム。

- 第1の側と第2の側とを有する第1の誘電材料と、

前記第1の誘電材料の前記第1の側に配置された、内側リングと外側リングとを含む、複数の同軸配置導電リングと、

前記第1の誘電材料の前記第2の側に配置された第1の接地面とを備え、前記外側リングの信号伝搬速度を上げるために、前記外側リングの少なくとも一方の側の前記第1の誘電材料に溝が形成され、

前記内側リングと第1の接地面との間の前記第1の誘電材料の中に形成される第2の接地面を備え、前記第2の接地面が前記内側リングの信号伝搬速度を下げる接触リング・システム。 - インピーダンス不連続に起因する反射を減らすために配置された複数の終端装置をさらに備える、請求項12に記載のシステム。

- 前記終端装置が、表面実装部品、埋め込み受動部品、又はストリップライン手法により作成された部品のうちの少なくともいずれかである、請求項12に記載のシステム。

- 前記内側リングの幅が前記外側リングの幅より大きく、前記内側リング及び外側リングの電気的な長さがほぼ等しくなるように、前記内側リング及び外側リングの幅が選択される、請求項12に記載のシステム。

- 前記内側リング及び外側リングの厚さが異なり、前記内側リング及び外側リングの表面仕上げが異なる、請求項12に記載のシステム。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/192,910 US7142071B2 (en) | 2003-02-19 | 2005-07-29 | Broadband high-frequency slip-ring system |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007042643A JP2007042643A (ja) | 2007-02-15 |

| JP2007042643A5 JP2007042643A5 (ja) | 2007-05-17 |

| JP4425248B2 true JP4425248B2 (ja) | 2010-03-03 |

Family

ID=37310857

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006206446A Expired - Fee Related JP4425248B2 (ja) | 2005-07-29 | 2006-07-28 | 広帯域高周波スリップリング・システム |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US7142071B2 (ja) |

| EP (1) | EP1748523B1 (ja) |

| JP (1) | JP4425248B2 (ja) |

| AT (1) | ATE448587T1 (ja) |

| CA (1) | CA2552338C (ja) |

| DE (1) | DE602006010275D1 (ja) |

| DK (1) | DK1748523T3 (ja) |

| ES (1) | ES2334055T3 (ja) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB2493977A (en) * | 2011-08-26 | 2013-02-27 | Overview Ltd | Slip ring apparatus |

| CN102542170B (zh) * | 2012-01-16 | 2015-05-13 | 烟台磐能电气控制系统有限公司 | 一种得到电力系统频率滑差的方法 |

| US9306353B2 (en) | 2013-05-29 | 2016-04-05 | Moog Inc. | Integrated rotary joint assembly with internal temperature-affecting element |

| WO2015094802A1 (en) | 2013-12-17 | 2015-06-25 | Moog Inc. | High-speed data link with planar near-field probe |

| JP5792367B1 (ja) * | 2014-08-08 | 2015-10-14 | 京楽産業.株式会社 | 遊技機 |

| US9240660B1 (en) | 2014-11-18 | 2016-01-19 | General Electric Company | Slip ring assembly and method for impedance matching high frequency signals across the slip ring assembly |

| US9528891B2 (en) | 2014-11-25 | 2016-12-27 | Hamilton Sundstrand Corporation | Slip ring containment band |

| US9735530B2 (en) * | 2015-03-10 | 2017-08-15 | General Electric Company | Apparatus and method for axially spacing conductive rings of a slip ring assembly |

| ITUB20152201A1 (it) * | 2015-07-15 | 2017-01-15 | Conductix Wampfler S R L | COLLETTORE ELETTRICO ROTANTE AD ALBERO CAVO PER ETHERNET FINO A UN Gbps |

| US9894767B1 (en) | 2016-03-20 | 2018-02-13 | Jason Krugman Products, LLC | Concentric circle printed circuit board electrical connection |

| SE543303C2 (en) | 2016-06-21 | 2020-11-24 | Universal Instruments Corp | Sliptrack architecture for an assembly machine, system and method |

| KR102542594B1 (ko) * | 2016-12-16 | 2023-06-14 | 삼성전자 주식회사 | 다층 인쇄 회로 기판 및 이를 포함하는 전자 장치 |

| EP3963659B1 (en) | 2019-05-28 | 2023-09-27 | Moog Inc. | Graduated frequency response non-contacting slip ring probe |

| WO2021262984A1 (en) | 2020-06-25 | 2021-12-30 | Blate Alex | Reconfigurable interconnection node |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3382387A (en) * | 1968-05-07 | Gen Electric | Electrical current collection and delivery method and apparatus | |

| US5805115A (en) * | 1995-08-01 | 1998-09-08 | Kevlin Corporation | Rotary microwave antenna system |

| DE10219958A1 (de) * | 2002-05-03 | 2003-12-04 | Schleifring Und Appbau Gmbh | Vorrichtung zur elektrischen Verbindung zweier gegeneinander beweglicher Einheiten |

| US6956445B2 (en) | 2003-02-19 | 2005-10-18 | Electro-Tec Corp. | Broadband high-frequency slip ring system |

-

2005

- 2005-07-29 US US11/192,910 patent/US7142071B2/en not_active Expired - Fee Related

-

2006

- 2006-07-14 CA CA2552338A patent/CA2552338C/en not_active Expired - Fee Related

- 2006-07-20 ES ES06253823T patent/ES2334055T3/es active Active

- 2006-07-20 AT AT06253823T patent/ATE448587T1/de active

- 2006-07-20 EP EP06253823A patent/EP1748523B1/en not_active Not-in-force

- 2006-07-20 DK DK06253823.6T patent/DK1748523T3/da active

- 2006-07-20 DE DE602006010275T patent/DE602006010275D1/de active Active

- 2006-07-28 JP JP2006206446A patent/JP4425248B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| ES2334055T3 (es) | 2010-03-04 |

| CA2552338A1 (en) | 2007-01-29 |

| JP2007042643A (ja) | 2007-02-15 |

| US7142071B2 (en) | 2006-11-28 |

| CA2552338C (en) | 2012-09-04 |

| EP1748523B1 (en) | 2009-11-11 |

| ATE448587T1 (de) | 2009-11-15 |

| EP1748523A2 (en) | 2007-01-31 |

| US20050258915A1 (en) | 2005-11-24 |

| EP1748523A3 (en) | 2008-04-09 |

| DE602006010275D1 (de) | 2009-12-24 |

| DK1748523T3 (da) | 2010-03-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4425248B2 (ja) | 広帯域高周波スリップリング・システム | |

| JP4874380B2 (ja) | 広帯域高周波スリップリングシステム | |

| JP5003359B2 (ja) | プリント配線基板 | |

| US20090133906A1 (en) | Flexible printed circuit board and manufacturing method thereof | |

| JP5153869B2 (ja) | 高周波ドラム型スリップリング・モジュール | |

| WO2014003087A1 (ja) | 高周波伝送線路および電子機器 | |

| CN111834728A (zh) | 共面波导电路宽带不等分一分二功分器 | |

| KR101577370B1 (ko) | 마이크로웨이브 필터 | |

| KR20050087802A (ko) | 차동 신호를 태핑하는 회로 | |

| JP4203005B2 (ja) | コモンモードチョークコイル | |

| JP2018181987A (ja) | 多層配線基板 | |

| JP2005018627A (ja) | データ転送回路基板 | |

| JP2005012559A (ja) | カプラ及びカプラアレー | |

| Board | Analog, RF and EMC Considerations |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070322 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070322 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090424 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090508 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20090810 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20090813 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20091110 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20091208 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4425248 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121218 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121218 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131218 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |