JP4414751B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP4414751B2 JP4414751B2 JP2003434841A JP2003434841A JP4414751B2 JP 4414751 B2 JP4414751 B2 JP 4414751B2 JP 2003434841 A JP2003434841 A JP 2003434841A JP 2003434841 A JP2003434841 A JP 2003434841A JP 4414751 B2 JP4414751 B2 JP 4414751B2

- Authority

- JP

- Japan

- Prior art keywords

- lead frame

- semiconductor device

- conductive wire

- semiconductor element

- pair

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H10W72/536—

-

- H10W72/5363—

-

- H10W74/00—

-

- H10W90/756—

Landscapes

- Lead Frames For Integrated Circuits (AREA)

Description

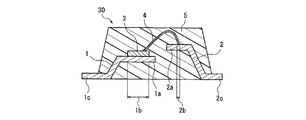

本発明にかかる半導体装置は、前記一対のリードフレームにおける少なくとも一方のリードフレームの封止体内方端の形状が、前記半導体素子主面に垂直な方向から見て、R形状またはテーパー形状である。従来技術におけるリードフレーム内方端の形状は、当該リードフレームに搭載された半導体素子主面に垂直な方向から見て、直線形状であった。これにより、本発明によるリードフレームの方が、対向する面積を従来技術と比較して、小さくすることができるため、不要輻射を低減することができる。ここで言う内方端とは、リードフレームの両端のうち、封止体に内包されている方の端部を示す。さらに、外方端とは、リードフレームの両端のうち、封止体に内包されていない方の端部を示し、外部回路接続端子の機能を有する。

(実施の形態1)

本発明の一実施形態にかかる半導体装置について説明する。

(実施の形態2)

本発明の第2の実施形態にかかる半導体装置について説明する。

(実施の形態3)

本発明の第3の実施形態にかかる半導体装置について、以下に説明する。なお、本実施形態にかかる半導体装置は、平面図における構成が実施の形態1と同様であるため、図1(a)を用いて説明する。

1a、2a 内方端

1b 半導体素子搭載部

2b 導電性ワイヤ接続部

1c、2c 外方端

1d、2d 幅広部

1e、2e 段差部

3 半導体素子

4 導電性ワイヤ

5 封止体

101、102 リードフレーム

101c、102c 外部回路接続端子

103 半導体素子

104 半導体素子搭載部

105 半導体素子搭載面

106 導電性ワイヤ

107 導電性ワイヤ接続部

108 導電性ワイヤ接続面

109 封止体

110 半導体装置

Claims (5)

- 対向する一対のリードフレームと、

前記一対のリードフレームを覆う封止体と、

前記一対のリードフレームの一方に搭載される半導体素子と、

前記一対のリードフレームの他方に接続され、前記半導体素子の電極に接続される導電性ワイヤとを備え、

前記一対のリードフレームの他方の幅が、少なくとも前記導電性ワイヤが接続された部分において、前記リードフレームの幅方向における前記導電性ワイヤの断面の長さである前記導電性ワイヤの断面の幅と略同一であることを特徴とする半導体装置。 - 前記一対のリードフレームにおける少なくとも一方のリードフレームの封止体内方端の形状が、前記半導体素子主面に垂直な方向から見て、R形状またはテーパー形状である請求項1に記載の半導体装置。

- 前記一対のリードフレームの一方の幅が、少なくとも前記半導体素子が搭載された部分において、前記半導体素子の幅と略同一である、請求項1または2に記載の半導体装置。

- 前記一対のリードフレームの一方において前記半導体素子が搭載された部分と、前記一対のリードフレームの他方において前記導電性ワイヤが接続された部分との高さが異なる、請求項1〜3のいずれかに記載の半導体装置。

- 前記一対のリードフレームのうち、少なくとも一方のリードフレームが、前記封止体内に、内方端幅および外方端幅よりも幅の広い幅広部を有する、請求項1〜4のいずれかに記載の半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003434841A JP4414751B2 (ja) | 2003-12-26 | 2003-12-26 | 半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003434841A JP4414751B2 (ja) | 2003-12-26 | 2003-12-26 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005197270A JP2005197270A (ja) | 2005-07-21 |

| JP4414751B2 true JP4414751B2 (ja) | 2010-02-10 |

Family

ID=34815149

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003434841A Expired - Fee Related JP4414751B2 (ja) | 2003-12-26 | 2003-12-26 | 半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4414751B2 (ja) |

-

2003

- 2003-12-26 JP JP2003434841A patent/JP4414751B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005197270A (ja) | 2005-07-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6700189B2 (en) | Resin sealed semiconductor device | |

| US8637976B2 (en) | Semiconductor device with lead terminals having portions thereof extending obliquely | |

| US20010033008A1 (en) | Lead frame for fabricating surface mount type semiconductor devices with high reliability | |

| US8952518B2 (en) | Semiconductor device housing package, and semiconductor apparatus and electronic apparatus including the same | |

| US11742279B2 (en) | Semiconductor device | |

| US5661628A (en) | Fused surface mounting type solid electrolytic capacitor | |

| KR102145167B1 (ko) | 반도체 장치 | |

| US6717260B2 (en) | Clip-type lead frame for source mounted die | |

| KR100612165B1 (ko) | 전원 회로 장치 | |

| JP4414751B2 (ja) | 半導体装置 | |

| JP4737664B2 (ja) | 面実装型固体電解コンデンサとその製造方法 | |

| JP2007294884A (ja) | 半導体装置 | |

| CN112640099B (zh) | 功率半导体装置 | |

| JP4067472B2 (ja) | 電子部品用パッケージ | |

| EP1519643A2 (en) | Integrated circuit socket contact | |

| JP7650147B2 (ja) | 半導体装置及び接続部材 | |

| JP4849802B2 (ja) | 半導体装置 | |

| JP2003017628A (ja) | 樹脂封止型半導体装置 | |

| WO2023100754A1 (ja) | 半導体装置 | |

| JP4759314B2 (ja) | 固体撮像装置の製造方法および固体撮像装置 | |

| KR100253298B1 (ko) | 솔더조인트신뢰성이개선된반도체패키지및그를이용한디바이스 | |

| JP2025149011A (ja) | 半導体装置 | |

| JP2023183440A (ja) | 磁気センサ装置 | |

| JP2005032753A (ja) | チップ部品 | |

| CN120998906A (zh) | 半导体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060116 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080725 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080729 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080924 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090709 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090831 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20091029 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20091120 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121127 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |