JP4352664B2 - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP4352664B2 JP4352664B2 JP2002233756A JP2002233756A JP4352664B2 JP 4352664 B2 JP4352664 B2 JP 4352664B2 JP 2002233756 A JP2002233756 A JP 2002233756A JP 2002233756 A JP2002233756 A JP 2002233756A JP 4352664 B2 JP4352664 B2 JP 4352664B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- semiconductor chip

- solid

- state

- peripheral circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 141

- 238000004519 manufacturing process Methods 0.000 title claims description 16

- 239000000758 substrate Substances 0.000 claims description 87

- 238000003384 imaging method Methods 0.000 claims description 71

- 230000002093 peripheral effect Effects 0.000 claims description 58

- 230000015572 biosynthetic process Effects 0.000 claims description 35

- 238000000034 method Methods 0.000 claims description 22

- 238000005452 bending Methods 0.000 claims description 20

- 238000006243 chemical reaction Methods 0.000 claims description 9

- 238000012545 processing Methods 0.000 claims description 4

- 238000012544 monitoring process Methods 0.000 claims description 2

- 230000007246 mechanism Effects 0.000 description 10

- 230000008569 process Effects 0.000 description 5

- 238000001444 catalytic combustion detection Methods 0.000 description 4

- 238000005304 joining Methods 0.000 description 4

- 230000004075 alteration Effects 0.000 description 3

- 238000013461 design Methods 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 239000011521 glass Substances 0.000 description 3

- 239000000463 material Substances 0.000 description 3

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 239000000428 dust Substances 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- 239000011347 resin Substances 0.000 description 2

- 229920005989 resin Polymers 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 239000007787 solid Substances 0.000 description 2

- 238000012546 transfer Methods 0.000 description 2

- 230000009466 transformation Effects 0.000 description 2

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 230000002542 deteriorative effect Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- 230000001771 impaired effect Effects 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 230000013011 mating Effects 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000002265 prevention Effects 0.000 description 1

- 230000002787 reinforcement Effects 0.000 description 1

- 239000005394 sealing glass Substances 0.000 description 1

Images

Landscapes

- Solid State Image Pick-Up Elements (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

Description

【発明の属する技術分野】

本発明は、例えばCCDやCMOSセンサ等の固体撮像素子を高密度に実装したカメラモジュール等に用いられる半導体装置に関し、特に薄型で周辺ボケの少ない固体撮像装置を実現することができる半導体装置及びその製造方法に関する。

【0002】

【従来の技術】

従来より、例えばCCDイメージセンサやCMOSイメージセンサといった固体撮像装置において、同一基板上に固体撮像素子形成領域と周辺回路領域を設けたものが提供されている。

一般的に、このような固体撮像装置の結像光学系に関しては、像面湾曲と呼ばれるレンズの収差が発生するという問題がある。

図10は、このような像面湾曲の発生原理を説明するための図であり、固体撮像素子1と結像光学系2との配置状態を示している。

図示のように、固体撮像素子1の中心部で合焦点位置をAに合わせても、撮像素子1の周辺部では像面湾曲の影響により焦点位置がBとなるため、焦点ずれが発生してしまう。

その結果、画像の中心部と周辺部とで画質が不均一になるなど、撮像特性の劣化が発生していた。

【0003】

さらに具体的には、撮像素子1の中心部Aがジャストフォーカスになるようにレンズマウントを行うと、撮像素子1の周辺部Bの画像はピンボケした画像になる。このため、レンズマウントの手法として、中心のフォーカスを若干デフォーカスさせて、周辺の解像度を高めるようなレンズマウントを行う。

しかし、この場合、画像の全体的な解像度は比較的改善できるが、中心から周辺までをジャストフォーカスにすることは、レンズの持つ収差の影響により不可能であった。

この他にも、カメラモジュールの厚みを薄くしたいという要求に対して、カメラモジュールを薄型化するほどレンズ設計が困難になるという問題もあった。

【0004】

そこで、従来より、上述のような像面湾曲の問題を解決し、レンズユニットを簡略化する目的で、例えば特開平10−108078号、特開2001−156278号、及び特開2001−284564号等に開示されるように、固体撮像素子を構成する半導体チップ全体を湾曲実装する技術が提案されている。

【0005】

【発明が解決しようとする課題】

しかしながら、上記従来の湾曲実装技術では、半導体チップ全体を湾曲させて実装するため、半導体チップ上の全ての半導体回路素子について、シリコン基板結晶に表面歪応力がかかることになる。このため、例えば、像面湾曲の問題とは無関係な周辺回路領域についても表面歪応力が作用し、それによる基板表面の接合リークが生じ、周辺回路の信頼性を劣化させるという問題がある。

また、従来のように半導体チップを一律に湾曲させることは、高密度実装の点でも不利である。

さらに、半導体チップを外部回路と接続する電極パッド領域にも湾曲が生じることになり、半導体チップと外部回路とを接続するフリップチップ実装やワイヤボンディング等の工程を複雑化するという問題がある。

【0006】

そこで本発明の目的は、固体撮像素子に対する像面湾曲の問題を解決し、かつ、周辺部分にかかる歪応力を軽減でき、解像度の改善やレンズユニットの簡略化を達成できる半導体装置及びその製造方法を提供することにある。

【0007】

【課題を解決するための手段】

本発明は前記目的を達成するため、複数の光電変換素子により被写体の撮像を行う固体撮像素子形成領域と、周辺回路領域とを同一基板上に形成した半導体チップを有し、前記半導体チップの固体撮像素子形成領域は湾曲されて形成され、前記周辺回路領域が平坦に形成されていることを特徴とする。

また本発明は、複数の光電変換素子により被写体の撮像を行う固体撮像素子形成領域と、前記固体撮像素子形成領域の各素子と外部回路とを接続するための電極パッド領域とを同一基板上に形成した半導体チップを有し、前記半導体チップの固体撮像素子形成領域が所定の曲率で湾曲されて形成され、前記電極パッド領域が平坦に形成されていることを特徴とする。

【0008】

また本発明は、複数の光電変換素子により被写体の撮像を行う固体撮像素子形成領域と、周辺回路領域及び/又は電極パッド領域とを同一基板上に形成した半導体チップを有し、前記半導体チップの固体撮像素子形成領域が湾曲されて形成され、前記周辺回路領域及び/又は電極パッド領域が平坦に形成されている半導体装置の製造方法であって、前記半導体装置は前記半導体チップを実装する実装用基板を有し、前記実装用基板は、本体基板と、前記本体基板に対しスライド自在に保持されたスライド基板から構成されており、前記実装用基板と前記半導体チップの周辺回路領域を、前記周辺回路領域を平坦に保持した状態で接合するステップと、前記スライド基板又は前記本体基板に応力を付与することにより、前記半導体チップの基板面方向に応力を付与して、前記固体撮像素子形成領域を湾曲させるステップとを有することを特徴とする。

【0009】

本発明の半導体装置及びその製造方法では、半導体チップに設けられる固体撮像素子形成領域だけを所定の曲率に湾曲させて形成し、その他の周辺回路領域や電極パッド領域は平坦に形成したことから、固体撮像素子形成領域については像面湾曲の問題を解決し、周辺部分にかかる歪応力を軽減でき、接合リークの問題を解決し、かつ電極パッドによる接続性を改善でき、撮像装置における解像度の改善やレンズユニットの簡略化を達成することができる。

【0010】

【発明の実施の形態】

以下、本発明による半導体装置及びその製造方法の実施の形態例について説明する。

本実施の形態例は、固体撮像素子形成領域と周辺回路領域や電極パッド領域とを同一半導体チップ上に形成した半導体装置において、固体撮像素子形成領域だけを湾曲して形成し、周辺回路領域や電極パッド領域を平坦に形成したものである。

具体的には、固体撮像素子や周辺回路等を形成したSiウェーハに裏面研削を行い、所定の厚さに薄型化する。その後、ダイシングを行い、個々の半導体チップに分割し、これを実装用基板に実装する。この際、実装用基板には、固体撮像素子形成領域を外部からの力によって湾曲させるスライド機構(応力付与手段)を設けることにより、このスライド機構によって半導体チップに応力を付与して湾曲させ、その湾曲率を可変調整した状態で、所定の位置にて固定する。

また、スライド機構は、固体撮像素子形成領域だけを湾曲させる構造とし、固体撮像素子形成領域の外側の周辺回路領域や電極パッド領域は、平坦なままの状態で固体撮像素子形成領域だけを湾曲させるようにする。

これにより、周辺回路領域における接合リーク等をなくし、信頼性を向上できるとともに、平坦な電極パッド部によってフリップチップ実装やワイヤボンディング等の作業を簡略化することができる。

【0011】

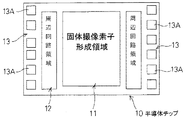

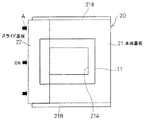

図1〜図3は、本発明の第1の実施の形態例による半導体装置を搭載したカメラモジュールの構成例を示す図であり、図1はカメラモジュールの各構成要素の組み付け状態を示す断面図、図2はカメラモジュールに搭載される半導体チップの各素子配置を示す平面図、図3はカメラモジュールに設けられる実装用基板とそのスライド機構を示す平面図である。

図1に示すように、本例のカメラモジュールは、半導体チップ10、実装用基板20、及びレンズユニット30で構成されている。

半導体チップ10は、図2に示すように、全体が長方形の薄板状に形成され、中央部に固体撮像素子形成領域11が形成され、その両側に周辺回路領域12が形成され、さらにその外側に電極パッド領域13が形成されている。

【0012】

固体撮像素子形成領域11には、CCD型センサである場合には、フォトダイオード(光電変換素子)を2次元配列で配置した単位画素や垂直、水平の各転送レジスタ等が設けられている。また、CMOS型センサの場合には、フォトダイオード及び各種画素トランジスタによって構成される2次元配列の単位画素や各種信号線等が設けられている。

また、周辺回路領域12は、固体撮像素子形成領域11の駆動回路や信号処理回路、さらには各種のバスライン等が設けられている。

さらに、電極パッド領域13は、半導体チップ10と外部回路とを接続するための複数の電極パッド13Aが配置されている。

なお、半導体チップ10は、デジタル信号処理回路を含むワンチップでデジタル出力が可能な機能を有するものを用いても良いし、または、信号処理回路を独立させて、センサ出力機能のみを有するものを用いても良い。

【0013】

実装用基板20は、Auバンプ14及びアンダーフィル材15を介して半導体チップ10を実装するものであり、図3に示すように、本体基板21及びスライド基板22より構成される。

本体基板21は、固体撮像素子形成領域11の受光面に対応する開口部21Aを有するとともに、この本体基板21の両側部には、スライド基板22をスライド自在に取り付けるためのスライドレール部21Bが設けられている。

スライド基板22は、スライドレール部21Bによってスライド自在に保持され、図3に示す矢印A方向にスライドするものである。

【0014】

この実装用基板20には、図示しない回路配線パターンが形成されており、この回路配線パターンに半導体チップ10の電極パッド13AがAuバンプ14を介して接続されている。また、電極パッド13AのAuバンプ14による接合部分には、アンダーフィル材15が充填され、接合状態が補強されている。

そして、この接合状態で、半導体チップ10の固体撮像素子形成領域11の受光面は、実装用基板20の開口部21Aに臨み、この開口部21Aを通してレンズユニット30からの光を受光する。

なお、開口部21Aには、シールガラス23が装着され、塵芥等の進入を防止している。

また、半導体チップ10は、カメラモジュールが組み立てられた状態で、図1に示すように、固体撮像素子形成領域11だけが湾曲した状態で固定され、周辺回路領域12及び電極パッド領域13は平坦な状態に保持され、さらに図1では省略するモールド樹脂によって包囲されている。なお、このような湾曲形状を得る方法については後述する。

【0015】

また、レンズユニット30は、実装用基板20の上面に装着されるものであり、固定絞り31を設けた鏡筒32にレンズ33を設けたものである。なお、鏡筒32は、一体物であっても、ネジ式でレンズ部が可動するような機構を持たせたものであっても良い。

このようなカメラモジュールでは、固定絞り31及びレンズ33を通して入射した光が、半導体チップ10の固体撮像素子形成領域11に受光され、この固体撮像素子形成領域11によって画像信号に変換され、周辺回路領域12及び電極パッド領域13を経て実装基板側の回路に伝送される。

【0016】

次に、以上のようなカメラモジュールの組み立て工程と各要素の具体例について説明する。

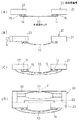

図4は本実施の形態例によるカメラモジュールの組み立て工程を示す断面図である。

まず、図4(A)に示すように、実装用基板20に対する半導体チップ10のフリップチップ実装を行う。この際、半導体チップ10は湾曲させるために、厚さ50μmまで薄くする。なお、半導体チップ10の厚みの範囲としては、例えば20μmから70μmまでの範囲が望ましい。

このフリップチップ実装工程において、実装用基板20にAuバンプ14を形成し、超音波接合により実装用基板20と半導体チップ10を接合する。なお、ここでの実装方法としては、例えばAgペーストによる接合、異方性導電膜による接合等、別の方法であっても良い。

続いて、バンプ接合箇所にアンダーフィル材15を充填し、接合強度を補強する。

【0017】

次に、図4(B)に示すように、実装用基板20の本体基板21とスライド基板22のいずれか一方(図4ではスライド基板22側より)から力を加えて固体撮像素子形成領域11を下方に突出する方向に湾曲させる。この際、実装用基板20を電気的に画出し用ボードに接続し、測定用のモニタ上で出力画像を見ながら画面の中心及び4隅の解像度が最大となるような位置にスライド基板22を瞬間接着材等で固定する。

なお、ここで、解像度を確認する代わりに、所定のピッチで白黒の縦線を描いたパターンを撮像し、そのMTF(Modulation Transfer Function)を確認しながらフォーカス調整を行ってもよい。

【0018】

次に、図4(C)に示すように、半導体チップ10の補強としてモールド樹脂16を図示のように塗布形成する。

次に、固体撮像素子形成領域11等に付着した浮遊ゴミなどを除去するための洗浄を行い、シールガラス23を実装用基板20に接合し、固体撮像素子形成領域11を封止する。シールガラス23は赤外線カットフィルタ機能を持たせることもできる。また、例えば回折格子による色偽防止機構をもたせることも可能である。

次に、図4(D)に示すように、レンズユニット30を実装用基板20に固定する。

【0019】

以上のような工程により、湾曲した固体撮像素子形成領域を有する半導体装置が完成する。

なお、本実施の形態においては、スライド機構を有する実装用基板20の位置調整により、固体撮像素子形成領域の受光面の曲率を任意に変更することが可能であり、各種のレンズに適用することが可能である。

そして、固体撮像素子形成領域のみを湾曲させることにより、微小リークが問題となる周辺回路領域においては歪応力のない平坦なシリコン基板を用いることができ、回路の信頼性を向上できる。

さらに、パッド領域は、平坦な基板面を用いることにより、フリップチップ実装そのものに従来と同様の手法を流用でき、製造作業の簡略化を得ることが可能である。つまり、半導体チップをフリップチップ実装する相手側の基板を高精度な湾曲面にするような必要がなく、煩雑化を避けることができる。

これはワイヤボンディングにおいても同様な効果が得られる。つまり、従来と同様な平坦なチップ部分に対してワイヤボンディングをすれば良く、不安定な湾曲面に対してワイヤボンディングする必要はないという利点がある。

【0020】

図5は、本発明の第2の実施の形態例による半導体装置を搭載したカメラモジュールの構成例を示す図であり、カメラモジュールに設けられる実装用基板とそのスライド機構を示す平面図である。なお、半導体チップ及びレンズユニットの構成については第1の実施の形態例と共通であるため、図面は省略し、同一符号を用いて説明する。

本例は、半導体チップ10の両側からスライド基板をスライドさせて湾曲実装する場合の構成例である。すなわち、本例の実装基板40には、本体基板41に図中の左右両側から半導体チップ10を押圧する一対のスライド基板42、43が実装基板40の上下両側に設けられたスライドレール部41Bによってスライド自在に設けられている。

そして、半導体チップ10を湾曲実装する場合には、両側のスライド基板42、43を矢印A、B方向にスライドし、半導体チップ10の固体撮像素子形成領域11を所望の曲率で湾曲させる。

なお、本体基板41に形成した開口部41Aは、上述した開口部21Aと同様である。

また、カメラモジュールの組み立て製造工程は、半導体チップの湾曲方法を除いて図4に示した第1の実施の形態例と同様であるので、ここでは省略する。

【0021】

次に、以上のような第1、第2の実施の形態例において、半導体チップ10の固体撮像素子形成領域11のみを湾曲させる方法について説明する。

まず、第1の方法としては、半導体チップ10の周辺回路領域12及びパッド領域13を実装用基板20または実装用基板40に強固に接合して補強し、その平坦性が損なわれないようにした状態で、スライド基板22またはスライド基板42、43を移動することにより、固体撮像素子形成領域11のみを湾曲させることができる。

この際、半導体チップ10の周辺回路領域12及びパッド領域13と実装用基板20、40との接合強度、及び半導体チップ10の板厚を適宜選択することにより、容易に所望の湾曲状態を得ることが可能となる。

【0022】

また、第2の方法として、湾曲型による吸着実装を行うことが可能である。

図6は、この場合の湾曲型と実装作業の具体例を示す断面図である。

図示のように、湾曲型50には、半導体チップ10の固体撮像素子形成領域11の湾曲形状に対応する円弧状の凹部51と、周辺回路領域12及びパッド領域13を平坦に保持するための平坦部52が形成されるとともに、半導体チップ10を真空吸着するための複数の吸着孔53が凹部51から平坦部52にわたって分散して形成されている。

このような湾曲型50では、凹部51及び平坦部52を半導体チップ10に宛がった状態で、吸着孔53によって真空吸着を行い、固体撮像素子形成領域11だけを所望の湾曲形状に湾曲させることができる。

なお、この際の湾曲変形に同期して上述したスライド基板22または42、43をスライドさせ、半導体チップ10の変形に追従することが可能となる。

また、湾曲後の固定等の作業は上述した通りであるので説明は省略する。

【0023】

図7及び図8は、本発明の第3の実施の形態例による半導体装置を搭載したカメラモジュールの構成例を示す図であり、図7はカメラモジュールの各構成要素の組み付け状態を示す断面図、図8はカメラモジュールに搭載される半導体チップの各素子配置を示す平面図である。

本例の半導体チップ60は、中央部に固体撮像素子形成領域61が設けられているが、その側部にパッド領域62が設けられ、さらにその外側に周辺回路領域63が設けられている。

そして、本例では、半導体チップ60の周辺回路領域63を設けた外縁部分64を裏面方向に90°折り曲げることにより、幅方向に縮小したモジュールを構成するものである。なお、半導体チップ60の折り曲げられた部分自体は平坦であることから、周辺回路領域63での表面歪応力は小さいものとなり、接合リークの問題は生じない。

なお、その他の実装用基板及びレンズユニットについては、寸法上の変更はあるものの、基本的原理は上述した第1、第2の実施の形態例と同様であるので同一符号を付して説明は省略する。

【0024】

また、図9は、上述した第3の実施の形態例による半導体チップを湾曲実装する場合の湾曲型と実装作業の具体例を示す断面図である。

図示のように、湾曲型70には、半導体チップ60の固体撮像素子形成領域61の湾曲形状に対応する円弧状の凹部71と、パッド領域62を受けるエッジ部72と、周辺回路領域63を90°折れ曲がった状態で平坦に保持するための垂直平坦部73とを有する。

そして、凹部71及び垂直平坦部73には、半導体チップ10を真空吸着するための複数の吸着孔74が分散して形成されている。

このような湾曲型70により、半導体チップ60の固体撮像素子形成領域61を円弧状に吸着湾曲するとともに、周辺回路領域63を90°折り曲がった状態に整形し、図7に示すようなカメラモジュールを得ることができる。

なお、周辺回路領域63の90°折り曲げ加工は、真空吸着だけでなく、予め機械的に曲げるような処理で実現することもできる。また、湾曲型の具体的形状等は、図示のものに限らず、種々変形が可能である。

例えば、湾曲型の形状は半円筒状又は球面状のいずれであってもよく、また、湾曲面は一定の曲率をもった理想曲面でなくてもよい。

【0025】

以上説明したように、本発明の各実施の形態例によれば、固体撮像素子の受光面をレンズの像面湾曲収差を吸収するように湾曲させることができ、薄型で、かつ、画面の全領域に渡ってフォーカスが合った固体撮像素子を搭載した半導体装置を得ることができる。

また、固体撮像素子形成領域の湾曲率は、出力画像をモニタしながら調整することが可能であり、固体差の少ない、精度の高い工法が実現できる。

また、設計の異なるレンズに最適な湾曲位置で固体撮像素子を実装することも可能であり、レンズ設計に依存しない精密な固体撮像素子を製造することができる。

また、半導体チップの一部を折り曲げた状態でカメラモジュールに組み込むことも可能であり、固体撮像素子ならびにカメラモジュールの小型化に貢献することができる。

【0026】

なお、以上の実施の形態例では、同一チップ上に固体撮像素子形成領域、周辺回路領域、及びパッド領域を設けた場合について説明したが、同一チップ上に固体撮像素子形成領域と周辺回路領域、あるいは同一チップ上に固体撮像素子形成領域とパッド領域を設けた素子構成のものについても同様に適用し得るものである。

また、本発明に適用する撮像素子としては、CCD型やCMOS型等の各種の形態のものに適用できるものである。

【0027】

【発明の効果】

以上説明したように本発明の半導体装置及びその製造方法によれば、半導体チップに設けられる固体撮像素子形成領域だけを所定の曲率に湾曲させて形成し、その他の周辺回路領域や電極パッド領域は平坦に形成したことから、固体撮像素子形成領域については像面湾曲の問題を解決し、周辺部分にかかる歪応力を軽減でき、接合リークの問題を解決し、かつ電極パッドによる接続性を改善でき、撮像装置における解像度の改善やレンズユニットの簡略化を達成できる効果がある。

【図面の簡単な説明】

【図1】 本発明の第1の実施の形態例による半導体装置を搭載したカメラモジュールの各構成要素の組み付け状態を示す断面図である。

【図2】 図1に示すカメラモジュールに搭載される半導体チップの各素子配置を示す平面図である。

【図3】 図1に示すカメラモジュールに設けられる実装用基板とそのスライド機構を示す平面図である。

【図4】 図1に示すカメラモジュールの組み立て工程を示す断面図である。

【図5】 本発明の第2の実施の形態例による半導体装置を搭載したカメラモジュールに設けられる実装用基板とそのスライド機構を示す平面図である。

【図6】 図1及び図5に示す半導体チップに用いる湾曲型と実装作業の具体例を示す断面図である。

【図7】 本発明の第3の実施の形態例による半導体装置を搭載したカメラモジュールの各構成要素の組み付け状態を示す断面図である。

【図8】 図7に示すカメラモジュールに搭載される半導体チップの各素子配置を示す平面図である。

【図9】 図7に示す半導体チップに用いる湾曲型と実装作業の具体例を示す断面図である。

【図10】 従来の固体撮像装置において生じる像面湾曲の発生原理を説明する側面図である。

【符号の説明】

10……半導体チップ、11……固体撮像素子形成領域、12……周辺回路領域、13……電極パッド領域、20……実装用基板、21……本体基板、21A……開口部、21B……スライドレール部、22……スライド基板、23……シールガラス、30……レンズユニット、31……固定絞り、32……鏡筒、33……レンズ。

Claims (15)

- 複数の光電変換素子により被写体の撮像を行う固体撮像素子形成領域と、周辺回路領域とを同一基板上に形成した半導体チップを有し、

前記半導体チップの固体撮像素子形成領域は湾曲されて形成され、前記周辺回路領域が平坦に形成されている、

ことを特徴とする半導体装置。 - 前記周辺回路領域は前記固体撮像素子形成領域の各素子の駆動回路又は信号処理回路の少なくとも一方を含むことを特徴とする請求項1記載の半導体装置。

- 前記半導体チップは、前記固体撮像素子形成領域と同一基板上に形成され該固体撮像素子形成領域の各素子と外部回路とを接続するための電極パッド領域を有し、前記半導体チップの電極パッド領域は平坦に形成されていることを特徴とする請求項1記載の半導体装置。

- 前記半導体チップを実装する実装用基板を有し、

前記実装用基板は、本体基板と、前記本体基板に対しスライド自在に保持されたスライド基板から構成され、

前記実装用基板と前記半導体チップの周辺回路領域は、前記周辺回路領域を平坦に保持した状態で接合されており、

前記スライド基板をスライドさせることにより、前記半導体チップの基板面方向に応力を付与して、前記固体撮像素子形成領域を湾曲させた状態で、前記固体撮像素子形成領域が固定されていることを特徴とする請求項1記載の半導体装置。 - 前記半導体チップを実装する実装用基板を有し、

前記実装用基板は、本体基板と、前記本体基板に対しスライド自在に保持されたスライド基板から構成され、

前記実装用基板と前記半導体チップの周辺回路領域及び電極パッド領域は、前記周辺回路領域及び電極パッド領域を平坦に保持した状態で接合されており、

前記スライド基板をスライドさせることにより、前記半導体チップの基板面方向に応力を付与して、前記固体撮像素子形成領域を湾曲させた状態で、前記固体撮像素子形成領域が固定されていることを特徴とする請求項3記載の半導体装置。 - 前記半導体チップの周辺回路領域を設けた部分が、前記固体撮像素子形成領域を設けた部分に対して半導体チップの裏面方向に折れ曲がっていることを特徴とする請求項1記載の半導体装置。

- 複数の光電変換素子により被写体の撮像を行う固体撮像素子形成領域と、前記固体撮像素子形成領域の各素子と外部回路とを接続するための電極パッド領域とを同一基板上に形成した半導体チップを有し、

前記半導体チップの固体撮像素子形成領域が所定の曲率で湾曲されて形成され、前記電極パッド領域が平坦に形成されている、

ことを特徴とする半導体装置。 - 前記半導体チップを実装する実装用基板を有し、

前記実装用基板は、本体基板と、前記本体基板に対しスライド自在に保持されたスライド基板から構成され、

前記実装用基板と前記半導体チップの電極パッド領域は、前記電極パッド領域を平坦に保持した状態で接合されており、

前記スライド基板をスライドさせることにより、前記半導体チップの基板面方向に応力を付与して、前記固体撮像素子形成領域を湾曲させた状態で、前記固体撮像素子形成領域が固定されていることを特徴とする請求項3記載の半導体装置。 - 前記半導体チップが前記電極パッド領域を介して前記実装用基板に設けられた回路配線に接続されていることを特徴とする請求項5又は請求項8記載の半導体装置。

- 複数の光電変換素子により被写体の撮像を行う固体撮像素子形成領域と、周辺回路領域及び/又は電極パッド領域とを同一基板上に形成した半導体チップを有し、前記半導体チップの固体撮像素子形成領域が湾曲されて形成され、前記周辺回路領域及び/又は電極パッド領域が平坦に形成されている半導体装置の製造方法であって、

前記半導体装置は前記半導体チップを実装する実装用基板を有し、

前記実装用基板は、本体基板と、前記本体基板に対しスライド自在に保持されたスライド基板から構成されており、

前記実装用基板と前記半導体チップの周辺回路領域を、前記周辺回路領域を平坦に保持した状態で接合するステップと、

前記スライド基板又は前記本体基板に応力を付与することにより、前記半導体チップの基板面方向に応力を付与して、前記固体撮像素子形成領域を湾曲させるステップと、

を有することを特徴とする半導体装置製造方法。 - 前記半導体チップを固体撮像素子形成領域が湾曲し、前記周辺回路領域が平坦である状態で前記スライド基板を固定するステップと、

を有することを特徴とする請求項10記載の半導体装置製造方法。 - 複数の光電変換素子により被写体の撮像を行う固体撮像素子形成領域と、周辺回路領域及び/又は電極パッド領域とを同一基板上に形成した半導体チップを有し、前記半導体チップの固体撮像素子形成領域が湾曲されて形成され、前記周辺回路領域及び/又は電極パッド領域が平坦に形成されている半導体装置の製造方法であって、

前記半導体チップの固体撮像素子形成領域の湾曲形状に対応する円弧状の凹部と周辺回路領域及び/又は電極パッド領域を平坦に保持するための平坦部と、前記凹部と前記平坦部に複数の吸着孔を有する湾曲型に半導体チップを宛がった状態で前記吸着孔によって真空吸着を行うステップと、

を有することを特徴とする半導体装置製造方法。 - 前記半導体装置は前記半導体チップを実装する実装用基板を有し、

前記実装用基板は、本体基板と、前記本体基板に対しスライド自在に保持されたスライド基板から構成されており、

前記半導体チップを固体撮像素子形成領域が湾曲し、前記周辺回路領域が平坦である状態で前記スライド基板を固定するステップと、

を有することを特徴とする請求項12記載の半導体装置製造方法。 - 複数の光電変換素子により被写体の撮像を行う固体撮像素子形成領域と、周辺回路領域と電極パッド領域とを同一基板上に形成した半導体チップを有し、前記半導体チップの固体撮像素子形成領域が湾曲されて形成され、前記電極パッド領域が平坦に形成され、前記周辺回路領域を設けた部分が前記固体撮像素子形成領域を設けた部分に対して半導体チップの裏面方向に折れ曲がっている半導体装置の製造方法であって、

前記半導体チップの固体撮像素子形成領域の湾曲形状に対応する円弧状の凹部と電極パッド領域を受けるエッジ部と、前記周辺回路領域を保持する平坦部と、前記凹部と前記エッジ部と前記平坦部に複数の吸着孔を有する湾曲型に半導体チップを宛がった状態で前記吸着孔によって真空吸着を行うステップと、

を有することを特徴とする半導体装置製造方法。 - 前記固体撮像素子領域の湾曲率を、前記半導体装置の出力画像をモニタしながら調整し、解像度が最大となる位置で、前記半導体チップを固定するステップと、

を有することを特徴とする請求項10又は12又は14記載の半導体装置製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002233756A JP4352664B2 (ja) | 2002-08-09 | 2002-08-09 | 半導体装置及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002233756A JP4352664B2 (ja) | 2002-08-09 | 2002-08-09 | 半導体装置及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004079578A JP2004079578A (ja) | 2004-03-11 |

| JP2004079578A5 JP2004079578A5 (ja) | 2005-10-20 |

| JP4352664B2 true JP4352664B2 (ja) | 2009-10-28 |

Family

ID=32018805

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002233756A Expired - Fee Related JP4352664B2 (ja) | 2002-08-09 | 2002-08-09 | 半導体装置及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4352664B2 (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4806957B2 (ja) * | 2005-05-12 | 2011-11-02 | コニカミノルタオプト株式会社 | 撮像装置 |

| JP4969237B2 (ja) * | 2006-12-25 | 2012-07-04 | パナソニック株式会社 | 固体撮像装置とその製造方法 |

| JP5676171B2 (ja) * | 2010-07-26 | 2015-02-25 | シャープ株式会社 | 固体撮像装置およびその製造方法、並びに電子機器 |

| JP5724322B2 (ja) * | 2010-11-24 | 2015-05-27 | ソニー株式会社 | 固体撮像装置の製造方法 |

| US8878116B2 (en) * | 2011-02-28 | 2014-11-04 | Sony Corporation | Method of manufacturing solid-state imaging element, solid-state imaging element and electronic apparatus |

| JP5720304B2 (ja) * | 2011-02-28 | 2015-05-20 | ソニー株式会社 | 固体撮像装置及び電子機器 |

| JP5720305B2 (ja) * | 2011-02-28 | 2015-05-20 | ソニー株式会社 | 固体撮像素子の製造方法、固体撮像素子、および電子機器 |

| JP5720306B2 (ja) * | 2011-02-28 | 2015-05-20 | ソニー株式会社 | 固体撮像素子の製造方法 |

| JP6491519B2 (ja) * | 2015-04-02 | 2019-03-27 | キヤノン株式会社 | 撮像素子及び撮像装置 |

-

2002

- 2002-08-09 JP JP2002233756A patent/JP4352664B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2004079578A (ja) | 2004-03-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5724322B2 (ja) | 固体撮像装置の製造方法 | |

| EP1081944B1 (en) | Imaging element, imaging device, camera module and camera system | |

| JP5676171B2 (ja) | 固体撮像装置およびその製造方法、並びに電子機器 | |

| JP4310348B2 (ja) | 固体撮像装置およびそれを備えた電子機器 | |

| JP5709435B2 (ja) | 撮像モジュール及びカメラ | |

| EP1443754A2 (en) | Camera module and manufacturing method thereof | |

| CN1842137A (zh) | 光学装置模块及光学装置模块的制造方法 | |

| JP4352664B2 (ja) | 半導体装置及びその製造方法 | |

| JP2014154643A (ja) | 積層型固体撮像装置および撮像装置 | |

| KR100673643B1 (ko) | 카메라모듈 패키지 및 그 제조방법 | |

| JP2011018747A (ja) | 撮像ユニット | |

| JP4641578B2 (ja) | 光学モジュール、撮像装置及びカメラシステム | |

| JP4720120B2 (ja) | 半導体イメージセンサ・モジュール | |

| JP7513634B2 (ja) | 撮像装置および撮像装置の製造方法 | |

| JP3896586B2 (ja) | 固体撮像装置及び固体撮像カメラ | |

| JP2005064060A (ja) | 固体撮像素子、固体撮像素子の製造方法及び固体撮像装置 | |

| JP2004146633A (ja) | 固体撮像装置及びその製造方法 | |

| JP2011066092A (ja) | 撮像ユニット | |

| US20090001493A1 (en) | Electronic imaging device | |

| JP4737311B2 (ja) | 光学モジュールとその製造方法、撮像装置とその製造方法、及びカメラシステムとその製造方法 | |

| JP3959711B2 (ja) | 固体撮像装置及びその製造方法 | |

| WO2015122299A1 (ja) | 固体撮像装置、電子機器、および固体撮像装置の製造方法 | |

| US20050205898A1 (en) | Electronic imaging device | |

| JPH09199701A (ja) | 固体撮像装置 | |

| JP2011066093A (ja) | 撮像ユニット |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050629 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050629 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080201 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20081209 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090206 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090707 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090720 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120807 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130807 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |