JP4308279B2 - 高周波用電圧制御発振回路 - Google Patents

高周波用電圧制御発振回路 Download PDFInfo

- Publication number

- JP4308279B2 JP4308279B2 JP2007055892A JP2007055892A JP4308279B2 JP 4308279 B2 JP4308279 B2 JP 4308279B2 JP 2007055892 A JP2007055892 A JP 2007055892A JP 2007055892 A JP2007055892 A JP 2007055892A JP 4308279 B2 JP4308279 B2 JP 4308279B2

- Authority

- JP

- Japan

- Prior art keywords

- reactance element

- circuit

- pass filter

- oscillation

- low

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 230000010355 oscillation Effects 0.000 title claims description 95

- 230000001939 inductive effect Effects 0.000 claims description 41

- 230000010363 phase shift Effects 0.000 claims description 17

- 235000012489 doughnuts Nutrition 0.000 claims description 8

- 238000010586 diagram Methods 0.000 description 14

- 238000001228 spectrum Methods 0.000 description 9

- 230000002159 abnormal effect Effects 0.000 description 7

- 230000000694 effects Effects 0.000 description 4

- 230000002238 attenuated effect Effects 0.000 description 3

- 230000005540 biological transmission Effects 0.000 description 3

- 230000002542 deteriorative effect Effects 0.000 description 3

- 239000003990 capacitor Substances 0.000 description 2

- 238000005549 size reduction Methods 0.000 description 2

- 239000000758 substrate Substances 0.000 description 2

- 230000006698 induction Effects 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

Images

Landscapes

- Inductance-Capacitance Distribution Constants And Capacitance-Resistance Oscillators (AREA)

Description

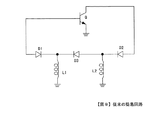

従来の高周波用電圧制御発振回路は、図9に示すように、発振用増幅回路のトランジスタQのコレクタとベースを帰還ループで接続し、当該帰還ループに可変容量のダイオードD2 、D3 、D1 が直列に接続され、ダイオードD1 とダイオードD3 との間の点が誘導性リアクタンス素子であるコイルL1 の一方に端子に接続し、他方の端子が接地し、ダイオードD2 とダイオードD3 との間の点が誘導性リアクタンス素子であるコイルL2 の一方に端子に接続し、他方の端子が接地されている。

ここで、ダイオードD3 とコイルL1 ,L2 で3次のπ型可変ハイパスフィルタ(HPF:High Pass Filter)を形成している。

発振周波数は、図10においては、700MHzとなっており、そのため、移相回路がハイパスフィルタの場合、700MHz以上の周波数において発振ループゲインが0dB以上となって、発振周波数以上の周波数において意図しない発振が発生することが懸念される。

図11において、横軸の「1」は所望の発振周波数、「2」以降は高次高調波の次数を示しており、図11、図12から、高次高調波のレベルが所望の発振周波数に対して近いものがあることが確認できる。

特許文献3には、振幅変調器において、インダクタL1 ,L2 ,L3 、キャパシタC2 、可変容量ダイオードVDからなる低域通過フィルタを構成したものが記載されている。

特許文献5は、広帯域化高周波電力増幅回路において、直列インピーダンス機能インダクタンスとしてマイクロストリップラインを使用し、当該直列インピーダンス機能インダクタンスをコの字形のパターンに形成することが記載されている。

本発明の実施の形態について図面を参照しながら説明する。

本発明は、高周波用電圧制御発振回路において、発振用増幅回路の帰還ループに移相回路として、3次以上の奇数のπ型ローパスフィルタと、その入出力に直列に接続された容量性可変リアクタンス素子とで構成し、ローパスフィルタは帰還ループに直列に接続する誘導性リアクタンス素子と、その誘導性リアクタンス素子の入出力に並列に接続された容量性可変リアクタンス素子とで構成したものであり、ローパスフィルタの容量性可変リアクタンス素子の容量を制御することで利用する周波数を選択でき、更に帰還ループに直列に接続する容量性可変リアクタンス素子の容量を制御することで低い周波数のゲインを減衰させて、バンドパスフィルタのような特性にでき、異常発振を抑制し、位相雑音を改善できると共に、簡易な構成で調整が容易な回路を実現できるものである。

本発明の実施の形態における要点は、第1に、目的の発振周波数以外の周波数にて発振条件を満足させないこと、第2に、発振周波数以上の周波数における発振ループゲインを低下させることにより、発振ループ上に発生する高次高調波を低減させ、所望の発振周波数への雑音付加量を低減させることによる。

但し、通常のバンドパスフィルタでは、ローパスフィルタに比べて素子数が増え、同調が難しいため、本発明の実施の形態では、バンドパスフィルタを3次のπ型可変ローパスフィルタと、当該ローパスフィルタの入出力に直列に接続する容量性可変リアクタンス素子とから構成する移相回路としたものである。これにより、通常のバンドパスフィルタに比べて素子数を少なくし、コスト減及び小型化を実現している。

次に、本発明の実施の形態に係る高周波用電圧制御発振回路について図1を参照しながら説明する。図1は、本発明の実施の形態に係る高周波用電圧制御発振回路の簡易回路を示す構成図である。

本発明の実施の形態に係る高周波用電圧制御発振回路(本回路)は、図1に示すように、発振用増幅回路のトランジスタQと、3次のπ型可変ローパスフィルタと、当該ローパスフィルタの入出力に直列に接続された容量性可変リアクタンス素子とから基本的に構成されている。

尚、3次のπ型ローパスフィルタと、当該ローパスフィルタの入出力に直列に接続された容量性可変リアクタンス素子によって可変バンドパスフィルタ特性を実現するものとなる。

3次のπ型可変ローパスフィルタは、帰還ループに設けられ、直列に接続された誘導性リアクタンス素子のコイルL3 と、そのコイルL3 の両端に並列に容量性可変リアクタンス素子のダイオードD4 、D5 が接続されている。

尚、ダイオードD4 、D5 のカソード側がコイルL3 の両端に接続し、ダイオードD4 、D5 のアノード側が接地している。

図1では、ローパスフィルタを3次のπ型可変ローパスフィルタとしたが、3次以上の奇数次のπ型可変ローパスフィルタであってもよい。

ダイオードD1 は、アノード側をトランジスタQのベースに接続し、カソード側をローパスフィルタに接続している。

トランジスタQのコレクタとローパスフィルタとの間には容量性可変リアクタンス素子のダイオードD2 が直列に接続している。

ダイオードD2 は、アノード側をトランジスタQのコレクタに接続し、カソード側をローパスフィルタに接続している。

次に、本回路における発振スペクトラムを図2に示し、その発振スペクトラムのレベルを従来(図12)と比較して図3に示している。図2は、本回路の発振ループ内の発振スペクトラムを示す図であり、図3は、本回路の高調波成分のレベルを示す図である。

図2において、横軸の「1」は所望の発振周波数、「2」以降は高次高調波の次数を示しており、図2、図3から、従来技術と比較して、本回路は、明らかに高次高調波のレベルが低くなっており、歪み率が140%(従来)から21%に改善されている。

これにより、高次高調波同士のミキシングによって発生する雑音成分が発振周波数の信号に付加されにくくなり、従来よりも良好な位相雑音特性を実現できる。

次に、本回路の具体的回路について図4を参照しながら説明する。図4は、本回路の具体的回路の構成図である。

本回路の具体的回路は、図4に示すように、発振用増幅回路(Amplifier)1と、バッファ増幅回路(Amplifier)2と、出力整合部(LPF)3と、発振用増幅回路1の出力をその入力に帰還させる帰還ループの途中に設けられた誘導性リアクタンス素子(TLIN)4と、帰還ループにおいて発振用増幅回路1の出力側と誘導性リアクタンス素子4の入力側との間に設けられた容量性可変リアクタンス素子5と、帰還ループにおいて誘導性リアクタンス素子4の出力側と発振用増幅回路1の入力側との間に設けられた容量性可変リアクタンス素子6と、誘導性リアクタンス素子4の入力側と出力側の両端に設けられた容量性可変リアクタンス素子7,8とを備えている。

容量性可変リアクタンス素子5〜8は、バリキャップのダイオードで構成されている。

容量性可変リアクタンス素子5のダイオードのアノードが発振用増幅回路1の出力側に接続し、カソードが誘導性リアクタンス素子4の入力側に接続している。

容量性可変リアクタンス素子6のダイオードのアノードが発振用増幅回路1の入力側に接続し、カソードが誘導性リアクタンス素子4の出力側に接続している。

容量性可変リアクタンス素子7,8のダイオードのアノードが接地され、カソードが誘導性リアクタンス素子4の入出力側に接続している。

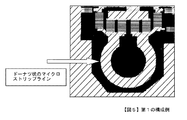

次に、誘導性リアクタンス素子4の具体的な第1、第2の構成例(第1,2の構成例)について図5、図6を参照しながら説明する。図5は、誘導性リアクタンス素子の第1の構成例を示す図であり、図6は、誘導性リアクタンス素子の第2の構成例を示す図である。

誘導性リアクタンス素子4の第1の構成例は、図5に示すように、マイクロストリップラインとしてドーナッツ形としており、誘導性リアクタンス素子4の第2の構成例は、図6に示すように、マイクロストリップラインとして45度のベント処理されたコの字形としている。

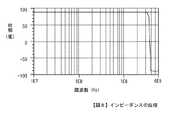

次に、マイクロストリップラインの特性について図7、図8を参照しながら説明する。図7は、上記第1,2の構成例に示したマイクロストリップラインの代表的なインピーダンスの大きさを示した図であり、図8は、上記第1,2の構成例に示したマイクロストリップラインの代表的なインピーダンスの位相を示した図である。図7において、横軸は周波数、縦軸はインピーダンスの大きさ、図8において、横軸は周波数、縦軸が位相を表している。

図7及び図8に示す実線が本回路におけるインピーダンス特性を示しており、点線は理想的なインダクタのインピーダンス特性を示している。

本回路において、マイクロストリップラインは発振周波数において等価的にインダクタとして機能しているのが特徴となっている。

本回路によれば、発振用増幅回路の帰還ループに移相回路として、3次以上の奇数のπ型ローパスフィルタと、その入出力に直列に接続された容量性可変リアクタンス素子とで構成し、ローパスフィルタは帰還ループに直列に接続する誘導性リアクタンス素子と、その誘導性リアクタンス素子の入出力に並列に接続された容量性可変リアクタンス素子とで構成したものとしているので、ローパスフィルタの容量性可変リアクタンス素子の容量を制御することで利用する周波数を選択でき、更に帰還ループに直列に接続する容量性可変リアクタンス素子の容量を制御することで低い周波数のゲインを減衰させて、バンドパスフィルタのような特性にでき、異常発振を抑制し、位相雑音を改善できると共に、簡易な構成で調整が容易な回路を実現できる効果がある。

Claims (5)

- 発振用増幅回路を備える高周波用電圧制御発振回路において、

前記発振用増幅回路の帰還ループに、3次以上の奇数のπ型ローパスフィルタと、当該ローパスフィルタの出力側に直列に接続された容量性可変リアクタンス素子の第1のダイオードと当該ローパスフィルタの入力側に直列に接続された容量性可変リアクタンス素子の第2のダイオードとを有する移相回路を設け、

前記ローパスフィルタは、前記帰還ループに直列に接続する誘導性リアクタンス素子のコイルと、当該誘導性リアクタンス素子の出力側に並列に接続された容量性可変リアクタンス素子の第4のダイオードと当該誘導性リアクタンス素子の入力側に並列に接続された容量性可変リアクタンス素子の第5のダイオードとを備えることを特徴とする高周波用電圧制御発振回路。 - 移相回路における容量性可変リアクタンス素子をバリキャップとしたことを特徴とする請求項1記載の高周波用電圧制御発振回路。

- ローパスフィルタにおける容量性可変リアクタンス素子をバリキャップとしたことを特徴とする請求項1記載の高周波用電圧制御発振回路。

- ローパスフィルタにおける誘導性リアクタンス素子をマイクロストリップラインで形成したことを特徴とする請求項1乃至3のいずれか記載の高周波用電圧制御発振回路。

- マイクロストリップラインの形状を、馬蹄形状、ドーナッツ形状、45度のベント処理されたコの字形状としたことを特徴とする請求項4記載の高周波用電圧制御発振回路。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007055892A JP4308279B2 (ja) | 2007-03-06 | 2007-03-06 | 高周波用電圧制御発振回路 |

| CN2008800062250A CN101622783B (zh) | 2007-03-06 | 2008-02-25 | 高频用电压控制振荡电路 |

| EP08720826.0A EP2120333B1 (en) | 2007-03-06 | 2008-02-25 | High-frequency voltage-controlled oscillation circuit |

| PCT/JP2008/053173 WO2008108201A1 (ja) | 2007-03-06 | 2008-02-25 | 高周波用電圧制御発振回路 |

| US12/585,092 US7956698B2 (en) | 2007-03-06 | 2009-09-03 | High-frequency voltage-controlled oscillation circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007055892A JP4308279B2 (ja) | 2007-03-06 | 2007-03-06 | 高周波用電圧制御発振回路 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008219609A JP2008219609A (ja) | 2008-09-18 |

| JP2008219609A5 JP2008219609A5 (ja) | 2009-05-07 |

| JP4308279B2 true JP4308279B2 (ja) | 2009-08-05 |

Family

ID=39839094

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007055892A Active JP4308279B2 (ja) | 2007-03-06 | 2007-03-06 | 高周波用電圧制御発振回路 |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JP4308279B2 (ja) |

| CN (1) | CN101622783B (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP2798665A4 (en) * | 2011-12-27 | 2015-07-01 | Dh Technologies Dev Pte Ltd | HIGH VOLTAGE POWER SUPPLY FILTER |

| CN107947752A (zh) * | 2017-12-29 | 2018-04-20 | 中国电子科技集团公司第四十三研究所 | 一种带通滤波器 |

| CN111934621B (zh) * | 2020-09-25 | 2020-12-22 | 成都信息工程大学 | 一种适用于小负载情况的振荡器 |

| CN112953393B (zh) * | 2021-04-09 | 2023-09-29 | 东南大学 | 一种低相位噪声的宽带压控振荡器 |

Family Cites Families (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7315217B2 (en) * | 2005-03-18 | 2008-01-01 | Avago Technologies General Ip (Singapore) Pte Ltd. | Linear phase-locked loop with dual tuning elements |

-

2007

- 2007-03-06 JP JP2007055892A patent/JP4308279B2/ja active Active

-

2008

- 2008-02-25 CN CN2008800062250A patent/CN101622783B/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2008219609A (ja) | 2008-09-18 |

| CN101622783B (zh) | 2011-12-07 |

| CN101622783A (zh) | 2010-01-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN106664059B (zh) | 谐振器电路 | |

| JP4308279B2 (ja) | 高周波用電圧制御発振回路 | |

| US7956698B2 (en) | High-frequency voltage-controlled oscillation circuit | |

| KR100457939B1 (ko) | 고주파 수정발진기 | |

| JP4825860B2 (ja) | 低雑音電圧制御発振器 | |

| KR20030088349A (ko) | 발진기 | |

| CN115051650B (zh) | S波段倍频带低相噪的压控振荡器及信号发生装置 | |

| JP4356900B2 (ja) | 高周波用電圧制御発振回路 | |

| JP2020205576A (ja) | 電力増幅回路 | |

| US20100085131A1 (en) | Filter circuit and voltage-controlled oscillating circuit | |

| CN111819788B (zh) | 放大器 | |

| JP2008141655A (ja) | 可変同調回路及びテレビジョンチューナ | |

| JPH052001B2 (ja) | ||

| CN111416575A (zh) | 一种基于同轴介质谐振腔的振荡器及设计方法 | |

| JP2013098795A (ja) | 発振器 | |

| JP2006197056A (ja) | 高周波増幅回路およびそれを用いた無線送信機器 | |

| US7170355B2 (en) | Voltage-controlled oscillator using current feedback network | |

| KR100447743B1 (ko) | 복수의 공진기를 포함하는 전압제어 발진 장치 | |

| JP6601710B2 (ja) | 発振装置 | |

| JP6232220B2 (ja) | 発振回路の調整方法 | |

| CN217508714U (zh) | 一种倍频带低相噪的压控振荡器及信号发生装置 | |

| US11677367B2 (en) | Power amplifier circuit | |

| KR100498989B1 (ko) | 고주파 초크 | |

| JP2013090214A (ja) | 電圧制御発振器 | |

| JP2005039596A (ja) | 集積化発振回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090319 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090319 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20090319 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090430 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20090424 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090430 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4308279 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120515 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120515 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120515 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130515 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130515 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140515 Year of fee payment: 5 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |