JP4245437B2 - 不揮発性半導体記憶装置の書き込み方法 - Google Patents

不揮発性半導体記憶装置の書き込み方法 Download PDFInfo

- Publication number

- JP4245437B2 JP4245437B2 JP2003289838A JP2003289838A JP4245437B2 JP 4245437 B2 JP4245437 B2 JP 4245437B2 JP 2003289838 A JP2003289838 A JP 2003289838A JP 2003289838 A JP2003289838 A JP 2003289838A JP 4245437 B2 JP4245437 B2 JP 4245437B2

- Authority

- JP

- Japan

- Prior art keywords

- write

- writing

- voltage

- memory cell

- memory cells

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0408—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors

- G11C16/0441—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors comprising cells containing multiple floating gate devices, e.g. separate read-and-write FAMOS transistors with connected floating gates

- G11C16/0458—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors comprising cells containing multiple floating gate devices, e.g. separate read-and-write FAMOS transistors with connected floating gates comprising two or more independent floating gates which store independent data

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

- G11C11/5628—Programming or writing circuits; Data input circuits

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Read Only Memory (AREA)

Description

"A Double−Level−Vth Select Gate Array Architecture for Multilevel NAND Flash Memories" IEEE Journal Of Solid−State Circuits, Vol.31, No.4, 1996年4月 "A 117−mm2 3.3−V Only 128−Mb Multilevel NAND Flash Memory for Mass Storage Applications" IEEE Journal Of Solid−State Circuits, Vol.31, No.11, 1996年11月 "40−mm2 3−V−Only 50−MHz 64−Mb 2−b/Cell CHE NOR Flash Memory"IEEE Journal Of Solid−State Circuits, Vol.35, No.11, 2000年11月

図1は、本発明装置10の一実施の形態の機能的な概略構成を示すブロック構成図である。尚、図1では、複数のアドレス入力信号(図中ADD)、複数のデータ入力信号(図中DI)、複数の制御信号(図中CTRL)等の入力回路、複数のデータ出力信号(図中DO)等の出力回路、及び、アドレス入力信号のデコーダ回路等の周辺回路の詳細は、公知のフラッシュメモリ等の不揮発性半導体記憶装置と同様であるため、その記載を省略してある。図1は、専ら、本発明装置10のメインメモリアレイ11(以下、単にメモリアレイ11と称す。)の書き込み動作に関係する回路部分を中心に記載してある。

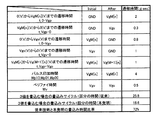

次に、書き込み対象メモリセルが同一ワード線上に複数有り、目的の記憶状態(閾値電圧)が異なる場合について、第1実施形態の説明の中で若干言及したが、図3を用いて詳細に説明する。以下の説明では、記憶状態“10”に書き込むメモリセルの集合をA0、記憶状態“01”に書き込むメモリセルの集合をB0、記憶状態“00”に書き込むメモリセルの集合をC0とする。尚、第2実施形態に係る本発明方法は、第1実施形態と同様に図1及び図2に示す本発明装置10で実行される。

次に、書き込み対象メモリセルが同一ワード線上に複数有り、目的の記憶状態(閾値電圧)が異なる場合の別実施形態について、図8のフローチャートを用いて説明する。ここで、第2実施形態と同様に、記憶状態“10”に書き込むメモリセルの集合をA0、記憶状態“01”に書き込むメモリセルの集合をB0、記憶状態“00”に書き込むメモリセルの集合をC0とする。図8に示す書き込みシーケンスにおける、ステップST30〜ST35のフローは、第2実施形態におけるステップST20〜ST25(図3参照)と同様であるので説明を省略する。

次に、書き込み対象メモリセルが同一ワード線上に複数有り、目的の記憶状態(閾値電圧)が異なる場合の更に別の実施形態について、図9のフローチャートを用いて説明する。ここで、図9に示す書き込みシーケンスにおける、ステップST40〜ST45のフローは、第3実施形態におけるステップST30〜ST35(図8参照)と同様であるので説明を省略する。

ベリファイ時に所定の閾値電圧に達していないと判定されたメモリセルに対する再書き込み時に、第1及び第2実施形態では、前回と同じ振幅のワード線電圧と同じパルス幅のビット線電圧(書き込みパルス)を用い、第3実施形態では、ワード線電圧の振幅のみ再書き込み回数に応じて段階的に増加させ、第4実施形態では、ワード線電圧の振幅とビット線電圧のパルス幅の両方を再書き込み回数に応じて段階的に増加させた。これに対し、第5実施形態では、前回と同じ振幅のワード線電圧を用いながら、ビット線電圧のパルス幅のみ再書き込み回数に応じて段階的に増加させ、再書き込みを行うようにしても構わない。

上記第2実施形態〜第5実施形態では、書き込み対象メモリセルが同一ワード線上に複数有り、目的の記憶状態(閾値電圧)が異なる場合について、説明したが、書き込み対象メモリセルが同一ワード線上に複数有り、目的の記憶状態(閾値電圧)が1つか、或いは、全ての書き込み状態を含まない場合はあり得る。例えば、記憶状態“10”に書き込むメモリセルの集合をA0、記憶状態“01”に書き込むメモリセルの集合をB0、記憶状態“00”に書き込むメモリセルの集合をC0とした場合に、書き込み対象メモリセルが、A0,B0,C0の内のA0、B0またはA0とB0には含まれない場合があり得る。かかる場合に、更に書き込み時間を短縮可能な書き込みシーケンスについて、図10のフローチャートを用いて説明する。図10中、ステップST50,ST52,ST54,St56,ST57,ST58,ST59は、夫々、第4実施形態のステップST40,ST41,ST42,ST43,ST44,ST45,ST46(図9参照)に相当し、各処理内容は基本的に同じである。

第7実施形態では、第6実施形態における1回目または1回目を含むn回目までの一連の書き込み工程において、ステップST51とST53(図10参照)の判定を行わずに、ステップST52をST54(図10参照)の書き込みを強制的に実行するようにすることで、上記問題(低閾値電圧のメモリセルに高ゲート電圧が印加され過大なドレイン電流が流れる問題)を解決することができる。つまり、(n+1)回目以降の再書き込み時にステップST51とST53を行うことで、第6実施形態が実施され、再書き込みに係る書き込み時間の短縮が図れる。

第7実施形態では、ステップST51とST53を実施するか否かの判定が、毎回の書き込み工程で必要となる。この煩雑さを回避するために、図11に示すような書き込みシーケンスを行っても構わない。即ち、1回目または1回目を含むn回目までの一連の書き込み工程において、別経路で、ステップST62とST63(図10のステップST52とST54に対応)の書き込みを行うようにする。

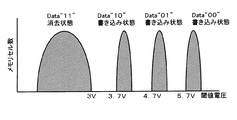

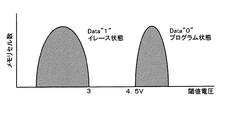

上記第1乃至第8実施形態では、メモリセルの取り得る記憶状態(閾値電圧状態)が4値の場合を説明したが、第1乃至第8実施形態で例示した本発明方法は、多値レベルとして4値に限定されるものではない。本発明方法の技術的思想は、N値(Nは3以上の自然数)メモリセルの書き込みに対して適用しても同様の効果を奏する。N値の記憶状態を閾値電圧の低い状態から、レベル“1”〜レベル“N”とすると、4値の場合と対応付けると、レベル“2”以上が書き込み状態となる。ここで、書き込み状態のレベルをM(Mは2以上N以下の自然数)とした場合、各書き込み状態に対応した書き込み処理が(N−1)回存在し、夫々の書き込み処理M(書き込み状態レベルMへの書き込み)のワード線電圧(メモリセルレベルでは書き込みゲート電圧)をVgM[n]とすると(nは再書き込み回数を表し、1回目の書き込み時は0)、一般式としてVg(M−1)[n]<VgM[n]の関係が成立する(4値の場合は、第1実施形態で示した通り、Vg10[n]<Vg01[n]<Vg00[n]と表される)。書き込み処理Mのビット線電圧VdpM[n] (メモリセルレベルでは書き込みドレイン電圧)及びパルス幅WpM[n]は、第1〜第8実施形態と同様に、Mの値に拘わらず一定とする。書き込み処理MはM=2〜Nに対し順次実行し、その後に書き込み対象メモリセルの目的の記憶状態に対応するベリファイ処理を行い、ワード線及びビット線の電圧を初期状態に戻す。ベリファイ処理で、全ての書き込み対象メモリセルの目的の記憶状態になるまで、書き込み処理M(M=2〜N)を繰り返す。

11 :メモリアレイ(メインメモリアレイ)

12 :リファレンスメモリアレイ

13 :ワード線電圧供給回路

14 :ビット線電圧供給回路

15 :センスアンプ・アレイ

16 :書き込み電圧発生回路

17 :読み出し電圧発生回路

18 :制御回路

20 :センスアンプ

21 :読出し回路

22 :ビット線選択回路

23 :読出し回路

24 :スイッチ回路

40 :浮遊ゲート(フローティングゲート)

41 :チャネル領域

42 :制御ゲート

43 :酸化膜(絶縁膜)

44 :層間絶縁膜

45 :ソース領域

46 :ドレイン領域

100:メモリセル

100a:書き込み対象メモリセル

101a〜101c:ベリファイ用リファレンスセル

SL :共通ソース線

WL0〜WLn:ワード線

BL0〜BLm:ビット線

Claims (10)

- チャネル領域と制御ゲート間に絶縁膜を介して電荷蓄積領域の形成されたトランジスタを有し、前記電荷蓄積領域の電荷量に応じて決定される閾値電圧のレベルに応じて2以上の書き込み状態を含む3以上の記憶状態を取り得るメモリセルを行方向及び列方向に夫々複数配列し、同一行の前記メモリセルの前記制御ゲートを相互に接続して共通のワード線とし、同一列の前記メモリセルのドレインを相互に接続して共通のビット線として構成されたメモリセルアレイを備えてなる不揮発性半導体記憶装置の書き込み方法であって、

前記2以上の書き込み状態に各別に対応する複数の書き込みゲート電圧を予め設定しておき、

同一の前記ワード線に接続する2以上の書き込み対象メモリセルに同時に書き込む場合において、

前記2以上の書き込み対象メモリセルに接続する前記ワード線に、書き込み後の書き込み状態を含む2以上の書き込み状態に対応する2以上の前記書き込みゲート電圧を電圧値の低い順に順次印加し、前記書き込みゲート電圧の各印加と同時に、前記書き込み対象メモリセルに接続する前記ビット線の少なくとも1つに、所定の書き込みドレイン電圧を印加する書き込み工程と、

前記書き込み工程を実行した後に、前記2以上の書き込み対象メモリセルが夫々書き込まれたか否かを検証するベリファイ工程を有し、

前記ベリファイ工程において、前記書き込み対象メモリセルの少なくとも1つが書き込まれていないと判定された場合、前記書き込み工程を再度実行し、

1回目の実行及び2回目以降所定回までの再実行に係る前記書き込み工程では、電圧値の低い順に前記書き込みゲート電圧を順次印加する各印加前に、前記書き込み対象メモリセルが印加される前記書き込みゲート電圧に対応する前記書き込み状態への書き込みを要するか否かを判定する要否判定を、前記書き込みゲート電圧の各印加の少なくとも低電圧側の2回の印加前には実行せずに、前記書き込みゲート電圧及び前記書き込みドレイン電圧の印加を強制的に実行し、

前記所定回より後の再実行に係る前記書き込み工程では、電圧値の低い順に前記書き込みゲート電圧を順次印加する各印加前に、前記要否判定を行い、その判定結果に基づいて前記書き込みゲート電圧及び前記書き込みドレイン電圧の印加を実行することを特徴とする不揮発性半導体記憶装置の書き込み方法。 - 前記書き込み工程を実行する前に、何回目の実行であるかを判定し、1回目の実行及び2回目以降前記所定回までの再実行である場合には、当該書き込み工程において、電圧値の低い順に前記書き込みゲート電圧を順次印加する各印加前に、前記要否判定を実行しないことを特徴とする請求項1に記載の不揮発性半導体記憶装置の書き込み方法。

- 前記書き込み工程において印加する2以上の前記書き込みゲート電圧に、書き込み後の書き込み状態に対応する前記書き込みゲート電圧より低い電圧値の前記書き込みゲート電圧が含まれることを特徴とする請求項1または2に記載の不揮発性半導体記憶装置の書き込み方法。

- 前記書き込み工程において、前記所定の書き込みドレイン電圧の印加される前記ビット線は、そのビット線に接続する前記書き込み対象メモリセルの前記所定の書き込みドレイン電圧印加前の記憶状態に対応する閾値電圧範囲が、前記所定の書き込みドレイン電圧印加時に印加される前記書き込みゲート電圧を決定する書き込み状態に対応する閾値電圧範囲より低いことを特徴とする請求項1〜3の何れか1項に記載の不揮発性半導体記憶装置の書き込み方法。

- 再度実行される2回目以降の前記書き込み工程における前記書き込み対象メモリセルから、前記ベリファイ工程で書き込まれていると判定された書き込み済みメモリセルを除外することを特徴とする請求項1〜4の何れか1項に記載の不揮発性半導体記憶装置の書き込み方法。

- 1回目及び再度実行される2回目以降の前記書き込み工程の内、少なくとも1回目の前記書き込み工程において印加する2以上の前記書き込みゲート電圧に、書き込み後の書き込み状態に対応する前記書き込みゲート電圧より低い電圧値の前記書き込みゲート電圧が含まれることを特徴とする請求項1〜4の何れか1項に記載の不揮発性半導体記憶装置の書き込み方法。

- チャネル領域と制御ゲート間に絶縁膜を介して電荷蓄積領域の形成されたトランジスタを有し、前記電荷蓄積領域の電荷量に応じて決定される閾値電圧のレベルに応じて2以上の書き込み状態を含む3以上の記憶状態を取り得るメモリセルを行方向及び列方向に夫々複数配列し、同一行の前記メモリセルの前記制御ゲートを相互に接続して共通のワード線とし、同一列の前記メモリセルのドレインを相互に接続して共通のビット線として構成されたメモリセルアレイと、

書き込み対象メモリセルに接続する前記ワード線に前記2以上の書き込み状態に各別に対応して予め設定された複数の書き込みゲート電圧を選択的に印加し、前記書き込み対象メモリセルに接続する前記ビット線に所定の書き込みドレイン電圧を印加する書き込み手段と、

前記書き込み対象メモリセルが書き込まれたか否かを検証するベリファイ手段と、を備えてなる不揮発性半導体記憶装置であって、

前記書き込み対象メモリセルが、印加する前記書き込みゲート電圧に対応する前記書き込み状態への書き込みを要するか否かを判定する要否判定を実行する判定手段を、更に備え、

同一の前記ワード線に接続する2以上の書き込み対象メモリセルに同時に書き込む場合において、

前記書き込み手段が、前記2以上の書き込み対象メモリセルに接続する前記ワード線に、書き込み後の書き込み状態を含む2以上の書き込み状態に対応する2以上の前記書き込みゲート電圧を電圧値の低い順に順次印加し、前記書き込みゲート電圧の各印加と同時に、前記書き込み対象メモリセルに接続する前記ビット線の少なくとも1つに、所定の書き込みドレイン電圧を印加する書き込み工程を実行するように構成され、

前記ベリファイ手段が、前記2以上の書き込み対象メモリセルが夫々書き込まれたか否かを検証するベリファイ工程を実行するように構成され、

前記ベリファイ手段が、前記ベリファイ工程において、前記書き込み対象メモリセルの少なくとも1つが書き込まれていないと判定した場合、前記書き込み手段が、前記書き込み工程を再度実行し、

1回目の実行及び2回目以降所定回までの再実行に係る前記書き込み工程では、前記書き込み手段が電圧値の低い順に前記書き込みゲート電圧を順次印加する各印加の少なくとも低電圧側の2回の印加前には、前記判定手段が前記要否判定を実行せずに、前記書き込み手段が前記書き込みゲート電圧及び前記書き込みドレイン電圧の印加を強制的に実行し、

前記所定回より後の再実行に係る前記書き込み工程では、前記書き込み手段が電圧値の低い順に前記書き込みゲート電圧を順次印加する各印加前に、前記判定手段が前記要否判定を実行し、その判定結果に基づいて、前記書き込み手段が前記書き込みゲート電圧及び前記書き込みドレイン電圧の印加を実行することを特徴とする不揮発性半導体記憶装置。 - 前記書き込み手段が、前記書き込み工程を実行する前に、当該書き込み工程が何回目の実行であるかを判定する第2判定手段を備え、

前記第2判定手段の判定結果が、1回目の実行及び2回目以降前記所定回までの再実行である場合には、当該書き込み工程において、電圧値の低い順に前記書き込みゲート電圧を順次印加する各印加前に、前記判定手段が前記要否判定を実行しないことを特徴とする請求項7に記載の不揮発性半導体記憶装置の書き込み方法。 - 前記ベリファイ手段が、同時に前記ベリファイ工程を実行するベリファイ対象メモリセル毎に、前記メモリセルが取り得る前記書き込み状態の数に応じた複数のセンスアンプを備えてなり、

前記複数のセンスアンプの夫々に異なる固有の電圧値の参照電圧が用いられることを特徴とする請求項7または8に記載の不揮発性半導体記憶装置。 - 前記ベリファイ手段が、同時に前記ベリファイ工程を実行するベリファイ対象メモリセル毎に1つのセンスアンプを備えてなり、

前記センスアンプに前記メモリセルが取り得る前記書き込み状態の数に応じた複数の夫々異なる電圧値の参照電圧がスイッチ回路を介して選択的に用いられることを特徴とする請求項7または8に記載の不揮発性半導体記憶装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003289838A JP4245437B2 (ja) | 2003-08-08 | 2003-08-08 | 不揮発性半導体記憶装置の書き込み方法 |

| US10/913,251 US6954380B2 (en) | 2003-08-08 | 2004-08-06 | Programming method of nonvolatile semiconductor memory device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003289838A JP4245437B2 (ja) | 2003-08-08 | 2003-08-08 | 不揮発性半導体記憶装置の書き込み方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005063516A JP2005063516A (ja) | 2005-03-10 |

| JP4245437B2 true JP4245437B2 (ja) | 2009-03-25 |

Family

ID=34101131

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003289838A Expired - Fee Related JP4245437B2 (ja) | 2003-08-08 | 2003-08-08 | 不揮発性半導体記憶装置の書き込み方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US6954380B2 (ja) |

| JP (1) | JP4245437B2 (ja) |

Families Citing this family (29)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6937520B2 (en) * | 2004-01-21 | 2005-08-30 | Tsuyoshi Ono | Nonvolatile semiconductor memory device |

| ITMI20042462A1 (it) * | 2004-12-23 | 2005-03-23 | St Microelectronics Srl | Memoria ausiliare |

| JP4907896B2 (ja) * | 2005-04-12 | 2012-04-04 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| KR100616214B1 (ko) * | 2005-06-30 | 2006-08-28 | 주식회사 하이닉스반도체 | 멀티-레벨 셀을 가지는 플래시 메모리 장치의 프로그램제어 회로 및 그 프로그램 제어 방법 |

| US7342833B2 (en) * | 2005-08-23 | 2008-03-11 | Freescale Semiconductor, Inc. | Nonvolatile memory cell programming |

| JP2007102865A (ja) * | 2005-09-30 | 2007-04-19 | Toshiba Corp | 半導体集積回路装置 |

| JP2007213719A (ja) * | 2006-02-10 | 2007-08-23 | Sharp Corp | 半導体記憶装置 |

| KR100706816B1 (ko) * | 2006-03-10 | 2007-04-12 | 삼성전자주식회사 | 프로그램 속도를 향상시킬 수 있는 불휘발성 메모리 장치및 그것의 프로그램 방법 |

| KR100766241B1 (ko) * | 2006-05-10 | 2007-10-10 | 주식회사 하이닉스반도체 | 플래쉬 메모리 소자의 프로그램 방법 |

| US7411832B2 (en) * | 2006-05-18 | 2008-08-12 | Micron Technology, Inc. | Programming a non-volatile memory device |

| JP4896605B2 (ja) | 2006-07-04 | 2012-03-14 | 株式会社東芝 | 不揮発性半導体記憶システム |

| US7525838B2 (en) * | 2006-08-30 | 2009-04-28 | Samsung Electronics Co., Ltd. | Flash memory device and method for programming multi-level cells in the same |

| US7602650B2 (en) * | 2006-08-30 | 2009-10-13 | Samsung Electronics Co., Ltd. | Flash memory device and method for programming multi-level cells in the same |

| US7656709B2 (en) * | 2007-05-03 | 2010-02-02 | Micron Technology, Inc. | NAND step up voltage switching method |

| US7965866B2 (en) * | 2007-07-03 | 2011-06-21 | Shoppertrak Rct Corporation | System and process for detecting, tracking and counting human objects of interest |

| KR101301773B1 (ko) * | 2007-10-25 | 2013-09-02 | 삼성전자주식회사 | 멀티 비트 프로그래밍 장치 및 방법 |

| US7952927B2 (en) | 2007-12-05 | 2011-05-31 | Micron Technology, Inc. | Adjusting program and erase voltages in a memory device |

| KR101448851B1 (ko) * | 2008-02-26 | 2014-10-13 | 삼성전자주식회사 | 비휘발성 메모리 장치에서의 프로그래밍 방법 |

| JP5754761B2 (ja) | 2008-07-22 | 2015-07-29 | ラピスセミコンダクタ株式会社 | 不揮発性半導体メモリおよび不揮発性半導体メモリのデータ書込み方法 |

| JP2010135023A (ja) * | 2008-12-05 | 2010-06-17 | Toshiba Corp | 半導体記憶装置 |

| US8223555B2 (en) * | 2009-05-07 | 2012-07-17 | Micron Technology, Inc. | Multiple level program verify in a memory device |

| JP2011040135A (ja) * | 2009-08-13 | 2011-02-24 | Toshiba Corp | 不揮発性半導体記憶装置 |

| US8406072B2 (en) * | 2010-08-23 | 2013-03-26 | Qualcomm Incorporated | System and method of reference cell testing |

| KR20130072520A (ko) * | 2011-12-22 | 2013-07-02 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 및 이의 동작 방법 |

| US9384799B2 (en) | 2013-03-21 | 2016-07-05 | Micron Technology, Inc. | Advanced memory interfaces and methods |

| US9123414B2 (en) * | 2013-11-22 | 2015-09-01 | Micron Technology, Inc. | Memory systems and memory programming methods |

| US9336875B2 (en) | 2013-12-16 | 2016-05-10 | Micron Technology, Inc. | Memory systems and memory programming methods |

| US9269432B2 (en) * | 2014-01-09 | 2016-02-23 | Micron Technology, Inc. | Memory systems and memory programming methods |

| WO2021223099A1 (en) | 2020-05-06 | 2021-11-11 | Yangtze Memory Technologies Co., Ltd. | Control method and controller of 3d nand flash |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3238574B2 (ja) * | 1994-07-28 | 2001-12-17 | 株式会社東芝 | 不揮発性半導体記憶装置とその消去方法 |

| US5943263A (en) * | 1997-01-08 | 1999-08-24 | Micron Technology, Inc. | Apparatus and method for programming voltage protection in a non-volatile memory system |

| US6850438B2 (en) * | 2002-07-05 | 2005-02-01 | Aplus Flash Technology, Inc. | Combination nonvolatile memory using unified technology with byte, page and block write and simultaneous read and write operations |

-

2003

- 2003-08-08 JP JP2003289838A patent/JP4245437B2/ja not_active Expired - Fee Related

-

2004

- 2004-08-06 US US10/913,251 patent/US6954380B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US6954380B2 (en) | 2005-10-11 |

| US20050024938A1 (en) | 2005-02-03 |

| JP2005063516A (ja) | 2005-03-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4245437B2 (ja) | 不揮発性半導体記憶装置の書き込み方法 | |

| US7362616B2 (en) | NAND flash memory with erase verify based on shorter evaluation time | |

| JP5280679B2 (ja) | メモリのラッチプログラミングおよびその方法 | |

| US7414871B2 (en) | Program control circuit of flash memory device having MLC and method thereof | |

| US7826273B2 (en) | Method of verifying programming of a nonvolatile memory device | |

| TWI497507B (zh) | 縮短抹除操作的方法與裝置 | |

| US8737131B2 (en) | Programming memory cells using smaller step voltages for higher program levels | |

| US20020154545A1 (en) | Non-volatile memory device with plurality of threshold voltage distributions | |

| US20130077408A1 (en) | Nonvolatile semiconductor memory device | |

| US8027200B2 (en) | Reduction of quick charge loss effect in a memory device | |

| JP2009503763A (ja) | 不揮発性集積メモリデバイスのセルをプログラムするためのシステムと方法 | |

| US7151701B2 (en) | Self-adaptive program delay circuitry for programmable memories | |

| JP3739102B2 (ja) | 不揮発性半導体記憶装置 | |

| US6661709B2 (en) | Nonvolatile semiconductor memory device | |

| US7336532B2 (en) | Method for reading NAND memory device and memory cell array thereof | |

| US6256702B1 (en) | Nonvolatile memory device with extended storage and high reliability through writing the same data into two memory cells | |

| KR100589469B1 (ko) | 단시간에 소거 동작을 행하는 비휘발성 메모리 | |

| KR20060003258A (ko) | 비트 스캐닝 프로그램을 수행하는 불휘발성 메모리 장치 | |

| JP3945652B2 (ja) | 不揮発性記憶装置 | |

| EP1752989B1 (en) | NAND flash memory with erase verify based on shorter delay before sensing | |

| EP1782426B1 (en) | Self-adaptive program delay circuitry for programmable memories | |

| JP3859975B2 (ja) | 不揮発性メモリ | |

| JP2003085987A (ja) | 不揮発性半導体記憶装置 | |

| JP2007188547A (ja) | 不揮発性半導体記憶装置 | |

| CN118072794A (zh) | 用于执行编程操作的半导体装置和操作半导体装置的方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20041224 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050810 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080609 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080624 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080808 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20081209 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090106 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120116 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130116 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130116 Year of fee payment: 4 |

|

| LAPS | Cancellation because of no payment of annual fees |