JP4141549B2 - Manufacturing method of semiconductor light emitting device - Google Patents

Manufacturing method of semiconductor light emitting device Download PDFInfo

- Publication number

- JP4141549B2 JP4141549B2 JP31575998A JP31575998A JP4141549B2 JP 4141549 B2 JP4141549 B2 JP 4141549B2 JP 31575998 A JP31575998 A JP 31575998A JP 31575998 A JP31575998 A JP 31575998A JP 4141549 B2 JP4141549 B2 JP 4141549B2

- Authority

- JP

- Japan

- Prior art keywords

- solder

- submount

- semiconductor laser

- present

- light emitting

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/48463—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a ball bond

Landscapes

- Led Device Packages (AREA)

- Semiconductor Lasers (AREA)

- Led Devices (AREA)

Description

【0001】

【発明の属する技術分野】

本発明は、片面に複数の電極を有する半導体発光素子チップを用いた半導体発光装置の製造方法に関する。

【0002】

【従来の技術】

GaN系半導体は、紫外ないし緑色領域における発光素子を実現する材料として注目されており、中でも、これを用いて、従前よりも短波長で発振する半導体レーザ装置を実用化することが望まれている。GaN系半導体の特徴として、基板に絶縁体であるサファイアを用いる点が挙げられ、よって、このような半導体を用いた発光素子チップでは、従前と異なり、正負両方の電極がエピ層側に形成されるのが常である。そのため、GaN系半導体レーザチップに対して、エピ層側を下にした、すなわちジャンクションダウンのダイボンディングを実施するためには、エピ層側に一方の電極しか形成されない従前の半導体レーザチップとは異なったマウント方法が必要となる。

【0003】

図19は、特開平7−235729号公報に開示された、このような技術を用いた半導体レーザ装置の一例である。図において、1はサブマウント基体、2はサブマウント積載面に設けられた金属パターン、3はハンダ、4はGaN系半導体レーザチップ本体、5はGaN系半導体レーザチップエピ層側に設けられた、正負電極である。本例においては、絶縁性のサブマウントを用いており、サブマウント上面に、半導体レーザ正負電極に対応した金属膜パターンが設けられ、それぞれが、ハンダにより半導体レーザ正負電極に接合されて、ジャンクションダウンのダイボンディングが実現されている。

【0004】

ここで、ダイボンディングとは、一般的には、次のような工程である。通常、ハンダはあらかじめサブマウント上に設けられている。これを、融点以上に加熱し、所定の位置にアライメントしたレーザチップを、溶解したハンダに押し付け、その後、ハンダを冷却固化させる。これにより、レーザチップとサブマウントとが熱伝導性よく接着される。

【0005】

【発明が解決しようとする課題】

従来の技術に示すような、片面に正負電極を有する半導体レーザチップでは、図19に示されたように、正負電極の間がハンダ接合され得ず、ブリッジ状にサブマウントと接合することになる。これによって、エピ層側に一方の電極しか形成されない従前の半導体レーザチップでは生じ得なかった、以下に示すような問題が発生する。

【0006】

ダイボンディング工程において、融解したハンダが冷却される際には、ハンダの固化・合金化が必ずしも各部で均一に進行するものではないために、ハンダ部分の体積変化や表面張力が領域毎に変動し、接着面には複雑な力が加わっている。図19のように、接着面が正負両側に別れている半導体レーザ装置では、このような、接着面毎に加わる力のバランスが崩れることによって、冷却の途中でレーザチップが動き、アライメントずれが発生してしまう。実際に、本発明者の実験的知見によれば、図19に示された半導体レーザ装置でのアライメントずれの発生確率は、エピ層側に一方の電極しか形成されない従前の半導体レーザにおけるものと比べて、5倍程度高いものであった。このようなアライメントずれは、半導体レーザ装置の光学的特性の問題、すなわち、レーザ光の出射方向ずれを引き起こすだけでなく、片側に正負電極が形成されているがために、正負間でのショート・リークという問題をも発生させていた。これが、従来の技術の半導体レーザ装置における第1の問題点である。

【0007】

また、レーザチップがブリッジ状にサブマウントと接合するので、レーザチップに大きな応力が加わりやすいという、構造上の問題もある。特に、両ハンダが同時に固化する際の、上述のような、予測できないそれぞれの接着面に加わる力の集中の具合によっては、半導体レーザチップに大きな熱歪みが加わってしまう。このような応力・歪みは、半導体レーザ装置の寿命を短縮させる。これが、従来の技術の半導体レーザ装置における第2の問題点である。

【0008】

本発明は、従来の技術における、上述の問題点を解消することを目的とする。

【0009】

【課題を解決するための手段】

本発明によれば、片面に第1と第2の電極を有する半導体発光素子チップが、各電極に対向する導電膜パターンを積載面上に有したマウント部材にハンダを用いて積載され、第1の電極と第1の導電膜パターンとが第1のハンダで接続され、第2の電極と第2の導電膜パターンとが第1ハンダと異なる第2のハンダで接続される半導体発光装置の製造方法において、マウント部材上にあらかじめ設置した第1ハンダおよび第2ハンダを第1ハンダの融点T1および第2ハンダの融点T2のいずれよりも高い温度に加熱する工程と、第1ハンダおよび第2ハンダをT1とT2の中間の一定温度に所定時間保持することにより、第1ハンダおよび第2のハンダのうちで高い融点を有するハンダを固化させるとともに、低い融点を有するハンダを溶融した状態に保持する工程と、第1のハンダおよび第2のハンダをT1とT2のいずれよりも低い温度に冷却することにより、第1ハンダおよび第2ハンダのうちで低い融点を有するハンダを固化させる工程を上記の順に行なうことを特徴としている。

なお、マウント部材上における第1ハンダと第2ハンダとの間のスペースには、溝、梨地面、樹脂突起、および絶縁体突起のいずれかが設けられていることが好ましい。また、半導体発光素子チップは半導体レーザチップであり得る。

【0024】

本明細書において、半導体発光装置とは、半導体レーザチップやLEDチップのような半導体発光素子チップを、マウント部材に積載し、一体化したものを表している。

【0025】

また、本明細書において、マウント部材とは、半導体発光素子チップを直接積載するための部品を意味しており、例えば、半導体発光素子チップ用のサブマウントや、サブマウントを用いず直接ステム、フレームもしくはパッケージに積載する場合においては、このステム、フレームもしくはパッケージ自身を指している。

また、本明細書において導電性接着剤とは、ハンダ、ロー材、導電性樹脂を含む。

また、放熱材料として知られている材料の例としては、熱伝導率の大きいものから順にダイヤモンド>cBN>Ag>Cu>SiC>CuW>BeO>AlN>Fe>Mo>Si>Al2O3>GaAs等がある。(参照:培風館、伊藤良一・中村道治共著「半導体レーザ」P.232、図16.19)但し、本発明においては、放熱材料の熱伝導率の差に着目するため、熱伝導率の異なる組合わせを選択すれば、上記材料以外の材料から選択しても構わない。

【0026】

【発明の実施の形態】

以下の実施の形態においては、サブマウント基体が放熱部となる。

【0027】

〔実施の形態1〕

図1は、本発明の実施の形態1の半導体レーザ装置を示す断面模式図である。図において、10は本実施の形態の半導体レーザ装置、100は本実施の形態のサブマウント、101は絶縁性サブマウント基体、102は正側金属パターン、103は負側金属パターン、104は第1のハンダ、105は第2のハンダであり、また、200はGaN系半導体レーザチップ、201はサファイア基板、202は半導体成長層、203は正電極、204は負電極である。図示されるように、サブマウント積載面のハンダおよび金属パターンは、適宜パターン形成されることにより、それぞれが絶縁分離されており、よって、片面に正負電極を有する半導体レーザ素子の積載を可能としていることは、従来の技術と同様である。

【0028】

図2は、上記GaN系半導体レーザチップ200の構成を、より詳しく示した断面図であり、これを参照して、以下にその構成を説明する。

【0029】

サファイア基板201表面に、AlNもしくはGaNからなるバッファ層210、n−GaN層211、n−AlGaNクラッド層212、多層のInGaNからなる量子井戸活性層213、半導体レーザの共振器方向に沿ったリッジストライプ形状のp−AlGaNクラッド層214が順次形成されている。さらに、ストライプ外部には、n−AlGaN電流阻止層215が積層され、電流阻止層表面およびリッジストライプ部p−AlGaNクラッド層表面には、p−GaNキャップ層216が積層形成されている。バッファ層210からキャップ層216の各層により、半導体成長層202が構成される。半導体成長層202の一部には、リッジストライプに平行して、表面からn−GaN層に達する溝が設けられ、各p型の成長層が、二分される。リッジストライプの存在する側のp−GaNキャップ層表面には、正電極203が設けられ、さらに、溝底部に露出したn−GaN層に接触して、負電極204が設けられ、これは、反対側のp−GaNキャップ層表面にまで、延長される。これにより、半導体レーザチップの成長層側表面に正負電極が露出している。また、溝内部にはSiO等からなる絶縁体205が設けられ、ダイボンディング工程におけるショートを防止する役割を果たしている。上記構成により図2において記号206で示すストライプ状部分が半導体レーザの発光部となる。本実施の形態においては、一例として、レーザチップのサイズを、長さ0.5×幅0.6×高さ0.1mmとし、電極間の距離を50 mとした。このような半導体レーザチップは、公知技術により容易に構成できるので、その製造方法の説明は省略する。

【0030】

図3は、本実施の形態の半導体レーザ装置に用いた、本実施の形態のサブマウントを示す模式図である。各記号は図1と同一である。本実施の形態において、サブマウント基体101には、絶縁体であるAlNを用い、金属パターン102および103には、Au(0.1 m)/Pt(0.1 m)/Ti(0.1 m)(Au オン Pt オン Ti、以下同様)、第1のハンダ104には融点T1が280℃であるAuSn(Au80%,Sn20%)、第2のハンダには、融点T2が、232℃であるSnを用いた。すなわち、本実施の形態においては、T1>T2の関係が成立する。各金属パターンおよび各ハンダの成膜は、真空蒸着法、CVD法、スパッタ法、メッキ法、熱転写法、印刷法、焼結法等の公知技術を適宜用いて行うことができる。本実施の形態においては、一例として、サブマウント基体101のサイズを、長さ1.5×幅2×高さ0.2mmとし、ハンダ間の距離を50μm、ハンダの厚さを1μmとした。

【0031】

上述の構成によって、本半導体レーザチップにおいては、正電極が発光部に隣接する側の電極となり、負電極がその反対側の電極に相当する。また、本サブマウントにおいては、正側金属パターンが、正電極に対向する導電膜パターンとなり、負側金属パターンが負電極に対向する導電膜パターンに相当する。

【0032】

次に、本実施の形態の半導体レーザ装置を製造するためのダイボンディング工程について、図4を参照しつつ、説明する。図4は、工程の各過程におけるサブマウント積載面温度Tの変化を示したグラフ(温度プロファイル)である。ここで、Tは、各ハンダの温度に一致している。

【0033】

〈過程A〉始めに、図3に示した、本実施の形態のサブマウントを、第1および第2のハンダの融点よりも高い温度であるT=300℃まで加熱したところ、双方のハンダが融解した。

〈過程B〉図2に示した半導体レーザチップを、適切にアライメントし、レーザチップ電極形成面とサブマウント積載面とが突き合わされるように、サブマウント上に積載した。ここで、アライメントは、次の要領でなされる。正電極と第1のハンダおよび正側金属パターン、負電極と第2のハンダおよび負側金属パターンが、それぞれ一致するように、すなわち、図1に示されるように、また、半導体レーザチップのストライプ方向が、サブマウントの端面と垂直の関係になり、光出射面がサブマウントの端面とほぼ一致するように、方向および位置併せされる。

次いで、半導体レーザチップに約20gの荷重を加えて、T=300℃の状態を30〜120秒間保持し、ハンダと、金属パターンおよび電極とを良くなじませた。(T>T1、T2)

〈過程C〉荷重を加えたまま、Tを第1のハンダの融点よりも低く、第2のハンダの融点よりも高い温度である250℃に変化させた。

〈過程D〉T=250℃の状態を30秒間保持した。この間に、第1のハンダが固化し、半導体レーザチップはサブマウントに固定された。第1のハンダが固化した後、荷重を加えることを止めた。(T1>T>T2)

〈過程E〉サブマウントを冷却し、第2のハンダも固化させた。室温に近い適当な温度まで冷却されたところで、ダイボンディング工程を、終了した。

以上により、図1に示す本実施の形態の半導体レーザ装置が完成した。

【0034】

本実施の形態の半導体レーザ装置は、第1のハンダの融点が第2のハンダの融点よりも高く構成されているので、従来の技術の問題点が以下のように、解消されている。

【0035】

上記過程Bにおいて融解したハンダのうち、発光部に隣接する第1のハンダ104のみが、過程Dで固化する。このとき、第2のハンダは、まだ、融解しているので、従来の技術において問題となったような、両方のハンダが同時に固化しようとすることに伴う、各接合面毎に加わる力のアンバランスが生じない。これにより、半導体レーザチップは、第1のハンダの固化に伴って、動くことなく固定される。よって、その後、第2のハンダが固化する際にチップがずれてしまうこともなく、結果として、ハンダ冷却の途中でレーザチップが動き、アライメントずれが発生してしまう従来の技術第1の問題が回避される。 また、従来の技術において、両ハンダが同時に固化する際の、予測できないそれぞれの接着面に加わる力の、偶然の集中によって、ブリッジ状にサブマウントに固定される半導体レーザチップに大きな熱歪みが加わることも無い。さらに、先に第1のハンダ側が固定された後、第2のハンダ側の固定に至るまでの間に、チップに引き起こされる歪みが緩和されている。結果として、半導体レーザチップに大きな応力・熱歪みが発生してしまう従来の技術における第2の問題点が回避される。

【0036】

本実施の形態の半導体発光素子の製造方法においては、過程Bの温度Tが、第1のハンダの融点より若干高い温度に設定されている。これは、正電極と正側金属パターンの接合を、最適な条件で行うためのもので、これにより、それらとハンダの間での合金化が適正に進み、また、ハンダが厚すぎて介在されることがなくなり、よって、熱抵抗を最小限とした接合が可能になる。これに対して、負電極側の接合は、より低融点のハンダが用いられているために、過程Bの温度Tが第2のハンダの融解処理温度として必ずしも適切なものではなく、よって、第2のハンダの適正な処理温度を用いたダイボンディング工程によるものに比べると、接合の熱抵抗として最適な値が得られない。しかしながら、本実施の形態の半導体レーザ装置では、発光部に隣接した電極が正電極であるので、負電極側の熱抵抗は、半導体レーザ装置の熱抵抗にほとんど影響せず、結果として、半導体レーザ装置の熱抵抗が最適化されていることになって、温度特性向上に貢献する。

【0037】

比較のために、本実施の形態の半導体レーザ装置における、第2のハンダを第1のハンダと同一の材料で構成した、対照半導体レーザ装置を作製した。サブマウントの端面垂直方向から±2°以内にレーザビーム中心がくることをダイボンディング工程の位置ずれに関する良品条件と規定したとき、本実施の形態の半導体レーザ装置においては、良品の得られる率が96%だったのに対し、対象半導体レーザ装置においては、78%であった。また、それぞれの半導体レーザ装置に、3mW、70℃(初期電流90mA程度)の条件での通電試験を1000時間行ったところ、前者では、駆動電流の上昇がほとんど見られなかったのに対し、後者では、約40%の装置で駆動電流値の20%以上の上昇が観察された。このように、従来の技術を用いた半導体レーザ装置と比較して、ダイボンディング工程の生産性の向上と、装置寿命特性の向上が確認された。

【0038】

また、本実施の形態のサブマウントによれば、従来の技術のものと比較して、半導体レーザ装置の生産性を向上せしめ、装置寿命特性を改善させる効果を奏する。

【0039】

〔実施の形態2〕

本実施の形態の構成は、第1のハンダおよび第2のハンダの材料が異なる他は、実施の形態1と同様である。

【0040】

本実施の形態の半導体レーザ装置、および、これに用いた本実施の形態のサブマウントにおいて、第1のハンダには融点T1が156℃であるIn、第2のハンダには、融点T2が217℃であるSnAu(Sn90%、Au10%)を用いた。すなわち、本実施の形態においては、T1<T2の関係がある。

【0041】

本実施の形態についても実施の形態1と同様に、半導体レーザチップにおいて、正電極が発光部に隣接する側の電極となり、負電極がその反対側の電極に相当する。また、サブマウントにおいては、正側金属パターンが、正電極に対向する導電膜パターンとなり、負側金属パターンが負電極に対向する導電膜パターンに相当する。

【0042】

次に、本実施の形態の半導体レーザ装置を製造するためのダイボンディング工程について、図5を参照しつつ、説明する。図5は、本ダイボンディング工程の各過程におけるサブマウント積載面温度Tの変化を示したグラフである。ここで、Tは、各ハンダの温度にほぼ一致する。

【0043】

〈過程A〉始めに、本実施の形態のサブマウントを、第1および第2のハンダの融点よりも高い温度であるT=250℃まで加熱したところ、両方のハンダが融解した。

〈過程B〉図2に示した半導体レーザチップを、適切にアライメントし、レーザチップ電極形成面とサブマウント積載面とが突き合わされるように、サブマウント上に積載した。ここで、アライメントは、次の要領でなされる。正電極と第1のハンダおよび正側金属パターン、負電極と第2のハンダおよび負側金属パターンが、それぞれ一致するように、すなわち、図1に示されたのと同様に、また、半導体レーザチップのストライプ方向が、サブマウントの端面と垂直の関係になり、光出射面がサブマウントの端面とほぼ一致するように、方向および位置併せされる。

次いで、半導体レーザチップに約30gの荷重を加えて、T=250℃の状態を30秒間保持し、ハンダと金属パターンおよび電極とを良くなじませた。(T>T1、T2)

〈過程C〉荷重を加えたまま、Tを第1のハンダの融点よりも高く、第2のハンダの融点よりも低い温度である190℃に変化させた。

〈過程D〉T=190℃の状態を30秒間保持した。この間に、第2のハンダが固化し、半導体レーザチップはサブマウントに固定された。第2のハンダが固化した後、荷重を加えることを止めた。(T1<T<T2)

〈過程E〉サブマウントを冷却し、第1のハンダも固化させた。室温に近い適当な温度まで冷却されたところで、ダイボンディング工程を、終了した。

以上により、本実施の形態の半導体レーザ装置が完成した。

【0044】

本実施の形態の半導体レーザ装置は、第1のハンダの融点が第2のハンダの融点よりも低く構成されているので、従来の技術の問題点が以下のように、解消されている。

【0045】

上記過程Bにおいて融解したハンダのうち、発光部に隣接する第2のハンダのみが、過程Dで固化する。このとき、第1のハンダは、まだ、融解しているので、従来の技術において問題となったような、両方のハンダが同時に固化しようとすることに伴う、各接合面に加わる力のアンバランスが生じない。この過程で、半導体レーザチップは、第2のハンダの固化に伴って、動くこともなく固定される。よって、その後、第1のハンダが固化する際にチップがずれてしまうこともなく、結果として、ハンダ冷却の途中でレーザチップが動き、アライメントずれが発生してしまう従来の技術第1の問題が回避される。

【0046】

また、従来の技術において、両ハンダが同時に固化する際の、予測できないそれぞれの接着面に加わる力の、偶然の集中によって、ブリッジ状にサブマウントに固定される半導体レーザチップに大きな熱歪みが加わることも無い。さらに、先に第2のハンダ側が固定された後、第1のハンダ側の固定に至るまでの間に、チップに引き起こされる歪みが緩和されている。結果として、半導体レーザチップに大きな応力・熱歪みが発生してしまう従来の技術における第2の問題点が回避される。

【0047】

また、本実施の形態の半導体発光素子の製造方法において、半導体レーザチップの発光部に隣接する側の電極、すなわち、正電極は、ダイボンディング工程の最終過程Eで始めて固定される。よって、ダイボンディング工程途中で、発光部に引き起こされる歪みは、最終過程の段階まで緩和され得るので、本ダイボンディング工程を経た半導体レーザ装置の発光部における応力・熱歪みは、実施の形態1とくらべて小さいものにできる。よって、本実施の形態によれば、半導体レーザ装置の寿命特性をさらに向上できる。

【0048】

比較のために、本実施の形態の半導体レーザ装置における第2のハンダを、第1のハンダと同一の材料で構成した、対照半導体レーザ装置を作製した。サブマウントの端面垂直方向から±2°以内にレーザビーム中心がくることをダイボンディング工程の位置ずれに関する良品条件と規定したとき、本実施の形態の半導体レーザ装置においては、良品の得られる率が98%だったのに対し、対象半導体レーザ装置においては、75%であった。また、それぞれの半導体レーザ装置に、5mW、60℃(初期電流80mA程度)の条件での通電試験を1000時間行ったところ、前者では、駆動電流の上昇がほとんど見られなかったのに対し、後者では、約70%の装置で駆動電流値の20%以上の上昇が観察された。このように、従来の技術を用いた半導体レーザ装置と比較して、ダイボンディング工程の生産性の向上と、装置寿命特性の向上が確認された。

【0049】

また、本実施の形態のサブマウントによれば、従来の技術のものと比較して、半導体レーザ装置の生産性を向上せしめ、装置寿命特性を改善させる効果を奏する。

【0050】

実施の形態1ないし2における、上述の各ハンダは、In、Sn、Pb、InAl、SnAg、PbIn、PbSn、AuSn、AuSi、AuGe等の他のハンダ、金属性ろう材に置き換えることができる。この際、融点に注意して、正負ハンダを選定する必要がある。表1に、代表的な電子工業用ハンダの融点を示した。このように、本表に示されているだけでも、ハンダの融点は150℃〜400℃と多岐にわたるから、各実施の形態において、融点の異なるハンダの組み合わせを容易に得ることができることが明らかである。

【0051】

【表1】

【0052】

また、各実施の形態における温度プロファイルを図4もしくは図5で説明したが、これは、理想的な温度変化を示したものであって、実際には、過程BやDで厳密に一定温度が保持される必要があるものでもなく、それぞれの過程で徐々に温度変化があるようなプロファイルであってもかまわない。

【0053】

〔実施の形態3〕

図6は、本発明に密接に関連する参考的な実施の形態3の半導体レーザ装置を示す断面図である。図において、30は、本実施の形態の半導体レーザ装置、300はサブマウント、301は導電性樹脂であり、その他実施の形態1と同様の部分については図1と同一の符号で示した。本実施の形態の半導体レーザ装置の構成は、実施の形態2における第2のハンダを導電性樹脂に置換した他は、実施の形態2とほぼ同様である。

【0054】

ここで、導電性樹脂とは、熱可塑性樹脂、熱硬化性樹脂、あるいはこれらの混合物のいずれかの樹脂の中に、金属粉等を所定量混入したものであり、接着性と導電性を併せ持つものである。本実施の形態の半導体レーザ装置において、導電性樹脂接着剤301には、熱硬化性エポキシ樹脂の中に、Ag粒子を50ないし90wt%配合したものを用いた。これにより、導電性樹脂は、金属並の導電性を有している。樹脂の硬化温度として180℃程度のものを用いた。また、第1のハンダには融点が156℃であるInを用いた。

【0055】

本実施の形態についても実施の形態2と同様に、半導体レーザチップにおいて、正電極が発光部に隣接する側の電極となり、負電極がその反対側の電極に相当する。また、サブマウントにおいては、正側金属パターンが、正電極に対向する導電膜パターンとなり、負側金属パターンが負電極に対向する導電膜パターンに相当する。

【0056】

次に、本実施の形態の半導体レーザ装置を製造するためのダイボンディング工程について説明する。

【0057】

あらかじめ、図3に示されたのと同様のサブマウントを準備する。ただし、負側の電極パターン上には、第2のハンダに代えて、上記導電性樹脂が設けられている。この段階で、樹脂は未硬化である。

【0058】

次に、サブマウントの温度を上昇させ、ハンダが融解した後、図2に示した半導体レーザチップを、適切にアライメントし、レーザチップ電極形成面とサブマウント積載面とが突き合わされるように、サブマウント上に積載した。

【0059】

その後、レーザチップに30gの荷重を加えつつ、ハンダの融点以上の温度である180℃の状態を1分間保持して、ハンダと金属パターンおよび電極とを良くなじませ、また、樹脂を硬化させた。

【0060】

それから、ハンダを固化させ、室温に近い適当な温度まで冷却されたところで、ダイボンディング工程を、終了した。

以上により、本実施の形態の半導体レーザ装置が完成した。

【0061】

本実施の形態の半導体レーザ装置は、第2のハンダに替えて、導電性樹脂を用いたので、従来の技術の問題点が以下のように、解消されている。

【0062】

上記過程において融解したハンダが固化する際には、既に、導電性樹脂が硬化しており、よって、半導体レーザチップは、第1のハンダの固化に伴って動くことがない。つまり、ハンダ冷却の途中でレーザチップが動き、アライメントずれが発生してしまう従来の技術第1の問題が回避される。

【0063】

また、従来の技術において、両ハンダが同時に固化する際の、予測できないそれぞれの接着面に加わる力の偶然の集中によって、ブリッジ状にサブマウントに固定される半導体レーザチップに大きな熱歪みが加わることも無い。結果として、半導体レーザチップに大きな応力・熱歪みが発生してしまう従来の技術における第2の問題点が回避される。

【0064】

また、本実施の形態の半導体発光素子の製造方法において、半導体レーザチップの発光部に隣接する側の電極は、従来同様ハンダにてサブマウントに接着されており、半導体レーザ装置の熱抵抗は、従来のものと同等である。本実施の形態と逆に、発光部に隣接する側の電極を、導電性樹脂で接続する構成とすると、熱抵抗が大きくなり、半導体発光装置の温度特性が悪化してしまう。

【0065】

比較のために、本実施の形態の半導体レーザ装置における導電性樹脂に替えて、第1のハンダと同一の材料を用いた、対照半導体レーザ装置を作製した。サブマウントの端面垂直方向から±2°以内にレーザビーム中心がくることをダイボンディング工程の位置ずれに関する良品条件と規定したとき、本実施の形態の半導体レーザ装置においては、良品の得られる率が98%だったのに対し、対象半導体レーザ装置においては、75%であった。また、それぞれの半導体レーザ装置に、3mW、50℃(初期電流50mA程度)の条件での通電試験を1000時間行ったところ、前者では、駆動電流の上昇がほとんど見られなかったのに対し、後者では、約30%の装置で駆動電流値の20%以上の上昇が観察された。

【0066】

さらに、図2に示したように、半導体レーザチップの正負電極がほぼ同一面上にある場合に限らず、図19に示されるように、発光層に隣接する側と逆側の電極(負電極)が窪んだ面上に設けられていても良い。特に、本実施の形態のように、発光層に隣接する側と逆側の電極の接続に、導電性樹脂を用いたので、この硬度を調整することによって、窪みが大きくても、確実に電気的導通を確保することができるようになる。

【0067】

このように、本実施の形態のサブマウントを用いれば、従来の技術の場合と比較して、半導体レーザ装置の生産性が向上した。さらに、半導体レーザ装置の長期信頼性も向上した。

【0068】

〔実施の形態4〕

図7は、本発明に密接に関連する参考的な実施の形態4の半導体レーザ装置を示す断面図である。図において、40は、本実施の形態の半導体レーザ装置、400はサブマウント、401はサブマウント積載面上の金属パターン間に設けられた溝、402は異方導電性樹脂であり、その他実施の形態1と同様の部分については図1と同一の符号で示した。本実施の形態の半導体レーザ装置の構成は、実施の形態3における導電性樹脂を異方導電性樹脂とした他は、実施の形態3と同様である。溝のサイズは、深さ0.2mm、幅0.1mmとした。

【0069】

ここで、導電性樹脂を異方性とするために、本実施の形態においては、熱硬化性エポキシ樹脂の中に、Ag粒子を数ないし数10wt%配合したものを用いた。これにより、異方導電性樹脂は、荷重を加えずに硬化した場合、金属粉が分散するので、絶縁性となり、所定の荷重を加えて硬化した場合、金属粉同士が接触するので、導電性となる。樹脂の硬化温度は180℃程度とした。また、第1のハンダには融点が156℃であるInを用いた。

【0070】

本実施の形態についても実施の形態1と同様に、半導体レーザチップにおいて、正電極が発光部に隣接する側の電極となり、負電極がその反対側の電極に相当する。また、サブマウントにおいては、正側金属パターンが、正電極に対向する導電膜パターンとなり、負側金属パターンが負電極に対向する導電膜パターンに相当する。

【0071】

次に、本実施の形態の半導体レーザ装置を製造するためのダイボンディング工程について説明する。

【0072】

あらかじめ、図3に示されたのと同様ではあるが、上記溝が設けられたサブマウントを準備する。また、負側の電極パターン上には、第2のハンダに代えて、上記異方導電性樹脂が設けられる。ただし、この段階で、樹脂は未硬化である。

【0073】

次に、サブマウントの温度を上昇させ、ハンダが融解した後、図2に示した半導体レーザチップを、適切にアライメントし、レーザチップ電極形成面とサブマウント積載面とが突き合わされるように、サブマウント上に積載した。このとき、樹脂が拡がり、図7に示されるように、正側のハンダ等に接触した。

【0074】

その後、レーザチップに30gの荷重を加えつつ、ハンダの融点以上の温度である180℃の状態を1分間保持して、ハンダと金属パターンおよび電極とを良くなじませ、また、樹脂を硬化させた。

【0075】

それから、ハンダを固化させ、室温に近い適当な温度まで冷却されたところで、ダイボンディング工程を、終了した。

以上により、本実施の形態の半導体レーザ装置が完成した。

【0076】

本実施の形態の半導体レーザ装置は、第2のハンダに替えて、導電性樹脂を用いたので、従来の技術の問題点が実施の形態3の場合と同様、以下の如く解消されている。

【0077】

上記過程において融解したハンダが固化する際には、既に、導電性樹脂が硬化しており、よって、半導体レーザチップは、第1のハンダの固化に伴って動くことがない。つまり、ハンダ冷却の途中でレーザチップが動き、アライメントずれが発生してしまう従来の技術第1の問題が回避される。

【0078】

また、従来の技術において、両ハンダが同時に固化する際の、予測できないそれぞれの接着面に加わる力の偶然の集中によって、ブリッジ状にサブマウントに固定される半導体レーザチップに大きな熱歪みが加わることも無い。結果として、半導体レーザチップに大きな応力・熱歪みが発生してしまう従来の技術における第2の問題点が回避される。

【0079】

また、本実施の形態の半導体発光素子の製造方法において、半導体レーザチップの発光部に隣接する側の電極は、従来同様ハンダにてサブマウントに接着されており、半導体レーザ装置の熱抵抗は、従来のものと同等である。

【0080】

比較のために、本実施の形態の半導体レーザ装置における第2のハンダを、第1のハンダと同一の材料で構成した、対照半導体レーザ装置を作製した。サブマウントの端面垂直方向から±2°以内にレーザビーム中心がくることをダイボンディング工程の位置ずれに関する良品条件と規定したとき、本実施の形態の半導体レーザ装置においては、良品の得られる率が98%だったのに対し、対象半導体レーザ装置においては、75%であった。また、それぞれの半導体レーザ装置に、3mW、50℃(初期電流50mA程度)の条件での通電試験を1000時間行ったところ、前者では、駆動電流の上昇がほとんど見られなかったのに対し、後者では、約30%の装置で駆動電流値の20%以上の上昇が観察された。

【0081】

このように、本実施の形態のサブマウントを用いれば、従来の技術の場合と比較して、半導体レーザ装置の生産性が向上した。さらに、半導体レーザ装置の長期信頼性も向上した。

【0082】

さらに、図2に示したように、半導体レーザチップの正負電極がほぼ同一面上にある場合に限らず、図19に示されるように、発光層に隣接する側と逆側の電極(負電極)が窪んだ面上に設けられていても良い。特に、本実施の形態のように、発光層に隣接する側と逆側の電極の接続に、導電性樹脂を用いたので、この硬度を調整することによって、窪みが大きくても、確実に電気的導通を確保することができるようになる。

【0083】

また、特に、本実施の形態の半導体発光素子においては、異方導電性樹脂を用い、サブマウント金属膜パターン間に溝を設けたので、樹脂の溝上の領域には荷重が加わらず絶縁性であり、金属パターン上の領域には荷重が加わり導電性となる。よって、負電極と負側金属パターン間には、電気的など導通が確保されるが、図7に示される如く、たとえ樹脂が正電極等と接触したとしても、ショートすることがない。よって、ダイボンディング工程における、ショート発生による生産性の低下を防止することができる。

【0084】

以上、本発明に関連する構成を特定の例を挙げて説明したが、本発明の適用範囲はこれに限られるものではなく、当然ながら、各構成要素をそれぞれ用途を同じくする材料に置換し得るし、他の技術を組み合わせて用いることもできる。

【0085】

上述の絶縁性サブマウント基体は、ダイヤモンド、Si、SiC、cBN、BeO、AlO等の他の絶縁材料や、さらには、ダイヤモンド/Si、SiO/Siに代表されるように、それら各絶縁材料の積層構造からなる、他の絶縁性サブマウント基体に置き換えることができる。

【0086】

また、必ずしもサブマウント基体は絶縁性である必要はなく、正負両電極の間を絶縁する工夫を行ったうえで、導電性サブマウント基体を用いることができる。導電性サブマウント基体としては、Si、Ge、SiC、Cu、CuW、Mo等の材料や、それら各物質の積層構造を用いることができる、

上述の半導体レーザチップは、図2に示した特定の例に限られるものではなく、基板としてGaN、SiC、Si、SiO/サファイア等の他の材料を用いる等の変更が可能であり、また、半導体成長層の材料系として、例えば、InGaAsP系、InGaAlP系、AlGaN系、CdZnSe系等の他のもの用いることも可能である。また、半導体レーザチップを、LED、スーパールミネッセンスダイオード等の他の発光素子チップにも置換し得る。

【0087】

また、上記実施の形態のサブマウントにおいて、各ハンダおよび各金属パターンの形状を、図3に特定の例で示したが、本発明はこれに限られるものではなく、適宜変更され得るものである。例えば、必ずしも、金属パターンがサブマウントのほぼ全面を覆うように設けられる必要はない。また、サブマウント積載面上に、さらに、ワイヤボンディング用のパッド部を設けることや、ダイボンディング時の位置合わせのための印を設けることは、当業者には、容易に想定し得る事項である。あるいは、いわゆるマルチビームレーザのように、3以上の電極を有する半導体レーザチップを積載した半導体レーザ装置にも、上記原理に基づいて、本発明を応用することは、当業者にとって容易に想定し得る。

【0088】

さらに、ハンダ層とサブマウント基体との間には、公知のごとく、種々の膜を介在させることが可能であり、例えば、サブマウントとハンダ間の密着性を向上させるための膜、サブマウントとハンダ間の反応を防止するための膜、さらには、これらの膜の間の密着性を高めたり、酸化を防止するための膜が適宜積層形成させてもよい。上記実施の形態に示した金属パターンAu/Pt/Tiに置換し得るものとして、Pt/Cr、Au/Mo、Au/Pt/Cr、Au/Mo/Ti等も用いることが可能である。ハンダ、絶縁膜、ボンディングパッド、サブマウント基体相互の間にも、同様の目的で、種々の膜を介在させることが想定される。

【0089】

またさらに、図1、3、6に示されたサブマウントの構成によれば、第1ハンダと第2ハンダとの間のスペースには、特別の構造は設けられていないが、ここに、ダイボンディング工程時のショートを防止したり、アライメントずれを防止するために、溝・梨地面・樹脂突起・絶縁体突起等の構造物を設けても良い。

【0090】

上述の各実施の形態においては、半導体レーザ素子用サブマウントについて説明したが、本発明の適用は、これに限られるものでなく、発光素子チップのマウント部材全般に適用できる。すなわち、任意のマウント部材において、発光素子チップのダイボンディングされる部分が、上述の各実施の形態と同様の構成であれば、他の発光素子チップ用マウント部材においても上述同様の効果を奏することは、明白である。したがって、発光素子チップを、サブマウントを用いず直接ステム、フレーム、もしくはパッケージに積載する場合においては、このステム、フレームもしくはパッケージに、上記本発明に関連する構成を適用することができる。

【0091】

〔実施の形態5〕

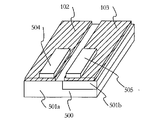

図8は、本発明に密接に関連する参考的な実施の形態5の半導体レーザ装置を示す断面模式図である。図8において、50は本実施の形態の半導体レーザ装置、500は本実施の形態のサブマウント、501a、501bは絶縁体で形成されるサブマウント基体、102は正側金属パターン、103は負側金属パターンであり、504、505は導電性接着剤としてハンダを用いている。ここで501aと501bは、熱伝導率が異なる絶縁体材料で形成されている。図示されるように、サブマウント積載面のハンダおよび金属パターンは、適宜パターン形成されることにより、それぞれが絶縁分離されており、よって、片面に正負電極を有する半導体レーザ素子の積載を可能としていることは、従来の技術と同様である。本実施の形態では、サブマウント基体501aは、その断面図においてL字型をしているが、断面図においてコの字型を形成するように掘り、その中に501bを埋め込んでもよい。

【0092】

図9は、本実施の形態の半導体レーザ装置に用いた、本実施の形態のサブマウントを示す模式図である。各記号は図8と同一である。本実施の形態において、サブマウント基体501aには絶縁体であるAlNを用い、サブマウント基体501bにはAlNより熱伝導率が低い絶縁体であるAl2O3を用い、正側金属パターン102および負側金属パターン103には、Au(0.1μm)/Pt(0.1μm)/Ti(0.1μm)(Au オン Pt オン Ti、以下同様)、ハンダ504および505には融点が217℃であるSnAu(Sn90%、Au10%)ハンダを用いた。サブマウント基体の作成方法の一例として、図10(a)に示すように、サブマウント基体501aをまず、ドライエッチングやウェットエッチング等のエッチング手段、また物理的に研削する手段等を用いで段差を形成したうえで、図10(b)に示すように真空蒸着法、CVD法、スパッタ法、熱転写法、印刷法、焼結法、塗布法等の公知技術を適宜用いて501bを成膜し、図10(c)に示すように研磨により平坦化することにより形成する。そして、図10(d)に示すように正側金属パターン102、負側金属パターン103を、真空蒸着法、CVD法、スパッタ法、熱転写法、印刷法、焼結法、塗布法等の公知技術を適宜用いて成膜する。本実施の形態においては、一例として、サブマウント基体501aと501bを併せた全体のサイズを、長さ2mm×幅1.5mm×高さ0.2mmとし、501bのみの大きさは長さ2mm×幅0.7mm×高さ0.1mmとし、ハンダ間の距離を50μm、ハンダの厚さを1μmとした。

【0093】

上述の構成によって、本半導体レーザチップにおいては、正電極が発光部に隣接する側の電極となり、負電極がその反対側の電極に相当する。また、本サブマウントにおいては、正側金属パターンが、正電極に対向する導電膜パターンとなり、負側金属パターンが負電極に対向する導電膜パターンに相当する。

また、501a、501bは放熱部となるので、放熱効率を高くするため、厚さが20μm以上あるのが好ましい。

【0094】

次に、本実施の形態の半導体レーザ装置を製造するためのダイボンディング工程について説明する。図11は、工程の各過程におけるサブマウント積載面温度Tの変化を示したグラフ(温度プロファイル)である。ここで、Tは、各ハンダの温度に一致している。

〈過程A〉始めに、図9に示した、本実施の形態のサブマウントを、ハンダの融点(Tm=217℃)よりも高い温度であるTp=250℃まで加熱したところ、双方のハンダが融解した。

〈過程B〉図2に示したGaN系半導体レーザチップ200を、適切にアライメントし、レーザチップ電極形成面とサブマウント積載面とが突き合わされるように、サブマウント上に積載した。ここで、アライメントは、次の要領でなされる。正電極203とハンダ504および正側金属パターン102、負電極204とハンダ505および負側金属パターン103が、それぞれ一致するように、すなわち、図8に示されるように、また、半導体レーザチップのストライプ方向が、サブマウントの端面と垂直の関係になり、光出射面がサブマウントの端面とほぼ一致するように、方向および位置併せされる。

次いで、半導体レーザチップに約20gの荷重を加えて、Tp=250℃の状態を30秒間保持し、ハンダと、金属パターンおよび電極とを良くなじませた。

〈過程C〉荷重を加えたまま、加熱を止めた。すると、図中実線で示すように、熱伝導率の大きいサブマウント基体501aに対向するハンダ504は早く冷却され、t1秒で融点Tmまで下がり、固化する。ここで、荷重を加えるのを止めた。その後、図中破線で示すように、t2秒で熱伝導率の小さいサブマウント基体に対向するハンダ505が融点Tmまで下がり、固化する。室温に近い適当な温度まで冷却されたところで、ダイボンディング工程を、終了した。

以上により、図8に示す本実施の形態の半導体レーザ装置が完成した。

【0095】

本実施の形態の半導体レーザ装置は、熱伝導率の異なるサブマウント基体を用いて、ハンダの固まる速度を正電極側と負電極側で異ならせることにより、固化の際に接着面毎にかかる力のバランスを保ちつつ、接着面にかかる力を分散させているので、従来の技術の問題点が以下のように、解消されている。

【0096】

上記過程Bにおいて融解したハンダのうち、発光部に隣接するハンダ504のみが、先にt1秒で固化する。このとき、ハンダ505は、まだ、融解しているので、従来の技術において問題となったような、両方のハンダが同時に固化しようとすることに伴う、各接合面毎に加わる力のアンバランスが生じない。これにより、半導体レーザチップは、ハンダ504の固化に伴って、動くことなく固定される。よって、その後、ハンダ505が固化する際にチップがずれてしまうこともなく、結果として、ハンダ冷却の途中でレーザチップが動き、アライメントずれが発生してしまう従来の技術第1の問題が回避される。

【0097】

また、従来の技術において、両ハンダが同時に固化する際の、予測できないそれぞれの接着面に加わる力の、偶然の集中によって、ブリッジ状にサブマウントに固定される半導体レーザチップに大きな熱歪みが加わることも無い。さらに、先にハンダ504側が固定された後、ハンダ505側の固定に至るまでの間に、チップに引き起こされる歪みが緩和されている。結果として、半導体レーザチップに大きな応力・熱歪みが発生してしまう従来の技術における第2の問題点が回避される。

【0098】

本実施の形態の半導体発光素子の製造方法においては、過程Bの温度Tが、ハンダ504、505の融点より若干高い温度に設定されている。これは、電極と金属パターンの接合を、最適な条件で行うためのもので、これにより、それらとハンダの間での合金化が適正に進み、また、ハンダが厚すぎて介在されることがなくなり、よって、熱抵抗を最小限とした接合が可能になる。

【0099】

また、本実施の形態の半導体レーザ装置では、発光部に隣接した電極が正電極である。レーザーチップの温度上昇による特性劣化を押さえるためには発光部に隣接した正電極からの放熱が良好な方がこのましい。そのため、正電極に接するハンダ504が、熱伝導率の大きい方のサブマウント基体に配置されている方が好ましい。さらに、正電極と負電極とで電気抵抗率が異なる場合はそれによっても各電極での発熱量が異なるため、その点も考慮するのが好ましい。

【0100】

比較のために、本実施の形態の半導体レーザ装置における、サブマウント基体501aおよび501bを同一の材料で構成した、対照半導体レーザを作成した。サブマウントの端面垂直方向から+−2°以内にレーザビーム中心がくることをダイボンディング工程の位置ずれに関する良品条件として規定したとき、本実施の形態の半導体レーザ装置においては。良品の得られる率が98%であったのに対し、対照半導体レーザにおいては、78%であった。また、それぞれの半導体レーザ装置に、3mW、70℃(初期電流90mA程度)の条件での通電試験を1000時間行ったところ、前者では、駆動電流の上昇がほとんど見られなかったのに対し、後者では、約40%の装置で駆動電流値の20%以上の上昇が観察された。このように、従来の技術を用いた半導体レーザ装置と比較して、ダイボンディング工程の生産性の向上と、装置寿命特性の向上が確認された。

また、本実施の形態のサブマウントによれば、従来の技術のものと比較して、半導体レーザ装置の生産性を向上せしめ、装置寿命特性を改善させる効果を奏する。

【0101】

本実施の形態においては、サブマウント基体501aおよび501bがどちらも絶縁体であったが、熱伝導率の異なる材料の組合わせであれば、絶縁体と導電体の組合わせでもよいことは言うまでもない。例えば、図12(a)に示すように金属で形成されるサブマウント基体501aを途中まで形成した上に、真空蒸着法、CVD法、スパッタ法、熱転写法、印刷法、焼結法、塗布法等の公知技術を適宜用いて、絶縁膜で形成されるサブマウント基体501bを成膜し、図12(b)に示すように、ドライエッチングやウェットエッチング等のエッチング手段、また物理的に研削する手段等の公知技術を適宜用いてを用いで段差形成を行い、図12(c)に示すように、めっき法によって段差部分へサブマウント基体501aを埋め込み、図12(d)に示すように電極を形成することでも形成することができる。

【0102】

また、導電体を用いる場合は、金属パターンを兼ねることも可能であるし、さらにはマウント部材のレーザーチップに面した側からだけではなく、側面や裏面からもステム、パッケージ、外部リード等へ直接接続が可能となり、放熱効率のアップやシステム全体の簡略化へつながる。

また、本実施の形態では504、505には同一のハンダを用いたが、504側が先に固化するように設計されていれば異なるハンダを用いてもいいことは言うまでもない。

また、本実施の形態では放熱部に直接導電性接着剤が形成されているが、導電性を保つ程度であれば間に絶縁層が形成されていても良い。

【0103】

[実施の形態6]

本発明に密接に関連する参考的な実施の形態6によれば、実施の形態5のバリエーション実施の形態5のサブマウント基体以外にも、異なる熱伝導率をもった材料を組合わせた、図13(a)、(b)に示すような形のサブマウント基体を用いても同様の効果が得られる。

【0104】

例えば、図13(a)のサブマウント基体は熱伝導率のことなる立方体あるいは直方体の二種類材料をある一面で接合させたものである。この場合、図8に比べ、501bの表面積を大きくできるので、熱を効果的に発散することができる。これは、2種材料を接着剤で接着してもよいし、一方の材料の上に、真空蒸着法、CVD法、スパッタ法、メッキ法、熱転写法、印刷法、焼結法等の公知技術を用いて堆積してもよい。本実施の形態においては、一例として、サブマウント基体501aには導電体であるCuを用い、サブマウント基体501bにはCuより熱伝導率が低い絶縁体であるAl2O3を用い、正側金属パターンおよび負側金属パターン103には、Au(0.1μm)/Pt(0.1μm)/Ti(0.1μm)、導電性接着剤としてハンダ504および505には融点が156℃であるInハンダを用いた。また本実施の形態においては、一例として、サブマウント基体501a、501bの大きさはそれぞれ長さ2mm×幅1mm×厚さ0.2mmとし、接着剤で接着した。

【0105】

また、図13(b)のサブマウント基体は、501bが501aの裏面まで覆う場合である。この場合、図8に比べ501bの表面積を大きくできるので、熱を効果的に発散することができる。これは、熱伝導率の異なる2種材料を接着剤で接着してもよいし、一方の材料の上に、真空蒸着法、CVD法、スパッタ法、メッキ法、熱転写法、印刷法、焼結法等の公知技術を用いて堆積してもよい。本実施の形態で一例として、サブマウント基体501aには絶縁体であるcBNを用い、サブマウント基体501bにはcBNより熱伝導率が低い導電体であるFeを用い、正側金属パターン102および負側金属パターン103には、Au(0.1μm)/Pt(0.1μm)/Ti(0.1μm)、導電性接着剤としてハンダ504および505には融点が156℃であるInハンダを用いた。また本実施の形態においては、一例として、サブマウント基体501aは長さ2mm×幅1.5mm×厚さ0.2mmの上に、長さ2mm×幅0.7mm×厚さ0.1mmの凹部を持ち、501bは501a上の凹部から裏面にかけて厚さ0.1mmで覆うものとする。501a上の凹部はドライエッチングやウェットエッチング等のエッチング手段、また物理的に研削する手段等の公知技術を用いて形成し、その凹部から裏面にかけて表面を導電化処理(銀ペースト塗布等)をした後、Feメッキにより501bを形成する。

【0106】

以上図13(a)、(b)のサブマウント基体においても、実施の形態5と同様に、サブマウント基体501aおよび501bが熱伝導率が異なる絶縁体同志であってもよいし、熱伝導率の異なる材料の組合わせであれば、絶縁体と導電体の組合わせでもよいことは言うまでもない。

また、501a、501bは放熱部となるので、放熱効率を高くするため、厚さが20μm以上あるのが好ましい。

また、サブマウント基体に導電体を用いる場合は、金属パターンを兼ねることも可能であるし、さらにはマウント部材のレーザーチップに面した側からだけではなく、側面や裏面からもステム、パッケージ、外部リード等へ直接接続が可能となり、放熱効率のアップやシステム全体の簡略化へつながる。

【0107】

上記、実施の形態5、2に示したサブマウントにおいては、図8、図13に示すように、サブマウント基体の表面がほぼ平面であるため、対面するレーザーチップの正および負の電極がほぼ平面上にある場合に容易にダイボンドできるが、もし対面するレーザーチップの正負の電極に高低差がある場合には、501aまたは501bの厚さによって任意に調整することが可能である。

【0108】

〔実施の形態7〕

本発明に密接に関連する参考的な実施の形態7の構成は、サブマウントの形と材料が異なる他は、実施の形態5、6と同様である。本実施の形態を図14に示す。60は本実施の形態の半導体レーザ装置、600はサブマウント、サブマウント基体には熱伝導率のことなる二種類の導電性材料を用いた601a、601bを絶縁体601cを介して接合させたものを用いた。本実施の形態ではサブマウント断面図における絶縁体はL字型をしているが、断面図でコの字型、平面図ではサブマウント基体601bの周囲を絶縁体601cが覆い、絶縁体601cの周囲をサブマウント基体601bを覆うような構造になっていてもよい。

【0109】

本実施の形態においては一例として、サブマウント基体601aには導電体であるAgを用い、サブマウント基体601bにはAgより熱伝導率の低い導電体であるAlを用い、絶縁体601cにはSiO2を用い、正側金属パターン102および負側金属パターン103には、Au(0.1μm)/Pt(0.1μm)/Ti(0.1μm)、導電性接着剤としてハンダ504および505には融点が217℃であるSnAu(Sn90%、Au10%)ハンダを用いた。これは、サブマウント基体601aをまず、ドライエッチングやウェットエッチング等のエッチング手段、また物理的に研削する手段等の公知技術を用いて段差を形成したうえで、601c、601bを順次成膜して形成する。サブマウント基体601bおよび、正側金属パターン102、負側金属パターン103の成膜は、真空蒸着法、CVD法、スパッタ法、メッキ法、熱転写法、印刷法、焼結法等の公知技術を適宜用いて作成することができる。例えば、図15(a)に示すように、サブマウント基体601a上にフォトレジスト606でパターン形成した後、エッチングを行い段差を形成し、図15(b)に示すようにフォトレジスト606を除かずに、601cのSiO2をCVD法で1μm堆積し、さらに601bのAlをスパッタ法で0.5μm堆積した後にレジストおよび、レジスト上のSiO2、Alをウェットエッチングで除去した後(リフトオフ法)、図15(c)に示すように凹部に601bのAlメッキを行い、図15(d)に示すように、その上に正側金属パターン102、負側金属パターン103を形成することで、作ることができる。

【0110】

本実施の形態においては、一例として、サブマウント基体601aと601bを併せた全体のサイズを、長さ2mm×幅1.5mm×高さ0.2mmとし、601bのみの大きさは長さ2mm×幅0.7mm×高さ0.1mmとし、ハンダ間の距離を50μm、ハンダの厚さを1μmとした。

【0111】

また、601a、601bは放熱部となるので、放熱効率を高くするため、厚さが20μm以上あるのが好ましい。601cの膜厚は、601aと601bの間の絶縁性を保てるだけの膜厚があればよく、例えばSiO2では最低0.1μm程度あれば十分である。絶縁耐厚の大小は、絶縁膜の種類、膜質により異なるため、必要最低限の膜厚は、使用する膜により適宜変更される。

【0112】

次に、実施の形態5と同様にして、本実施の形態の半導体レーザ装置を製造するためのダイボンディング工程を行った。工程の各過程におけるサブマウント積載面温度Tの変化(温度プロファイル)は実施の形態5で説明したのと同様である。

以上で、本実施の形態の半導体レーザ装置が完成した。

【0113】

本実施の形態の半導体レーザ装置は、熱伝導率の異なるサブマウント基体を用いて、ハンダの固まる速度を正電極側と負電極側で異ならせることにより、固化の際に接着面毎にかかる力のバランスを保ちつつ、接着面にかかる力を分散させているので、従来の技術の問題点が以下のように、解消されている。

【0114】

上記実施の形態5及び図11で記した、過程Bにおいて融解したハンダのうち、発光部に隣接するハンダ504のみが、t1秒で固化する。このとき、ハンダ505は、まだ、融解しているので、従来の技術において問題となったような、両方のハンダが同時に固化しようとすることに伴う、各接合面毎に加わる力のアンバランスが生じない。これにより、半導体レーザチップは、ハンダ504の固化に伴って、動くことなく固定される。よって、その後、ハンダ505が固化する際にチップがずれてしまうこともなく、結果として、ハンダ冷却の途中でレーザチップが動き、アライメントずれが発生してしまう従来の技術第1の問題が回避される。

【0115】

また、従来の技術において、両ハンダが同時に固化する際の、予測できないそれぞれの接着面に加わる力の、偶然の集中によって、ブリッジ状にサブマウントに固定される半導体レーザチップに大きな熱歪みが加わることも無い。さらに、先にハンダ504側が固定された後、ハンダ505側の固定に至るまでの間に、チップに引き起こされる歪みが緩和されている。結果として、半導体レーザチップに大きな応力・熱歪みが発生してしまう従来の技術における第2の問題点が回避される。

【0116】

本実施の形態についても実施の形態5と同様に、半導体レーザチップにおいて、正電極が発光部に隣接する側の電極となり、負電極がその反対側の電極に相当する。また、サブマウントにおいては、正側金属パターンが、正電極に対向する導電膜パターンとなり、負側金属パターンが負電極に対向する導電膜パターンに相当する。

【0117】

また、本実施の形態の半導体レーザ装置では、発光部に隣接した電極が正電極である。レーザーチップの温度上昇による特性劣化を押さえるためには発光部に隣接した正電極からの放熱が良好な方がこのましい。そのため、正電極に接するハンダ504が、熱伝導率の大きい方のサブマウント基体に配置されている方が好ましい。さらに、正電極と負電極とで電気抵抗率が異なる場合はそれによっても各電極での発熱量が異なるため、その点も考慮するのが好ましい。

【0118】

比較のために、本実施の形態の半導体レーザ装置におけるサブマウント基体601aおよび601bを同一の材料で構成した、対照半導体レーザ装置を作製した。サブマウントの端面垂直方向から±2°以内にレーザビームの中心がくることをダイボンディング工程の位置ずれに関する良品条件と規定したとき、本実施の形態の半導体レーザ装置においては、良品の得られる率が98%だったのに対し、対照半導体レーザ装置においては、75%であった。また、それぞれの半導体レーザ装置に、5mW、60℃(初期電流80mA程度)の条件での通電試験を1000時間行ったところ、前者では、駆動電流の上昇がほとんど見られなかったのに対し、後者では、約70%の装置で駆動電流値の20%以上の上昇が観察された。このように、従来の技術を用いた半導体レーザ装置と比較して、ダイボンディング工程の生産性の向上と、装置寿命特性の向上が確認された。

【0119】

また、本実施の形態のサブマウントによれば、従来の技術のものと比較して、半導体レーザ装置の生産性を向上せしめ、装置寿命特性を改善させる効果を奏する。本実施の形態においては、サブマウント基体601aおよび601bともに導電体を用いているため、金属パターンを兼ねることも可能であるし、さらにはマウント部材のレーザーチップに面した側からだけではなく、側面や裏面からもステム、パッケージ、外部リード等へ直接接続が可能となり、放熱効率のアップやシステム全体の簡略化へつながる。また、一般的に導電体には熱伝導率の高い金属が多いため、材料選択の幅が広がり、より最適な材料を選ぶことができる。

【0120】

[実施の形態8]

本発明に密接に関連する参考的な実施の形態8によれば、実施の形態7のバリエーション実施の形態7のサブマウント基体以外にも、異なる熱伝導率をもった導電体材料を組合わせた、図16(a)、(b)に示すような形のサブマウント基体を用いても同様の効果が得られる。

【0121】

まず、図16(a)のサブマウント基体は熱伝導率の異なる立方体あるいは直方体の二種類の導電体を絶縁体601cを介して一面で接合させたものである。この場合、図14に比べ、601bの表面積を大きくできるので、熱を効果的に発散することができる。これは、各材料を接着剤で接着してもよいし、一方の材料の上に、真空蒸着法、CVD法、スパッタ法、メッキ法、熱転写法、印刷法、焼結法等の公知技術を用いて堆積してもよい。本実施の形態においては、一例として、サブマウント基体601aには導電体であるCuを用い、サブマウント基体601bにはCuより熱伝導率が低い導電体であるFeを用い、絶縁体601cにはSiO2を用い、正側金属パターン102および負側金属パターン103には、Au(0.1μm)/Mo(0.1μm)、導電性接着剤としてハンダ504および505には融点が156℃であるInハンダを用いた。また本実施の形態においては、一例として、サブマウント基体601a、601bの大きさはそれぞれ長さ2mm×幅1mm×厚さ0.2mmとし、601aまたはbの一面にCVD法でSiO2膜を1μm堆積した後、接着剤で接着した。この接着剤が十分な絶縁性を持つ場合には、601cを兼ねる事も可能である。

【0122】

また、図16(b)のサブマウント基体は、601bが601cを介して601aの裏面まで覆う場合である。この場合、図14に比べ601bの表面積を大きくできるので、熱を効果的に発散することができる。これは、熱伝導率の異なる各材料を接着剤で接着してもよいし、一方の材料の上に、真空蒸着法、CVD法、スパッタ法、メッキ法、熱転写法、印刷法、焼結法等の公知技術を用いて堆積してもよい。本実施の形態で一例として、サブマウント基体601aには導電体であるCuを用い、サブマウント基体601bにはCuより熱伝導率が低い導電体であるFeを用い、絶縁体601cにはSiO2を用い、正側金属パターン102および負側金属パターン103には、Au(0.1μm)/Mo(0.03μm)、ハンダ504および505には融点が156℃であるInハンダを用いた。また本実施の形態においては、一例として、サブマウント基体601aは長さ2mm×幅1.5mm×厚さ0.2mmの上に、長さ2mm×幅0.7mm×厚さ0.1mmの凹部を持ち、601bは601a上の凹部から裏面にかけて厚さ約0.1mmで覆うものとする。601a上の凹部はドライエッチングやウェットエッチング等のエッチング手段、また物理的に研削する手段等の公知技術を用いて形成し、その凹部から裏面にかけてCVD法でSiO2膜1μmを堆積した後、SiO2表面を導電化処理(銀ペースト塗布等)をした後、Feメッキにより601bを形成する。

【0123】

また、601a、601bは放熱部となるので、放熱効率を高くするため、厚さが20μm以上あるのが好ましい。601cの膜厚は、601aと601bの間の絶縁性を保てるだけの膜厚があればよく、例えばSiO2では最低0.1μm程度あれば十分である。絶縁耐厚の大小は、絶縁膜の種類、膜質により異なるため、必要最低限の膜厚は、使用する膜により適宜変更される。

【0124】

本実施の形態においては、サブマウント基体に導電体を用いているので、金属パターンを兼ねることも可能であるし、さらにはマウント部材のレーザーチップに面した側からだけではなく、側面や裏面からもステム、パッケージ、外部リード等へ直接接続が可能となり、放熱効率のアップやシステム全体の簡略化へつながる。

【0125】

上記、図14、図16においては、サブマウント基体の表面がほぼ平面であるため、対面するレーザーチップの正および負の電極がほぼ平面上にある場合に容易にダイボンドできるが、もし対面するレーザーチップの正負の電極に高低差がある場合には、601aまたは601bの厚さによって調整することが可能である。

【0126】

また、実施の形態5〜8における温度プロファイルを図12で説明したが、これは、理想的な温度変化を示したものであって、実際には、過程Bで厳密に一定温度が保持される必要があるものでもなく、それぞれの過程で徐々に温度変化があるようなプロファイルであってもかまわない。

【0127】

上記実施の形態7、8においては、サブマウントの101aと101bを熱伝導率の異なる金属で形成したが、絶縁膜101cの熱伝導率や厚さを考慮すれば、熱伝導率の同じ金属で形成した場合にも、本発明と同様の効果が得られる。

【0128】

例えば、図14や図16(b)において、101aと101bに銅を用い、101cとして銅の千分の一程度の熱伝導率であるアニリン樹脂やエポキシ樹脂あるいはシリコン樹脂(いずれも熱硬化性樹脂)を厚さ100μm形成した場合、正電極101aにおける熱伝導は不電極側の101bより大きくなるため、正、負電極側での導電性接着剤の固化するタイミングがずれることとなる。この場合、金属と絶縁物の熱伝導率の比は、大きい方が固化のタイミングをずらしやすいため好ましく、10以上あるのが好ましい。同様に絶縁物の膜厚が厚い方が好ましく、10〜150μmあるのが好ましい。

【0129】

さらに加えて、101aと101bの大きさを、101aが101bに比べて十分大きくしてやることで、放熱効果に差を生じさせれば、より大きな効果が得られる。

【0130】

本方法は前記熱伝導率の異なる金属を用いる場合にもより効果を高めるために有効である。

【0131】

〔実施の形態9〕

図17は、本発明に密接に関連する参考的な実施の形態9の半導体レーザ装置を示す断面図である。これは、実施の形態5の図8に記載の装置において、サブマウントの表面に溝が形成されている点、及び導電性接着剤が異方導電性樹脂である点が異なる。図において、70は、本実施の形態の半導体レーザ装置、700はサブマウント、703は実施の形態5のサブマウントの積載面上の金属パターン間に設けられた溝、702は異方導電性樹脂であり、その他実施の形態5と同様の部分については図8と同一の符号で示した。

【0132】

本実施の形態においては、実施の形態5と同様にサブマウント基体701aには絶縁体であるAlNを用い、サブマウント基体701bにはAlNより熱伝導率が低い絶縁体であるAl2O3を用い、正側金属パターン102および負側金属パターン103には、Au(0.1μm)/Pt(0.1μm)/Ti(0.1μm)(Au オン Pt オン Ti、以下同様)、異方導電性接着剤として702には異方導電性樹脂を用いた。本実施の形態においては、一例として、サブマウント基体701aと701b全体のサイズを、長さ2mm×幅1.5mm×高さ0.2mmとし、701bのみの大きさは長さ2mm×幅0.7mm×高さ0.1mmとし、異方導電性樹脂の厚さを1μmとした。また、溝のサイズは、深さ0.1mm、幅0.1mmとした。

【0133】

ここで、導電性樹脂を異方性とするために、本実施の形態においては、熱硬化性エポキシ樹脂の中に、Ag粒子を数ないし数10wt%配合したものを用いた。これにより、異方導電性樹脂は、荷重を加えずに硬化した場合、金属粉が分散するので、絶縁性となり所定の荷重を加えて硬化した場合、金属粉同士が接触するので、導電性となる。樹脂の硬化温度は180℃程度とした。

【0134】

本実施の形態についても実施の形態5と同様に、半導体レーザチップにおいて、正電極が発光部に隣接する側の電極となり、負電極がその反対側の電極に相当する。また、サブマウントにおいては、正側金属パターンが、正電極に対向する導電膜パターンとなり、負側金属パターンが負電極に対向する導電膜パターンに相当する。

【0135】

また、本実施の形態の半導体レーザ装置では、発光部に隣接した電極が正電極である。レーザーチップの温度上昇による特性劣化を押さえるためには発光部に隣接した正電極からの放熱が良好な方がこのましい。そのため、正電極が、熱伝導率の大きい方のサブマウント基体に対応して配置されている方が好ましい。さらに、正電極と負電極とで電気抵抗率が異なる場合はそれによっても各電極での発熱量が異なるため、その点も考慮するのが好ましい。

【0136】

次に、本実施の形態の半導体レーザ装置を製造するためのダイボンディング工程を行った。工程の各過程におけるサブマウント積載面温度Tの変化(温度プロファイル)を図18に示す。ここで、Tは異方導電性樹脂の温度に一致している。

【0137】

あらかじめ、図9に示されたのと同様ではあるが、上記溝が設けられたサブマウントを準備する。

まず、サブマウント電極上に上記異方導電性樹脂を配置する。ただし、この段階で、樹脂は未硬化である。次に図2に示した半導体レーザチップを、適切にアライメントし、レーザチップ電極形成面とサブマウント積載面とが突き合わされるように、サブマウント上に積載し、樹脂が拡がった。このとき、樹脂の粘度等によっては、正電極側と負電極側とが接触しない場合もあるが、本実施の形態では図17に示されるように、正電極側および負電極側の樹脂が接触し、溝内に入り込んだ例で説明する。

【0138】

〈過程A〉レーザチップに30gの荷重を加えつつ、サブマウントの温度を上昇させた。まず、実線で示すように、熱伝導率が高いサブマウント基体701a上の異方導電性樹脂がt1秒で硬化温度Ts=180℃に達し、硬化する。

〈過程B〉荷重を加えるのをやめ、加熱を続ける。次に熱伝導率が低いサブマウント基体701b上の異方導電性樹脂がt2秒で硬化温度Tsに達し、硬化する。この後硬化温度より若干高い温度Tp=200℃で30秒保持し、硬化反応を完全に進行させた。

〈過程C〉室温に近い適当な温度まで冷却されたところで、ダイボンディング工程を、終了した。

以上により、本実施の形態の半導体レーザ装置が完成した。

【0139】

本実施の形態の半導体レーザ装置は、ハンダに替えて、異方導電性樹脂を用いたので、従来の技術の問題点が実施の形態5の場合と同様、以下の如く解消されている。

【0140】

上記過程において熱伝導率の低い材料のサブマウント基体701bに接する側の異方導電性樹脂が固化する際には、既に、熱伝導率の高い材料のサブマウント基体701aに接する側の異方導電性樹脂が硬化しており、よって、半導体レーザチップは、第1の導電性樹脂の固化に伴って動くことがない。つまり、ハンダ冷却の途中でレーザチップが動き、アライメントずれが発生してしまう従来の技術第1の問題が回避される。

【0141】

また、従来の技術において、両ハンダが同時に固化する際の、予測できないそれぞれの接着面に加わる力の偶然の集中によって、ブリッジ状にサブマウントに固定される半導体レーザチップに大きな熱歪みが加わることも無い。結果として、半導体レーザチップに大きな応力・熱歪みが発生してしまう従来の技術における第2の問題点が回避される。

【0142】

さらに、半導体レーザチップの正負電極がほぼ同一面上にある場合に限らず、発光層に隣接する側と逆側の電極(負電極)が窪んだ面上に設けられていても良い。特に、本実施の形態では、電極の接続に、導電性樹脂を用いたので、正電極側と負電極側で、異なる硬度の導電性樹脂を用いれば、窪みが大きくても、確実に電気的導通を確保することができるようになる。

【0143】

また、特に、本実施の形態の半導体発光素子においては、異方導電性樹脂を用い、サブマウント金属膜パターン間に溝を設けたので、樹脂の溝上の領域には荷重が加わらず絶縁性であり、金属パターン上の領域には荷重が加わり導電性となる。よって、負電極と負側金属パターン間には、電気的な導通が確保されるが、図17に示される如く、たとえ樹脂が正電極等と接触したとしても、ショートすることがない。よって、ダイボンディング工程における、ショート発生による生産性の低下を防止することができる。

【0144】

比較のために、本実施の形態の半導体レーザ装置におけるサブマウント基体701aおよび701bを同一の材料で構成した、対照半導体レーザ装置を作製した。サブマウントの端面垂直方向から±2°以内にレーザビーム中心がくることをダイボンディング工程の位置ずれに関する良品条件と規定したとき、本実施の形態の半導体レーザ装置においては、良品の得られる率が98%だったのに対し、対照半導体レーザ装置においては、75%であった。また、それぞれの半導体レーザ装置に、5mW、50℃(初期電流50mA程度)の条件での通電試験を1000時間行ったところ、前者では、駆動電流の上昇がほとんど見られなかったのに対し、後者では、約30%の装置で駆動電流値の20%以上の上昇が観察された。このように、従来の技術を用いた半導体レーザ装置と比較して、ダイボンディング工程の生産性の向上と、装置寿命特性の向上が確認された。

【0145】

本実施の形態においては、実施の形態5に示した、図8及び9の構造のマウント部材を用いて説明したが、これを、実施の形態6〜8で示した図13、14、16の様な、他のマウント部材と置き換えても同様の効果が得られる。

【0146】

以上、実施の形態5ないし9によって、本発明に関連する構成を特定の例を挙げて説明したが、本発明の適用範囲はこれに限られるものではなく、当然ながら、各構成要素をそれぞれ用途を同じくする材料に置換し得るし、他の技術を組み合わせて用いることもできる。

【0147】

絶縁性サブマウント基体は、上述の材料以外にも、ダイヤモンド、Si、SiC、BeO等の他の絶縁材料や、さらには、ダイヤモンド/Si、SiO2/Siに代表されるように、それら各絶縁材料の積層構造からなる、他の絶縁性サブマウント基体に置き換えることができる。

導電性サブマウント基体としては、上述の材料以外にも、Si、Ge、SiC、CuW、Mo等の材料や、それら各物質の積層構造を用いることができる、

上述の半導体レーザチップは、図2に示した特定の例に限られるものではなく、基板としてGaN、SiC、Si、、SiO2/サファイア等の他の材料を用いる等の変更が可能であり、また、半導体成長層の材料系として、例えば、InGaAsP系、InGaAlP系、AlGaN系、CdZnSe系等の他のもの用いることも可能である。また、半導体レーザチップを、LED、スーパールミネッセンスダイオード等の他の発光素子チップにも置換し得る。

【0148】

また、上記実施の形態5ないし9のサブマウントにおいて、各導電性接着剤および各金属パターンの形状を、図9に特定の例で示したが、本発明はこれに限られるものではなく、適宜変更され得るものである。例えば、必ずしも、金属パターンがサブマウントのほぼ全面を覆うように設けられる必要はない。また、サブマウント積載面上に、さらに、ワイヤボンディング用のパッド部を設けることや、ダイボンディング時の位置合わせのための印を設けることは、当業者には、容易に想定し得る事項である。あるいは、いわゆるマルチビームレーザのように、3以上の電極を有する半導体レーザチップを積載した半導体レーザ装置にも、上記原理に基づいて、本発明を応用することは、当業者にとって容易に想定し得る。

【0149】

さらに、ハンダ層とサブマウント基体との間には、公知のごとく、種々の膜を介在させることが可能であり、例えば、サブマウントとハンダ間の密着性を向上させるための膜、サブマウントとハンダ間の反応を防止するための膜、さらには、これらの膜の間の密着性を高めたり、酸化を防止するための膜が適宜積層形成させてもよい。上記実施の形態に示した金属パターンに置換し得るものとして、Au/Pt/Ti、Pt/Cr、Au/Mo、Au/Pt/Cr、Au/Mo/Ti等も用いることが可能である。導電性接着層、絶縁膜、ボンディングパッド、サブマウント基体相互の間にも、同様の目的で、種々の膜を介在させることが想定される。

【0150】

またさらに、図8、9、13、14、16に示されたサブマウントの構成によれば、ハンダ504とハンダ505との間のスペースには、特別の構造は設けられていないが、ここに、ダイボンディング工程時のショートを防止したり、アライメントずれを防止するために、溝・梨地面・樹脂突起・絶縁体突起等の構造物を設けても良い。

【0151】

上述の実施の形態5ないし9においては、半導体レーザ素子用サブマウントについて説明したが、本発明の適用は、これに限られるものでなく、発光素子チップのマウント部材全般に適用できる。すなわち、任意のマウント部材において、発光素子チップのダイボンディングされる部分が、上述の各実施の形態と同様の構成であれば、他の発光素子チップ用マウント部材においても上述同様の効果を奏することは、明白である。したがって、発光素子チップを、サブマウントを用いず直接ステム、フレーム、もしくはパッケージに積載する場合においては、このステム、フレームもしくはパッケージに、上記本発明に関連する構成を適用することができる。

【0152】

【発明の効果】

本発明によれば、上記構成により、ダイボンディング工程時におけるアライメントずれが防止され、また、ダイボンディング工程により引き起こされる半導体発光素子チップ内部の応力・熱歪みを削減できる。これにより、半導体発光装置のダイボンディング工程歩留まりが改善され、また、寿命特性も向上する。

【図面の簡単な説明】

【図1】本発明の実施の形態1の半導体レーザ装置を示す、模式断面図である。

【図2】本発明の実施の形態1の半導体レーザチップを示す、模式断面図である。

【図3】本発明の実施の形態1のサブマウントを示す、模式図である。

【図4】本発明の実施の形態1のダイボンディング工程における温度プロファイルを示すグラフである。

【図5】本発明の実施の形態2のダイボンディング工程における温度プロファイルを示すグラフである。

【図6】本発明に密接に関連する参考的な実施の形態3の半導体レーザ装置を示す、模式断面図である。

【図7】本発明に密接に関連する参考的な実施の形態4の半導体レーザ装置を示す、模式断面図である。

【図8】本発明に密接に関連する参考的な実施の形態5の半導体レーザ装置(本発明のサブマウントを含む)を示す、模式断面図である。

【図9】本発明に密接に関連する参考的な実施の形態5のサブマウントを示す、模式図である。

【図10】本発明に密接に関連する参考的な実施の形態5のサブマウントの製造方法を示すフローチャート図である。

【図11】本発明に密接に関連する参考的な実施の形態5のサブマウントの製造方法を示すフローチャート図である。

【図12】本発明の実施の形態のダイボンディング工程における温度プロファイルを示すグラフである。

【図13】本発明に密接に関連する参考的な実施の形態6の半導体レーザ装置を示す、模式図である。

【図14】本発明の実施の形態7の半導体レーザ装置を示す、模式断面図である。

【図15】本発明に密接に関連する参考的な実施の形態7のサブマウントの製造方法を示すフローチャート図である。

【図16】本発明に密接に関連する参考的な実施の形態8の半導体レーザ装置を示す、模式断面図である。

【図17】本発明に密接に関連する参考的な実施の形態9の半導体レーザ装置を示す、模式断面図である。

【図18】本発明に密接に関連する参考的なの実施の形態9のダイボンディング工程における温度プロファイルを示すグラフである。

【図19】従来の技術の半導体レーザ装置を示す模式断面図である。

【符号の説明】

10、30、40、50、60、70 半導体レーザ装置

100、300、400、500、600、700 サブマウント

101、501a、501b、601a、601b、701 サブマウント基体

102 正側金属パターン

103 負側金属パターン

104 第1のハンダ

105 第2のハンダ

200 GaN系半導体レーザチップ

201 サファイア基板

202 半導体成長層

203 正電極

204 負電極

301 導電性樹脂

401 溝

402 異方導電性樹脂

504、505 ハンダ

601c 絶縁体

606 フォトレジスト

702 異方導電性樹脂

703 溝[0001]

BACKGROUND OF THE INVENTION

The present invention uses a semiconductor light emitting element chip having a plurality of electrodes on one side. Half Conductor light emitting device Set Manufacturing method To the law Related.

[0002]

[Prior art]

GaN-based semiconductors are attracting attention as materials for realizing light-emitting elements in the ultraviolet or green region, and among them, it is desired to put into practical use a semiconductor laser device that oscillates at a shorter wavelength than before. . A feature of GaN-based semiconductors is that sapphire, which is an insulator, is used for the substrate. Therefore, in a light-emitting element chip using such a semiconductor, both positive and negative electrodes are formed on the epi layer side, unlike before. It is usual. Therefore, the GaN-based semiconductor laser chip is different from the conventional semiconductor laser chip in which only one electrode is formed on the epi layer side in order to perform the junction bonding die bonding with the epi layer side down. Mounting method is required.

[0003]

FIG. 19 shows an example of a semiconductor laser device using such a technique disclosed in Japanese Patent Laid-Open No. 7-235729. In the figure, 1 is a submount substrate, 2 is a metal pattern provided on the submount mounting surface, 3 is solder, 4 is a GaN-based semiconductor laser chip body, and 5 is provided on the GaN-based semiconductor laser chip epilayer side. Positive and negative electrodes. In this example, an insulating submount is used, and a metal film pattern corresponding to the positive and negative electrodes of the semiconductor laser is provided on the upper surface of the submount, and each is joined to the positive and negative electrodes of the semiconductor laser by soldering and junction-down is performed. Die bonding is realized.

[0004]

Here, die bonding is generally the following process. Usually, the solder is provided in advance on the submount. This is heated above the melting point, the laser chip aligned at a predetermined position is pressed against the melted solder, and then the solder is cooled and solidified. As a result, the laser chip and the submount are bonded with good thermal conductivity.

[0005]

[Problems to be solved by the invention]

In a semiconductor laser chip having positive and negative electrodes on one side as shown in the prior art, as shown in FIG. 19, the positive and negative electrodes cannot be soldered and joined to the submount in a bridge shape. . This causes the following problems that could not occur in the conventional semiconductor laser chip in which only one electrode is formed on the epi layer side.

[0006]

In the die bonding process, when the molten solder is cooled, the solidification and alloying of the solder does not necessarily proceed uniformly in each part, so the volume change and surface tension of the solder part vary from region to region. A complex force is applied to the bonding surface. As shown in FIG. 19, in the semiconductor laser device in which the bonding surface is divided on both the positive and negative sides, the balance of the force applied to each bonding surface is lost, so that the laser chip moves during cooling and misalignment occurs. Resulting in. Actually, according to the experimental knowledge of the present inventor, the probability of occurrence of misalignment in the semiconductor laser device shown in FIG. 19 is higher than that in a conventional semiconductor laser in which only one electrode is formed on the epilayer side. About 5 times higher. Such misalignment not only causes a problem in the optical characteristics of the semiconductor laser device, i.e., the laser beam emission direction, but also has a positive / negative electrode formed on one side. It also caused a problem of leakage. This is the first problem in the conventional semiconductor laser device.

[0007]

In addition, since the laser chip is joined to the submount in a bridge shape, there is a structural problem that a large stress is easily applied to the laser chip. In particular, when both the solders are solidified at the same time, a large thermal strain is applied to the semiconductor laser chip depending on the concentration of the force applied to each unpredictable bonding surface as described above. Such stress / strain shortens the life of the semiconductor laser device. This is the second problem in the conventional semiconductor laser device.

[0008]

The object of the present invention is to eliminate the above-mentioned problems in the prior art.

[0009]

[Means for Solving the Problems]

According to the invention, on one side 1st and 2nd The semiconductor light emitting device chip having the electrodes is stacked on a mounting member having a conductive film pattern facing each electrode on the stacking surface by using solder, and the first electrode and the first conductive film pattern are the first. In the method of manufacturing a semiconductor light emitting device in which the second electrode and the second conductive film pattern are connected by a second solder different from the first solder, the first solder previously installed on the mount member And heating the second solder to a temperature higher than the melting point T1 of the first solder and the melting point T2 of the second solder, and holding the first solder and the second solder at a constant temperature between T1 and T2 for a predetermined time. The first solder and the second 2 Solder of Among them, solidifying the solder having a high melting point, holding the solder having a low melting point in a molten state, and cooling the first solder and the second solder to a temperature lower than any of T1 and T2. Thus, the step of solidifying the solder having a low melting point out of the first solder and the second solder is performed in the order described above.

In addition, it is preferable that a space between the first solder and the second solder on the mount member is provided with any one of a groove, a matte surface, a resin protrusion, and an insulator protrusion. The semiconductor light emitting element chip may be a semiconductor laser chip.

[0024]

In this specification, the semiconductor light emitting device represents a semiconductor light emitting element chip such as a semiconductor laser chip or an LED chip stacked on a mount member and integrated.

[0025]

In the present specification, the mount member means a component for directly stacking a semiconductor light emitting element chip. For example, a submount for a semiconductor light emitting element chip or a direct stem or frame without using a submount. Or, when loading on a package, this stem, frame, or package itself.

In this specification, the conductive adhesive includes solder, brazing material, and conductive resin.

Examples of materials known as heat dissipation materials include diamond>cBN>Ag>Cu>SiC>CuW>BeO>AlN>Fe>Mo>Si>Al2O3> GaAs, etc. in descending order of thermal conductivity. is there. (Ref: Baifukan, Ryoichi Ito, Michiharu Nakamura, “Semiconductor Laser” P.232, FIG. 16.19) However, in the present invention, the difference in thermal conductivity is different in order to focus on the difference in thermal conductivity of the heat dissipation material. If a combination is selected, a material other than the above materials may be selected.

[0026]

DETAILED DESCRIPTION OF THE INVENTION

In the following embodiments, the submount substrate serves as a heat radiating portion.

[0027]

[Embodiment 1]

FIG. 1 is a schematic cross-sectional view showing a semiconductor laser device according to

[0028]

FIG. 2 is a cross-sectional view showing the configuration of the GaN-based

[0029]

On the surface of the

[0030]

FIG. 3 is a schematic diagram showing the submount of the present embodiment used in the semiconductor laser device of the present embodiment. Each symbol is the same as in FIG. In the present embodiment, AlN that is an insulator is used for the

[0031]

With the above configuration, in the present semiconductor laser chip, the positive electrode corresponds to the electrode adjacent to the light emitting portion, and the negative electrode corresponds to the opposite electrode. In this submount, the positive side metal pattern corresponds to the conductive film pattern facing the positive electrode, and the negative side metal pattern corresponds to the conductive film pattern facing the negative electrode.

[0032]

Next, a die bonding process for manufacturing the semiconductor laser device of the present embodiment will be described with reference to FIG. FIG. 4 is a graph (temperature profile) showing changes in the submount loading surface temperature T in each process. Here, T corresponds to the temperature of each solder.

[0033]

<Process A> First, when the submount of the present embodiment shown in FIG. 3 was heated to T = 300 ° C., which is higher than the melting point of the first and second solders, Melted.

<Process B> The semiconductor laser chip shown in FIG. 2 was appropriately aligned and loaded on the submount so that the laser chip electrode formation surface and the submount loading surface were abutted. Here, alignment is performed in the following manner. The positive electrode and the first solder and the positive side metal pattern, and the negative electrode and the second solder and the negative side metal pattern are matched with each other, that is, as shown in FIG. The direction and the position are aligned so that the direction is perpendicular to the end face of the submount, and the light exit surface substantially coincides with the end face of the submount.

Next, a load of about 20 g was applied to the semiconductor laser chip, and the state of T = 300 ° C. was maintained for 30 to 120 seconds, so that the solder, the metal pattern, and the electrode were well blended. (T> T1, T2)

<Process C> T was changed to 250 ° C., which is lower than the melting point of the first solder and higher than the melting point of the second solder, while the load was applied.

<Process D> The state of T = 250 ° C. was maintained for 30 seconds. During this time, the first solder was solidified, and the semiconductor laser chip was fixed to the submount. After the first solder solidified, the load was stopped. (T1>T> T2)

<Process E> The submount was cooled and the second solder was solidified. When the temperature was cooled to an appropriate temperature close to room temperature, the die bonding process was terminated.

Thus, the semiconductor laser device of the present embodiment shown in FIG. 1 was completed.

[0034]

In the semiconductor laser device according to the present embodiment, since the melting point of the first solder is higher than the melting point of the second solder, the problems of the conventional technique are solved as follows.

[0035]

Of the solder melted in the process B, only the

[0036]

In the method for manufacturing the semiconductor light emitting device of the present embodiment, the temperature T in the process B is set to a temperature slightly higher than the melting point of the first solder. This is for joining the positive electrode and the positive side metal pattern under the optimum conditions, so that the alloying between them and the solder proceeds properly, and the solder is interposed too thickly. Therefore, it is possible to perform bonding with a minimum thermal resistance. On the other hand, since solder having a lower melting point is used for joining on the negative electrode side, the temperature T in the process B is not necessarily appropriate as the melting temperature of the second solder. Compared with the case of the die bonding process using an appropriate processing temperature of solder No. 2, the optimum value as the thermal resistance of the bonding cannot be obtained. However, in the semiconductor laser device of the present embodiment, since the electrode adjacent to the light emitting portion is a positive electrode, the thermal resistance on the negative electrode side hardly affects the thermal resistance of the semiconductor laser device. As a result, the semiconductor laser The thermal resistance of the device is optimized, which contributes to improving temperature characteristics.

[0037]

For comparison, a control semiconductor laser device was fabricated in which the second solder in the semiconductor laser device of the present embodiment was made of the same material as the first solder. In the semiconductor laser device of this embodiment, when the laser beam center within ± 2 ° from the vertical direction of the end face of the submount is defined as a non-defective condition regarding the positional deviation in the die bonding process, the yield of non-defective products is While it was 96%, it was 78% in the target semiconductor laser device. Further, when each semiconductor laser device was subjected to an energization test under the conditions of 3 mW and 70 ° C. (initial current of about 90 mA) for 1000 hours, the former showed almost no increase in driving current, whereas the latter In about 40% of the devices, an increase of 20% or more in the drive current value was observed. As described above, it was confirmed that the productivity of the die bonding process and the improvement of the device life characteristics were improved as compared with the semiconductor laser device using the conventional technique.

[0038]

In addition, according to the submount of the present embodiment, the productivity of the semiconductor laser device can be improved and the device life characteristics can be improved as compared with the conventional one.

[0039]

[Embodiment 2]

The configuration of the present embodiment is the same as that of the first embodiment except that the materials of the first solder and the second solder are different.

[0040]

In the semiconductor laser device of this embodiment and the submount of this embodiment used therefor, the first solder has a melting point T1 of 156 ° C. In and the second solder has a melting point T2 of 217. SnAu (Sn 90%,

[0041]

Also in the present embodiment, as in the first embodiment, in the semiconductor laser chip, the positive electrode corresponds to the electrode adjacent to the light emitting portion, and the negative electrode corresponds to the opposite electrode. In the submount, the positive side metal pattern corresponds to the conductive film pattern facing the positive electrode, and the negative side metal pattern corresponds to the conductive film pattern facing the negative electrode.

[0042]

Next, a die bonding process for manufacturing the semiconductor laser device of the present embodiment will be described with reference to FIG. FIG. 5 is a graph showing changes in the submount loading surface temperature T in each process of the die bonding process. Here, T substantially matches the temperature of each solder.

[0043]

<Process A> First, when the submount of the present embodiment was heated to T = 250 ° C., which is higher than the melting point of the first and second solders, both the solders melted.

<Process B> The semiconductor laser chip shown in FIG. 2 was appropriately aligned and loaded on the submount so that the laser chip electrode formation surface and the submount loading surface were abutted. Here, alignment is performed in the following manner. The positive electrode and the first solder and the positive side metal pattern, the negative electrode and the second solder and the negative side metal pattern are respectively coincided, that is, as shown in FIG. The stripe direction of the chip is perpendicular to the end face of the submount, and the direction and alignment are made so that the light exit surface substantially coincides with the end face of the submount.

Next, a load of about 30 g was applied to the semiconductor laser chip, and the state of T = 250 ° C. was maintained for 30 seconds, so that the solder, the metal pattern, and the electrode were well blended. (T> T1, T2)

<Process C> T was changed to 190 ° C., which is higher than the melting point of the first solder and lower than the melting point of the second solder, while the load was applied.

<Process D> The state of T = 190 ° C. was maintained for 30 seconds. During this time, the second solder was solidified, and the semiconductor laser chip was fixed to the submount. After the second solder solidified, the load was stopped. (T1 <T <T2)

<Process E> The submount was cooled and the first solder was also solidified. When the temperature was cooled to an appropriate temperature close to room temperature, the die bonding process was terminated.

Thus, the semiconductor laser device of the present embodiment has been completed.

[0044]

In the semiconductor laser device of the present embodiment, since the melting point of the first solder is lower than the melting point of the second solder, the problems of the prior art are solved as follows.

[0045]

Of the solder melted in the process B, only the second solder adjacent to the light emitting portion is solidified in the process D. At this time, since the first solder is still melted, an unbalance of the force applied to each joint surface caused by both the solders trying to solidify at the same time, which has been a problem in the prior art. Does not occur. In this process, the semiconductor laser chip is fixed without moving as the second solder is solidified. Therefore, after that, when the first solder is solidified, the chip is not displaced, and as a result, the laser chip moves during the solder cooling, resulting in the first problem of the conventional technique that misalignment occurs. Avoided.

[0046]

In addition, in the conventional technology, a large thermal strain is applied to the semiconductor laser chip fixed to the submount due to accidental concentration of unpredictable forces on the bonding surfaces when both solders are solidified simultaneously. There is nothing. Further, the distortion caused to the chip is alleviated after the second solder side is first fixed and before the first solder side is fixed. As a result, the second problem in the prior art that causes a large stress / thermal distortion in the semiconductor laser chip is avoided.

[0047]

In the method for manufacturing a semiconductor light emitting device of this embodiment, the electrode on the side adjacent to the light emitting portion of the semiconductor laser chip, that is, the positive electrode is fixed only in the final process E of the die bonding process. Therefore, since the distortion caused in the light emitting portion during the die bonding process can be relaxed to the final process stage, the stress / thermal strain in the light emitting portion of the semiconductor laser device that has undergone this die bonding step is the same as that of the first embodiment. Smaller than that. Therefore, according to the present embodiment, the life characteristics of the semiconductor laser device can be further improved.

[0048]

For comparison, a control semiconductor laser device was fabricated in which the second solder in the semiconductor laser device of the present embodiment was made of the same material as the first solder. In the semiconductor laser device of this embodiment, when the laser beam center within ± 2 ° from the vertical direction of the end face of the submount is defined as a non-defective condition regarding the positional deviation in the die bonding process, the yield of non-defective products is While it was 98%, it was 75% in the target semiconductor laser device. Further, when each semiconductor laser device was subjected to an energization test under conditions of 5 mW and 60 ° C. (initial current of about 80 mA) for 1000 hours, the former showed almost no increase in driving current, whereas the latter In about 70% of the devices, an increase of 20% or more in the drive current value was observed. As described above, it was confirmed that the productivity of the die bonding process and the improvement of the device life characteristics were improved as compared with the semiconductor laser device using the conventional technique.

[0049]

In addition, according to the submount of the present embodiment, the productivity of the semiconductor laser device can be improved and the device life characteristics can be improved as compared with the conventional one.

[0050]

Each of the above-described solders in the first and second embodiments can be replaced with other solders such as In, Sn, Pb, InAl, SnAg, PbIn, PbSn, AuSn, AuSi, and AuGe, and a metallic brazing material. At this time, it is necessary to select positive and negative solders while paying attention to the melting point. Table 1 shows melting points of typical electronic industry solders. Thus, even if only shown in this table, the melting point of the solder ranges from 150 ° C. to 400 ° C., so it is clear that each embodiment can easily obtain a combination of solders having different melting points. is there.

[0051]

[Table 1]

[0052]

Also, each Embodiment The temperature profile in FIG. 4 has been described with reference to FIG. 4 or FIG. 5, but this shows an ideal temperature change. In practice, it is necessary to maintain a strictly constant temperature in the processes B and D. It may be a profile that gradually changes in temperature in each process.

[0053]

[Embodiment 3]

FIG. Reference information closely related to the present invention FIG. 6 is a cross-sectional view showing a semiconductor laser device according to a third embodiment. In the figure, 30 is the semiconductor laser device of the present embodiment, 300 is a submount, 301 is a conductive resin, and other parts similar to those of the first embodiment are denoted by the same reference numerals as in FIG. The configuration of the semiconductor laser device of the present embodiment is substantially the same as that of the second embodiment except that the second solder in the second embodiment is replaced with a conductive resin.

[0054]

Here, the conductive resin is a resin in which a predetermined amount of metal powder or the like is mixed in any one of a thermoplastic resin, a thermosetting resin, or a mixture thereof, and has both adhesiveness and conductivity. Is. In the semiconductor laser device of the present embodiment, the

[0055]

Also in the present embodiment, as in the second embodiment, in the semiconductor laser chip, the positive electrode corresponds to the electrode adjacent to the light emitting portion, and the negative electrode corresponds to the opposite electrode. In the submount, the positive side metal pattern corresponds to the conductive film pattern facing the positive electrode, and the negative side metal pattern corresponds to the conductive film pattern facing the negative electrode.

[0056]

Next, a die bonding process for manufacturing the semiconductor laser device of the present embodiment will be described.

[0057]

A submount similar to that shown in FIG. 3 is prepared in advance. However, the conductive resin is provided on the negative electrode pattern instead of the second solder. At this stage, the resin is uncured.

[0058]

Next, after the temperature of the submount is raised and the solder is melted, the semiconductor laser chip shown in FIG. 2 is properly aligned so that the laser chip electrode formation surface and the submount loading surface are abutted. Loaded on the submount.

[0059]

After that, while applying a load of 30 g to the laser chip, the state of 180 ° C., which is a temperature higher than the melting point of the solder, was maintained for 1 minute, and the solder, the metal pattern and the electrode were well blended, and the resin was cured. .

[0060]

Then, after the solder was solidified and cooled to an appropriate temperature close to room temperature, the die bonding process was completed.

Thus, the semiconductor laser device of the present embodiment has been completed.

[0061]

Since the semiconductor laser device of the present embodiment uses a conductive resin instead of the second solder, the problems of the prior art are solved as follows.

[0062]

When the solder melted in the above process is solidified, the conductive resin is already cured, and therefore the semiconductor laser chip does not move as the first solder is solidified. That is, the first problem of the prior art in which the laser chip moves during the solder cooling and the misalignment occurs is avoided.

[0063]

Also, in the conventional technology, when both solders are solidified at the same time, a large thermal strain is applied to the semiconductor laser chip fixed to the submount due to accidental concentration of the force applied to each bonding surface which cannot be predicted. There is no. As a result, the second problem in the prior art that causes a large stress / thermal distortion in the semiconductor laser chip is avoided.

[0064]

Further, in the method for manufacturing the semiconductor light emitting device of the present embodiment, the electrode on the side adjacent to the light emitting portion of the semiconductor laser chip is bonded to the submount with solder as in the prior art, and the thermal resistance of the semiconductor laser device is It is equivalent to the conventional one. Contrary to the present embodiment, when the electrode on the side adjacent to the light emitting portion is connected with a conductive resin, the thermal resistance increases and the temperature characteristics of the semiconductor light emitting device deteriorate.

[0065]

For comparison, a reference semiconductor laser device using the same material as the first solder was produced instead of the conductive resin in the semiconductor laser device of the present embodiment. In the semiconductor laser device of this embodiment, when the laser beam center within ± 2 ° from the vertical direction of the end face of the submount is defined as a non-defective condition regarding the positional deviation in the die bonding process, the yield of non-defective products is While it was 98%, it was 75% in the target semiconductor laser device. Further, when each semiconductor laser device was subjected to an energization test under conditions of 3 mW and 50 ° C. (about 50 mA initial current) for 1000 hours, the former showed almost no increase in driving current, whereas the latter In about 30% of the devices, an increase of 20% or more in the drive current value was observed.

[0066]

Further, as shown in FIG. 2, not only when the positive and negative electrodes of the semiconductor laser chip are substantially on the same plane, but as shown in FIG. 19, an electrode (negative electrode) opposite to the side adjacent to the light emitting layer is used. ) May be provided on the recessed surface. In particular, as in this embodiment, a conductive resin is used to connect the electrode on the side opposite to the side adjacent to the light-emitting layer. It becomes possible to ensure the electrical continuity.

[0067]

As described above, when the submount of the present embodiment is used, the productivity of the semiconductor laser device is improved as compared with the conventional technique. Furthermore, the long-term reliability of the semiconductor laser device has also been improved.

[0068]

[Embodiment 4]

FIG. Reference information closely related to the present invention Embodiment 4 It is sectional drawing which shows this semiconductor laser apparatus. In the figure, 40 is a semiconductor laser device of the present embodiment, 400 is a submount, 401 is a groove provided between metal patterns on the submount mounting surface, 402 is an anisotropic conductive resin, and other implementations. Portions similar to those in

[0069]

Here, in order to make the conductive resin anisotropic, in the present embodiment, a thermosetting epoxy resin containing several to several tens wt% of Ag particles is used. As a result, when anisotropically conductive resin is cured without applying a load, the metal powder is dispersed, so that it becomes insulative, and when cured with a predetermined load, the metal powder comes into contact with each other. It becomes. The curing temperature of the resin was about 180 ° C. Further, In having a melting point of 156 ° C. was used for the first solder.

[0070]

Also in the present embodiment, as in the first embodiment, in the semiconductor laser chip, the positive electrode corresponds to the electrode adjacent to the light emitting portion, and the negative electrode corresponds to the opposite electrode. In the submount, the positive side metal pattern corresponds to the conductive film pattern facing the positive electrode, and the negative side metal pattern corresponds to the conductive film pattern facing the negative electrode.

[0071]

Next, a die bonding process for manufacturing the semiconductor laser device of the present embodiment will be described.

[0072]

In advance, a submount provided with the groove is prepared in the same manner as shown in FIG. Further, the anisotropic conductive resin is provided on the negative electrode pattern in place of the second solder. However, at this stage, the resin is uncured.

[0073]

Next, after the temperature of the submount is raised and the solder is melted, the semiconductor laser chip shown in FIG. 2 is properly aligned so that the laser chip electrode formation surface and the submount loading surface are abutted. Loaded on the submount. At this time, the resin spread and contacted the positive-side solder or the like as shown in FIG.

[0074]

After that, while applying a load of 30 g to the laser chip, the state of 180 ° C., which is a temperature higher than the melting point of the solder, was maintained for 1 minute, and the solder, the metal pattern and the electrode were well blended, and the resin was cured. .

[0075]

Then, after the solder was solidified and cooled to an appropriate temperature close to room temperature, the die bonding process was completed.

Thus, the semiconductor laser device of the present embodiment has been completed.

[0076]

Since the semiconductor laser device of the present embodiment uses a conductive resin instead of the second solder, the problems of the prior art are solved as in the case of the third embodiment as follows.

[0077]

When the solder melted in the above process is solidified, the conductive resin is already cured, and therefore the semiconductor laser chip does not move as the first solder is solidified. That is, the first problem of the prior art in which the laser chip moves during the solder cooling and the misalignment occurs is avoided.

[0078]

Also, in the conventional technology, when both solders are solidified at the same time, a large thermal strain is applied to the semiconductor laser chip fixed to the submount due to accidental concentration of the force applied to each bonding surface which cannot be predicted. There is no. As a result, the second problem in the prior art that causes a large stress / thermal distortion in the semiconductor laser chip is avoided.

[0079]

Further, in the method for manufacturing the semiconductor light emitting device of the present embodiment, the electrode on the side adjacent to the light emitting portion of the semiconductor laser chip is bonded to the submount with solder as in the prior art, and the thermal resistance of the semiconductor laser device is It is equivalent to the conventional one.

[0080]

For comparison, a control semiconductor laser device was fabricated in which the second solder in the semiconductor laser device of the present embodiment was made of the same material as the first solder. In the semiconductor laser device of this embodiment, when the laser beam center within ± 2 ° from the vertical direction of the end face of the submount is defined as a non-defective condition regarding the positional deviation in the die bonding process, the yield of non-defective products is While it was 98%, it was 75% in the target semiconductor laser device. Further, when each semiconductor laser device was subjected to an energization test under conditions of 3 mW and 50 ° C. (about 50 mA initial current) for 1000 hours, the former showed almost no increase in driving current, whereas the latter In about 30% of the devices, an increase of 20% or more in the drive current value was observed.

[0081]

As described above, when the submount of the present embodiment is used, the productivity of the semiconductor laser device is improved as compared with the conventional technique. Furthermore, the long-term reliability of the semiconductor laser device has also been improved.

[0082]

Further, as shown in FIG. 2, not only when the positive and negative electrodes of the semiconductor laser chip are substantially on the same plane, but as shown in FIG. 19, an electrode (negative electrode) opposite to the side adjacent to the light emitting layer is used. ) May be provided on the recessed surface. In particular, as in this embodiment, a conductive resin is used to connect the electrode on the side opposite to the side adjacent to the light-emitting layer. It becomes possible to ensure the electrical continuity.

[0083]

In particular, in the semiconductor light emitting device of the present embodiment, an anisotropic conductive resin is used, and a groove is provided between the submount metal film patterns. A load is applied to the region on the metal pattern to make it conductive. Therefore, electrical conduction such as electrical conductivity is ensured between the negative electrode and the negative metal pattern, but as shown in FIG. 7, even if the resin contacts the positive electrode or the like, there is no short circuit. Therefore, it is possible to prevent a decrease in productivity due to occurrence of a short in the die bonding process.

[0084]

As described above, the present invention is connected with Although the configuration has been described with a specific example, the scope of the present invention is not limited to this, and it is a matter of course that each component can be replaced with a material having the same application, and other technologies are combined. Can also be used.

[0085]

The above-mentioned insulating submount substrate is composed of other insulating materials such as diamond, Si, SiC, cBN, BeO, AlO, and further, as represented by diamond / Si, SiO / Si. It can be replaced with another insulating submount substrate having a laminated structure.

[0086]

In addition, the submount substrate does not necessarily have to be insulative, and the conductive submount substrate can be used after devising to insulate between the positive and negative electrodes. As the conductive submount substrate, materials such as Si, Ge, SiC, Cu, CuW, and Mo, and laminated structures of these substances can be used.

The above-mentioned semiconductor laser chip is not limited to the specific example shown in FIG. 2, but can be changed such as using other materials such as GaN, SiC, Si, SiO / sapphire as a substrate, As the material system of the semiconductor growth layer, other materials such as an InGaAsP system, an InGaAlP system, an AlGaN system, and a CdZnSe system can be used. In addition, the semiconductor laser chip can be replaced with another light emitting element chip such as an LED or a super luminescence diode.

[0087]

Further, in the submount of the above embodiment, the shape of each solder and each metal pattern is shown as a specific example in FIG. 3, but the present invention is not limited to this, and can be appropriately changed. . For example, the metal pattern is not necessarily provided so as to cover almost the entire surface of the submount. Further, it is easy for those skilled in the art to provide a wire bonding pad portion and a mark for alignment during die bonding on the submount stacking surface. . Alternatively, it is easily conceivable for those skilled in the art to apply the present invention to a semiconductor laser device loaded with a semiconductor laser chip having three or more electrodes, such as a so-called multi-beam laser, based on the above principle. .

[0088]

Further, as is well known, various films can be interposed between the solder layer and the submount base. For example, a film for improving the adhesion between the submount and the solder, the submount, and the like. A film for preventing a reaction between solders, and a film for improving adhesion between these films or preventing oxidation may be appropriately laminated. Pt / Cr, Au / Mo, Au / Pt / Cr, Au / Mo / Ti, or the like can be used as the metal pattern Au / Pt / Ti described in the above embodiment. It is assumed that various films are interposed between the solder, the insulating film, the bonding pad, and the submount substrate for the same purpose.

[0089]

Furthermore, according to the submount configuration shown in FIGS. 1, 3, and 6, no special structure is provided in the space between the first solder and the second solder. In order to prevent a short circuit during the bonding process or to prevent misalignment, a structure such as a groove, a matte surface, a resin protrusion, or an insulator protrusion may be provided.

[0090]

In each of the above-described embodiments, the semiconductor laser element submount has been described. However, the application of the present invention is not limited to this, and the present invention can be applied to all light emitting element chip mounting members. That is, in any mounting member, if the portion to be die-bonded of the light-emitting element chip has the same configuration as that of each of the above-described embodiments, the same effects as described above can be obtained in other light-emitting element chip mounting members. Is obvious. Therefore, when the light emitting element chip is directly mounted on the stem, the frame, or the package without using the submount, the above-described present invention is attached to the stem, the frame, or the package. is connected with Configuration can be applied.

[0091]

[Embodiment 5]

Figure 8 is the present invention Closely related to the reference FIG. 10 is a schematic cross-sectional view showing a semiconductor laser device according to a fifth embodiment. In FIG. 8, 50 is the semiconductor laser device of the present embodiment, 500 is the submount of the present embodiment, 501a and 501b are submount bases formed of an insulator, 102 is a positive metal pattern, and 103 is a negative side. A

[0092]

FIG. 9 is a schematic diagram showing the submount of the present embodiment used in the semiconductor laser device of the present embodiment. Each symbol is the same as in FIG. In this embodiment, AlN that is an insulator is used for the

[0093]