JP4083802B2 - デジタルベースの高速x線スペクトロメータについての方法 - Google Patents

デジタルベースの高速x線スペクトロメータについての方法 Download PDFInfo

- Publication number

- JP4083802B2 JP4083802B2 JP50940597A JP50940597A JP4083802B2 JP 4083802 B2 JP4083802 B2 JP 4083802B2 JP 50940597 A JP50940597 A JP 50940597A JP 50940597 A JP50940597 A JP 50940597A JP 4083802 B2 JP4083802 B2 JP 4083802B2

- Authority

- JP

- Japan

- Prior art keywords

- dsp

- signal

- value

- adc

- digital

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 238000000034 method Methods 0.000 title claims description 48

- 238000012545 processing Methods 0.000 claims description 33

- 238000001228 spectrum Methods 0.000 claims description 14

- 238000005070 sampling Methods 0.000 claims description 11

- 238000007493 shaping process Methods 0.000 claims description 10

- 230000011664 signaling Effects 0.000 claims 1

- 230000006870 function Effects 0.000 description 43

- 238000012360 testing method Methods 0.000 description 36

- 238000001914 filtration Methods 0.000 description 33

- 238000012937 correction Methods 0.000 description 21

- 238000010586 diagram Methods 0.000 description 21

- 230000008569 process Effects 0.000 description 19

- 238000007689 inspection Methods 0.000 description 17

- 230000015654 memory Effects 0.000 description 16

- 238000004458 analytical method Methods 0.000 description 11

- 238000004422 calculation algorithm Methods 0.000 description 11

- 238000001514 detection method Methods 0.000 description 11

- 238000013461 design Methods 0.000 description 10

- 238000012546 transfer Methods 0.000 description 10

- 238000004364 calculation method Methods 0.000 description 7

- 230000008859 change Effects 0.000 description 7

- 238000012544 monitoring process Methods 0.000 description 7

- 238000005259 measurement Methods 0.000 description 6

- 230000000737 periodic effect Effects 0.000 description 6

- 230000002829 reductive effect Effects 0.000 description 6

- 230000003595 spectral effect Effects 0.000 description 6

- 230000003750 conditioning effect Effects 0.000 description 5

- 239000003990 capacitor Substances 0.000 description 4

- 230000007423 decrease Effects 0.000 description 4

- 230000036961 partial effect Effects 0.000 description 4

- 238000006243 chemical reaction Methods 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 230000004044 response Effects 0.000 description 3

- 239000004576 sand Substances 0.000 description 3

- 230000003044 adaptive effect Effects 0.000 description 2

- 238000003491 array Methods 0.000 description 2

- 230000003139 buffering effect Effects 0.000 description 2

- 230000003247 decreasing effect Effects 0.000 description 2

- 230000003111 delayed effect Effects 0.000 description 2

- 230000001419 dependent effect Effects 0.000 description 2

- 238000012850 discrimination method Methods 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000010606 normalization Methods 0.000 description 2

- 238000005457 optimization Methods 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 230000000630 rising effect Effects 0.000 description 2

- 230000036962 time dependent Effects 0.000 description 2

- 238000002083 X-ray spectrum Methods 0.000 description 1

- 238000010521 absorption reaction Methods 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 230000002238 attenuated effect Effects 0.000 description 1

- 230000006399 behavior Effects 0.000 description 1

- 230000002457 bidirectional effect Effects 0.000 description 1

- JJWKPURADFRFRB-UHFFFAOYSA-N carbonyl sulfide Chemical compound O=C=S JJWKPURADFRFRB-UHFFFAOYSA-N 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 239000012141 concentrate Substances 0.000 description 1

- 238000013480 data collection Methods 0.000 description 1

- 230000006735 deficit Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 229920005994 diacetyl cellulose Polymers 0.000 description 1

- 238000003745 diagnosis Methods 0.000 description 1

- 239000006185 dispersion Substances 0.000 description 1

- 238000002474 experimental method Methods 0.000 description 1

- 230000005251 gamma ray Effects 0.000 description 1

- 230000036039 immunity Effects 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 230000000670 limiting effect Effects 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- ORQBXQOJMQIAOY-UHFFFAOYSA-N nobelium Chemical compound [No] ORQBXQOJMQIAOY-UHFFFAOYSA-N 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 238000003908 quality control method Methods 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 238000011160 research Methods 0.000 description 1

- 238000012552 review Methods 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 230000035945 sensitivity Effects 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000004611 spectroscopical analysis Methods 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

- 230000005469 synchrotron radiation Effects 0.000 description 1

- 230000009897 systematic effect Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01T—MEASUREMENT OF NUCLEAR OR X-RADIATION

- G01T1/00—Measuring X-radiation, gamma radiation, corpuscular radiation, or cosmic radiation

- G01T1/16—Measuring radiation intensity

- G01T1/17—Circuit arrangements not adapted to a particular type of detector

- G01T1/171—Compensation of dead-time counting losses

Landscapes

- Physics & Mathematics (AREA)

- Health & Medical Sciences (AREA)

- Life Sciences & Earth Sciences (AREA)

- General Physics & Mathematics (AREA)

- High Energy & Nuclear Physics (AREA)

- Molecular Biology (AREA)

- Spectroscopy & Molecular Physics (AREA)

- Measurement Of Radiation (AREA)

Description

合衆国政府はエネルギ省から与えられた契約No. DE-FG03-92ER81311に準ずる本発明について権利を有する。

発明の背景

本発明は一般的には、吸収された放射能に応答する検出システムで生成されたパルスをデジタル的に処理するシステム、特に、低コスト、高分解能、高レートなX線やγ線のためのスペクトロメータでそのようなパルスを処理することに関する。

特に、シンクロトロン放射能研究では、低コスト、高速度のX線スペクトロメータのアレイが必要である。データ取得を最大限に利用するために、そのようなスペクトロメータは、重ね合せ拒絶(pileup rejection)を持つ良好なエネルギ分解能、高カウント・レート能力を持ち、コストが十分低いので30あるいはそれ以上の検出器のアレイが予期されることができる。全多チャンネル分析(full multichannel analysis)(MCA)能力はかなり適用の範囲を広くするであろう。全てのスペクトロメータの機能の完全なコンピュータ制御はまた、別のやり方による検出アレイのセットアップならびに構成を行うとアレイの大きさが大きくなるにつれてかなりやっかいになるので、非常に重要である。スペクトロメータの物理的な大きさもまたコンパクトになって好ましい。

現在のエレクトロニクスによると多チャンネル分析を装備しない方法では検出器1台当たりでも約6000ドルのコストがかかるとともに、13要素検出器(13 element detector)で格子棚全てを満たしてしまうので、所期の目的は達成できない。それゆえ、30要素検出器を取り付けるのは非現実的となり、さらに100要素となると基本的には不可能である。多くの利用に対し、低価格MCAは十分に速くはなく一方高速のMCAは高価なので、多重チャンネル分析は、検出器アレイと共にはあまり利用されない。重ね合せ検査(pileup inspection)は散発的に実行され、しかし、だいたいは8keV以上のエネルギに対してのみ効果的である。少ないモジュールはスペクトロメータの機能の部分的なコンピュータ制御は可能とするが、しかしだいたいはコンピュータインターフェイスなしのモジュールの約2倍のコストがかかる。単一のスペクトロメーターのチャンネルを調整するのにはほんの数分必要であるが、この取組みは要素の数だけ増倍され、10要素あるいはそれ以上のアレイではかなりの負担になる。

これらシンクロトロンの用途、そして他の多くにとってもまた、高カウント・レートでかつ良好なエネルギ分解能をもって完全エネルギ分析が可能な、低価格,小容量の分光測定装置を備えて、コンピュータシステムとインターフェイスすることがさらに可能となる。必要なチューニング操作を、適当なプログラムによって、自動的に行うことができる点も有利であろう。

発明の概要

本発明は、検出器−プリアンプシステムからのパルス信号を処理し、検出器に吸収されたX線又はγ線のエネルギを解析する方法及び装置を提供する。具体的な実施例では、それは、小型であって、低コストであって、高速に、重ね合わせ検査を実行し、コンピュータに容易に接続できるようにデジタルインターフェースを有する。きわめて一般的なプリアンプで効果的に動作することができる。

本発明は、検出器−プリアンプ入力パルスを解析するデジタル信号処理技術を使用する。この方法では、低コストで高速のアナログ−デジタル変換器(ADCs)及びデジタル信号プロセッサ(DSPs)を使用して、所望の性能基準(performannce criteria)に合致するようにする。本発明は、エネルギ分解能を複製し、従来技術のアナログスペクロメータ(分光器)の重ね合わせ拒絶(pileup rejection)性能を凌駕し、以前はSCAシステムだけの特徴であった非常に高いカウント・レートでの完全な出力スペクトラを生成する。デジタル処理は、商用のアナログ回路に比べて、全体のコストと物理的な容量がそれぞれ4及び10のファクタで低減されることを可能にする。すべての分光(spectrometory)チューニング機能は、デジタル的に実現され、外部のコンピュータ制御の下で自動的に取り扱われる。

意図した応用では、低コストでの高いデータスループットは最適なエネルギ分解能よりも更に重要である。このような目標を達成するため、本発明はデジタルパルス処理を、2つのステージ(stage)で実行する。第1のステージは、“ハードワイヤード”(hardwired)デジタル複合論理を使用して、時間不変フィルタリングを実現し、第2のステージは、プログラマブルDSPを使用して、時間依存のパラメータに基づいて第1のステージの出力を調整して補正する。この処理の分割が、本発明の成功にとっての限界点である。

具体的な実施例では、ハードワイヤード論理ステージは、従来の適応形フィルタリング(adaptive filtering)、尖頭状重み付け(cusp-like weighting)、又はデコンボルーション(deconvolution)手法を回避する。このような手法は、乗算や重み付け機能のためのルックアップテーブルや時間変動処理(time variant processing)及びプロセス間(interprocess)同期の双方のためのデータセットのバッファリングなどを、含む複雑なデータ演算を必要とする。その代わりに、本発明は、加算と減算だけを必要とするアルゴリズムを使用して、低速と高速の両方のチャンネルで、簡単な整形(shaping)フィルタ(台形が好ましい)だけを使用する。従来技術で普通に行われているように、高速チャンネルの出力は重ね合わせ検査と低速のピーク獲得(capture)に使用され、低速チャンネルのフィルタリングは良好なエネルギフィルタリングを実行するのに必要な雑音(ノイズ)の低減を行う。例えば、GouldingとLandisの設計によるアナログスペクトロメータ(US特許第4,658,216号)を参照のこと。すべてのパルスを同様に処理し、すべての複雑なデータ演算を除いて、第1のステージの設計を単純化することにより、それを単一媒体サイズのフィールド・プログラマブル・ゲート・アレイ(FPGA)で容易に実現でき、それでも処理は500,000回/秒(cps)以上である。比較をすれば、Mott et al.(US特許第5,349,193号)に示された適応形デジタルフィルタリングスペクトロメータは、制御データフローに必要なステートマシンを実現するためだけに同様の大きさのFPGAを必要とする。

しかしながら、従来技術でより複雑な手法の開発が行われた理由が高性能の実現であったにもかかわらず、単純なフィルタだけを使用したのでは、既存のアナログ装置に比べて許容できる分光性能を実現できない。従って、本発明は、プログラマブル・コンピュータを使用した第2の処理ステージを、対等な性能を実現するのに必要な時間変動補正(correction)に適用する。これらの補正は、容易に数10MHzにもなるシステムのサンプリング速度では実行できず、10倍から100倍も遅い平均信号パルス・レート(rate)で、高価でないDSPを使用して相対的に複雑な補正を実現する。更に、全ての可能な補正を同時に行う必要はない。ハードウエアによる解決策に比べて、検出器−プリアンプの組による補正だけが、システムのスタートアップ時に、DSPにダウンロードされる。具体的な実施例では、例えば、上記の500,000cpsのデータ・レートは、40$のDSPチップだけで処理できる。

このように、本発明は、X線及びγ線スペクトロメータにおいてパルスをデジタル的に処理するようにこれまで工夫された、データの流れに(data stream)おけるパルスの同定及び時間依存の補正と最適化とを伴った振幅の導出に必要なすべての演算がハードワイヤード論理を使用して実行される“ハードワイヤード”クラスと、これらの全ての演算がソフトウエア制御の下に実行される“コンピュータ解析”のクラスの解決策とは区別される。前者のクラスは、Koeman(US特許第3,872,287号)、Lakatos et al.(US特許第5,005,146号)、Georgiev et al.(IEEE Trans. Nucl. Sci. 41(1994)1116-1124)、Mott et al., Jordanov and Knoll(IEEE Trans. Nucl. Sci. 42(1995)683-685)、及びFarrow et al.(Rev. Sci. Instr. 66(1995)2307-2309)の装置を含む。Georgiev et al. とMott et al., Jordanov and Knollの装置の商用化は、Target, Inc.、Princeton Gamma-tech, Inc.、及びAmptek, Inc.によってそれぞれ試みられている。後者のクラスの例は、Takahashi et al.(IEEETrans. Nucl. Sci. 40(1993)626-629)、Al-Haddad et al.(IEEETrans. Nucl. Sci. 41(1994)1765-1769)によって報告されている。後者のクラスは現在のところ商用化されておらず、その原因は有用なデータ・レートの処理に十分な速さのプロセッサが非常に高コストであるからだと思われる。本発明は、このように新しい“ハイブリッド”クラスを定義し、デジタルフィルタリングを、ハードワイヤードのプリプロセッサ(前処理プロセッサ)とプログラムされた信号補正器との間で分配する。

分光フィルタリング処理の第2のステージにおける、DSPの補正的な使用は、検出器に見られる光子・エネルギのスペクトルの生成に使用されるMCAステップと混同しないようにする必要がある。フィルタされた(filtered)パルス振幅のソーティング(sorting)とビニング(binning)は、また、専用のデジタルコンピュータによって共通に処理されるが、これらの機能は概念的にはフィルタリング処理の一部ではない。従って、従来技術の多くのシステムがデジタル・フィルタリング・ステージに続いてMCAを行うDSPを有する類似の物理的な構成を有していても、本発明におけるDSPの革新的な使用は、上記及び以下に説明されるように、まったく異なるものである。

具体的な実施例では、単一のDSPが、発明性あるフィルタリング機能、MCA機能、アナログ調整フロントエンド(analog conditioning front end)の制御、及びシステム制御コンピュータに対するデータ入出力の取扱の4つの論理的に分離した機能を実現するのに実際に使用される。

この具体例では、本発明は、入力データ・ストリームからランプ状(ramp-like)成分を除去して、システムのADCで必要な精度のビット数を低減するために、アナログ信号調整(ASC:Analog Signal Conditioning)フロントエンドと共に使用される。このASCの入力制御パラメータは、DSPによってデジタル的にセットされ、調整した信号がADCの入力範囲(input range)内に保持されるように調整される。デジタル化後、パルス・ストリームは上記のハードワイヤード論理ユニットで処理され、それはパルスを検出し、三角フィルタリングを行い、重ね合わせ検査を実行する。更に、良好なピークとベースライン(baseline)の値が獲得され、更なる処理のためにDSPに送られる。DSPは、ピーク値を正確なエネルギ値に変換する演算と補正を行い、その結果を、MCAスペクトラを生成するように、箱に入れる(bin)。ASCの動作はハードワイヤード・フィルタリング方法に歪を生じるが、DSPは、ASCの制御パラメータとフィルタされていない信号値の両方を適当に使用して、適当な補正を行える。ピーク間のベースライン値を獲得することにより、DSPは各種の原因で生じるシステム的な変動を少なくするように、ピークの高さを補正できる。

本発明においては、ハードワイヤードデジタル処理ステージは、それが「フィルタリング・ピーク検出・重ね合わせ検査」″Filtering, Peak detection, and Pileup Inspection″を実現するため、FiPPIと呼ぶことにする。FiPPI処理は各データ・サンプルを処理するが、入力データ・ストリームにおけるX線パルスの部分的な(local)振幅を検出して正確に獲得するために必要な、フィルタリングと検査機能との少数の組だけを実行する。正確なX線エネルギ値を生成するには、これらの獲得ピーク振幅を処理するのに、より複雑なDSP演算が必要であるが、実際の事象を検出するときに行うだけでよい。この分割は、必要な高価な高速論理の量と必要なDSPの速度(すなわちコスト)の両方を最小にするので、有利である。その結果、各解決策を単独で使用するのに比べて、よりコストを下げられ、性能を高くできる。

1つ又は他の具体例にて現われるFiPPI機能は、デシメータ(decimator)、低速台形フィルタ(slow trapezoidal filter)、高速台形フィルタ(fast trapezoidal filter)、ピーク検出器(peak detector)、重ね合わせ検査器(pileup checker)、出力バッファ、及び入力カウント・レート(input count rate(ICR))カウンタを備える。FiPPI演算は、スペクトロメータシステムが動作を開始する前に、FiPPIにロードされるいくつかのデジタルパラメータによって制御される。

Nによる除算機能は、ADCからの入力をN値の連続したブロックに分解し、入力データ・ストリームの周波数の1/Nで各ブロックの平均値を出力する。調整可能なパラメータNは、2の累乗であり、1、2、4、8などをとり得る。デシメータの第1の機能は、FiPPI低速フィルタにおける長いフィルタリング時間を必要とする先入れ・先出し(FIFO)メモリの量を低減することである。

低速と高速の両方のフィルタは対称な台形で、そのピーク時間(peaking times)τpと上辺の長さτgは外部からロードされるパラメータである。台形のピーク値は検出されたX線のエネルギの測定値を構成する。これらの機能は、2つの遅延オフセット差の間の差の移動平均によって形成されるものでありFIFOの機能を使用して実現される。高速フィルタは、低速フィルタよりはるかに短く、通常、クロック速度の速度で進行する。低速フィルタは、クロック速度の1/Nでデシメータ出力と共に働き、32ワードだけの深さ(deep)のFIFOを使用して、数μs以上のピーク時間を有する。

ピーク検出回路は、信号パルスに対する高速フィルタの出力を監視して、あるしきい値レベルTを越えたM以上連続した値を探し、そのような値の組(セット)を見つけた時に、そのセット内の最大信号値の到着時間を獲得する。この時間が、以後関係する信号パルス到着時間として定義される。外部からロードされたパラメータTとMは、ノイズによるトリガに対して適当な不感性を維持しながら、低い信号レベルに対する感度を最適化するように調整される。

重ね合わせ検査器は、低速フィルタ台形が上辺の中央でサンプルされることを保証して、このサンプリングが良好なピーク(good peak)に対してだけ起きることを保証する。許容できる時間間隔で前者と後者を分離するパルスが、良好なピークになる。

重ね合わせ検査は、いくつかのテストからなる。これらのうちの2つは、高速フィルタ出力の各ピークを分離するのと同様に、分解するには接近しすぎている「高速の重ね合わせ」パルス用のものである。時間dで分離された重ね合わされた高速パルスの組は、高速フィルタの単一パルス出力の期間をDからD+dに伸ばすので、第1の高速重ね合わせテストは、しきい値Tにおける高速パルス幅を、Dより若干長い値にセットされたパラメータWと比較する。

第1の高速重ね合わせテストは、しきい値Tにおける高速のピークの幅をテスト値と比較するが、第2の高速重ね合わせテストは、その半値幅を、理想的な高速パルスの半値幅より若干大きくセットしたテスト値と比較する。このテストは、パルスの振幅には無関係であり、実現するのはより複雑であるが、大きくしきい値を越えることはなく、従って固定の振幅しきい値以上の期間が振幅に大きく依存する非常に低い振幅の高速パルスに対して、精度を向上させることができる。

低速のチャンネルにおける重ね合わせは、高速パルスが検出される毎にリセットされるカウンタを使用して検査される。もしこのカウンタがリセットされることなく外部パラメータの値Sに到達すれば、低速フィルタの出力値はその瞬間に出力バッファに、FiPPIのフィルタされていない入力値として獲得される。もし、カウンタが第2の外部パラメータの値Nに到達し続けたら、このパルスは後縁が重ならない。もし記憶されたフラグ値が前縁も重ならないことを示していれば、ピーク値は良好で、DSP割り込みフラグがその獲得を指示するように上昇する。Nの値は典型的には、τspにτsg/2と小さな余裕期間とを加えたのに等しい。Sの値はタイミングオフセットを調整されたNである。

良好な事象値が獲得された後、第2の試みが行われNをカウントする。もし成功すれば、低速フィルタの出力はそのベースライン・レベルに戻り、正規化補正で使用するためのDSPの要求で値が獲得される。

ICRカウンタは、重ね合っているかいないかにかかわらず、X線が検出された時には何時でも増加される。この値は、読み取られ、時間毎にゼロにされ、部分的な重ね合わせレートの統計が集められ、量的に正確な結果が必要な時に、正確なデッドタイムの補正を行うことを可能にする。

この同じ実施例では、DSPはその機能のすべてがソフトウエアで実現された商用のデジタル信号処理回路である。これらの機能は、ASCの制御、獲得したFiPPIのデータ値をピーク高さ評価の精度に最適化する補正、スペクトラを生成するマルチチャンネル解析の実行、及びシステムと外部との間のデータ及びパラメータの入力/出力(I/O)転送の4つの一般的なカテゴリィに入る。I/P回路とソフトウエアは当業者であれば容易に実現できる。

DSPは、ASCのランプ発生器(ramp generator)におけるオフセットとスロープDACに初期値をまず設定することによりASCを制御し、要求に応じてランプ発生器をリセットする。最初のDACのセッティングは、動作を開始する前に評価される。スロープDACセッティング評価は、時間毎に更新され、検出器へのX線の到着レートにおける変動を補償する。もしASCの出力がADCの入力範囲外になれば、オフセットDACはそれを記憶するように、調整される。

DSPは、FiPPIレジスタからの獲得ピーク値を、割り込み制御の下で検索しそのピーク値とICRカウンタ値とを、フィルタされなていないFiPPI入力値と獲得した事象を特徴付けるすべての他の値と含むレジスタを読み取る。DSPの設計により、割り込み応答(interrupt response)は、最小の低速フィルタピーク時間より小さく、従ってこの読み取りはシステム全体の応答にいかなる無効なデッドタイムをも与えない。良好なピーク値は、エネルギ値に変換され、そのような補正が許容できる精度を実現できるように行われる。次に、それが選択されたスペクトルエネルギ範囲内にあれば、MCAがその結果を集められたスペクトルに入れる。

更に、DSPは、良好なピーク値を読んだのと同様の方法でFiPPIベースライン値を次々に獲得する。″set baseline″フラグがこの2つのケースを識別する。ベースライン値は、定義ではエネルギがゼロの事象に対応し、FiPPIのゼロオフセットを確立するのに使用される。ベースライン統計も集めることができ、スペクトロメータのエネルギ分解能を監視(モニタ)など診断の目的で使用できる。

もし補正されていなければ、ASCでのプリアンプの入力信号からのランプ波形(ramp waveform)の減算がスペクトルの歪を生じる。DSPがASCのランプ発生器を制御するので、それは元の信号の振幅を演算でき、適当な補正を行うアルゴリズムが実現できる。DSPは、これらの補正の後平均のベースライン値を監視し、それがゼロでなければこの値を良好なピークエネルギから減算して、例えば検出器漏れ電流から生じるいかなる残留誤差も補償する。

本発明の特質及び利点は、明細書の後述の部分と図面を参照することにより、更に理解できる。

図面の説明

図1Aは、本発明にパルスを供給する典型的な検出器−プリアンプの回路の概略である。

図1Bは、本検出器で単一X線の吸収の結果として生ずる典型的な検出器−プリアンプの出力信号の図である。

図1Cは、多重のX線のコースに亘る連続的な放電検出器−プリアンプからの典型的な出力を示す。

図1Dは、多重のX線のコースに亘る周期的なリセット検出器−プリアンプからの典型的な出力を示す。

図1Eは、ASCが信号のリセット−ランプ部分を取り除いた後の3つの共通X線パルス到着パターンを示す。

図2は、本発明のおもな部分と他の装置との本発明の接続を示すブロック図である。

図3は、アナログ信号調整(ASC)と図2のAからDのハードウェア部のブロック図である。

図4は、図3のそれぞれのブロックの典型的な実施例の回路の概略である。

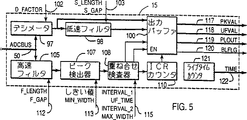

図5は、図2のハードワイヤードデジタル信号プロセッサのハードウェアブロックのブロック図である。

図6Aは、図5のデシメータハードウェアブロックの典型的な実施例の回路の概略である。

図6Bは、図6Aの回路の働きを図解したタイミングダイヤグラムである。

図7Aは、図5の低速フィルタハードウェアブロックの典型的な実施例の回路の概略である。

図7Bは、図7Aの回路の働きを図解したタイミングダイヤグラムである。

図8Aは、図6AのFIFO10ハードウェアブロックの典型的な実施例の回路の概略である。

図8Bは、図8Aの回路の働きを図解したタイミングダイヤグラムである。

図9Aから9Gは、図5の高速と低速のフィルタによって出力される対応したパルス間の関係を表示し、図5のピーク検出器と重ね合せ検査器ブロックの機能を図解した一連のタイミングダイアグラムである。

図10Aは、図5のピーク検出器のハードウェアブロックの典型的な実施例の回路の概略である。

図10Bは、図10Aの回路の働きを図解したタイミングダイヤグラムである。

図11Aは、図5の重ね合せ検査器のハードウェアブロックの典型的な実施例の回路の概略である。

図11Bは、図11Aの回路の働きを図解したタイミングダイヤグラムである。

図12Aは、図5の入力カウント・レート(ICR)カウンタのハードウェアブロックの典型的な実施例の回路の概略である。

図12Bは、図12Aの回路の働きを図解したタイミングダイヤグラムである。

図13は、図5のライブタイムカウンタの典型的な実施例の回路の概略である。

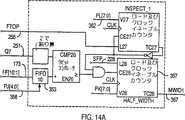

図14Aは、半分の高さの速いピーク幅を計る重ね合せ検査器の典型的な実施例の回路の概略である。

図14Bは、図14Aの回路の働きを図解したタイミングダイヤグラムである。

図15は、DSP制御プログラムの主な特徴を示したフローダイアグラムである。

図16は、DSP制御プログラムのデータ取得タスクの特徴のフローダイアグラムである。そして、

図17Aから17Dは、X線の到着レートにおける時間変動の影響を示すASCの発明の具体的な実施例の出力のオシロスコープの結果である。

図18は、ASCの入力範囲内でASCの出力を保つのに使われる制御手順のブロック図である。

図19Aから19Bは、プリアンプの2つのタイプのパルス高補正期間の必要を示している略図である。

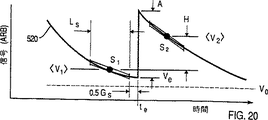

図20は、連続放電型プリアンプのためのパルス高補正期間を導き出すのに使われる期間を定義する略図である。

図21Aは、図4の低速フィルタのハードウェアブロックの別の実施例の回路の概略である。

図21Bは、図21Aの回路の働きを図解したタイミングダイヤグラムである。そして、

図22はアナログフィルタリングを使った別の低速フィルタの実施例を示す。

具体的な実施例の説明

1:システムの概観

1.1.プリアンプの入力信号

具体的な実施例の本記述は、われわれが処理する、検出されたX線に対応した、電気パルスについての簡単な論議によって明らかにされるであろう。図1Aは、半導体検出ダイオード10、電圧供給源12、フィードバックキャパシタCf15をつけた充電積分プリアンプ13、及びフィードバック要素17を備える一般的なX線検出器/プリアンプ回路を示す。ダイオード10に吸収されたエネルギExのX線は、Ex/εに等しい電荷Qxを放つ。ここで、εはダイオードの材質に依存する。Qxは、図1Bに示すように、Cf15で積分され、Qx/CfあるいはEx/(ε/Cf)と等しい出力電圧ステップVxを生成する。本発明は、Vxの測定において、ノイズσを減らすことによって正確にExを見積もるためのデジタルフィルタリングを使用している。

機能的には、2つの基本的なタイプのプリアンプがある。第1のタイプでは、抵抗によるのと同様に要素17はキャパシタ15を連続的に放電(continuously discharges)する(“CD″の場合)。図1Cは、それぞれの間で指数関数形減衰をする一連の信号ステップ(図1Bにより)を備える典型的なCDプリアンプ出力を示す。平均出力電圧Vavgは、入力ダイオード電流Iinに要素17の抵抗値をかけたものに等しい。

第2のプリアンプのタイプでは、要素17は、プリアンプ13の出力電圧が上位リセット電圧VUに達したときに周期的に閉じて、プリセット下位限界Vlが達せられたとき再び開くスイッチである。これは、周期リセット(“PR″)(periodic reset)の場合の一般的な出力を示す図で、図1Dがその代表的な出力を示し、VUに応じて立ち上がる電圧ステップの勾配を備え、リセットがおきて電圧VLにもどり、処理が再び始まる。ランプの平均の傾きSavgはIin/Cfに等しい。平均の傾きについての典型的な信号変動は図1Eに示される。

1.2.ダイナミックレンジとデジタル化レートの議論

ADCの選択は、良好な重ね合せ拒絶と良好なエネルギ分解能両方を持つデジタルスペクトロメーターを実現するうえで重大である。重ね合せに関して:少なくとも20メガサンプル/秒(MSA)は200nsのパルス重ね合せ検査時間を実現するために必要である。

エネルギ分解能に関して:経験的に、良好なエネルギ分解能を得るためには、ノイズレンジσ(図1B参照)はADCの最下位ビットΔV1の約4倍でなければならない。これはADCの前のアンプステージのゲイン(ボルト/ビット)をセットする。

与えられたΔV1に対して、ADCは0からVmaxの範囲を全部カバーするのに十分なビットNBを持たなければならない。

NBの一般的な値は14である。

20MSAで動作する14ビットADCは存在するが、しかし我々が置換したいアナログエレクトロニクスのコストと比較して高価である。高速の8から10ビットのADCは、しかし、デジタル通信におけるその広い用途のおかげで高価ではない。本発明では、我々はこれらのより安価な装置が使用できるようにプリアンプ信号のダイナミックレンジを十分減らす。14-15ビットから8-9ビットへの減少はまた、より短い語は処理のためのエレクトロニクスを少なくし、所定のデータ・レートで処理をするためのパワーを少なくするという両方の点で有利である。

1.3.機能の構成

図2は本発明のデジタルスペクトロメータの基本的な構造を示す。従来の検出器−プリアンプ20からの入力は、図1Aにあるように、3つの機能ブロックを備えるデジタルスペクトロメータ22へ入力される。その3つの機能ブロックは、アナログ信号調整(ASC)とアナログデジタル変換器(ADC)のブロック23,ハードワイヤードデジタルフィルタとピーク検出器と重ね合せ検査器(FiPPI)(a hardwired digital filter, peak detector and pileup inspecter)のブロック25,及び具体的な実施例においては、信号精練、多チャンネル信号分析,ASC制御,及び入出力(I/O)機能のためのデジタル信号処理装置(DSP)であるプログラマブル・デジタル・コンピュータのブロック27である。デジタルスペクトロメーター22は汎用制御コンピュータとインターフェイス28に接続されており、それからパラメータ値と制御信号を受け取り、集められたスペクトラをそれらへ送る。ASC23の機能はデジタルスペクトロメータの各ブロック25,27の動作には必要ないが、しかし我々の好適な実施例では設けられている。各ブロック25,27の機能は、様々な回路を使って実現されるが、しかし我々の好適な実施例では以下に示された明細書によって実現されている。一般的用途の制御コンピュータとインターフェイス28は従来のものであり、様々な一般的な個人あるいは実験室のコンピュータとインターフェイスの基準のいずれも含む。DSPにコンピュータを接続する詳細は従来の当業者にとって公知である。

2:ASC:アナログ信号処理とAD変換ブロック

2.1.ASCの機能の概念

ASC23は入力信号のダイナミックレンジを縮めることと、式1を満たすようにそのゲインを調整すること2つの主要な機能を持つ。ダイナミックレンジの縮小は、プリアンプの信号を2つの成分に分解することによって成し遂げられる。その2つの成分とは、広いダイナミックレンジの、“低周波数″信号部分(LFF)と、さらにもっと狭いダイナミックレンジの“高周波数″信号部分(HFF)であり、興味のある信号(SOI:図1Dを図1Eと比較)を搬送する。“低周波数″と“高周波数″の周期は記述的である。なぜなら、この用途では、LFFの基本周波数はHFFのSOIを搬送する周波数帯幅よりももっと小さいからである。重要な概念は、LFFの信号部分の妥当な複製は比較的小さい個数のパラメータによって記述され、それはたやすく入力信号から生成、減算され得る。残留信号部はそしてSOIを搬送するオリジナルのHFFに密接に近く、非常に縮小されたダイナミックレンジを持ち、非常に縮小されたビット数のADCを使ってデジタル化することを可能にする。

DSP27によるパラメータの制御の下では、ASC23は従ってLFF複製を生成し、入力信号からそれを減算し、式1に合うように残留HFF複製(remaining HFF replica)の振幅を調整する。ADCビットを少なくする以外にも、この方法は3つの付加的な有利性を有する。第1に、DSP27はASCの制御パラメータがわかり、それが収集しているエネルギスペクトラムを精製するのにそれらパラメータを使うことができる。第2に、HFF部分のX線パルスはADCの入力範囲にわたってほとんどランダムに(身震いされて)降下することになるので、スペクトロメータ22の精度と線形性はADCの微分積分非線形性に対して比較的に鋭敏ではなく、どんな直流オフセット電圧に対しても完全に鋭敏でない。第3は、プリアンプの入力の異なった各タイプは単にパラメータの調節によって調整することができる。CDプリアンプに対しては、LFFは、図1Cに示されるように、単に値Vavgにセットされる定数に過ぎない。PRプリアンプに対しては、LFFは図1Dに示すように、交互の傾きSavgのランプとリセットを備える、のこぎり波の機能である。

2.2.ASCのハイレベルに関する説明

図3はASCと変換ブロック23の機能ブロック図である。アンプ30は、検出器−プリアンプからの入力信号と、プリアンプの信号を回路の他の部分で約ゼロに中心を置くようにするデジタルアナログ変換器(DAC)32のバイアスDACによってセットされる電圧レベルとの差を増幅する。減算器33は、アンプ30の出力からLFF生成器35の出力を減算する。LFF生成器35の出力波形は、オフセットDAC37、及びスロープDAC38及びDSP27からのリセット線40からの入力によって制御される。減算器33の出力は、可変ゲインがゲインDAC43で制御されるアンプ42に送られる。コンパレータ44は信号を検査し、もしそれがADCの入力限界を越えたなら割り込み線45でDSP27に警報を発する。ローパスフィルタ47は、それがADC48に達する前に、ADCのナイキスト限界を越えるどんな信号も取り除く。

ADCの出力は、デジタルADCの出力バス50を経由して直接的にFiPPIブロック25に接続され、バスバッファ52を経由して間接的にDSPブロック27に接続されている。バッファ52は双方向DSPデータバス53、DSPアドレス線54、リセット線40に接続されており、DSP27が各DAC32,37,38,43へデジタル入力値をロードするようにし、ADC出力バス50上の所望のADC出力データ・ストリームをサンプルする。このようにDSP27は直接ASC23の全機能を制御し、また直接ADC出力50においてその効果を測定することもできる。適切な制御ソフトウェアによって、これはDSP27がまずASC23に好適な動作量を最初にセットし、そしてLFF生成器35の動作もまた動的に制御することを可能にする。各インターフェイスバッファを使用することの詳細は、デジタルエレクトロニクスの従来技術に関する当業者にとっては公知であり、さらには記述しない。

2.3.ASCブロックの出力信号

DSP27の制御のもとでは、LFF生成器35は直流オフセットとともにリセットするランプ関数(ramp function)を生成する。CRプリアンプに対しては値Vavgの直流オフセットのみが使われる(図1C参照)。PRプリアンプに対しては、直流オフセットは値VLにセットされ、ランプの傾き(ramp's slope)は平均の傾きSavgと一致するように調整される(図1D参照)。ランプ減算(ramp's subtraction)、ゲイン調整、フィルタリングした後の、3つのPR出力信号の各例は図1Eに示される。準周期的なランプ構成を取り除いた後、個別X線パルスはそれらの到着時に変動を伴う垂直なステップとして現れる。トレースAは到着した場合の平均レートを示す。各トレースB,Cはその平均からの一時的な変動を示す。ランプ減算は各ステップ間の負の傾きを残すが、それらの振幅はこの手続きによって感知できるようには修正はされず、デジタルスペクトロメータによって復元される。

CRプリアンプに対しては、垂直の目盛りがADCの全体の入力範囲を満たすように調整されることを除いて、ASCの出力はだいたい図1Cのようになる。この場合、各X線パルス間の範囲は、プリアンプと同じ指数関数形減衰の傾きを持つ。

2.4.ASCの具体的な実施例

図4は、ASC20のアンプ30、減算器33、LFF生成器35、可変ゲインアンプ42の各ブロックの回路の概略である。本回路はアナログエレクトロニクスの当業者にとってはおそらく自明であり、少しの構造の説明のほかにそれ以上の論議は少しも必要としない。従来技術の当業者にとっては公知である回路の各詳細、例えば電力供給フィルタリングまたはオペアンプ補償は、示されていない。本実現は唯一ではなく、多くのほかの適切なアレンジは容易に工夫できる。

入力信号をASC回路の範囲で中心に持っていくことのほかに、アンプ30の主要な機能は、入力からASCを保護し、約3つのファクタによって入力を増幅することにより回路の他の部分のノイズの要求事項を低減する。したがって適当な周波数帯幅のとても低いノイズのオペアンプを使うことが実現されるべきである。

LFF生成器35はリセット可能な電流積分器であり、オフセット電圧Voffを有しリセットに5μs以下の整定時間で低ノイズ、高精度な各ランプを生成するように設計されている。抵抗68はDAC37の電流を電圧Voffに変換する。キャパシタ72はDAC38からの電流を、スイッチ75によってリセットされるまで積分する。抵抗77はFETオペアンプ65のスルーレイトが限界を越えないように保証する。オペアンプ78とスイッチ85は、LFF生成器35の出力の振幅と符号が入力と一致するようにする。DAC37は、一般に、LFF生成器35の出力とアンプ30からの信号がプリアンプのリセットの後すぐに一致するように調整される。

可変ゲインステージ42は、粗いゲインを精密なゲインのための電圧制御、可変ゲインオペアンプであるアナログ・デバイゼス社製AD60392の100Ωに固定された入力インピーダンスにするスイッチ88と抵抗90を備える。ノイズを最小限にするために、固定出力ノイズがオペアンプ92は約12dBの細かいゲイン調整に対してのみ使用される。

ASC部20の残された各ブロック、コンパレーター44とローパスフィルタ47は、直列に接続されている。コンパレータは、図1Eを参照すると、変動によって、ASCの出力信号がADCの入力範囲に位置するLLからULの範囲を越える、どんな場合も検出することが求められる。

ローパスフィルタ47は、ASCの出力信号の周波数帯幅を、ADC48のサンプリング周波数の半分であるナイキスト周波数fN以下に制限する。なぜなら、より高周波数の全ノイズは、デジタル化された出力信号に“偽信号化″されて、余計にノイズを増やすからである。この具体的な実施例では、ADCは20MHz、すなわちfNが10MHzで動作する。さまざなフィルタ設計が使用できるにもかかわらず、4極のバターワースフィルタが具体的な実施例で使われる。なぜなら、それは周波数における速いロールオフと、最小のピーク時間を持ち、4つの受動部品だけを必要とするからである。ナイキスト判別法が満たされたときスペクトロメータエネルギ分解能はサンプリング・レートに独立であることを、我々は実験的に確認した。2,5,10,25MSAで動作し、各々1,2.5,5,12,5MHzの各ローパスフィルタを有する実施例は、集められたデータサンプル数が、2MSAにおける8から25MSAにおける100に変化するにもかかわらず、2μsのピーク時間をもつ三角フィルタリングに対してすべて同一のエネルギ分解能を作り出した。サンプリング・レートを増やしてエネルギ分解能の改善を報告した様々な著者はナイキスト判別法を満足させることに明らかに失敗している。従ってサンプリング・レートを選ぶことは、主として、良好パルスの組の分解能を実現するためにサンプリング・レートを上げることと、デジタル処理のコストを下げるようにサンプリング・レートを下げることとのトレードオフである。

3.FiPPI:フィルタ、ピーク検出、重ね合せ検査回路

3.1.FiPPI設計の概念

発明の概要でも議論されているように、本発明のスペクトロメータは2ステージでデジタルフィルタリングを実行する。第1のステージは、FiPPIと称され、フィルタリング、ピーク検出、重ね合せ検査(Filtering, Peak detection and Pileup Inspection)を行うために、組合せ論理を使う。フィルタリング回路を最小化し、処理速度を最大化するために、加算と減算以上の複雑な演算はこのステージでは行われない。速度を最大限に利用するために、すべての演算は、1クロック周期(clock cycle)あたり1点で入力データを処理するようにパイプライン化される。すなわち、もしO(n,j)がデータサンプルnに必要とされるj番目の演算であるなら、そしてタイムステップiとすると、同時にO(n,1),O(n−1,2),O(n−2,3)などを実行する。

この方法には重大な限界がある。なぜなら、補償調整はパルスの具体的な状態のもとでは行われることができず、加算あるいは減算のみを使うフィルタは正確ではないので我々の分光動作の目的を満たさない。それゆえ、発明の概要で言及したように、第2のフィルタリングステージでは、所望の精度を実現するのに必要な具体的な補正(プリアンプの形式に基づいたり、小域的な各動作状態など)を行うようにDSPが使用される。

この方法は様々な理由で有利である。第1に、FiPPIはとても安くかつとても速くなり得る。例えば、好適な実施例では、20MSAのADCと動作させても単一のFPGAで実現される。第2に、第2ステップでの機能は、ADCのサンプリング・レート(例えば、20MSAと比較して500,000cps)よりもずっと低いX線信号事象の平均到着レートでのみ実行される。必要とされる精度は典型的に簡単な各法則であるので、現在の技術で実施されているように、得られたピーク値だけにそれらを適用することは、データ・ストリーム自体に(プリコンディショニングやデコンボルーションを通して)適用するより、より簡単かつ速くなる。同様の実施例では、20MIPのDSPのみが第2のステージの処理に必要とされる。

具体的な実施例でのFiPPIはそれゆえ、部分集合として三角フィルタリングを含む台形フィルタリングのみ備える。この選択は、実現されようとしている高カウント・レート・レジーム(high count rate regime)でのスペクトロメータのエネルギ分解能を下げない。なぜなら、Revista del Nuovo Cimento(1986)Vol.9(1),pp.1-146で発表された“Processing the Signals from Solid State Detectors in Elementary-Particle Physics”と題される論文でGattiとManfrediが示したように、三角フィルタリングは、実際には、連続した白色雑音が支配する短い整形時間レジームでは理想的な固定された整形の形式であるからである。より長い整形時間であっても、三角整形はなおもとても効果的である。核原子物理学の年間評論38(1988),pp.217-277で発表された“Low Noise Techniques in Detectors”と題された論文で、ラデカ(Radeka)は、最大限のエネルギ分解能に対してさえ、三角フィルタの分解能は理想的な尖頭フィルタよりも8%だけ悪いことを示した。

3.2.FiPPIの具体的な実施例、ハイレベルに関する考察

1つの具体的な実施例では、FiPPI論理はフィールド・プログラマブル・ゲート・アレイ(FPGA)を使って実現される。これは小さなスペースでの高論理密度を可能にする。さらに、FiPPI論理は動作の前にファイルからダウンロードされるので、新しい各状態を満足したり設計改良を具体化することに対しても、容易に修正されることができる。より安いコストあるいはより速い動作速度が所望される他の各実施例では、FiPPIは、用途特定集積回路(ASIC)あるいは他の論理回路で実現される。

具体的な実施例におけるFiPPI25の微細構成は図5に示される。データ・ストリームはADC出力バス50に入り、低,高速信号両チャンネルに流れ込む。第1の低速チャンネル回路、デシメータ97は、プリセット・ファクタによって到来信号データ・レートを減らす。その出力は、デジタル的に台形フィルタリングするように備えられた低速フィルタ98によって処理される。低速フィルタ98の信号出力のピーク最大値は検出されたX線のエネルギに一致し、出力バッファ100によって得られることができる。低速チャンネルの動作はDSP27からFiPPI25にロードされる3つのパラメータ、デシメーション・ファクタ102と低速フィルタの長さと各ギャップ値103によって制御される。

高速信号チャンネルのもっとも重要な機能は、低速フィルタ98から適切な値を得るためにデータ入力ストリーム50とトリガー出力バッファ100を検査することである。第1の高速チャンネル回路は高速フィルタ105であり、それはまたデジタル的に台形フィルタリングを実現するが、しかし低速チャンネルにおけるよりももっと短い時定数である。ピーク検出器107は、少なくとも設定した連続する数のサンプルについて設定されたしきい値を越える各ピークについてその出力を検査し、そしてこれらのピークの到着時間の最大値を得る。これらの各到着時間は関連するX線事象到着時間を定義し、出力バッファ100へのトリガーのタイミングに使用される。ピーク検出器からの各出力パルスは、低速フィルタ98で最大値が一部重なり合う(重ね合せ)各事象を拒絶する重ね合せ検査器108によって検査される。重ね合せ検査器108が良好なピークを検査するごとに、第2のステージの処理に対してDSP27へ送る低速フィルタ98の出力値を獲得するために出力バッファ100を起動させる。各ピーク検出器107の出力パルスはまた入力カウント・レート(ICR)カウンタ110を進める。低速チャンネルにおけるのように、高速チャンネルの動作はDSP27からロードされた各パラメータによって制御される。すなわち、高速フィルタの長さとギャップ112、ピーク検出器のしきい値と最小ピーク幅各試験値113と、重ね合せ検出器に必要な、ピーク相互の間隔,高速ピーク最大幅,タイミングオフセット値115である。

出力バッファ100が起動されるごとに、それはまた、ICRカウンタ110の値とどんな形式の低速フィルタの値が得られたのかを印すフラグの、2つの別の各値を得る。そのバッファはしたがってDSP27に4つの各値を出力する。すなわち、2つの得られた低速フィルタの各値PKVAL117,UFVAL118と、最後の出力からのX線PLOUT119の数と、PKVAL117はX線の振幅か規格化を目的とするベースラインの値かどうかを指示するBLFLG120のフラグである。

FiPPIの最終の回路は、デジタルスペクトロメータがデータを集めるのにかかる正確な時間であるTIME122を測定するライブタイムカウンタ121である。これは2つの理由で有用である。第1は、制御コンピュータ28によってソフトウェア制御の下でスタートしたデータ習得処理を正確に計測することは、別のやり方では難しいことである。第2は、多重検出器システムにおいては、各スペクトロメータが、そのカウント・レートを正確に測定できるようにそれ自身のライブタイムを正確に測定できることは重要である。

3.3.FiPPIの具体的な実施例における分岐回路の動作

FiPPIの好適な実施例における分岐回路の実現と動作は、それら各々信号トレースを併せて図6から13に回路の概略によって示されている。これらの各回路と各軌跡は、デジタルエレクトロニクスの従来技術の当事者にとっては大部分は自明のことであろう。次の段落では、主にそれらの機能について述べ、明らかにされていないあらゆる設計の議論を示す。

3.3.1.デシメータ

図6Aは、4でデシメイトするハードワイヤードされた具体的な実施例のデシメータであって、しかも図6Bに示された各信号を代表的な信号とする、デシメータ97の回路の概略である。それはクロック分周器123とN値加算器125を備え、それは10ビット入力線ADCBUS50からの4つの連続した値を加算し、10ビット線CS147にその和を出力する。もしさらなる精度が所望されるならば、より多くのビットがCSに記憶される。同類の各技術を使えば、どんな任意のパラメータD_Facter102によってデシメイトする回路は容易に構成される。

3.3.2.低速フィルタモジュール

台形フィルタの機能は各時刻{i}のときの各データ{di}のストリームの{Ti}として、次の式で与えられる。

ここでLとGは低速フィルタの間隔長LSとギャップ間隔GSで、パラメータ103として本モジュールに入れている。GSがゼロのとき、三角フィルタの機能は得られる。両形式はアナログスペクトロメータの論文で広く議論されている。台形関数の振幅は、もしギャップGSが十分に長いならば、電荷収集時間と独立にされることができ、したがって弾道欠損の現象が避けられる。しかし短い整形時間に対するノイズ比のその信号は、三角関数のものほどは良くない。本場合においては、選択はパラメータS_LengthとS_Gap103によって定められる。

極端なFPGAの実体能力を消費する長い合計を避け、またゆっくり動作するために、式3は次のように計算し直され得る。

部分和(di-L-G−di-2L-G)はちょうど、タイムステップLs+Gsで以前に算出された部分和(di−di-L)であるので、先入れ・先出し(FIFO)メモリを2つだけを使って、式4に基づきTiを生成することができることがわかる。ここに1つのLsビット深さによって、項(di−di-L)を生成する値を保持し、また1つの(Ls+Gs)ビット深さによって式4を実現する値を保持する。

図7Aの回路の概略と図7Bの各波形は、10ビット入力について、式4に基づき、Tiの値を生成する低速フィルタモジュール98の実現について述べている。そのフィルタ内の全構成要素の幅は、デシメーションの各ビットについて1ビットだけ、拡張するであろう。デシメータ97からの入力CS[9:0]は、漏れ電流検出器の効果及び/またはASC23の動作を表わす一般的なパルスの前及び後の両方に、わずかな傾きを有する。

FIFOメモリ148と減算器150は、項(di−di-L)を生成する。ここで、LはパラメータPA[4:0]152によって設定される。FIFOメモリ158と減算器160は項(di−di-L)−(di-L-G+di-2L-G)を生成する。ここで、L+GはパラメータPB[4:0]162によって設定される。そしてアキュムレータ168は式4の各値Tiを生成し、ラインFS[11,0]173に出力する。3クロック周期の各パイプラインディレイが生成される。アキュムレータ168で12ビットを使用することは、X線の狭い領域が予期され、ひとつのX線ステップはADC入力範囲の約5%であるようにASCゲインが最適に設定されることができるXAS機器に対する技術的なトレードオフである。より一般的な設計では、アキュムレータの増加するビット数は有利なことである。

したがって、C[9:0]F[11:0]のステップ関数は、立ち上がり,立ち下がり時間175,177が両方とも“ピーク時間”TPKに等しくてLに等しい台形パルスになる。その上辺178は持続時間TGPを持ち、その“ギャップ時間”はPA152とPB153の差Gに等しい。図7BのトレースFS[11:0]の黒い点は、もしそのピークが重ね合わされてなければ重ね合せ検査器はバッファ100に出力するためにFS[11:0]を得るような時間tmを示す。CS[9:0]がまた得られたときは、これはパイプラインディレイが占めるよりも3クロック周期早くなる。

出力FS[11:0]173は信号CS[9:0]147の傾きに比例するゼロでないベースラインを持つ。したがって、ピークの各振幅はベースラインに対して計られ、それはしたがってまた正確に決定される。また、CS[9:0]の傾きが時間で一定でないとき(直流プリアンプに関しては)、そのベースラインは検出された各X線パルスに対して部分的に測定されるべきである。

デシメータ97と低速フィルタ98の組み合せは、32深さ(deep)だけの各FIFOと12ビットアキュムレータとを使った400サンプル(20MSA ADCについて20μs)までのピーク時間を許容する。だが一方で直接的に実現するには400深さの各FIFOと18ビットアキュムレータとが必要であろう。これがより少ないFPGAゲートを必要とするだけでなく、より短いワードの長さが、別の方式よりもより安い程度(grade)のFPGAを使っても回路が十分早く動くようにする。

3.3.3.FIFOの具体的な実現例

図8Aと8B8、Lsが3に等しいXilinx4000シリーズFPGAを使っている回路とFIFO148の具体的な実現例の波形を示す。設計が別の各FIFOは同様に実現できる。10個の32ビットの深さの各メモリ(データビットあたり1)は周期アドレスカウンタ185によって周期的にアドレスされる。周期アドレスカウンタ185の出力QCはクロック128と位相がずれている。そのXilinxメモリは、それゆえ、QCによって最初にアドレスされたとき、バッファ188によって得られる蓄積されたデータO[9,0]をディスプレイする。そしてこれらの各値は、クロックが正に進むに連れて、C147の新しい各値によって上書きされる。したがって読み出しと書き込みは、PA152カウントによって入力から遅れた出力値とともに、1クロック周期で達成される。

3.3.4.高速フィルタ

高速フィルタ105は低速フィルタがそれ自身の各制御パラメータF_LengthとF_Gap 112をもち、ADC48の10ビット出力50で直接動作すること以外は、低速フィルタと厳密に同じ方法で実現される。そのピーク時間とギャップ長は式4から、“fast”を意味する添え字をfとして、Lf,Gfとして書かれる。

3.3.5.重ね合せ検査

3.3.5.1重ね合せの意味

重ね合せ検査を理解するためには、連続する各入力パルス間の時間間隔の関数として、低速フィルタ98と高速フィルタ105の各パルス出力がどのように変化するか理解すべきである。図9A〜9Gがこの情報を表わし、これらの図には、2つの入力パルス間の時間が減少するときの、高速フィルタ192と低速フィルタ193の各出力トレースの重畳が示されている。もし2つのピークが適度に分離されている(図9A〜9C)のなら、低速フィルタのピークはX線のエネルギの測定を正確に維持する。より短い時間では、これらのピークは次第に変わり、拒絶(reject)されるべきである。最小許容分離は第1のピークがサンプルされてから1クロック周期後に第2のパルスが始まる(パイプラインディレイに対して補正された)ときである。さもなければ2つの各パルスは重ね合せされる。各パルスが連続して減少している間の間隔で、高速の各パルスはまた結果的に重ね合わさり、なおも重ね合せする(図9Eから9F)。

3.3.5.2.ピーク検出

第1の議論はピーク検出器107の関数であるパルスを検出することである。好適な実現は、タイミングジッタ(timing jitter)を持ちノイズフロアに近い振幅を持つパルスに対してはあまり良好に動作しない、従来の分別器(discriminators)を越えて改良された動作を提供する。ここで、図10Aから10Bの回路とトレースで示されているように、しきい値195はパラメータPC207で設定される。しかし、信号値FF205は、少なくとも連続して最低の数min_width113(パラメータPD208で設定される)の回数がしきい値を越えるときにピークとみなされるだけである。このような状態の下で信号REP223とSFP225は生成される。RFPはFFがしきい値を越え続けている限りは続く。しきい値195とmin_width113両方の値は、ノイズフロアをはるかに越えて上昇はしないソフトX線パルスとともに動作するとき、ノイズ耐性が増えるように調節され得る。

3.3.5.3.到着時間の確定

第2の議論は、図11Aから11Bの回路とトレースで示されるように、重ね合せ検査器108のブロック240の関数であるパルス到着時間を決定することである。ここで、高速のピークのロケーションは、しきい値195とそれが交差することによってではなく、その最大値の時間T3 196によって確定される。RFP223がハイのときはいつも、このブロックは、FF173をバッファ250で前もって得られた最大値と比較し、新しい最大値が見つけられるごとにFTOP255をハイにセットする。到着時間のロケーションTS194は本質的に独立した振幅であり、大いにタイムジッタ(tims jitter)を減らして低速チャンネルのピーク振幅決定の歪みに依存するどんなエネルギも取り除く。

3.3.5.4低速ピーク振幅の獲得

一度ピークが検査されると、FiPPIは、それが重ね合せと無関係かどうかを決定しなければならず、もしそうならば、低速チャンネルでその振幅を得る。実際の獲得は出力バッファ100によって実行され、それは図11Aにおいてより詳細に示されており、信号PSAM298によって起動される。低速ピーク振幅の獲得のタイミングは、図9Aに示されるように、概念的には明確である。所望の獲得時間T4198は台形の上辺の中点にある。高速低速両チャンネルのデジタル処理動作は数が固定されているので、T4198は一定時間TS194によって高速ピーク到着時間T3から分離され、それはD_Facter 102,S_LengthとS_Gap 103,F_LengthとF_Gap 112のようなFiPPI制御パラメータにのみに依存する。それゆえ、高速ピーク検査に続いて、カウンタは時間TS194を測定することができ、転送された低速フィルタ98の出力をバッファ100へ転送する。

3.3.5.5.低速チャンネルの重ね合せ検査

FiPPIにデジタル的で実現された重ね合せ検査は、概念的にアナログ分光回路で一般に見られることと同じである。すなわち、連続した各パルスは、低速チャンネルのピーク時間の数倍だけ分離されていなければならないことを、必要とする。アナログ三角フィルタリングの場合では、1.5から2.5の倍数が一般に使われる。図9Aが示すように、本当の台形フィルタリングでは、連続した各パルスは、単一の低速フィルタのピーク時間に上辺の時間の半分を足したものによってのみ分離される必要がある。アナログ“三角”パルスがピークが減衰した側で1ピーク時間を越えて十分に拡大するテールを持っているという事実は、それらの拡大した検査時間の原因である。デジタル的に生成した各パルスは、図7Bに示されるように、きれいに消滅し、より短い重ね合せ検査時間が使われるようになる。2あるいはそれ以上のカウント・レートの可能性が増えるという結果になるということは証明されている。

立ち下がり重ね合せ検査は、図11Bで示されるトレースで図11Aで示される回路のブロック243によって実行され、信号FTOP255の隣接した各終端の間の時間間隔を測定する。高速ピーク最大値、そしてその到着時間に印をつける降下するFTOP信号は、Interval_1カウンタ260をスタートさせ、重ね合せ検査期間のパラメータPF268と共にロードされる。もしカウンタが首尾よくオーバーフローしFF16265に蓄積された値がパルスが立ち上がり重ね合せエッジを持っていないことを表わすならば、信号は低速チャンネルのピークが得られる時間TS194をカウントするのを終える第2のインターバルカウンタブロック245について発せられる。Interval_2カウンタは、低速フィルタのパイプラインディレイを適合させる必要があり、10進クロックと共に動作しているであろう。

Interval_1カウンタ260がオーバーフローしたとき、それは再スタートさせられ、Pass_Cutカウンタ261は減少する。もしInterval_1カウンタ260が2度オーバーフローしたならば、それは低速フィルタの出力がベースラインに戻ることができるほどパルス間の期間がとても長いことを意味する。このような条件の下では、もしDSP27がフラグBLCOL315をセットするならば、Interval_2カウンタ245はベースライン獲得を初期化するよう起動させられる。ビットBL278は、この状態を意味するために、出力値BLFLG120としてバッファ100によって得られる。

ピークが立ち上がり重ね合せエッジと関係するか否かは、フリップフロップFF16265によって決定され、このFF16265は、新しい高速パルスが検出されるごとに、信号SFP228を受けて、Pass_Cutカウンタ261の値を蓄える。もしこの値が1ならば、最後のパルスから少なくともPF268の時間が経っていることになる。

フィルタを通していない出力CS(図7B参照)が必要なときは、時間T4198の前の3低速クロック周期が得られなければならず、それは、Interval_1カウンタが実際にそのピークが有効かどうかを確定してしまう前である。この時間はそれゆえコンパレータCMP23262によって確定され、CSの適切な値が、もしそのピークが有効ならば出力バッファ100へ転送されることができる中間バッファ307で得られる。

3.3.5.6.高速重ね合せ試験

第1の高速重ね合せ試験は図11Aのブロック242によって実現され、しきい値195で高速パルスの幅を測定する。図9Eから9Fが示すように、もしこの値TWが最大値TM200以上ならば、その時は高速チャンネルで重ね合せが起きているに違いなく、低速チャンネルのピーク値は無効であろう。この結果は、検出されたとき、フリップフロップ16265に蓄積され、低速ピークの獲得を妨げる。パラメータPMとしきい値は共に1件1件基準に調整されることができるので、高速ピーク検出回路と結び付けるときこれはとても効果的な試験である。単色光X線とともに、XASにあるように、各パラメータは、従来のアナログ試験よりも大きさが3けたまで低くなり得る重ね合せレートに達することができるように調整される。

3.3.5.7入力カウント・レートカウンタとタイマー

図12Aから12Bにおける回路と各トレースは、FIPPI15の入力カウント・レートカウンタ110(図5参照)の実施例を表わす。本回路は、検出されたそれぞれの有効X線パルスに対して検出されたX線パルスの合計数を記録するために、高速パルス到着信号SFP228とPass_Cutカウンタ261の出力Q10[0]270を使っている。その出力NSFP340は、それがバッファ100を読み出すのと同時にDSP27によって読み出されることができる。

図13の回路は、FiPPI15のライブタイムカウンタ121(図5参照)の実施例を表わす。本回路は、DSP27がC_Enable 273を経由して信号を送るとき、すなわちデータを収集するモードにおけるときははいつも、分割クロック信号をカウントする。

3.3.5.8.任意の高速重ね合せ試験

第2の高速重ね合せ試験は図14Aから14Bに示される回路と各トレースによってさらに実現されることができる。本回路は、高速ピークの幅をその最大値の半分において測定する。別の各比は容易に置き換えられることができる。Half_Widthカウンタ357がピーク幅を最大限に許容された値PKと比較する間、Inspect−1カウンタは検査期間PL 362をセットする。高速パルス信号FF173は、Q7251がその最大値に達する機会を得るまで、FIFO10353によってPJ358カウントが遅延させられる。もし高速ピークがこの試験について重ね合せられるのなら、出力MWID1367は、低速ピークの獲得を妨げるために、フリップフロップFF16265をセットするのに使われることができる。

広い範囲の振幅を持つパルスが示されるとき本試験はとくによく動作し、しきい値がピーク振幅のかなり大きな部分となる低い振幅のパルスに対して、高速パルスと重ね合せ試験が最大限に利用されることを防ぐ。この場合、2つの低い振幅パルスが重ね合せでき、まだ基本幅の重ね合せ試験値より小さいこれら2つの幅の和をもつ、とても広い時間の範囲が存在する。

3.3.6.任意の出力バッファリング

本回路はこの具体的な実現に示されていないにもかかわらず、もっとも高いカウント・レートに設計されたシステムでは、われわれは、それぞれが強力ないくつかの獲得された値であり得る3つの出力バッファ100を3つの短いFIFOによって取り替えることが好適であることを知った。本修正はDSP27が、どのようにそれがFiPPIから獲得されたピーク値を集めるかにおいて、より適応性を持たせる。示された好適な実施例では、ひとつが信号として送られるごとに、0.5μs以下で獲得された値を取ってくる計算を休止する割込み制御の下でDSPは動作する。割り込みルーチンを提供する本システムは、より少ないFiPPI回路リソースを使うにもかかわらず、より多くのそして平均ではより遅いDSPコードを必要とする。任意のFIFO出力と共に、それがルーチンを処理し、けっして割り込みを受けない固定された点のデータに対してFiPPIを得ることができ、それはその平均処理速度を増加させる。本実現はしたがって非常に最高のデータ・レートが適応されなければならないときに好まれる。

我々は本動作をモデル化しており、DSP27が、各事象を処理するごとに少なくとも一度はDSPFLAG302を得て、それらの平均レートで事象を処理できるほど速いならば、本バッファは、すべての事象の大多数を得る約4つの事象の深さだけ必要であることがわかっている。

4.DSP:デジタル信号処理装置と論理

4.1.DSPの概略

我々の設計の考え方に基づき、システムレベル動作を保つために、DSPは“事象ごとに”基づいたものであってもあるいはあまり頻繁でなくても必要とされるそれらの各タスク、各処理、各計算を実行する。図2に示されるように、DSP27の主な各タスクは、汎用制御コンピュータとインターフェイス28との相互連携することと、ASC23を調整して制御することと、FiPPI25からのデータ値を収集,補正,ヒストグラム化することを含む。本発明の一般的な実行は、これらの機能は、プロセッサとメモリの広範な組み合わせによって満たされることができ、具体的な実施例のいずれの選択も、コスト,速度,大きさなどのような考え方に基づいた技術的な決断が主である。

4.2.DSPハードウェアの実施

NECμPD77016プロセッサが具体的な実施例では使用されている。高速で、低価格で、その制御プログラムとそのMCA機能を生成するスペクトラを保持する十分な内部メモリを持つ16ビットDSPなのでそれが選ばれた。その2.0KのXデータメモリは、MCAスペクトラ用にされ、スペクトラが、32ビット(あるいは40億カウント以上)の深さごとに1024箱(bin)ビンまでヒストグラム化されるようにする。その2.0KのYデータメモリはシステム動作を制御するのに必要な各変数と各定数、すなわちシステムの遂行を監視するためのデータ、MCA処理のためのFiPPI事象を一時的に蓄えるためのサーキュラーバッファ(circular buffer)を蓄える。内部メモリは本発明には必要はなく、全体のあわせた数とコストを減らし、より高速の動作を与える。外部から与えられたクロック周期の半分で各指示を実行するので、ADCサンプルごとに1つ指示するという同期した動作を作るために、DSPはADCとFiPPIの比の厳密に倍でクロックされる。それは4つの外部割り込み線をもっているが、その外部割込み線はDSPがASC23,FiPPI25,外部制御コンピュータ28に応答するようにする。

マイクロプロセッサやDSPをプログラミングしたり割り込んだりすることに関係する一般的な議論は、従来技術の当業者にとっては公知であり、細い説明は行われない。各制御プログラムの一般的な各フローチャートは示されており、所望の機器機能を得るように発明された具体的なアルゴリズムに注目が集中する。

4.3.DSPハイレベルソフトウェアの説明

4.3.1.監視制御プログラム

図15は、この具体的な実施例で使われた監視制御プログラムのハイレベルフローチャートを示す。太字体の矢印は、信号データ収集サイクルを通したプログラム制御の流れを描いている。動作はDSPプログラムのダウンロードと、各レジスタのセットアップとYデータメモリの定数を初期化することを含む初期化380によって始まる。そしてそのプログラムはその主な制御ループである、CAMACモニタリングタスク382にとりかかる。具体的な実施例では制御コンピュータインターフェイスはCAMACインターフェイス基準であるIEEE基準583-1975を使うように実現されており、本選択は本発明の機能には決定的ではない。CAMACモニタリングタスク382においてはDSPは本質的にループの中にあり、割り込まれるのを待つ。

DSPへの及びそれからのデータ転送は、そのデジタルスペクトロメータ22のインターフェイスを通して制御コンピュータ28によって起動される。そのようなインターフェイスの実現の詳細はその技術の当業者によって公知である。データ転送のこれらの要求は、インターフェイスがDSPに対して転送割り込み383を発生するようにする。このような転送割り込み383を受けたとき、DSPはDSPへ/からの転送データ385を移動させる。ここで、それはインターフェイス28の2つの状態レジスタを読み込み、データワードをDSPメモリロケーションへインターフェイスレジスタから転送するかあるいはその逆にするかを決めるために使う。DSPは要求された転送をさせ、そしてデータワードをCAMACモニタリングタスク382に送る。多重ワードデータ転送は2MBytes/sまでのレートのDSPのブロックのデータ転送モードを使うよう実現したのと類似している。

デジタルスペクトロメータ22が効率的に制御され得る前に、それは、制御コンピュータ28からダウンロードされたり(たとえばFiPPI25のフィルタ長)、システムを較正することによって経験的に決められたり(たとえばスロープDSP38の推定値)しなければならない、色々な定数と制御パラメータの数値が必要である。特に注目すべきは制御ワードRUNTASKSであり、これはDSPプログラムを制御するフラッグの組である。獲得割り込み387が受け取られたとき、獲得タイプ388はRUNTASKSを試験することによって確定される。

4.3.1.1.各試験/校正ルーチン

もし獲得タイプが試験/校正390ならば、DSPは試験/校正各ルーチン392を実行し、それは正しいシステム動作を確認し、ASCに対するDAC制御を校正する。それらは次を含む:

1)ASC23の動作点をセットするために、バイアス32,オフセット37,スロープ38,ゲイン43の各DACへ書き込む。

2)第1にスペクトロメータ22に対して入力を分離し、バイアスDAC32を使ってオペアンプ30に印加された連続した電圧値についてADC48の出力を記録することによってシステム全体のゲインを測定する。結果にぴったりあったときは、ボルト入力あたりのADC単位を生じ、それはまさにデジタルスペクトロメータのゲインである。これは、eVあたりのADCの各ステージの全体のシステムゲインを得るために、X線エネルギのeVあたりの電圧であるプリアンプのゲインによって倍にされることができる。もしプリアンプのゲインがわからなければ、この定数を求めるべく既知のX線エネルギを測定することができる。

3)1つのステップごとにADCの出力を変えるのに必要なオフセットDACのステップの数である、規格化した定数DAC/ADCを得るために、上のルーチン2)の時と同じ処理によって、ADCのオフセットDAC37を校正する。

4)スロープDAC38へ既知の各値をセットすることと、生成された信号がADC入力範囲を越えるのに必要な時間を測定することによって傾き生成器を校正する。傾きはスロープDAC38からの電流入力と、積分キャパシタ72の大きさとにだけ依存し、それによってDAC/ADC値の良好な第2の試験が与えられる。

5)制御された入力波形としてASCの傾き生成器を使ってADCの微分積分非線形性を試験する。

6)スペクトラムデータなしでASC割り込みを監視する。

7)DSPでADCの出力信号トレースを得る。このモードは、ADC−DSPの組み合わせが本質的に簡単なデジタルオシロスコープとして動作するモードで、信号トレースを獲得することによって検出器の問題をデバッグするのに特に有効となり得る。

8)FiPPIのデシメータの各出力値C[9:0]147を獲得する。これはルーチンNo.7と同じ有効性を持っているが、より低速なデシメータの出力で動作する。

9)入力X線信号をシミュレーションするために、まずスペクトロメータ22の入力を分離し、そしてバイアスDAC32によって電圧の各ステップの出力を使ってスペクトラムを集めることによって全部のスペクトロメータの正しい動作を確認する。出力スペクトラムは全体のシステムゲインの直接測定する場所を持ち、スペクトロメータのノイズを測定する幅を持つ、単一の狭いピークであるべきである。本試験は、完全な計器は選ばれたデジタルフィルタのパラメータで正確に動作していることの数値的な診断である。

これらの試験は、本発明のデジタルスペクトロメータが自己試験と自己校正をしていてまた製造するときの品質コントロール試験に有効であるようにする。普通の動作では、制御コンピュータ28はデータを集めようとすることより先にスペクトロメータが正確に動作しているか確かめるために、これらのプログラムの試験一式を走らせる。

4.3.1.2.データ獲得

獲得割り込みのタイプがデータ393のとき、データ獲得の準備をするために(リセット形プリアンプを想定している)、DSPはスタートデータ獲得ルーチン395に進み、次のタスクを実行する。

1)X線のエネルギ範囲、プリアンプの特性、初期速度推定値によって確定される各値を指定するために、ASCのバイアスDAC32、オフセットDAC37,スロープDAC38,ゲインDAC43をセットする。

2)MCAデータと統計値をゼロにリセットする。

3)低速フィルタ長と各ギャップ値103,高速フィルタ長とギャップ112,ピーク検出器試験値113,FiPPIに対する重ね合せ検査器の値115の、各制御パラメータのデシメーション要素102を書き込み、FiPPIの動作を再起動する。

4)傾き生成器を非活性化(disable)しながら、時間に対するADCの各値を観察することによってASCモニタリングを始める。プリアンプの信号のランプの傾きを推定し、スロープDAC38の値がそれと一致するように計算する。そしてリセット値をオフセットDAC37へロードし、傾き生成器35を活性化する(enable)。

5)もしASC28の出力の信号がADC48の入力範囲を超えたとき、DSPに割り込みをするために、ASCコンパレータ割り込みを割込み可能にする。

6)低速フィルタのベースラインの各値の最初の一組を集め、ベースラインの平均値と分散量を計算する。

7)FiPPIデータの受領の準備のために、ポインタの各値をDSPのYデータメモリのサーキュラー事象ループバッファへセットアップする。

8)FiPPIが有効なピーク振幅を獲得したとき、FiPPIがDSPに信号を送るように、FiPPIの割り込み信号DSPFLAG302をイネーブルにする。

4.3.1.3.データ獲得タスク

もしこれらの処理のいずれかが失敗したときは、プログラムは中止し、さもなければデータ獲得タスク402へ進む。このタスクは、500,000cpsまでの平均レートでデータを処理している間、2,000,000cps(最低0.5μsの低速チャンネルピーク時間の逆数)までのデータ到着レートでのバーストに適用できるよう設計されている。これは、サーキュラーバッファへの到来データを蓄えることによって達成され、これは割込み制御の下での高速処理であり、さらに各割り込み間の間隔を有する安定レートでそれらを処理する。これは約4のファクタによって平均処理レートを減少させ、安価なDSPが使用できるようにする。

獲得FiPPIデータルーチン405は、データ獲得ステップを実行する。ここでDSPは、各値PKVAL117,UFVAL118,BLFLG120,PLOUT119を含むFiPPIから2つの16ビットワードを読み込む。そしてそれはこれら2つのワードをサーキュラーバッファに書き込み、それらのアドレスに対してポインタを増加させる。これらの動作は5あるいは6のクロック周期だけを必要とする。次にサーキュラーバッファに残っているいずれのデータも処理するために、制御はデータ獲得タスク402へ戻る。これは、プリセットの事象の最大限の数が処理されるまで、あるいはストップデータ獲得407が起きるまで続く。いずれのケースでも、プログラムは終了データ獲得408へ進み、その主な機能は、ASCコンパレータ割り込み45を割込み禁止にすること,FiPPIの割り込み302を割込み禁止にすること,サーキュラーバッファに残っているいずれのデータの処理も終わらせること,ライブタイムカウンタ121の値を記録することである。プログラムはその後CAMACモニタリングタスク382へ戻るが、ここでは集められたデータはロードされないようにできる。

データ獲得タスク402はまた、ASC23の出力がADC48への入力の範囲を越えるどんなときでもASC割り込み410によって割り込まれることができ、以下に記述するように、固定ADC範囲外状態412ルーチンのブランチへ押し込む。一度正しいASC動作が復活すると、プログラムはサーキュラーバッファのデータ処理へ戻る。

4.3.2.データ獲得タスクソフトウェア

図16は、データ獲得タスク402の具体的実施例のフローチャートを示す。大部分については、本チャートは、制御コンピュータプログラミングの当事者にとって自明であろう。一般的な解説の他では、我々の議論は、本発明のスペクトロメータの機能について特有である各ステップに集中する。そのプログラムは、本質的には、試験NEVENTS=MAX?463が真という理由から、あるいはRUNTASKSが試験RUN ENDED?440で見つかるまで、サーキュラーバッファからのデータを処理するループである。一度ループの256回すべてとADCの状態の独立の試験とが行われると、ベースラインの推定値はUPDATE BASELINE ESTIMATE(更新ベースライン推定値)438に対して低速フィルタから集められ、これについてはさらに後で議論することにする。256という数字は重要ではなく、変化する実験状態をたどることができるほどしばしば更新されるが、しかしデータ獲得タスク402内で実質的な計算の負担とならないようにあまり更新されないように、ベースラインが選ばれている。

処理ループでは、一旦良好な事象からのデータがバッファ452から読み込まれると、全事象数は、値PLOUT119を使って453で増加する。全カウント数は、正確な到来カウント・レート推定値を得るために、記録されたライブタイムで割る。PLOUT値の統計量も集めることができ、過剰な流量のような不正確な各実験状態に対して監視するように使われる。その後DSPは、ASC23からのひずみに対してやその他、獲得された低速フィルタの各値PKVAL117とUKVAL118から正確なX線エネルギ455を計算するのに必要である計算と修正を行う。選択されたアルゴリズムは、本発明のスペクトロメータが接続された検出器−プリアンプの組み合わせに充当される。これは発明されたステップであり、さらに後で記述される。一度エネルギが見つかると、多チャンネル分析(MCA)ビン(bin)458を計算するためにそれは測定されて、そしてそのビンは、その分野の当業者にとって公知である各技術を使って、検出されたX線スペクトラムのヒストグラムを生成するために増加する。

4.4.スペクトロメータ制御と計算アルゴリズム

本発明のデジタルスペクトロメータシステムは、3つの接続された各モジュール、ASC23,FiPPI25,DSP27を備えるので、今までにない新しいアルゴリズムで効率的にそれらを制御する必要がある。これらは次の各節で記述される。

4.4.1.ADCの範囲外状態の固定

本問題の本質は、入力カウント・レートの変動がASCアナログ小区分23の出力をもたらすことができ、その出力はADC48の入力電圧の範囲(例えば、図1EのLLからUKの範囲)外に一時的に落ちるためにプリアンプの入力とLFFの関数生成器35の間の増幅された差であるということである。これは図17Aと17Bによって図示される。図17Aはもっとも一般的な場合を示し、ここで、一時的に高いレート(トレースB)あるいは低いレート(トレースC)は平均のレート(トレースA)に戻っている。X線の到着が本当にランダムなので、しかし各場合のいくつかの小さな部分は図17Bで表れており、高(トレースD)あるいは低(トレースE)到着レートは、ADCの入力範囲LLからULを越えることができるほど十分に長く持続する。これは、FiPPI25のデータ・ストリームを無効にし、DSP27が正しい動作をするように要求する。ASCの出力信号がADCの入力範囲に戻るまで、各信号をLFF生成器35の各制御DAC37,38を調節することによってそれが起こる。図17Cと17DはDAC37が調整される2つの例を示している。一般的に直面する変動のタイプは、プリアンプの各リセット、検出器における宇宙線の各事象,検出器へのX線の到着レートにおける統計的変動を含む。

図18に示されるアルゴリズムは、高速で効率的な方法でこれらの場面を扱うように設計されており、好適な実現では、一般に約2μs以内で適切な動作に回復する。以下のいくつかの説明で、このアルゴリズムはコンピュータプログラミングの分野の当業者にとって明確になるであろう。この動作箱(action boxes)“Move Down1”495と“MoveUp1”504は、DAC37による調整を委ね、“単位”ステップは、図17Cと17Dに示されるように、ADC入力範囲を交差する半分の動作に必要なDACビットの数である。“リセット”箱498は、プリアンプのリセットが検出されており、スイッチ75を使うことと、DAC37がその基準値に戻ることによってLFF生成器35もリセットされるように要求していることを意味する。箱“もしABC(フラグ)が1ならば、トラッカーを更新する”511は、図17Bで示されるように、範囲外の単純なドリフトが検出され、次のセクションで記述される傾きを追跡するアルゴリズムが実施されなければならないことを意味する。

4.4.2.推定値をセットするスロープDAC38の更新

スロープDAC38が正確に設定されたとき、平均して、範囲外への逸脱は、ハイとローの方向で均一に起こる傾向があるべきである。しかし、もし到来X線レートが変わるなら、そのときは、スロープDACは調整される必要があろう。したがって、プログラムが固定ADC範囲外状態412ルーチンを呼び出すごとに、それが実際にはハイかローのどちらであるかを注意し、スロープDACの設定の調整が必要がある。

したがって、“トラッカーを更新する”511が呼び出されるごとに、具体的な実施例においては、次式によって過去の範囲外の状態の指数関数的に減衰するメモリの持つ重みWは更新され、式によると

ここでVi=+1に等しいときハイ、−1に等しいときロー範囲外である。その後Wiが試験されて、もしそれが試験値Vを越えるなら、それはゼロにされ、スロープ38は適切な方向の1ビットによって調整される。その他の点では何もされず、そのプログラムは進む。移動平均のような他の式は、Wiを計算するのに使うことができるが、式5は最小のメモリや計算だけが求められるときに有効である。

4.4.3.パルスの高さの振幅のエネルギの計算

4.4.3.1.周期的なリセットのプリアンプの場合

計算のいくつかは、システムのエラーを持ち出さないで、FiPPI25の出力値PKVAL117をX線エネルギへ変換する必要があり、その主な理由は、図1Bにあるように、ASC23出力のX線ステップの直前直後の各領域は平らではなく、図1Eにあるように、傾いている。それは周期的なリセットのプリアンプのこの傾きに対する2つの寄与があるからである。第1は、ASC23がLFF生成器35によって生成される傾きを減じるからであり、第2は、検出器かプリアンプの第1のFETかのいずれかからの漏れ電流のためである。

FiPPI25のこの傾いた信号に対する応答は図19A(PRプリアンプの場合に対して)に示される。振幅Aが所望されるにもかかわらず、FiPPIは値Hを生成し、それは端の上方と下方の2つの各領域の間の差である。計算ではしたがって測定された値HからAを取り戻す必要がある。図19Aはそれを示し、GSのギャップ時間とともに低速フィルタの長さLSに対して:

ここで、V1とV2はフィルタ領域を越える平均電圧であり、Sは生成した傾きSGと漏れ傾きS1の間の差である。したがって:

我々はそれゆえ、第2の期間の正確な推定値を得ることを望む、そうしないとスペクトロメータのエネルギ分解能を下げる。LSとGSはパラメータであり、厳密に知られており、生成された傾きSgである。S1は測定されなければならず、Aが0に等しいとき、X線の各事象がフィルタ内のいずれの場所でも存在しているとき、式7によって長さを使ってなされる。いま、Hが−(Sg−S1)(Ls+Gs)に等しく、三角パルスの間の“ベースライン”であるとする。多くの測定をすることによって、われわれは任意の精度で中間のベースラインの値Bを推定することができる。

ここで、PKVALBは、これより前で述べられているように、フラグBKCOL315が1にセットされたときに、FiPPIから得られたPKVAL117の値である。与えられたBで、われわれは次からX線エネルギを計算することができる。

ここでGはシステムのゲインで、PKVALの通常の値、すなわちフラグBKCOL315を0にセットした値である。

ベースラインBは、スペクトロメータの分解能に影響しないよう十分正確に決定されなければならない。式9において、ガウス分布エラーであるとみなして、PKVALの各分散量σP,σBとBを直角位相で足し算するので、σBはしたがってσPの1/10の次数であり、BはPKVALBのおおよそ100の測定量の平均から決定される。

好適な実施例でのBの決定は、2つのステップで進む。第1は、スタートデータ獲得ルーチン395のタスクNo.6で、PKVALBの100の測定がなされ、そしてそれらの平均Bと分散σBが計算される。これは正確なBのスタート値を供給する。第2に、データ獲得タスク402(図16)で、UPDATE BASELINE ESTIMATE 438の手順における全256ループのたびに、Bは更新される。Bの様々な移動平均をとる計算がされるとき、具体的な実施例では、

は指数関数的に減衰する過去の履歴を実現するように作られている。ここでbiは、PKVALB+SB(LS+GS)の現在の測定された値である。Bの現在の値だけ蓄えられ、もし比が2の累乗ならばシフト構造を使った固定点DSPでかなり速く実行することができるので効率的である。実験は、かなり速いBの変化でさえ、この技術によって正確に追跡できることを示す。もしBが非常に速く変化するのが予想されるのなら、NLOOP Modulo256=0TEST428の値256をベースラインをさらに頻繁にサンプルすべく、減少させることができる。

4.4.3.2.連続した放電をするプリアンプの場合

CDプリアンプについは、図19B,20に示されているように、X線ステップの事象の両側の信号は、異なる平均の傾きで指数関数的に減衰している。この状態はそれゆえPRプリアンプよりもさらに複雑であり、式9に取って代わる修正されたアルゴリズムが必要である。しかし、スペクトロメータのハードウェアもFiPPIのファームウェアもどちらも変える必要はない。

図20はこの状態を示す。われわれは、振幅Aを所望するが、しかし、パルスの後の0.5(LS+GS)で得られた移動平均<V2>とパルスの前の0.5(LS+GS)で得られた<V1>との差である値Hを得る。S1,S2は2つの測定点での信号の傾きであり、VeはX線の事象の直前の時間teにおけるその値であり、V0は指数関数的に減衰する値である。われわれは、K=(LS+GS)/2τによって一定値Kを定義するが、ここでτはプリアンプの指数関数的な減衰時間である。

それゆえ指数関数的減衰は:t<teに対して

t>teに対して

われわれは次式によってHを近似することができる:

傾きS1とS2は、同じ精度に対して:

式13に代入して次式が与えられる。

ここで、VeとV0はともに測定された変数ではない。われわれは、いずれの点においても瞬間的な電圧を測定することによってVeの推定値を得ることができる。数学的に簡単にするために、われわれは、時間(LS+GS)/2において、点V2を選ぶ。ここで、

式15に代入すると次式が得られる。:

ここでHとV2は測定された量で、V0は一般に一定である。Aはちょうど式9のようにしてX線エネルギを得るシステムのゲインGによって測定できる。2KV0の推定値は、X線が存在しないときAの値を測定することによって得られる。2KV0は、式9でベースラインBがするように式18でAの値を計算する厳密に同じ役割をし、同じアルゴリズムは正確にその値を推定するのに使うことができる。検出器の漏れ電流から生じるあらゆる線形の傾きの項はまたこの項に分類される。

CDプリアンプの校正を実現すること、したがってDSP27の符号を実現することは、式9は次式によって置き換えられて:

<V0>の計算に使われるV0の個別の各値は次式からわかる。

4.4.3.3.一つおきの連続した放電をするプリアンプの場合

ノイズ解析によって、式19は、Kの値が小さくはない(例えば、フィルタの時間がプリアンプの減衰時間に達する)とき、過剰なノイズの被害を被ることが分かる。この理由は、フィルタ長が減少するにつれPKVALにおけるノイズが減少するからであるのと、フィルタにかけていない項UFVALの重みKが増加するからである。50μsという一般的なプリアンプの減衰時間において、20μsでノイズはだいたい90%増加するのに対して、4μsのフィルタリングにおける分解能は、数パーセントだけ減少する。

議論は、そして、式18を使ってV2の申し分なくより正確な値を得ることである。<V2>はわれわれが作ることができるもっとも正確な測定量V2であることを認識し、Hはちょうど<V2>−<V1>であることに注目することによって、われわれは、Hについて式12から式13へ、S2とS1を置き換えることによって交互の補正を引き出すことができる。H=<V2>−<V1>であることに注意すると:

<V2>及び<V1>の双方を、平均のフィルタを通した平均値<V2>と<V1>によって置き換え、再び整理して次式が得られる。

これは式18の置き換えであり、ここで、いま全項は可能な限り統計的に正確である。

式21Aと式21Bにおける概略とトレースによって示されるように、式22を満たすには修正されたFiPPIの低速フィルタの設計が必要であり、図7Aと図7Bと比較されるべきである。本回路は移動平均V2を生成し、その後V1を生成するためにFIFOを使うが、それは適切に減衰した信号とちょうど同じである。4ビットでのデシメーションは一般に興味のある長い整形時間に必要とされているので、入力信号CS[13:0]527はいま14ビット幅である。FIFO528の長さは、LsであるパラメータPA[13:0]152によって設定される。D532は、X線パルスがADCの入力範囲の1/8を越えないという推定のもとに12ビットだけ持つ。その他の点では、Dと、続いている各ステージにおけるビットの数は増加するかもしれない。V2とV1の間の遅れはLs+Gsに等しく、FIFO537へのパラメータPB[4:0]162によって設定される。V2とV1は、V2[16:0]535の出力はPKVAL117として、V1[16:0]538の出力はPKVAL118として、上で記述されたように正確に重ね合せ検査器108の動作によって出力バッファ100で得られる。

FiPPIは、好適な具体例ではフィールド・プログラマブル・ゲート・アレイ(FPGA)において実現されるので、式18と式22のうちから選ぶことは、物理的にスペクトロメータを変えるのではなく、FPGAのダウロードされたファイルとDSPのソフトウェアを変えるだけである。

式18と式22は、減衰する各指数曲線と独立に提案されたデジタルの実施例の内容に単に基づいて導き出されたので、それらはまたアナログ方式で実施されることができる。したがってCDプリアンプを三角波整形とベースライン補正をするアナログ分光アンプをDC接続し、式18のHとしてアンプの出力を、V2としてアンプの入力の遅れ時間の複製を使うことによって、そして指数関数形減衰をする信号に起因する瞬時のベースラインシフトに校正される信号が生成され、AC接続されたシステムで要求であるゼロ極補償の必要を取り除く。

式22はまた、図22で大まかに示されているように、アナログ回路を使うことで実現されることができる。本回路は、アナログエレクトロニクスの従来技術の当業者にとっては明確であるだろうが、図21Aに示されるデジタル回路の直接アナログ変換を備え、V2とV2の合計を実現するオペアンプ合計回路(op-amp summing circuit)522と接続される。V0の校正は、従来技術の当業者にとっては公知であるように、ベースライン復元回路を回路の出力に付加することによって実際には提供される。本回路は、特にアナログ遅延回路が簡単に実現される時間期間内で、各方法の存在を越えて高入力レートと短い波形整正時間が所望されたとき、実質的な有利な点を提供する。

5.結論

結論では、本発明は、検出器−プリアンプのシステムからのパルスの各信号を処理し、検出器に影響を与える放射線の完全なエネルギ分析を提供する、物理的にコンパクトで、低価格で、高速な方法と機器をもたらす。プログラムされたプロセッサがその事象のレートにおいてより精練された分析を実行するのに使われている間、組み合せ論理は、限定されてはいるがサンプリング・レートにおいて十分な量の処理を実行するのに使われる。本作業部分は発明が高パフォーマンスで低価格を達成するようにする。

上記が本発明の具体的な実施例の完全な記述であるにもかかわらず、各種の変形例、別の構成、等価物が使われ得る。第1の例としては、具体的な実施例では、必要とするADCのビット数を減らすために、信号処理フロントエンド(signal conditoning front end)を使っているにもかかわらず、本発明の他の動作は本装置に従属ではない。もし、より安く、より速いより多くのビットを持つ各ADCが利用できるならば、この部分は取り除かれるかもしれない。さらに、本発明に必要な様々な計算を実行するために単一のデジタル信号処理装置を使うのに効果的なコストであるにもかかわらず、これらの計算は多重マイクロプロセッサ間で分配され、具体的な各機器に(例えばより高い総合カウント・レート能力が必要なとき)おいてはこれはより効果的になるかもしれない。したがって、上の記述は、付属の各請求項によって定義された本発明の範囲を制限するものとして受けとめられるべきではない。

Claims (6)

- ステップ状パルスを含む電気信号を分析する高速でデジタルベースの方法であって、平均レートで前記電気信号が到着し、前記ステップ状パルスの少なくともいくつかの各振幅を推定する方法において、

前記平均レートより大きいサンプリング周波数で動作するアナログデジタル変換器(ADC)で前記電気信号をデジタル化し、デジタル化された入力信号を生成するステップと、

周波数Sあるいはその倍数のクロックで動作するデジタルの組合せ論理回路を提供するステップと、

前記組合せ論理回路に組み合わされるプログラマブル・デジタル計算素子(DSP)を提供するステップと、

前記組合せ論理回路を使って、デジタル整形フィルタに前記デジタル化された入力信号を入力するステップと、

前記組合せ論理回路を使って、前記デジタル化された入力信号における前記パルス信号の存在を検出するステップと、

前記組合せ論理回路を使って、前記デジタル整形フィルタの出力から前記パルス信号の各振幅の推定値を引き出すステップと、

前記組合せ論理回路から前記DSPへ前記推定値を転送するステップと、

前記DSPを使って、前記推定値を修正するステップとを備える方法。 - 請求項1の方法であって、前記DSPを使って実行され、前記推定値を、エネルギ範囲の配列のうちいずれか1つのエネルギ範囲に割り振ることで、前記修正されたパルスの前記振幅のスペクトラムを作るステップをさらに備える方法。

- 請求項1の方法であって、アナログ信号処理回路によって実行される、前記ADCに入力される前までのアナログ電気信号をアナログ信号処理するステップをさらに備える方法。

- 請求項1の方法であって、前記デジタル化された入力信号を生成するステップの前に実行されるステップであって、前記入力信号のダイナミックレンジよりも小さいダイナミックレンジを有する入力信号を生成するために選択されたパラメータのセットに従って前記入力信号を調整するステップをさらに有する方法。

- 請求項4の方法であって、

各パラメータの前記セットを前記DSPに伝えるステップをさらに備え、

前記推定値を修正するステップにおいて前記DSPが前記パラメータのセットの値を使用する方法。 - 請求項4の方法であって、

前記調整された入力信号が前記ADCの入力範囲を越えるかどうかを検出するステップを備え、

もし前記調整された入力信号が前記ADCの入力範囲を越えるならば、前記DSPの動作に割り込みをかけるステップと、前記入力信号が前記ADCの入力範囲へ戻るように前記パラメータのセットを調節するように前記DSPに信号を送るステップと、のうち少なくとも1つを実行する方法。

Applications Claiming Priority (11)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US226695P | 1995-08-14 | 1995-08-14 | |

| US60/002,266 | 1995-08-14 | ||

| US08/730,916 | 1996-08-02 | ||

| US08/695,062 US5774522A (en) | 1995-08-14 | 1996-08-02 | Method and apparatus for digitally based high speed x-ray spectrometer for direct coupled use with continuous discharge preamplifiers |

| US08/702,327 | 1996-08-02 | ||

| US08/695,062 | 1996-08-02 | ||

| US08/695,063 US5684850A (en) | 1995-08-14 | 1996-08-02 | Method and apparatus for digitally based high speed x-ray spectrometer |

| US08/695,063 | 1996-08-02 | ||

| US08/730,916 US5873054A (en) | 1995-08-14 | 1996-08-02 | Method and apparatus for combinatorial logic signal processor in a digitally based high speed x-ray spectrometer |

| US08/702,327 US5870051A (en) | 1995-08-14 | 1996-08-02 | Method and apparatus for analog signal conditioner for high speed, digital x-ray spectrometer |

| PCT/US1996/013082 WO1997007591A1 (en) | 1995-08-14 | 1996-08-09 | Method and apparatus for digitally based high speed x-ray spectrometer |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007062409A Division JP2007163516A (ja) | 1995-08-14 | 2007-03-12 | デジタルベースの高速x線スペクトロメータについての方法と装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH11510900A JPH11510900A (ja) | 1999-09-21 |

| JP4083802B2 true JP4083802B2 (ja) | 2008-04-30 |

Family

ID=27532952

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP50940597A Expired - Lifetime JP4083802B2 (ja) | 1995-08-14 | 1996-08-09 | デジタルベースの高速x線スペクトロメータについての方法 |

| JP2007062409A Pending JP2007163516A (ja) | 1995-08-14 | 2007-03-12 | デジタルベースの高速x線スペクトロメータについての方法と装置 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007062409A Pending JP2007163516A (ja) | 1995-08-14 | 2007-03-12 | デジタルベースの高速x線スペクトロメータについての方法と装置 |

Country Status (4)

| Country | Link |

|---|---|

| EP (1) | EP0880821B1 (ja) |

| JP (2) | JP4083802B2 (ja) |

| DE (1) | DE69631165T2 (ja) |

| WO (1) | WO1997007591A1 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4880077B1 (ja) * | 2011-02-16 | 2012-02-22 | 株式会社リガク | X線検出信号処理装置および方法 |

| US8374814B2 (en) | 2011-02-16 | 2013-02-12 | Rigaku Corporation | X-ray detection signal processing apparatus and method therefor |

Families Citing this family (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3304801B2 (ja) * | 1997-02-05 | 2002-07-22 | 日本電子株式会社 | Ad変換回路 |

| US6587814B1 (en) * | 1999-08-27 | 2003-07-01 | William K. Warburton | Method and apparatus for improving resolution in spectrometers processing output steps from non-ideal signal sources |

| US6609075B1 (en) * | 2001-06-04 | 2003-08-19 | William K. Warburton | Method and apparatus for baseline correction in x-ray and nuclear spectroscopy systems |

| US6732059B2 (en) * | 2001-08-23 | 2004-05-04 | William K. Warburton | Ultra-low background gas-filled alpha counter |

| JP3980451B2 (ja) * | 2002-08-30 | 2007-09-26 | 株式会社東芝 | 波形弁別装置 |

| EP1706759A1 (en) * | 2004-01-13 | 2006-10-04 | Koninklijke Philips Electronics N.V. | Analog to digital conversion shift error correction |

| US7966155B2 (en) * | 2004-06-04 | 2011-06-21 | William K. Warburton | Method and apparatus for improving detection limits in x-ray and nuclear spectroscopy systems |

| CN101124725B (zh) | 2004-09-16 | 2012-06-20 | 南方创新国际私人有限公司 | 用于从检测器输出数据中分解单个信号的方法和设备 |

| EP2092369B1 (en) | 2006-12-13 | 2011-05-18 | Koninklijke Philips Electronics N.V. | Apparatus and method for counting x-ray photons |

| US8338791B2 (en) * | 2007-06-19 | 2012-12-25 | Koninklijke Philips Electronics N.V. | Digital pulse processing for multi-spectral photon counting readout circuits |

| WO2009121131A1 (en) | 2008-03-31 | 2009-10-08 | Southern Innovation International Pty Ltd | Method and apparatus for borehole logging |

| AU2009230876B2 (en) | 2008-03-31 | 2014-07-10 | Southern Innovation International Pty Ltd | Radiation imaging method with individual signal resolution |

| JP2011516838A (ja) | 2008-03-31 | 2011-05-26 | サザン イノヴェーション インターナショナル プロプライアトリー リミテッド | スクリーニング方法および装置 |

| WO2010068996A1 (en) | 2008-12-18 | 2010-06-24 | Southern Innovation International Pty Ltd | Method and apparatus for resolving piled-up pulses by using a mathematical transform |

| US8330123B2 (en) * | 2010-01-28 | 2012-12-11 | I.S.S. (Usa), Inc. | System and method for digital parallel frequency fluorometry |

| US8446308B2 (en) * | 2011-04-21 | 2013-05-21 | Kabushiki Kaisha Toshiba | Apparatus for detection of a leading edge of a photo sensor output signal |

| EP2530490B1 (en) * | 2011-06-03 | 2019-02-27 | Toshiba Medical Systems Corporation | Device for radiation detection, radiation detection system and radiation detection method |

| CN102353972B (zh) * | 2011-07-01 | 2013-04-10 | 成都理工大学 | 多种模式的数字化多道谱仪 |

| JP5823208B2 (ja) * | 2011-08-19 | 2015-11-25 | 株式会社東芝 | X線コンピュータ断層撮影装置 |

| WO2013073071A1 (ja) * | 2011-11-15 | 2013-05-23 | 富士電機株式会社 | パルス処理装置および放射線分析装置 |

| FR2984041B1 (fr) | 2011-12-13 | 2014-01-10 | Commissariat Energie Atomique | Numerisation asynchrone de signaux transitoires issus de detecteurs de rayonnement |

| JP6159144B2 (ja) * | 2013-05-10 | 2017-07-05 | 株式会社堀場製作所 | パルス波高検出装置、放射線検出装置、放射線分析装置、及びパルス波高検出方法 |

| JP6381973B2 (ja) * | 2014-06-03 | 2018-08-29 | 株式会社日立製作所 | 高計数率用パルス型放射線検出器 |

| JP6545221B2 (ja) * | 2017-05-15 | 2019-07-17 | アンリツ株式会社 | スペクトラムアナライザ及び信号分析方法 |

| US10224192B2 (en) * | 2017-07-21 | 2019-03-05 | Atonarp Inc. | High-speed low-noise ion current detection circuit and mass spectrometer using the same |

| US11646190B2 (en) | 2017-07-21 | 2023-05-09 | Atonarp Inc. | Current detection device and spectrometer using the same |

| US11417509B2 (en) | 2017-07-21 | 2022-08-16 | Atonarp Inc. | Current detection device and spectrometer using ihe same |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| NL7110516A (ja) * | 1971-07-30 | 1973-02-01 | ||

| US4658216A (en) * | 1983-07-14 | 1987-04-14 | The United States Of America As Represented By The Department Of Energy | High resolution, high rate X-ray spectrometer |

| HU210832B (en) * | 1986-05-07 | 1995-08-28 | Mta Atommag Kutato Intezete | Method for processing signals and adaptive implementation of said method for nuclear spectrometers |

| US5067090A (en) * | 1989-05-01 | 1991-11-19 | Schlumberger Technology Corporation | Nuclear spectroscopy method and apparatus for digital pulse height analysis |

| US5304808A (en) * | 1993-02-08 | 1994-04-19 | The United States Of America As Represented By The United States Department Of Energy | Method and apparatus for data sampling |

| US5349193A (en) * | 1993-05-20 | 1994-09-20 | Princeton Gamma Tech, Inc. | Highly sensitive nuclear spectrometer apparatus and method |

-

1996

- 1996-08-09 JP JP50940597A patent/JP4083802B2/ja not_active Expired - Lifetime

- 1996-08-09 WO PCT/US1996/013082 patent/WO1997007591A1/en active IP Right Grant

- 1996-08-09 EP EP96928138A patent/EP0880821B1/en not_active Expired - Lifetime

- 1996-08-09 DE DE69631165T patent/DE69631165T2/de not_active Expired - Lifetime

-

2007

- 2007-03-12 JP JP2007062409A patent/JP2007163516A/ja active Pending

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4880077B1 (ja) * | 2011-02-16 | 2012-02-22 | 株式会社リガク | X線検出信号処理装置および方法 |

| WO2012111195A1 (ja) * | 2011-02-16 | 2012-08-23 | 株式会社リガク | X線検出信号処理装置および方法 |

| US8374814B2 (en) | 2011-02-16 | 2013-02-12 | Rigaku Corporation | X-ray detection signal processing apparatus and method therefor |

Also Published As

| Publication number | Publication date |

|---|---|

| DE69631165D1 (de) | 2004-01-29 |

| JPH11510900A (ja) | 1999-09-21 |

| EP0880821A4 (en) | 2000-03-01 |

| DE69631165T2 (de) | 2004-09-02 |

| EP0880821A1 (en) | 1998-12-02 |

| EP0880821B1 (en) | 2003-12-17 |

| JP2007163516A (ja) | 2007-06-28 |

| WO1997007591A1 (en) | 1997-02-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4083802B2 (ja) | デジタルベースの高速x線スペクトロメータについての方法 | |

| US5684850A (en) | Method and apparatus for digitally based high speed x-ray spectrometer | |

| US5774522A (en) | Method and apparatus for digitally based high speed x-ray spectrometer for direct coupled use with continuous discharge preamplifiers | |

| US5873054A (en) | Method and apparatus for combinatorial logic signal processor in a digitally based high speed x-ray spectrometer | |

| JP5425071B2 (ja) | パルスプロセッサのエネルギー測定フィルタの応答を調整する方法およびこの方法を実行するパルスプロセッサ、エネルギー分散型放射線分光分析システム | |

| AU2005253117B2 (en) | Method and apparatus for improving detection limits in X-Ray and nuclear spectroscopy systems | |

| US6609075B1 (en) | Method and apparatus for baseline correction in x-ray and nuclear spectroscopy systems | |

| US6590957B1 (en) | Method and apparatus for producing spectra corrected for deadtime losses in spectroscopy systems operating under variable input rate conditions | |

| US7411198B1 (en) | Integrator circuitry for single channel radiation detector | |

| US7521682B1 (en) | Processing circuitry for single channel radiation detector | |

| JP2008501954A5 (ja) | ||

| Warburton et al. | Digital pulse processing: new possibilities in nuclear spectroscopy | |

| Jordanov et al. | Digital pulse processor using moving average technique | |

| Arnold et al. | TNT digital pulse processor | |

| Drndarevic et al. | Digital signal processing for high rate gamma-ray spectroscopy | |

| HU210832B (en) | Method for processing signals and adaptive implementation of said method for nuclear spectrometers | |

| Chrien et al. | Noise and pileup suppression by digital signal processing | |

| Murray et al. | A low power, high count rate radiation detection chip using a current subtraction technique | |

| CN109283569B (zh) | 用于测量光子信息的装置和光子测量设备 | |

| Lauer | Digital signal processing for segmented HPGe detectors: preprocessing algorithms and pulse shape analysis | |

| JP2003508764A (ja) | 非理想的な信号源からの出力ステップを処理する分光計における分解能を改善する方法及びその装置 | |

| Bogovac et al. | Digital pulse processor for ion beam microprobe imaging | |

| Cardoso et al. | A mixed analog-digital pulse spectrometer | |

| Durán et al. | Evaluation of digital pulse processing techniques for a β-γ coincidence counting system | |

| Kasani et al. | High count-rate digital gamma-ray spectroscopy using a low-cost COTS digitizer system |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060912 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20061211 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20061211 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20070129 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070312 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20071016 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071116 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080115 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080214 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110222 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120222 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120222 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130222 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130222 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140222 Year of fee payment: 6 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |