JP4027349B2 - 電力増幅器 - Google Patents

電力増幅器 Download PDFInfo

- Publication number

- JP4027349B2 JP4027349B2 JP2004185274A JP2004185274A JP4027349B2 JP 4027349 B2 JP4027349 B2 JP 4027349B2 JP 2004185274 A JP2004185274 A JP 2004185274A JP 2004185274 A JP2004185274 A JP 2004185274A JP 4027349 B2 JP4027349 B2 JP 4027349B2

- Authority

- JP

- Japan

- Prior art keywords

- base

- terminal

- impedance circuit

- power amplifier

- resistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Landscapes

- Amplifiers (AREA)

Description

上記エミッタ接地バイポーラトランジスタのベース端子と上記ベースバイアス電圧供給端子との間に上記抵抗に対して並列に接続され、直流成分に対して開放であると共に交流成分に対して導通であるインピーダンス回路部とを備え、

上記インピーダンス回路部は、

一方の端子が上記エミッタ接地バイポーラトランジスタのベース端子に接続され、他方の端子が信号入力端子に接続された第1のインピーダンス回路と、

一方の端子が上記信号入力端子に接続され、他方の端子が上記ベースバイアス電圧供給端子に接続された第2のインピーダンス回路とを有し、

上記第1のインピーダンス回路または上記第2のインピーダンス回路の少なくとも一方が直流成分に対して開放であると共に、上記第1のインピーダンス回路および第2のインピーダンス回路の両方が交流成分に対して導通であることを特徴としている。

上記複数個の増幅部の第1のインピーダンス回路または上記第2のインピーダンス回路の少なくとも一方が直流成分に対して開放であると共に上記第1のインピーダンス回路および第2のインピーダンス回路の両方が交流成分に対して導通である。

図1に、この発明の電力増幅器の第1の実施の形態を示す。この第1実施形態の電力増幅器は、ベース端子B,コレクタ端子Coを有したエミッタ接地型バイポーラトランジスタQ1と、ベースバイアス電圧供給端子VBとベース端子Bの間に接続された抵抗RBを備える。上記エミッタ接地型バイポーラトランジスタQ1のコレクタ端子Coは信号出力端子RFOUTに接続されている。

次に、図2に、この発明の電力増幅器の第2の実施の形態を示す。この第2の実施形態は、前述の第1の実施形態に比べて、具体的かつ簡素な実施形態の一例であり、図1における第1のインピーダンス回路Z1をキャパシタC1で構成し、第2のインピーダンス回路ZZをキャパシタCa1で構成したものである。

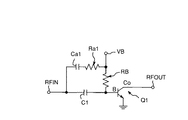

次に、図3に、この発明の第3の実施形態を示す。この第3実施形態は、前述の第2実施形態において、キャパシタCa1に直列に抵抗Ra1を接続した直列回路を第2のインピーダンス回路としたものである。第1のインピーダンス回路は、第2実施形態と同様、キャパシタC1で構成した。

次に、図4に、この発明の電力増幅器の第1の参考例を示す。この第1参考例は、ベース端子Bとコレクタ端子Coを有するエミッタ接地型バイポーラトランジスタQ1と、ベースバイアス電圧供給端子VBとベース端子Bの間に接続された抵抗RBとを有する。上記エミッタ接地型バイポーラトランジスタQ1のコレクタ端子Coは信号出力端子RFOUTに接続されている。

次に、図5に、この発明における電力増幅器の第2の参考例を示す。この第2参考例は、第1の参考例のより具体的かつ簡素な一例である。すなわち、この第2参考例では、図4に示した第1インピーダンス回路Z1をキャパシタC1とし、第2インピーダンス回路ZZをキャパシタCa1としたものである。

次に、図6に、この発明の電力増幅器の第4の実施形態を示す。この第4実施形態は、エミッタ接地型のn個のバイポーラトランジスタQ1〜Qnを備える。エミッタ接地型バイポーラトランジスタQ1〜Qnは、そのコレクタ端子Co1〜Conが信号出力端子RFOUTに接続され、エミッタが接地されている。

次に、図7に、この発明の電力増幅器の第5の実施の形態を示すものである。この第5実施形態は、前述の第4実施形態のより具体的かつ簡素な実施形態の一例である。この第5実施形態は、図6におけるn個のインピーダンス回路Z1〜Znを、n個のキャパシタC1〜Cnで構成し、かつ、1つの第2インピーダンス回路ZZを1個のキャパシタCaxで構成したものである。

次に、図8に、この発明の電力増幅器の第6の実施形態を示す。この第6実施形態は、前述の第5実施形態におけるキャパシタCaxに換えて、このキャパシタCaxに抵抗Raxを直列に接続した直列回路を備え、この直列回路が第2のインピーダンス回路を構成している。

次に、図9に、この発明の電力増幅器の第3の参考例を示す。この第3参考例は、n個のエミッタ接地型のバイポーラトランジスタQ1〜Qnを備えている。このn個のエミッタ接地型バイポーラトランジスタQ1〜Qnのコレクタ端子Co1〜Conは信号出力端子RFOUTに接続されている。

次に、図10に、この発明の電力増幅器の第4の参考例を示す。この第4参考例は、前述の第3参考例のより具体的かつ簡素な一例である。すなわち、この第4参考例は、図9における第2のインピーダンス回路Zx1〜ZxnをキャパシタCx1〜Cxnで構成し、第1のインピーダンス回路Z1〜ZnをキャパシタC1〜Cnで構成している。

この第4参考例によれば、このような簡素な回路構成でもって、熱的な安定動作と低歪み動作の両立を実現できる。

次に、図12に、この発明の第7の実施の形態を示す。この第7実施形態の電力増幅器は、上述の図1に示される第1実施形態の電力増幅器Amp1のベースバイアス電圧供給端子VBとベース電圧供給手段であるベース電圧供給回路121との間に、可変インピーダンス回路122が接続されている。

次に、図13に、第8の実施形態を示す。この第8実施形態は、図12に示した第7の実施の形態における可変インピーダンス回路122をより具体的な回路構成の可変インピーダンス回路132とした。

次に、図14に、第9の実施形態を示す。この第9の実施形態は、図12に示した第7の実施の形態における可変インピーダンス回路122をより具体的な回路構成の可変インピーダンス回路142とした。

次に、図15に、第10の実施の形態を示す。この第10実施形態は、図12の第7実施形態のベース電圧供給回路121に替えて、第1のベース電圧供給回路151と第2のベース電圧供給回路152を備える。また、この第10実施形態では、図12の可変インピーダンス回路122に替えて、可変インピーダンス回路153を備える。

Qx…バイポーラトランジスタ、

Dx…ダイオード、

Z1〜Zn…第1のインピーダンス回路、

ZZ,Zx1〜Zxn…第2のインピーダンス回路、

RFIN…信号入力端子、RFOUT…信号出力端子、

VB…ベースバイアス電圧供給端子、

B,B1〜Bn…ベース端子、Co,Co1〜Con…コレクタ端子、

RB,RB1〜RBn,Rx1,Rx11,Rx2,Rx22…抵抗、

C1〜Cn,Ca1,Cax,Cx1〜Cxn,Cx,Cxx…キャパシタ、

121,151,152…ベース電圧供給回路、

122,132,142,153…可変インピーダンス回路。

Claims (3)

- コレクタ端子が信号出力端子に接続されたエミッタ接地バイポーラトランジスタと、上記エミッタ接地バイポーラトランジスタのベース端子とベースバイアス電圧供給端子との間に接続された抵抗と、

上記エミッタ接地バイポーラトランジスタのベース端子と上記ベースバイアス電圧供給端子との間に上記抵抗に対して並列に接続され、直流成分に対して開放であると共に交流成分に対して導通であるインピーダンス回路部とを備え、

上記インピーダンス回路部は、

一方の端子が上記エミッタ接地バイポーラトランジスタのベース端子に接続され、他方の端子が信号入力端子に接続された第1のインピーダンス回路と、

一方の端子が上記信号入力端子に接続され、他方の端子が上記ベースバイアス電圧供給端子に接続された第2のインピーダンス回路とを有し、

上記第1のインピーダンス回路または上記第2のインピーダンス回路の少なくとも一方が直流成分に対して開放であると共に、上記第1のインピーダンス回路および第2のインピーダンス回路の両方が交流成分に対して導通であることを特徴とする電力増幅器。 - 請求項1に記載の電力増幅器において、

上記エミッタ接地バイポーラトランジスタと上記抵抗と上記第1のインピーダンス回路とが構成する増幅部を複数個だけ備え、

上記複数個の増幅部の第1のインピーダンス回路または上記第2のインピーダンス回路の少なくとも一方が直流成分に対して開放であると共に上記第1のインピーダンス回路および第2のインピーダンス回路の両方が交流成分に対して導通であることを特徴とする電力増幅器。 - 請求項1または2に記載の電力増幅器において、

上記第1または第2インピーダンス回路のうちの少なくとも一方が、キャパシタを有し、このキャパシタによって、直流成分に対して開放であると共に交流成分に対して導通になっていることを特徴とする電力増幅器。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004185274A JP4027349B2 (ja) | 2002-02-27 | 2004-06-23 | 電力増幅器 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002051600 | 2002-02-27 | ||

| JP2004185274A JP4027349B2 (ja) | 2002-02-27 | 2004-06-23 | 電力増幅器 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002273169A Division JP4287116B2 (ja) | 2002-02-27 | 2002-09-19 | 電力増幅器 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004266875A JP2004266875A (ja) | 2004-09-24 |

| JP2004266875A5 JP2004266875A5 (ja) | 2006-01-26 |

| JP4027349B2 true JP4027349B2 (ja) | 2007-12-26 |

Family

ID=33133448

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004185274A Expired - Lifetime JP4027349B2 (ja) | 2002-02-27 | 2004-06-23 | 電力増幅器 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4027349B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4699204B2 (ja) * | 2005-12-28 | 2011-06-08 | 新日本無線株式会社 | 高周波増幅回路 |

-

2004

- 2004-06-23 JP JP2004185274A patent/JP4027349B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2004266875A (ja) | 2004-09-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4287116B2 (ja) | 電力増幅器 | |

| US7834700B2 (en) | Radio frequency power amplifier | |

| KR102268387B1 (ko) | 적응형 다중밴드 바이어스 제어 회로 및 파워 증폭 장치 | |

| US8994453B2 (en) | Power amplifier | |

| US8497736B1 (en) | Direct DC coupled push-pull BJT driver for power amplifier with built-in gain and bias current signal dependent expansion | |

| US20060261897A1 (en) | Radio frequency power amplifier | |

| JP4088177B2 (ja) | バイアス電流供給回路及び増幅回路 | |

| JP2017103643A (ja) | 電力増幅回路 | |

| US10910999B2 (en) | Bias circuit | |

| JP5487328B2 (ja) | 高パワー広帯域増幅器及び方法 | |

| US20050068107A1 (en) | Amplifier power control circuit | |

| CN107493072B (zh) | 具有增强的净空的缓冲器 | |

| US7057462B2 (en) | Temperature compensated on-chip bias circuit for linear RF HBT power amplifiers | |

| JP2005101734A (ja) | 高出力増幅回路 | |

| JP3523638B2 (ja) | 電力増幅器の動作点の調整のための回路装置 | |

| US9148095B2 (en) | Bias circuit and amplifier controlling bias voltage | |

| US6879214B2 (en) | Bias circuit with controlled temperature dependence | |

| JP4027349B2 (ja) | 電力増幅器 | |

| US10826438B2 (en) | Bias circuit | |

| JP3770306B2 (ja) | ベースバイアス回路及びこのベースバイアス回路を用いた電力増幅器 | |

| US10386880B2 (en) | Circuit arrangement for compensating current variations in current mirror circuit | |

| US12119792B2 (en) | Variable gain amplifier circuit and semiconductor integrated circuit | |

| JP2008154043A (ja) | バイアス回路、能動素子回路、および、電力増幅器 | |

| JP2004172681A (ja) | 電力増幅器用バイアス回路 | |

| JP2006041996A (ja) | 電力増幅器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040623 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20051202 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20060301 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060314 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060511 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20061226 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070226 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20071002 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20071009 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101019 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4027349 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111019 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121019 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131019 Year of fee payment: 6 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |