JP4014633B2 - ディスクドライブ、差分距離ビタビ検出器、およびツリー検索ビタビ検出器 - Google Patents

ディスクドライブ、差分距離ビタビ検出器、およびツリー検索ビタビ検出器 Download PDFInfo

- Publication number

- JP4014633B2 JP4014633B2 JP51668397A JP51668397A JP4014633B2 JP 4014633 B2 JP4014633 B2 JP 4014633B2 JP 51668397 A JP51668397 A JP 51668397A JP 51668397 A JP51668397 A JP 51668397A JP 4014633 B2 JP4014633 B2 JP 4014633B2

- Authority

- JP

- Japan

- Prior art keywords

- distance

- difference

- servo

- time

- state

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000004044 response Effects 0.000 claims description 42

- 238000001514 detection method Methods 0.000 claims description 37

- 238000005070 sampling Methods 0.000 claims description 31

- 230000001360 synchronised effect Effects 0.000 claims description 27

- 230000007704 transition Effects 0.000 claims description 12

- 238000012937 correction Methods 0.000 claims description 11

- 238000013500 data storage Methods 0.000 claims description 11

- 238000001228 spectrum Methods 0.000 claims description 10

- 230000004907 flux Effects 0.000 claims description 7

- 238000007476 Maximum Likelihood Methods 0.000 claims description 5

- 238000001914 filtration Methods 0.000 claims description 3

- 230000002051 biphasic effect Effects 0.000 claims 1

- 238000010586 diagram Methods 0.000 description 16

- 238000000034 method Methods 0.000 description 13

- 230000003044 adaptive effect Effects 0.000 description 5

- 230000001143 conditioned effect Effects 0.000 description 3

- 238000012545 processing Methods 0.000 description 3

- 238000011084 recovery Methods 0.000 description 3

- 230000008901 benefit Effects 0.000 description 2

- 238000004364 calculation method Methods 0.000 description 2

- 238000012546 transfer Methods 0.000 description 2

- 238000012935 Averaging Methods 0.000 description 1

- 238000009825 accumulation Methods 0.000 description 1

- 230000003321 amplification Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 238000009833 condensation Methods 0.000 description 1

- 230000005494 condensation Effects 0.000 description 1

- 238000010276 construction Methods 0.000 description 1

- 230000003111 delayed effect Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 239000000284 extract Substances 0.000 description 1

- 238000009432 framing Methods 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 230000005415 magnetization Effects 0.000 description 1

- 238000003199 nucleic acid amplification method Methods 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 238000000819 phase cycle Methods 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 238000013139 quantization Methods 0.000 description 1

- 230000011664 signaling Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/38—Synchronous or start-stop systems, e.g. for Baudot code

- H04L25/40—Transmitting circuits; Receiving circuits

- H04L25/49—Transmitting circuits; Receiving circuits using code conversion at the transmitter; using predistortion; using insertion of idle bits for obtaining a desired frequency spectrum; using three or more amplitude levels ; Baseband coding techniques specific to data transmission systems

- H04L25/4904—Transmitting circuits; Receiving circuits using code conversion at the transmitter; using predistortion; using insertion of idle bits for obtaining a desired frequency spectrum; using three or more amplitude levels ; Baseband coding techniques specific to data transmission systems using self-synchronising codes, e.g. split-phase codes

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B20/00—Signal processing not specific to the method of recording or reproducing; Circuits therefor

- G11B20/10—Digital recording or reproducing

- G11B20/10009—Improvement or modification of read or write signals

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B27/00—Editing; Indexing; Addressing; Timing or synchronising; Monitoring; Measuring tape travel

- G11B27/10—Indexing; Addressing; Timing or synchronising; Measuring tape travel

- G11B27/19—Indexing; Addressing; Timing or synchronising; Measuring tape travel by using information detectable on the record carrier

- G11B27/28—Indexing; Addressing; Timing or synchronising; Measuring tape travel by using information detectable on the record carrier by using information signals recorded by the same method as the main recording

- G11B27/30—Indexing; Addressing; Timing or synchronising; Measuring tape travel by using information detectable on the record carrier by using information signals recorded by the same method as the main recording on the same track as the main recording

- G11B27/3027—Indexing; Addressing; Timing or synchronising; Measuring tape travel by using information detectable on the record carrier by using information signals recorded by the same method as the main recording on the same track as the main recording used signal is digitally coded

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B5/00—Recording by magnetisation or demagnetisation of a record carrier; Reproducing by magnetic means; Record carriers therefor

- G11B5/48—Disposition or mounting of heads or head supports relative to record carriers ; arrangements of heads, e.g. for scanning the record carrier to increase the relative speed

- G11B5/54—Disposition or mounting of heads or head supports relative to record carriers ; arrangements of heads, e.g. for scanning the record carrier to increase the relative speed with provision for moving the head into or out of its operative position or across tracks

- G11B5/55—Track change, selection or acquisition by displacement of the head

- G11B5/5521—Track change, selection or acquisition by displacement of the head across disk tracks

- G11B5/5526—Control therefor; circuits, track configurations or relative disposition of servo-information transducers and servo-information tracks for control thereof

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B5/00—Recording by magnetisation or demagnetisation of a record carrier; Reproducing by magnetic means; Record carriers therefor

- G11B5/48—Disposition or mounting of heads or head supports relative to record carriers ; arrangements of heads, e.g. for scanning the record carrier to increase the relative speed

- G11B5/58—Disposition or mounting of heads or head supports relative to record carriers ; arrangements of heads, e.g. for scanning the record carrier to increase the relative speed with provision for moving the head for the purpose of maintaining alignment of the head relative to the record carrier during transducing operation, e.g. to compensate for surface irregularities of the latter or for track following

- G11B5/596—Disposition or mounting of heads or head supports relative to record carriers ; arrangements of heads, e.g. for scanning the record carrier to increase the relative speed with provision for moving the head for the purpose of maintaining alignment of the head relative to the record carrier during transducing operation, e.g. to compensate for surface irregularities of the latter or for track following for track following on disks

- G11B5/59688—Servo signal format patterns or signal processing thereof, e.g. dual, tri, quad, burst signal patterns

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B2220/00—Record carriers by type

- G11B2220/20—Disc-shaped record carriers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B5/00—Recording by magnetisation or demagnetisation of a record carrier; Reproducing by magnetic means; Record carriers therefor

- G11B5/48—Disposition or mounting of heads or head supports relative to record carriers ; arrangements of heads, e.g. for scanning the record carrier to increase the relative speed

- G11B5/58—Disposition or mounting of heads or head supports relative to record carriers ; arrangements of heads, e.g. for scanning the record carrier to increase the relative speed with provision for moving the head for the purpose of maintaining alignment of the head relative to the record carrier during transducing operation, e.g. to compensate for surface irregularities of the latter or for track following

- G11B5/596—Disposition or mounting of heads or head supports relative to record carriers ; arrangements of heads, e.g. for scanning the record carrier to increase the relative speed with provision for moving the head for the purpose of maintaining alignment of the head relative to the record carrier during transducing operation, e.g. to compensate for surface irregularities of the latter or for track following for track following on disks

- G11B5/59633—Servo formatting

- G11B5/5965—Embedded servo format

Landscapes

- Engineering & Computer Science (AREA)

- Signal Processing (AREA)

- Physics & Mathematics (AREA)

- Spectroscopy & Molecular Physics (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing For Digital Recording And Reproducing (AREA)

- Moving Of The Head To Find And Align With The Track (AREA)

- Dot-Matrix Printers And Others (AREA)

- Electronic Switches (AREA)

- Printers Or Recording Devices Using Electromagnetic And Radiation Means (AREA)

- Non-Adjustable Resistors (AREA)

- Error Detection And Correction (AREA)

Description

この出願は1995年10月23日提出の合衆国仮出願番号60/006013の恩恵を主張するものである。この出願は1994年10月12日提出の合衆国特許出願連続番号08/320,540号に関連するものである。

発明の分野

この発明はディスクドライブ媒体上に記憶されるサーボ情報を記憶し、検出し、評価するための装置および方法に関し、特に、部分応答・最大尤度検出チャネルおよび磁気ディスク媒体を伴う場合に有用な装置および方法に関する。

発明の背景

ディスク面上のデータトラック内に記録されるサーボ情報を読取ることによって、ディスクドライブヘッドポジショナサーボシステムはデータトランスデューサのヘッド位置を評価することができる。この記録されるサーボ情報は典型的にはトラック(つまりシリンダおよびヘッド)アドレスおよびサーボバーストをふくむ。ディスク面上の各周方向データトラックはトラックに埋込まれるサーボセクタに記録される独自のトラックアドレスを有し、サーボバーストパターンは2つ以上のトラックごとに頻繁に繰返す。ディスクドライブが径方向トラック位置を探索しているとき、トラックアドレスは粗い位置決め情報として用いられて読取ヘッドの位置をおおよそ評価し、サーボバーストは精密な位置決め情報として用いられて所望の径方向位置上にヘッドを精密に位置決めする。

探索時間でトラックアドレスを読取っている間、ヘッドは2つの隣接トラック間に位置決めされるかもしれない。この状態では、ヘッドは両方のトラックからの信号の重なったものを受取るかもしれない。この曖昧さに対する1つの解決方法として、トラックアドレスをグレイコード化されたアドレスにエンコードして、任意の2つの隣接トラックのエンコードされたアドレスが互いに対し一つのビット位置においてのみによって異なるようにする。この解決法を用いると、ヘッドが2つのトラックを読取っている場合、アドレスをデコードした後の曖昧さは1トラックであり、1トラックの誤差は探索時間において受入れ可能である。

1つの公知の技術に従うと、各データトラックは複数のセクタに分割される。各セクタはヘッダセクションを含み、これにデータセクションが続く。ヘッダセクションは典型的にはDC消去フィールドと、プリアンブルフィールドと、ヘッダ同期文字と、トラックアドレスフィールド(粗いサーボ情報)と、サーボバーストフィールド(精密なサーボ情報)とを含む。データセクションは典型的には別のプリアンブルフィールドと、データ同期文字と、ユーザデータのブロックと、誤り訂正バイトとを含む。この例では、ヘッダセクションはデータセクションと同じデータ速度で記録され、ディスクドライブにおける単一読取チャネル構造を通しての同期ピーク検出を用いてヘッダセクションとデータセクションとの両方における情報を読取る。この方策の一例は、共通の譲受人に譲渡された、「高能率ディスクフォーマットおよび同期システム(“High Efficiency Disk Format and Synchronization System”)」と題される、リース(Leis)らへの米国特許第5,036,408号に見られ、その開示をここに引用により援用するものとする。

別の公知の技術では同心データトラックの径方向ゾーンまたは帯を用い、各ゾーンはそのゾーンのディスク半径に関連付けられるデータ転送速度を有している。この例では、データ領域は、単一データ転送速度でサーボ情報とともに工場で記録される、一連の径方向に延びる埋込サーボセクタによって分離される。サーボデータ回復回路は、各セクタ上を通過する間にデータトランスデューサによって読取られる情報から、サーボアドレスマークと、トラック番号と、精密位置情報とを非同期に(つまり入来サーボデータへの位相ロックなしに)回復する。このサーボ回復回路はユーザデータ情報のピーク検出のために用いられる読取チャネルエレクトロニクス装置とは別個である。この例は、共通の譲受人に譲渡された、「デジタル埋込セクタサーボを有するディスクドライブのためのサーボデータ回復回路(“Servo Data Recovery Circuit for Disk Drive Having Digital Embedded Sector Servo”)」と題されるムーン(Moon)らへの米国特許第5,420,730号に記載されており、その開示をここにおいて引用により援用するものとする。

ピーク検出技術を用いる磁気記録におけるデータ記憶密度を制限してきた1つの要因は、磁束遷移が互いにますます近くなると生ずる記号間干渉であった。磁気記録において磁束密度を増加させながらも、記録されたデータを正確に読取るための1つの技術として、同期サンプリングデータ検出が用いられる。「部分応答・最大尤度」(PRML)信号送信としばしば呼ばれるこの技術は、信号ストリームのアナログ側もしくはデジタル側または両側において、高速アナログ−デジタル変換およびチャネル等化を含む、増大する回路の複雑さを犠牲にして、いくらかの改善されたデータ記憶密度を提供している。PRMLを用いるディスクドライブの一例は、共通の譲受人に譲渡される、「PRML同期サンプリングデータ検出およびセクタサーボの非同期検出を用いるディスクドライブ(Disk Drive Using PRML Synchronous Sampling Data Detection and Asynchronous Detection of Sector Servo”)」と題されるアボット(Abbott)らへの米国特許第5,345,342号に挙げられており、その開示をここに引用により援用するものとする。この特許に記載される方策は、同期サンプリングデータ検出チャネル内の特別な回路を可能化して、一定のサーボデータ速度で記録される埋込サーボセクタにあるトラック番号値を非同期に検出し、一方、ユーザデータ速度は記録用ディスクにわたる径方向データゾーンによって異なっていた。サーボバーストは、従来のピーク検出、サンプルおよびホールド技術を用いて読取られ処理された。

上記のアボットらの特許により教示される非同期サーボサンプリング技術に対する改良が、後の、共通の譲受人に譲渡される、「PRMLサンプリングされるデータチャネル同期サーボ検出器(“PRML Sampled Data Channel Synchronous Servo Detector”)」と題されるフィッシャー(Fisher)への米国特許第5,384,671号に見られ、その開示をここに引用により援用するものとする。この方策では、同期サンプリングデータ検出システムのタイミングループはサーボ情報に位相ロックされ、トラックアドレスと精密位置情報とを含むこのサーボ情報は同期してサンプリングされデコードされる。この方策では、サーボプリアンブルフィールドは従来の1/4T正弦波パターンとして記録され、これはピーク検出チャネルにおける2Tパターンに対応する(Tは単位サンプルセルまたは間隔を表わす)。

ビタビ検出器は、同期サンプリングされるデータ検出チャネル内で用いられることで知られている。ビタビ検出器の1つの例は、共通の譲受人に譲渡される、「PRMLクラスIVサンプリングデータ検出のための調整可能な検出しきい値を有するビタビ検出器(“Viterbi Detector Having Adjustable Detection Thrersholds for PRML Class IV Sampling Data Detection”)」と題されるアングイェン(Nguyen)への米国特許第5,341,387号に挙げられており、その開示をここに引用により援用するものとする。

これら先行技術の方策は、それらのそれぞれの時期において十分に働いてきた一方で、単位サイズディスクごとの増大するデータ記憶容量およびデータ転送速度は、これまでにまだ解決されていない、改良されたディスクドライブヘッドサーボフォーマット、アーキテクチャおよび方策に対する要求に直接到ってきている。

目的を伴う、この発明の概要

この発明の一般的な目的は、部分応答・最大尤度同期サンプリングされるデータ検出チャネルを有するディスクドライブにおいてデータトラックをアドレス指定するための、改良されかつ単純化された方法、装置およびデータフォーマットを提供することである。

この発明の別の目的は、別個のピーク検出ハードウェアを必要としないPRMLディスクドライブのためのサーボフォーマットおよび装置を提供することである。

この発明のさらなる目的は、PRMLディスクドライブ内における単純化されたアドレスデコード方法および装置を提供することである。

この発明のさらにもう1つの目的は、PRMLディスクドライブ内で同期してサンプリングされ検出される埋込サーボセクタ内でより高い符号レートと、より小さいセル時間と、より小さい冗長度とを用いることを可能にする高能率サーボアドレスフォーマットを提供することである。

この発明の1つの局面において、ディスクドライブは、狭いサーボスポークによってデータセクタに分割される記録用トラックを規定する主表面を有する少なくとも1つの回転するデータ記憶ディスクを含む。トラックの各データセクタは、所定の距離およびユーザデータ符号レートを有するコードに従ってエンコードされるユーザデータが記録される。各サーボスポークは、ユーザデータ符号レートの1/4であるサーボ符号レートでワイド・バイフェーズパターンにコード化される少なくとも1つのサーボ情報フィールドを有する。この発明のこの局面において、同期サンプリングデータ検出チャネルは、

記録用トラック上において、サーボ制御されるアクチュエータによって位置決めされるデータトランスデューサヘッドと、

少なくともサーボ情報フィールドに存在する磁束遷移からデータトランスデューサヘッドによって磁気的に誘導される電気的アナログ信号を受取る前置増幅器と、

電気的アナログ信号を同期してサンプリングしてデジタルサンプルを発生させるためのデジタルサンプラと、

同期サンプリングデータ検出チャネルからのデジタルサンプルを受取るように結合され、コード化されたワイド・バイフェーズパターンを最大尤度サーボデータシーケンスとしてデコードするためのビタビ検出器とを含む。

このビタビ検出器は差分距離検出器またはツリー検索検出器を含んでもよい。

同期サンプリングデータ検出チャネルは部分応答・クラスIV・ターゲットスペクトルに調整される有限インパルス応答フィルタを含んでもよく、この例においてはビタビ検出器は有限インパルス応答フィルタの出力からの等化されたデジタルサンプルを受けるよう接続される。

代替的には、同期サンプリングデータ検出チャネルは、Dを1ビットセル遅延として、1−D2パルス応答(部分応答、クラスIV)に従ってデジタルサンプルをフィルタ処理するための有限インパルス応答フィルタと、1+D−D2−D3パルス応答(EPR4)に従ってフィルタ処理されたデジタルサンプルを与えるために有限インパルス応答フィルタの下流に接続される1+Dフィルタとを含んでもよい。この例では、ビタビ検出器は、1+Dフィルタの出力からEPR4等化されたワイド・バイフェーズサンプルを受取るよう接続される。

複数のサーボ情報フィールドに記録されるワイド・バイフェーズマグネットパターンは、2進0情報値のための−−++マグネットパターンと、2進1情報値のための−−++マグネットパターンとして配されてもよい。

複数のサーボ情報フィールドは各サーボスポーク内に与えられてもよく、それらフィールドの1つは、サーボ情報ブロックの始まりをマーキングするための9記号ワード000100101(2進)のようなサーボアドレスマークパターンを含んでもよい。少なくとも1つのサーボ情報フィールドは、所定のビット長の、グレイコード化されたトラック番号2値パターンを含む。このパターンは、まずワイド・バイフェーズコードとしてデコードされ、次いでそれがグレイコードとしてデコードされる。トラック番号2値パターンはパリティ記号を含んでもよく、この例では、チャネルはトラック番号2値パターンを受取ってデコードし、パリティ記号をチェックするための回路構成を含んでもよい。

この発明の関連する局面において、サーボ情報フィールドは、トラックの第1のトラック番号アドレスと、そのトラックに隣接して位置するトラックの第2のトラック番号アドレスとがある、所定ビット長の2つのトラック番号2値パターンを含んでもよい。1つの好ましい形態では、第2のトラック番号は1/2トラックをオフセットして第2のトラック内へ延びる状態で記録される。この発明のさらなる関連する局面として、1つのサーボ情報フィールドは第1および第2のトラック番号に関して計算される誤り訂正値を保持するための誤り訂正コードフィールドをさらに含んでもよく、この構成においてはチャネルは第1および第2のトラック番号のデコードされた値をデコードしチェックし訂正するための誤り訂正コードデコードおよび訂正回路構成を含む。

この発明のこれらならびに他の目的、利点、局面および特徴は、添付の図面に関連させて与えられる好ましい実施例の以下の詳細な説明を考慮するとより十分に理解され評価される。

【図面の簡単な説明】

図面において、

図1は、PR4およびEPR4ターゲットを与えるディスクドライブ読取チャネルのブロック図である。

図2は、ディスクドライブにおけるディスクの記録面の概略図である。

図3は、ディスクのトラック上のサーボセクタ上に記録される信号を示す。

図4は、サーボセクタのフィールドのブロック図である。

図5Aは、チャネルがEPR4ターゲットスペクトルに等化されている、1つの書込電流パルスの磁気記録からのアナログ信号応答のグラフである。

図5Bは、2進1(“−−00”)ワイド・バイフェーズ書込電流シーケンス等へのアナログ信号応答のグラフである。

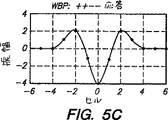

図5Cは、2進0(“++−−”)ワイド・バイフェーズ書込電流シーケンス等へのアナログ信号応答のグラフである。

図5Dは、ワイド・バイフェーズシーケンス、たとえば2進100シーケンス(“−−++++−−++−−”)へのアナログ信号応答のグラフである。

図6Aは、径方向干渉のないトラック番号のための第1のサーボセクタレイアウトを示す。

図6Bは、径方向干渉のないトラック番号のための第2のサーボセクタレイアウトを示す。

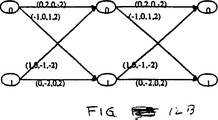

図7は、ワイド・バイフェーズ経路が強調されるPR4チャネルの格子図である。

図8Aは、4つのサンプルが一度に取られるワイド・バイフェーズPR4チャネルの格子図である。

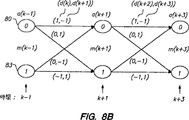

図8Bは、図8Aの図を単純化したものである。

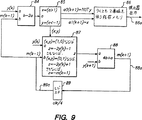

図9は、ワイド・バイフェーズコードのための差分距離ビタビ検出器のブロック図である。

図10は、ワイド・バイフェーズコードのためのツリー検索ビタビ検出器のブロック図である。

図11は、ワイド・バイフェーズ経路が強調されるEPR4チャネルの格子図である。

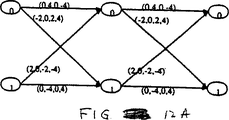

図12Aは、4つのサンプルが一度に取られるワイド・バイフェーズEPR4チャネルの格子図である。

図12Bは、図7Aのブロック図を単純化したものである。

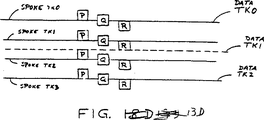

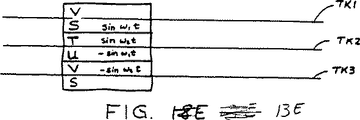

図13A−13Eは、サーボバーストフォーマットを示す図である。

図14A−14Bは、サーボバースト検出器のブロック図である。

好ましい実施例の詳細な説明

図1を参照して、ディスクドライブ10は、プログラマブルでありかつ適応型PR4のML読取チャネルを組込む。ディスクドライブ10は、共通の譲受人に譲渡され、その開示がここに引用により援用される「デジタル適応等化を伴うPRMLクラスIVサンプリングデータ検出を用いるディスクドライブ(Disk Drive Using PRML Class IV Sampling Data Detection with Digital Adaptive Equalization”)」と題される、アボットらへの米国特許第5,341,249号に記載されるようなさまざまな実施例の1つであってもよい。(この特許は、上に挙げられたアボットらの米国特許第5,345,342号の特許である。)

ドライブ10は少なくとも1つのデータ記憶ディスク16を含む。従来にあるように、たとえば磁気抵抗ヘッドであるデータトランスデューサヘッド26は各ディスク16のディスク面上において「浮動」関係において関連付けられる。ヘッド26は、回転するディスク16の各記憶面上に規定される複数の同心データ記憶トラック71のうち選択されたものに対し位置決めされ、図2を参照されたい。

埋込サーボパターンは、図2を参照して、ディスク16の選択されたデータ記憶面上に、たとえば、共通の譲受人に譲渡され、その開示がここに引用により援用される米国特許第5,170,299号に記載される方法に従って、サーボライタにより書込まれる。

読取中、選択されたデータトラック71上をヘッド26が接近して浮動する間にヘッド26によって感知される磁束遷移は読取前置増幅器回路28によって前置増幅される。前置増幅されたアナログ信号(または「読取信号」)は次いで、アナログ可変利得増幅器(VGA)38に送られる。制御される増幅の後、読取信号は次いでプログラマブルアナログフィルタ/等化器段40を通過する。

アナログフィルタ/等化器40は、トランスデューサヘッド26がデータを読取っている最中の選択されたデータゾーン70のデータ転送速度に対して最適化されるようプログラムされる。等化されたアナログ読取信号は、次いで、ユーザデータに同期されると少なくとも5ビット解像度の原始データサンプル{x(k)}を発生する高速アナログ−デジタル(A/D)変換器46内でサンプル処理および等化を受ける。

適応型デジタルFIRフィルタ48は、所望のPR4チャネル応答特性に従って原始データサンプル{x(k)}をフィルタ処理し条件付けするための適応フィルタ係数を用いて、フィルタ処理され条件付けされたサンプル{y(k)}を発生させる。FIRフィルタ48からのバンドパスフィルタ処理され条件付けされたデータサンプル{y(k)}は次いで、データパス経路49上をビタビ検出器(図示せず)に送られ、これによってPR4ターゲットを伴うユーザデータが検出される。PR4ターゲットおよびEPR4ターゲットの両方を用いる実施例では、FIRフィルタ48からのフィルタ処理され条件付けされたサンプル{y(k)}は1+Dフィルタ50を通してさらに送られ、その出力経路51はEPR4チャネル応答特性にフィルタ処理された信号を与える。(EPR4ターゲットのみが所望される場合には、FIRフィルタ48は適当な係数で直接プログラムされ、1+Dフィルタ50は必要とされない。)

ディスクドライブ10内にはサーボエンジン32がさらに設けられ、これは、デコードされたワイド・バイフェーズサーボ情報値に従ってたとえば回転音声コイルヘッドポジショナ構造30を制御するために適用されるヘッド位置制御および訂正値と、この発明の原理に従ってデコードされるバースト値とを展開する。

原始データサンプル{x(k)}およびフィルタ処理されたサンプル{y(k)}を含むサンプルは、クロックビット時間周期Tを有するデータサンプリング速度で取られる。この時間Tはそのサンプリング速度での「ビットセル」またはより単純には「セル」に対応する。タイミングループ44は、経路49上のPR4ターゲットサンプル等を受取り、所望されるサンプリング位置でサンプリングおよび量子化をA/D変換器46に同期させてもよい。同様に、利得ループ36はVGA38をたとえば経路49上のPR4ターゲットサンプルに基づいて制御してもよい。タイミングループおよび利得ループは参照したアボットらの米国特許第5,345,342号に記載されている。DCオフセット制御ループ37をさらに設けてDCオフセットのためのオフセット増幅器93をPR4ターゲットサンプルに基づいて調整してもよい。代表的なDCオフセットループは、共通の譲受人に譲渡され、その開示がここに引用により援用される「実時間DCオフセット制御および関連の方法(“Real-Time DC Offset Control and Associated Method”)」と題されるジペロビッチ(Ziperovich)への米国特許第5,459,679号に記載されている。

図2を参照して、記憶ディスク16の例示的なデータ記憶面は、内側の降着ゾーン領域LZと径方向において最も外側の周縁データトラックゾーン70−1との間にある複数のデータ記録ゾーン70に好ましくは配される複数の同心データトラック71を有する。この示される実施例では、データトラックは、たとえば、最も外側のゾーン70−1および径方向において内方に向かうゾーン70−2、70−3、70−4、70−5、70−6、70−7、70−8および70−9を含むたとえば9つのデータゾーンに配されるものとして示される。実際には、より多くのゾーンが現在は好ましい。各データゾーンは、そのゾーンの特定の半径に対し面積遷移ドメイン密度を最適化するよう選択されるビット転送速度を有する。

図2はさらに、たとえばディスク16の円周に沿って等間隔に置かれる、一連の径方向に延びる埋込サーボセクタまたは「スポーク」68を示している。図3の概観によると、各サーボセクタ68は、たとえば、サーボプリアンブルフィールド68Aと、サーボ識別フィールド68Bと、円周方向に千鳥状である、径方向にオフセットするサーボバーストのフィールド68Cとを本質的に含む。トラックごとのデータセクタ数はデータゾーンによって変動するが、トラックごとのたとえば68のような埋込サーボセクタの数はこの実施例においてはディスク16の表面領域にわたって一定のままである。

サーボセクタ68は、工場で従来のサーボ書込装置を用いて、1つのデータセル速度で、トラックからトラックへの位相コヒーレンスを伴って、好ましくは記録される。レーザサーボライタおよびそれとともに用いるのに好適なヘッドアーム取付具は、その開示をここに引用により援用する、共通の譲受人に譲渡された米国特許第4,920,442号に記載されている。代替的に、サーボセクタは、既に上で論じた、共通の譲受人に譲渡された米国特許第5,384,671号に記載されるように、ゾーン化されたデータセル速度で書込まれる。

図4を参照して、各サーボセクタ68または「スポーク」は、たとえば、示されるような埋込サーボ情報のサーボ識別フィールドを有する。遷移が実質的に全くないかまたはわずかしかないディスク上のクリーンな領域にあるサイズたとえば40セルの、オプションとしてのDC消去フィールド731(図4ではフィールドの下に時間「40T」を伴う)は、サーボセクタ68のオンセットにフラグを立てるのに用いられ得る。サイズたとえば160セルのプリアンブルフィールド732は、所望される長さの「−++−−++−−++」などの2T繰返しパターンで書込まれ得る。プリアンブル732は、入来アナログ信号に対して訂正利得および位相ロックを確立しそれによってアナログ−デジタル変換器46によるサンプリング等化を制御するために、タイミングループおよび利得ループによって用いられる。全体として、オプションのDC消去フィールド731およびプリアンブルフィールド732は図3のプリアンブルフィールド68Aを含む。

サーボアドレスマーク733はフレーミングクロックをリセットするために用いられる。これに、トラック番号のたとえば3つの最下位ビット(LSBs)734が続く。完全なスポーク番号735はオプションではあるが、少なくとも1ビットの情報を与えて回転位置が決定できるようにすべきである。全体のトラック番号736は少なくとも1回記録される。ヘッド番号(図示せず)をサーボアドレス指定情報の部としてさらに記録してもよい。全体として、サーボアドレスマーク733、LSBフィールド734、および完全なスポーク番号フィールド735は、図3のサーボ識別フィールド68Bを含む。

アドレス指定情報に続いてサーボバースト737が記録され、これらは、後に記載するように、トラック中央に対してヘッド位置を決定するのに用いられる。さまざまなサーボパターンの例をこの後に示す。フィールド737におけるこれらのパターンは図3のフィールド68Cに関連付けられる。サーボセクタ68のいくつかまたはすべてのフィールドの長さはプログラマブルなサイズであってもよい。他の情報フィールドは、これまでに記載したフィールド間またはそれらの後に記憶されてもよい。

ここで、たとえばサーボアドレスマーク733、LSBフィールド734、スポーク番号フィールド735およびトラック番号フィールド736等である、サーボセクタ68のデジタルデータ記憶フィールドのいくつかまたはすべてに対して用いられてもよい、ワイド・バイフェーズエンコードについて説明する。デジタルデータを書込む際、記号と呼ばれる未コード化ビット(つまり0または1)で始める。記号は、1つ以上の符号またはマグネット(+または−)をセルに割当てるコード化によってディスク上に記録される。(いくらか曖昧ではあるが、符号は0または1であるものとして示されてもよい。)バイフェーズコードにおいて、2つの符号が用いられ、記号は次のようにエンコードされてもよい:

1−>+−

0−>−+

我々は、ワイド・バイフェーズ(WBP)コードを、コード速度1/4で次のように規定する:

0−>++−−

1−>−−++

磁束遷移を全く有してはならないDC消去フィールド731はWBPエンコードされ得ない。

プリアンブルフィールド732は、PLLおよびAGCロックに対し、たとえば40またはプログラマブルな数のWBP記号「1」(またはセル「−−++」)でWBPエンコードされてもよい。

サーボアドレスマーク(「SAM」)733は、サーボブロックの始まりをマーキングする、WBPでエンコードされる9記号ワード「000100101」であってもよい。このSAMは、すべてのシフト(自動訂正)は、少なくとも5つの位置において同意せず、したがって、同期を失うことなしに2つの独立した誤りを斟酌する。今説明したプリアンブル732に付加されると、このシーケンスは「…1111111000100101」のように見える。これは、修正されたバーカー(Barker)シーケンスである。

トラック番号736は通常のグレイコード(符号レート=1)でまずエンコードされる14以上の記号のアドレスであってもよく、次いでパリティ記号が加えられてもよい。その結果はWBPエンコードされる。パリティ記号がある場合、それは探索時間には用いられ得ないが、読取時間に用いて信号誤りを検出することができる。グレイコード化は、読取ヘッド26が探索時間においてトラック間にあるときに2つの隣接トラックアドレスを同時に読取る場合の大きな誤りを回避するために用いられる。

代替的サーボセクタレイアウトにおいて、トラックアドレス(トラック番号)は各サーボセクタ68において2回書込まれ、その対にされたトラックアドレスは互いとは異なる。図6Aを参照して、図中において径方向のコラムとして見えるように、奇数トラックアドレス(A1、A3、A5、A7)が第1に書込まれ、偶数トラックアドレス(A2、A4、A6、A8)が第2に書込まれる。図6Bにおいて、第2のコラムは第1のコラムが記録するのと同じトラック番号を記録するが、第2のコラムは半トラックオフセットして記録される。両方のフォーマットにおいて、読取ヘッド26のすべての位置は、この2つのコラムのうちの少なくとも1つにある隣接トラックからの干渉なしにアドレスを読取り得る。この理由のため、グレイコード化は必要とされず、図示されるように、ECCフィールドを各アドレスに付加し得る。第1のフォーマット(図6A)において、不確定度は1トラックであり、第2のフォーマット(図6B)においては不確定度は半トラックである。探索の際、2トラックの周期を有するサーボバーストからの位置誤り信号を用いることによってコラムが読取られるのが認識されるかもしれない。このような使用では、サーボバーストをトラックアドレスに近く位置決めして、読取ヘッド26の径方向位置が、読取ヘッド26がサーボバーストを読取っているときおよびそれがトラックアドレスを読取っているときから大きく変わらないようにすべきである。

PR4ターゲットを伴うWBPコードのためのビタビ検出器

適応型FIRフィルタ48の経路49での出力はPR4(クラスIV部分応答)ターゲットであり、これは、Dを1ビットセル遅延として1−D2のパルス応答を有する。図7に示されるように、PR4ターゲットを表わすのに必要な状態の数は4である。図7はPR4ターゲットのビタビ検出器格子図を示し、実線はWBP経路を表わし、点線は非WBP経路を示す。すべての経路は有効PR4経路である。格子上において、WBP経路は形式「±/w」の表記でマーキングされ、「+」または「−」はディスク上の磁化(セルに何が書込まれるか)を示し、「w」はビタビ検出器入力での波形サンプルを表わす。図7は、検出器の、時間k−1での初期状態からの4つの時間ステップを示し、ここでは、WBPエンコードされた記号の検出が開始されて時間k+3に至り、そこでそれは終了する。マグネット「−」は「0」としても示され、マグネット「+」は「1」としても示される。したがって、たとえば、状態00(参照番号80)は、前の2つのセルが「−−」として読取られたことを示す。

この格子を参照して、検出器が時間k−1において参照番号80の状態00にあり、かつ次のサンプル値が1である場合、検出器は時間kで参照番号81の状態01に進む。時間k−1でのこの分岐に対するマグネット(または等価的には書込電流)は「+」であり、状態00からの「−」からの遷移であり、これが理想的には1のサンプル値をもたらす。同様に、検出器が時間k−1で参照番号83の状態11にあり、かつ時間kでのサンプル値が−1である場合、検出器は時間kで参照番号82の状態10に進む。時間k−1でのこの分岐に対するマグネットは「−」であり、状態11の「+」からの負の遷移であり、これが理想的には−1のサンプル値をもたらす。

各WBP記号は4つのセルを占めるため、検出器は各WBP記号がどこで始まってどこで終わるかを知りながら動作されなければならないことに注意されたい。この4セル同期をチャンク同期と呼ぶことにする。

チャンク同期が達成されると、格子は、元の格子の2つの状態00および11のみを伴って一度に4サンプル更新され得る。したがって、4状態ビタビ検出器は、図8Aに示されるように、参照番号80および83をそれぞれ伴う2つの状態に凝縮され得る。図8Aにおいて、検出器入力にあるサンプル値のみが各分岐を伴って与えられる。図示される各サンプルは2回繰返されることに注目されたい。このようにして、格子は、すべての2つの入来サンプルの平均を取り、次いで結果として生ずるストリームをクロック速度の半分で処理することによって、単純化されてもよい。図8Bに示されるこの単純化された格子では、チャンクは時間k−1、k+1およびk+3で始まる(状態の凝縮のため、時間軸kは2の因数でスケーリングされている)。

PR4ターゲットを伴うWBPコードのための、差分距離検出器と呼ぶことにする第1のビタビ検出器を、図8Bに示される状態および遷移に関してここで説明する。

a0(k−1)は、時間k+1において状態0で終わる、残存経路の時間k−1での状態を表すものとする。

a1(k−1)は、時間k+1において状態1で終わる、残存経路の時間k−1での状態を表すものとする。

y(k)は、時間kでの、たとえばFIRフィルタ48から出力経路49で受取られる2つのサンプルの平均のような、平均化後の受取られた有雑音サンプルを示す。

m0(k)は、時間kでの状態0の経路距離を表わす。

m1(k)は、時間kでの状態1の経路距離を表わす。

m(k)=m0(k)−m1(k)。これが差分距離である。

差分距離検出器のためのデコードアルゴリズムは擬似コードで次のように表されてもよい:

(m(k−1)−2y(k)>1)ならば、

{m(k+1)=4y(k+1)−2y(k)−1;

a0(k−1)=a1(k−1)=1;

/*両方の経路は状態1にマージする*/

}

さもなくば、(m(k−1)−2y(k)<−1ならば、

{m(k+1)=4y(k+1)−2y(k)+1;

a0(k−1)=a1(k−1)=0;

/*両方の経路は状態0にマージされる*/

}

さもなくば、

{m(k+1)=−m(k−1)+4y(k+1);

a0(k−1)=1;

a1(lk−1)=0

/*経路はマージされない*/

}

図9は、WBPコードのための差分距離ビタビ検出器の実現例を示すブロック図である。ブロック84はa=m(k−1)−2y(k)を計算する。ブロック85で、2つの論理値0および1(それぞれ偽および真)がxおよびyに対しx=a>1およびy=a<−1のように計算される。ブロック85はさらに、時間k+3において状態0および状態1でそれぞれ終わる、残存経路の時間k+1での状態である値a0(k+1)およびa1(k+1)を計算する。これらは残存メモリ86に与えられ、図8に示されるように計算される。つまり:

a0(k+1)=NOTy、および

a1(k+1)=x

ブロック86は、その出力86aが検出器の出力である標準ビタビ検出器残存メモリを実現する。この残存メモリの深さは検出器の性能要件を満たすよう選択され、ここに記載されるように使用される場合は、少なくとも1の深さで一般には十分であろう。

差分距離計算において用いるための値zはブロック87において次のように計算される:

(x,y)==(1,0)ならば、z=−2y(k)−1;

(x,y)==(0,1)ならば、z=−2y(k)+1;

さもなくば、z=−m(k−1)

ブロック88はこの計算された値zを用いて、次のように計算される出力m(k+1)を出力する:

m(k+1)=4y(k+1)+z

この出力88aはレジスタ89において4T(WBP記号時間)遅延され、このレジスタの出力89aがブロック87への入力値m(k−1)となる。(k=0でのm(k−1)の初期値は0である。)

WBPコードのための、ツリー検索検出器と呼ぶことにする第2のビタビ検出器を、図8Bに示される状態および遷移に関連してここで説明する。このツリー検索検出器は初期状態で開始するよう強制されなければならず、なぜなら、2つの残存経路は時間k−1でマージすると仮定されるからである。時間k+1での残存経路は次いで、時間k−1でのマージされた残存経路を表わすa(k−1)と、たとえばFIRフィルタ48の出力49で発生される等化され平均化されたサンプルy(k)、y(k+1)、y(k+2)、およびy(k+3)とから検出される。

サーボセクタフィールドに関しては、ツリー検索検出器は既知の状態でスタートするという要件は合理的であり、なぜなら、その状態はたとえばプリアンブルフィールド732のような既知のフィールドによって強制され得るからである。

ツリー検索検出器のためのデコードアルゴリズムは、擬似コードで次のように表現されてもよい:

距離1=y(k)−2y(k+1)+y(k+2)

距離2=y(k)−2y(k+1)+2y(k+3)

(a(k−1)==0)ならば、

a(k+1)=(距離1<0)OR

((距離1<1)AND(距離2<0.5))

さもなくば、

a(k+1)=(距離1<−1)OR

((距離1<0)AND(距離2<−0.5));

上のように、これらの計算において、論理上の偽は算術的0であり、論理上の真は算術的1である。

図10は、WBPコードのためのツリー検索ビタビ検出器の実現例を示すブロック図である。ブロック91および92は、上に規定したように、距離1および距離2をそれぞれ計算する。入力90aおよび90bで、ブロック90はサンプルy(k+1)およびy(k)をそれぞれ受取り、それらからy(k)−2y(k+1)を計算する。これは、ブロック91の入力91bと、ブロック92の入力92aとで与えられる。入力91aでブロック91はさらにサンプルy(k+1)を受取り、入力92bでブロック92はサンプルy(K+3)を受取る。距離1は経路91cでブロック93に出力される。距離2は経路92cでブロック93に出力される。ブロック93は、距離1、距離2、およびa(k−l)から、上記の擬似コードにおいて述べたようにa(k+1)を計算し、それは経路93aにおいて出力される。ブロック93の出力93aは4T遅延レジスタ94の入力となり、これがa(k−1)を経路94a上でブロック93に与える。

EPR4ターゲットを伴うWBPのためのビタビ検出器

図11を参照して、WBPエンコードされたEPR4ターゲットを検出するビタビ検出器の実現例を考える。このEPR4ターゲットは1+D−D2−D3のパルス応答を有する。EPR4ターゲットを表現するのに必要な状態数は8である。図11は、ワイド・バイフェーズ経路が強調されるEPR4チャネルの格子図である。この図は図6に見られるPR4チャネルに対する図と同様であるが、8つの状態および5つの考えられ得るサンプル入力−4、−2、0、2および4があるという違いがある。

図12Aを参照して、チャンク同期が達成されると、EPR4格子は、元の格子の状態のうちの2つだけを伴って、一度に4サンプル更新され得る。図12Aにおいて元の状態100および011は0および1とそれぞれ再度名付けられ、ビタビ検出器入力にあるサンプル値のみが分岐上に示される。この格子図は、入来サンプル値を2で除算することによって、図12Bに示されるようにさらに簡略化されてもよい。

図8Bの簡略化された格子の場合と同じように、図12Bに基づいて、EPR4ターゲットを伴うWBPコードのための2つのビタビ検出器についてここで説明する。

第1の検出器である差分距離検出器は、図9に関連して記載された差分距離検出器と実質的に同様である。

a0(k−1)は、時間k+3において状態0で終わる、残存経路の時間k−1での状態を表わす。

a1(k−1)は、時間k+3において状態1で終わる、残存経路の時間k−1での状態を表わす。

y(k)は、理想値−2、−1、0、1および2へのスケーリング後の、時間kでの、たとえばFIRフィルタ48から出力経路49で受取られる2つのサンプルの平均のような、受取られる有雑音サンプルを示す。

m0(k)は、時間kでの状態0の経路距離を表わす。

m1(k)は、時間kでの状態1の経路距離を表わす。

m(k)=m0(k)−m1(k)。これが差分距離である。

差分距離検出器のためのデコードアルゴリズムは擬似コードにおいて以下のように表現されてもよい:

thr(k−1)=m(k−1)−2y(k−1)−4y(k−2)+2y(k−3);

(thr(k−1)>2)ならば、

{m(k+3)=8y(k)+2y(k−1)−4y(k−2)−2y(k−3)−2;

a0(k−1)=a1(k−1)=1;

/*両方の経路は状態1にマージする*/

}

さもなくば、(thr(k−1)<−2)ならば、

{m(k+3)=8y(k)+2y(k−1)−4y(k−2)−2y(k−3)+2;

a0(k−1)=al(k−1)=0;

/*両方の経路は状態0にマージする*/

}

さもなければ、

{m(k+3)=−m(k−1)+8y(k)+4y(k−1)−4y(k−3);

a0(k−1)=1;

a1(k−1)=0

/*経路はマージしない*/

}

PR4ターゲットを伴うWBPのための差分距離ビタビ検出器と同様に、ここに記載されるように使用する場合には3の残存メモリ深さで一般には十分であろう。

第2の、EPR4ターゲットを伴うWBPコードのためのツリー検索ビタビ検出器をここで説明する。このツリー検索検出器を説明するに当り、2つの残存経路は時間k−1でマージすると仮定される。時間k+3での残存経路は次いで、

時間k−1におけるマージした残存経路を表わすa(k−1)と、

たとえば1+Dフィルタ50の出力として発生される、等化され平均化されたサンプルy(k)、y(k−1)…y(k−7)とから検出される。

ツリー検索検出器のためのデコードアルゴリズムは擬似コードにおいて次のように表現されてもよい:

距離1=2y(k−1)+4y(k−2)−2y(k−3)−8y(k−4)−2y(k−5)+4y(k−6)+2y(k−7);

距離2=8y(k)−4y(k−1)+4y(k−3)−8y(k−4)−2y(k−5)+4y(k−6)+2y(k−7);

(a(k−1)==0)ならば、

a(k+3)=(距離1<0)OR

((距離1<4)AND(距離2<2))

さもなければ、

a(k−3)=(距離1<−4)OR

((距離1<0)AND(距離2<−2))

PR4ターゲットを伴うWBPのためのツリー検索検出器の場合と同様に、EPR4ターゲットのためのこの検出器は残存メモリを全く有さない。

図1に戻って、EPR4ターゲットを伴うWBPコードのPRML検出のためのビタビ検出器60は、トラック番号、ヘッド番号、およびセクタ番号等の、サーボセクタにあるすべてのWBPエンコードされたデジタル情報を検出するのに用いられ得る。ビタビ検出器60は、図11、図12Aおよび図12Bに関連して上に記載されるように、差分距離検出器もしくはツリー検索検出器であってもよく、または従来のビタビ検出器であってもよい。代替的に、EPR4検出器に代えて、サーボセクタにあるWBPエンコードされたデータは、図7、図8A、図8B、図9および図10に関連して上に記載された差分距離検出器またはツリー検索検出器のような、PR4ターゲットを伴うWBPコードのためのビタビ検出器によってデコードされてもよく、または従来のビタビ検出器によってデコードされてもよい。

図1において、デジタルサーボバースト検出器54も1+Dフィルタ50からのEPR4ターゲット出力信号を受ける。代替的に、バースト検出器54はFIRフィルタ48からのPR4ターゲットを受取ってもよく、この場合は、PR4ターゲットで検出され得るバーストフォーマットが用いられる。

図13A〜13Eを参照して、5つのサーボバーストフォーマットについて記載する。データトラックの中央はTK0、TK1、TK2およびTK3によって示される。各フォーマットにおけるバーストは2トラックの周期で繰返す。I型フォーマットと呼ぶことにする第1のフォーマット、つまりフルトラックバーストを図13Aに概略的に示す。I型バーストA、B、およびC(およびオプションとしてD)はデータトラックの幅になるよう書込まれる。書込ヘッドはこの幅よりも小さいため、バーストは少なくとも2つのパスにおいて書込まれ、少なくとも1つの消去帯(図示せず)が各バースト内に見出される。さらに、たとえば、バーストAとバーストCとの間にTK1に沿って走る消去帯(図示せず)がある。

II型フォーマットと呼ぶことにする第2のフォーマット、つまり狭いバーストを図13Bに概略的に示す。このフォーマットでは、各バーストE、F、GおよびHは一度だけ書込まれ、したがってバースト内に消去帯はない。径方向に隣接するバースト(たとえばEおよびF)間の距離はトラック幅の半分である。書込ヘッドは一般にはこの幅を超え、したがって各バーストは1つのトラックの中央上を越えて通常は延びる。

I型およびII型フォーマットの両方では、バースト自体は通常は定周波数および振幅の正弦波である。

正反対フォーマットと呼ぶことにする第3のフォーマットを図13Cに概略的に示す。このフォーマットでは、バースト−−J、K、LおよびMはたとえばI型フォーマット(図13A)のAバーストとBバーストとの間の空間左側ブランクを埋めるように書込まれる。記録されない領域は反対の(または正反対の)極性の正弦波で埋められる。したがって、バーストJの信号がsin(x)であるならば、バーストKの信号は−sin(x)である。バーストLおよびMの波形はバーストJおよびKの波形に対応する。

I型およびII型での状況とは違い、正反対フォーマットでは位相情報が重要である。したがって、位相情報を「修正し」ないよう、このバーストフォーマットを読取っている間はPLLはロックされる。この同じ理由で、このフォーマットは、バースト内の消去帯、径方向位相非コヒーレンスおよび累積された位相誤りから生ずる誤りを被る。このような誤りの影響をディスクドライブに制限させるために、オプションの再同期パターン(図示せず)がバースト自体の前に記録されてもよい。

圧縮されたフォーマットと呼ぶことにする第4のフォーマットを図13Dに概略的に示す。このフォーマットは形式においてはI型と同様であるが、他のフォーマットでの状況とは違い、圧縮されたフォーマットではサーボ情報は、ここではDATA TK0、DATA TK1およびDATA TK2と示されるデータトラックには対応しないスポークトラックSPOKE TK0、SPOKE TK1、SPOKE TK2、およびSPOKE TK3上に書込まれる。各バースドP、QおよびRは一度だけ書込まれ、したがってバースト内に消去帯は全くなく、バーストはそれにもかかわらずサーボトラックの完全な幅である。このフォーマットでは、たとえばトラックDATA TKlのような奇数番号付けされたデータトラックを追尾する際、ディスクドライブはサーボトラック中央を辿らないことに注目されたい。実際に、ヘッドは理想的にはちょうど2つのトラック間に置かれ、バーストフォーマットの2トラック周期を用いて、たとえばデータトラックDATA TKlを追尾しながらスポークトラックSPOKE TK1およびSPOKE TK2から受取られるグレイコード化された番号間におけるトラック番号の曖昧さを解消しなければならない。

周波数フォーマットと呼ぶことにする第5のフォーマットを図13Eに概略的に示す。このフォーマットでは、先に記載したものとは違い、バースト波形は1つの周波数ですべて記録されるのではない。正反対フォーマットの場合のように、周波数フォーマットバーストは半トラックの径方向の全幅にわたって記録される。図14Eに示されるように、バーストS、T、UおよびVの径方向シーケンスは角周波数w1およびw2を伴う正弦波として記録され、したがってバーストのシーケンスの形式は、Sはsinw1tであり、Tはsintw2であり、Uは−sinw1tであり、Vは−sinw2tである。2つの周波数は異なっていなければならず、交差する高調波を有さないよう選択されるべきである。

図14A〜14Bを参照して、バースト検出器54はサーボバーストが記録されるフォーマットに依って異なる形式を取る。図14Aを参照して、バースト検出器541は正反対フォーマットおよび周波数フォーマットのような同期フォーマットに対し、有用である。乗算器542はEPR4サンプル波形を正弦波1 0 −1 0で乗算する。この結果は加算器543によりレジスタ544において累算される。レジスタ544からのこの検出器の出力は、図13CのバーストKおよびJのような2つの径方向に隣接するバーストによって発生される(一般には)複合信号の符号付振幅を表わす。読取ヘッドがちょうど2つのバースト間にありかつたとえばトラックTK1上にあるとき、この出力は理想的には0となる。

図14Bを参照して、バースト検出器55は、I型、II型のような非同期バーストフォーマット、および圧縮されたフォーマットに対し有用である。バースト検出器55は、90°の位相オフセットを有する2つの直交正弦波でEPR4サンプル波形を乗算することによってバースト信号の位相−振幅ベクトルを計算し、第1の正弦波1 0 −1 0は乗算器551と加算器552と累算レジスタ553とにおいて用いられ、第2の直交する正弦波0 −1 0 1は乗算器554と加算器555と累算レジスタ556とにおいて用いられる。この処理の結果は、実数部がレジスタ553にありかつ虚数部がレジスタ556にある位相−振幅ベクトルである。バーストが読取られると、そのバーストのエネルギは、位相−振幅ベクトルの実数部の二乗回路557と虚数部の二乗回路558との総和加算器559の二乗根回路550として計算される。この計算されたエネルギはバーストと読取ヘッドとの間のオーバラップ度を評価し、繰返す2トラックバーストパターンに対するヘッド位置を評価するのに後で用いられる。(今問題にしている非同期I型、II型および圧縮されたバーストフォーマットでは、2つのバーストは径方向に隣接せず、したがってバースト検出器は一度に処理を行なうのに1つのバーストしか有さないことに注目されたい。)

周波数フォーマットに対する2つの代替的バースト検出器をここで説明する。第1の代替例は、図14Aに示されるバースト検出器541の対として動作する。この対のうちの第1の検出器に入力される正弦波はw1の角周波数を伴う正弦波を乗算器542への入力として有し、第2の検出器の乗算器542への正弦波入力はw2の各周波数を有する。各検出器の出力は対応する角周波数でのバースト信号の符号付振幅であり、これら符号付振幅は読取ヘッドの位置を評価するために比較される。

周波数フォーマットの第2の代替的バースト検出器は、今説明した第1の代替例とは違い、径方向位相非コヒーレンスまたは位相誤りに対し感度を有しない。この第2の代替例は、図14Bに示されるバースト検出器55の対の動作を二重にする。検出器の対のうちの第1のものにある乗算器551および554への正弦波入力はw1の角周波数を有し、第2の検出器の乗算器551および554に対する正弦波入力はw2の角周波数を有する。それぞれの周波数でのバースト信号の符号付振幅を各々が評価する、2つの検出器の出力は、読取ヘッドの位置を評価するために比較される。

さらなる代替的バースト検出器および関連の同期サーボバーストパターンが、1994年10月12日提出のフィッシャーらによる「ディスクドライブにおける精密ヘッド位置のためのコンカレントサーボバーストの同期検出(“Synchronous Detection of Concurrent Servo Bursts for Fine Head Position in Disk Drive”)」と題される、引用される米国特許出願連続番号第08/320,540号に記載されており、その開示をここに引用により援用するものとする。

このようにこの発明の現在好ましい実施例を説明してきたが、この発明の目的が十分に達成されたことがここで理解され、当業者ならば、この発明の構成上の変形ならびに幅広く異なる実施例および適用例はそれら自体をこの発明の精神および範囲から逸脱することなく示唆することが理解するであろう。ここにおける開示および記載は純粋に例示的なものであり、いかなる意味においても限定的であるようには意図されない。

Claims (28)

- 少なくとも1つの回転するデータ記憶ディスクを含むディスクドライブであって、前記ディスクは、狭いサーボスポークによってデータセクタに分割される記録トラックを規定する主表面を有し、前記ディスクドライブはさらに、

所定の距離とユーザデータ符号レートとを有するコードに従ってエンコードされるユーザデータで記録を行なうための、記録トラックのデータセクタと、

ユーザデータ符号レートの1/4であるサーボ符号レートでワイド・バイフェズパターンにコード化される少なくとも1つのサーボ情報フィールドを有する、記録領域のサーボスポークと、

同期サンプリングデータ検出チャネルとを含み、前記チャネルは、

サーボ制御されるアクチュエータによって記録トラック上で位置決めされるデータトランスデューサヘッドと、

少なくとも前記サーボ情報フィールドにある磁束遷移から前記データトランスデューサヘッドによって磁気的に誘導される電気的アナログ信号を受取るための前置増幅器と、

前記電気的アナログ信号を同期的にサンプリングしてデジタルサンプルを発生させるためのデジタルサンプラとを含み、前記ディスクドライブはさらに、

前記同期サンプリングデータ検出チャネルからのデジタルサンプルを受取るよう結合され、前記コード化されたワイド・バイフェーズパターンを最大尤度サーボデータシーケンスとしてデコードするためのビタビ検出器を含む、ディスクドライブ。 - 前記ビタビ検出器は差分距離検出器を含む、請求項1に記載のディスクドライブ。

- 前記差分距離ビタビ検出器は、

前記チャネルから受取られる現在のワイド・バイフェーズエンコードされたサーボ情報サンプルの2倍を差分距離から減算して差分値を発生させるよう接続される差分回路と、

前記差分値を受取るよう接続され、複数の論理値を計算し、第1の残存経路の状態を計算し、第2の残存経路の状態を計算するための第1の計算機と、

前記第1の残存経路の状態および前記第2の残存経路の状態を受けるよう前記第1の計算機に接続されかつ所定の経路長を有し、検出されるサーボ情報を出すための残存メモリユニットと、

複数の論理値と、差分距離と、現在のサンプルとを受けるよう前記第1の計算機に接続され、現在の差分距離値を計算するための差分距離計算機と、

現在の差分距離値を受取りワイド・バイフェーズクロック間隔で遅延させて差分距離を発生させるための遅延レジスタとを含む、請求項2に記載のディスクドライブ。 - 前記差分距離ビタビ検出器は、

前記チャネルから受取られるワイド・バイフェーズエンコードされたサーボ情報サンプルy(k)の2倍を差分距離m(k−1)から減算して差分値aを発生させるよう接続される差分回路と、

前記差分値aを受けるように接続され、x=a>1およびy=a<−1に従ってxおよびyに対し論理値0および1を計算し、時間k+3において状態0で終わる残存経路の時間k+1の状態をa0(k+1)=NOTyとして計算し、時間k+3において状態1で終わる残存経路の時間k+1での状態をa1(k+1)=xとして計算するための第1の計算機と、

状態a0(k+1)およびa1(k+1)を受けるよう前記第1の計算機に接続されかつ所定の経路長を有し、検出されるサーボ情報を出すための残存メモリユニットと、

xおよびyを受けるよう前記第1の計算機に接続されかつ差分距離m(k−1)および現在のサンプルy(k)を受けるよう接続され、

(x,y)==(1,0)ならば、 z=−2y(k)−1,

(x,y)==(0,1)ならば、 z=−2y(k)+1,

さもなければ、 z=−m(k−1)

に従って原始差分距離を計算するための原始差分距離計算機と、

原始差分距離zを受取りかつ時間調整されたサンプルy(k+1)を受けるよう接続され、現在の差分距離m(k+1)=4y(k+1)+zを計算するための中間差分距離計算機と、

現在の差分距離m(k+1)を受取りそれをワイド・バイフェーズクロック間隔によって遅延させて差分距離m(k−1)を発生させるための遅延レジスタとを含む、請求項2に記載のディスクドライブ。 - 前記同期サンプリングデータ検出チャネルは部分応答・クラスIVターゲットスペクトルに調整される有限インパルス応答フィルタを含み、前記差分回路は前記有限インパルス応答フィルタの出力から等化されたデジタルサンプルを受けるよう接続される、請求項4に記載のディスクドライブ。

- 前記チャネルはEPR4ターゲットスペクトルに等化され、前記ビタビ検出器は、時間k+3において状態0で終わる残存経路の時間k−1での状態をa0(k−1)とし、時間k+3において状態1で終わる残存経路の時間k−1での状態をa1(k−1)とし、理想値−2、−1、0、1、および2にスケーリングされた後、時間kでの2つのサンプルの平均のような、受取られる有雑音サンプルをy(k)で示し、時間kでの状態0の経路距離をm0(k)とし、時間kでの状態1の経路距離をm1(k)とし、m(k)=m0(k)−m1(k)つまり差分距離として、

thr(k−1)=m(k−1)−2y(k−1)−4y(k−2)+2y(k−3);

(thr(k−1)>2)ならば、

{m(k+3)=8y(k)+2y(k−1)−4y(k−2)−2y(k−3)−2;

a0(k−1)=a1(k−1)=1;

/*両方の経路は状態1にマージする*/

}

さもなくば、(thr(k−1)<−2)ならば、

{m(k+3)=8y(k)+2y(k−1)−4y(k−2)−2y(k−3)+2;

a0(k−1)=a1(k−1)=0;

/*両方の経路は状態0にマージする*/

}

さもなければ、

{m(k+3)=−m(k−1)+8y(k)+4y(k−1)−4y(k−3);

a0(k−1)=1;

a1(k−1)=0

/*経路はマージしない*/

}

に従って、ワイド・バイフェーズエンコードされたサーボ情報を検出する、請求項2に記載のディスクドライブ。 - 前記ビタビ検出器はツリー検索検出器である、請求項1に記載のディスクドライブ。

- 前記ツリー検索ビタビ検出器は、

時間k+1でのワイド・バイフェーズエンコードされたサーボ情報サンプルy(k+1)の2倍を受取りそれを現在のサンプルy(k)から減算して差分値aを発生させるよう前記チャネルに接続される差分回路と、

前記差分値aと時間k+2でのサンプルy(k+2)とを受取るよう接続され、第1の距離1=y(k)−2y(k+1)+y(k+2)を計算して出す第1の距離計算機と、

前記差分値aと時間k+3でのサンプルy(k+3)とを受取るよう接続され、第2の距離2=y(k)−2y(k+1)+2y(k+3)を計算して出すための第2の距離計算機と、

前記距離1、距離2および検出器出力値a(k−1)を受取り、

(a(k−1)=0)ならば、

a(k+1)=(距離1<0)OR

((距離1<1)AND(距離2<0.5))

さもなくば、

a(k+1)=(距離1<1)OR

((距離1<0)AND(距離2<−0.5))

に従って中間値a(k+1)を計算するためのツリー検索計算機と、

前記中間値a(k+1)を受取りそれをワイド・バイフェーズクロック間隔によって遅延させて検出器出力値a(k−1)を発生させるための遅延レジスタとを含む、請求項7に記載のディスクドライブ。 - 前記同期サンプリングデータ検出チャネルは部分応答・クラスIVターゲットスペクトルに調整される有限インパルス応答フィルタを含み、前記差分回路は前記有限インパルス応答フィルタの出力から等化されたデジタルサンプルを受けよう接続される、請求項7に記載のディスクドライブ。

- 前記同期サンプリングデータ検出チャネルは、1ビットセル遅延をDとして1−D2パルス応答(部分応答・クラスIV)に従ってデジタルサンプルをフィルタ処理するための有限インパルス応答フィルタと、1+D−D2−D3

パルス応答(EPR4)に従ってフィルタ処理されるデジタルサンプルを与えるよう前記有限インパルス応答フィルタの下流に接続される1+Dフィルタとを含み、前記ビタビ検出器は、前記1+Dフィルタの出力からEPR4等化されたワイド・バイフェーズサンプルを受けるよう接続される、請求項1に記載のディスクドライブ。 - 前記ビタビ検出器は、時間k−1でのマージされた残存経路をa(k−1)とし、等化され平均化されるワイド・バイフェーズエンコードされたサーボ情報サンプルをy(k)、y(k−1)…y(k−7)として、

距離1=2y(k−1)+4y(k−2)−2y(k−3)−8y(k−4)−2y(k−5)+4y(k−6)+2y(k−7);

距離2=8y(k)−4y(k−1)+4y(k−3)−8y(k−4)−2y(k−5)+4y(k−6)+2y(k−7);

(a(k−1)==0)ならば、

a(k+3)=(距離1<0)OR

((距離1<4)AND(距離2<2))

さもなければ、

a(k−3)=(距離1<−4)OR

((距離1<0)AND(距離2<−2))

に従って時間k+3での残存経路を検出する、請求項10に記載のディスクドライブ。 - 前記サーボスポークはワイド・バイフェーズでエンコードされる複数のサーボ情報フィールドを含む、請求項1に記載のディスクドライブ。

- 前記複数のサーボ情報フィールドに記録される前記ワイド・バイフェーズマグネットパターンは、2進値0情報値に対しては−−++であり、2進値1情報値に対しては−−++である、請求項1に記載のディスクドライブ。

- 前記複数のサーボ情報フィールドの1つはサーボアドレスマークパターンを含む、請求項13に記載のディスクドライブ。

- 前記サーボアドレスマークパターンはサーボブロックの始まりをマーキングするための9記号ワード000100101(2進)である、請求項14に記載のディスクドライブ。

- 前記少なくとも1つのサーボ情報フィールドは所定のビット長のトラック番号2値パターンを含み、前記パターンは、ワイド・バイフェーズコードとしてデコードされ、次いで符号レートが1でグレイコードとしてデコードされる、請求項1に記載のディスクドライブ。

- 前記トラック番号2値パターンはパリティ記号を含み、さらに、前記トラック番号2値パターンを受取ってデコードし前記パリティ記号をチェックするための手段を含む、請求項16に記載のディスクドライブ。

- 前記少なくとも1つのサーボ情報フィールドは所定ビット長の2つのトラック番号2値パターンを含み、第1のトラック番号はトラックのアドレスであり、第2のトラック番号は前記トラックに隣接する第2のトラックのアドレスである、請求項1に記載のディスクドライブ。

- 前記第2のトラック番号は1/2トラックをオフセットして前記第2のトラック内に延びる状態で記録される、請求項18に記載のディスクドライブ。

- 前記少なくとも1つのサーボ情報フィールドは前記第1および第2のトラック番号に関して計算される誤り訂正コード値をさらに含み、さらに、前記同期サンプリングデータ検出チャネルに結合され、前記第1および第2のトラック番号のデコードされた値をデコードしチェックし訂正するための誤り訂正コードデコードおよび訂正回路を含む、請求項19に記載のディスクドライブ。

- 少なくとも1つの回転するデータ記憶ディスクを含むディスクドライブであって、前記ディスクは、狭いサーボスポークによってデータセクタに分割される記録トラックを規定する主表面を有し、前記ディスクドライブはさらに、

所定の距離とユーザデータ符号レートとを有するコードに従ってエンコードされるユーザデータで記録を行なうための、記録トラックのデータセクタと、

ユーザデータ符号レートの1/4であるサーボ符号レートでワイド・バイフェーズパターンにコード化される少なくとも1つのプリアンブルフィールドと少なくとも1つのサーボ情報フィールドとを有する、記録領域のサーボスポークと、

同期サンプリングデータ検出チャネルとを含み、前記チャネルは、

サーボ制御されるアクチュエータによって記録トラック上で位置決めされるデータトランスデューサヘッドと、

少なくとも前記サーボ情報フィールドにある磁束遷移から前記データトランスデューサヘッドによって磁気的に誘導される電気的アナログ信号を受取るための前置増幅器と、

前記電気的アナログ信号を同期的にサンプリングしてデジタルサンプルを発生させるためのデジタルサンプラとを含み、前記ディスクドライブはさらに、

前記デジタルサンプルを部分応答クラスIVターゲットスペクトルにフィルタ処理してPR4サンプルを発生させるための部分応答フィルタと、

Dを単位遅延演算子として、PR4サンプルをEPR4ターゲットサンプルにフィルタ処理するよう接続される1+Dフィルタと、

前記サーボ情報フィールドから取られるEPR4ターゲットサンプルを受取って最もあり得るサーボ情報2進値としてデコードするよう接続されるワイド・バイフェーズビタビ検出器とを含む、ディスクドライブ。 - 部分応答・クラスIV同期サンプリングデータ検出チャネル内においてワイド・バイフェーズエンコードされたサーボ情報を検出するための差分距離ビタビ検出器であって、

前記チャネルから受取られる現在のワイド・バイフェーズエンコードされたサーボ情報サンプルy(k)の2倍を差分距離m(k−1)から減算して差分値aを発生させるよう接続される差分回路と、

前記差分値aを受けるように接続され、x=a>1およびy=a<−1に従ってxおよびyに対し論理値0および1を計算し、時間k+3において状態0で終わる残存経路の時間k+1の状態をa0(k+1)=NOTyとして計算し、時間k+3において状態1で終わる残存経路の時間k+1での状態をa1(k+1)=xとして計算するための第1の計算機と、

状態a0(k+1)およびa1(k+1)を受けるよう前記第1の計算機に接続されかつ所定の経路長を有し、検出されるサーボ情報を出すための残存メモリユニットと、

xおよびyを受けるよう前記第1の計算機に接続されかつ差分距離m(k−1)および現在のサンプルy(k)を受けるよう接続され、

(x,y)==(1,0)ならば、 z=−2y(k)−1,

(x,y)==(0,1)ならば、 z=−2y(k)+1,

さもなければ、 z=−m(k−1)

に従って原始差分距離を計算するための原始差分距離計算機と、

原始差分距離zを受取りかつ時間調整されたサンプルy(k+1)を受けるよう接続され、現在の差分距離m(k+1)=4y(k+1)+zを計算するための中間差分距離計算機と、

現在の差分距離m(k+1)を受取りそれをワイド・バイフェーズクロック間隔によって遅延させて差分距離m(k−1)を発生させるための遅延レジスタとを含む、差分距離ビタビ検出器。 - 前記チャネルは部分応答・クラスIVターゲットスペクトルに調整される有限インパルス応答フィルタを含み、前記差分回路は前記有限インパルス応答フィルタの出力からサンプルを受けるよう接続される、請求項22に記載の差分距離ビタビ検出器。

- 部分応答・クラスIV同期サンプリングデータ検出チャネル内においてワイド・バイフェーズエンコードされるサーボ情報を検出するためのツリー検索ビタビ検出器であって、

時間k+1でのワイド・バイフェーズエンコードされたサーボ情報サンプルy(k+1)の2倍を受取りそれを現在のサンプルy(k)から減算して差分値aを発生させるよう前記チャネルに接続される差分回路と、

前記差分値aと時間k+2でのサンプルy(k+2)とを受取るよう接続され、第1の距離1=y(k)−2y(k+1)+y(k+2)を計算して出す第1の距離計算機と、

前記差分値aと時間k+3でのサンプルy(k+3)とを受取るよう接続され、第2の距離2=y(k)−2y(k+1)+2y(k+3)を計算して出すための第2の距離計算機と、

前記距離1、距離2および検出器出力値a(k−1)を受取り、

(a(k−1)=0)ならば、

a(k+1)=(距離1<0)OR

((距離1<1)AND(距離2<0.5))

さもなくば、

a(k+1)=(距離1<1)OR

((距離1<0)AND(距離2<−0.5))

に従って中間値a(k+1)を計算するためのツリー検索計算機と、

前記中間値a(k+1)を受取りそれをワイド・バイフェーズクロック間隔によって遅延させて検出器出力値a(k−1)を発生させるための遅延レジスタとを含む、ツリー検索ビタビ検出器。 - 前記チャネルは部分応答・クラスIVターゲットスペクトルに調整される有限インパルス応答フィルタを含み、前記差分回路は前記有限インパルス応答フィルタの出力からサンプルを受けるよう接続される、請求項21に記載のツリー検索ビタビ検出器。

- 部分応答同期サンプリングデータ検出チャネル内でワイド・バイフェーズエンコードされるサーボ情報を検出するための差分距離ビタビ検出器であって、

前記チャネルから受取られる現在のワイド・バイフェーズエンコードされたサーボ情報サンプルの2倍を差分距離から減算して差分値を発生させるよう接続される差分回路と、

前記差分値を受取るよう接続され、複数の論理値を計算し、第1の残存経路の状態を計算し、第2の残存経路の状態を計算するための第1の計算機と、

前記第1の残存経路の状態および前記第2の残存経路の状態を受けるよう前記第1の計算機に接続されかつ所定の経路長を有し、検出されるサーボ鯖報を出すための残存メモリユニットと、

複数の論理値と、差分距離と、現在のサンプルとを受けるよう前記第1の計算機に接続され、現在の差分距離値を計算するための差分距離計算機と、

現在の差分距離値を受取りワイド・バイフェーズクロック間隔で遅延させて差分距離を発生させるための遅延レジスタとを含む、差分距離ビタビ検出器。 - EPR4ターゲットスペクトルに等化される部分応答同期サンプリングデータ検出チャネル内でワイド・バイフェーズエンコードされたサーボ情報を検出するための差分距離ビタビ検出器であって、前記検出器は、時間k+3において状態0で終わる残存経路の時間k−1での状態をa0(k−1)とし、時間k+3において状態1で終わる残存経路の時間k−1での状態をa1(k−1)とし、理想値−2、−1、0、1、および2にスケーリングされた後、時間kでの2つのサンプルの平均のような、受取られる有雑音サンプルをy(k)で示し、時間kでの状態0の経路距離をm0(k)とし、時間kでの状態1の経路距離をm1(k)とし、m(k)=m0(k)−m1(k)つまり差分距離として、

thr(k−1)=m(k−1)−2y(k−1)−4y(k−2)+2y(k−3);

(thr(k−1)>2)ならば、

{m(k+3)=8y(k)+2y(k−1)−4y(k−2)−2y(k−3)−2;

a0(k−1)=a1(k−1)=1;

/*両方の経路は状態1にマージする*/

}

さもなくば(thr(k−1)<−2)ならば、

{m(k+3)=8y(k)+2y(k−1)−4y(k−2)−2y(k−3)+2;

a0(k−1)=a1(k−1)=0;

/*両方の経路は状態0にマージする*/

}

さもなければ、

{m(k+3)=−m(k−1)+8y(k)+4y(k−1)−4y(k−3);

a0(k−1)=1;

a1(k−1)=0

/*経路はマージしない*/

}

に従って、ワイド・バイフェーズエンコードされたサーボ情報を検出する、差分距離ビタビ検出器。 - EPR4ターゲットスペクトルに等化される部分応答同期サンプリングデータ検出チャネル内でワイド・バイフェーズエンコードされたサーボ情報を検出するためのツリー検索ビタビ検出器であって、2つの残存経路は時間k−1でマージし、時間k−1でのマージされた残存経路をa(k−1)とし、等化され平均化されるワイド・バイフェーズエンコードされたサーボ情報サンプルをy(k)、y(k−1)…y(k−7)として、

距離1=2y(k−1)+4y(k−2)−2y(k−3)−8y(k−4)−2y(k−5)+4y(k−6)+2y(k−7);

距離2=8y(k)−4y(k−1)+4y(k−3)−8y(k−4)−2y(k−5)+4y(k−6)+2y(k−7);

(a(k−1)==0)ならば、

a(k+3)=(距離1<0)OR

((距離1<4)AND(距離2<2))

さもなければ、

a(k−3)=((距離1<−4)OR

((距離1<0)AND(距離2<−2))

に従って時間k+3での残存経路を検出する、ワイド・バイフェーズエンコードされたサーボ情報を検出するためのツリー検索ビタビ検出器。

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US601395P | 1995-10-23 | 1995-10-23 | |

| US08/686,998 US5661760A (en) | 1995-10-23 | 1996-07-24 | Wide biphase digital servo information detection, and estimation for disk drive using servo Viterbi detector |

| US08/686,998 | 1996-07-24 | ||

| US60/006,013 | 1996-10-03 | ||

| PCT/US1996/016793 WO1997016011A1 (en) | 1995-10-23 | 1996-10-17 | Wide biphase digital servo information, detection, and estimation for disk drive using viterbi detection |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH10512384A JPH10512384A (ja) | 1998-11-24 |

| JP4014633B2 true JP4014633B2 (ja) | 2007-11-28 |

Family

ID=26675048

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP51668397A Expired - Fee Related JP4014633B2 (ja) | 1995-10-23 | 1996-10-17 | ディスクドライブ、差分距離ビタビ検出器、およびツリー検索ビタビ検出器 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US5661760A (ja) |

| EP (1) | EP0803158B1 (ja) |

| JP (1) | JP4014633B2 (ja) |

| CN (1) | CN1194074A (ja) |

| AU (1) | AU7458996A (ja) |

| CA (1) | CA2207899A1 (ja) |

| DE (1) | DE69634476T2 (ja) |

| WO (1) | WO1997016011A1 (ja) |

Families Citing this family (57)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5862005A (en) * | 1994-10-11 | 1999-01-19 | Quantum Corporation | Synchronous detection of wide bi-phase coded servo information for disk drive |

| DE19781889T1 (de) * | 1996-07-22 | 1999-07-01 | Seagate Technology | Kompensation der Datenerfassung im asymmetrischen Kanal |

| US5857002A (en) * | 1996-08-16 | 1999-01-05 | International Business Machines Corporation | PRML channel with EPR4 equalization and clocking |

| SG55370A1 (en) * | 1996-09-09 | 1998-12-21 | Texas Instruments Inc | Servo demodulator and method for synchronous servo demodulation |

| US6005727A (en) * | 1997-01-28 | 1999-12-21 | Cirrus Logic, Inc. | Servo decoder for decoding an error correcting servo code recorded on a disc storage medium |

| US5829011A (en) * | 1997-01-31 | 1998-10-27 | Texas Instruments Incorporated | Apparatus and method of exchanging data and operational parameters in a mass storage system |

| KR100243218B1 (ko) * | 1997-07-10 | 2000-02-01 | 윤종용 | 데이터 복호장치와 그 방법 |

| US6345074B1 (en) | 1998-03-20 | 2002-02-05 | Cirrus Logic, Inc. | Maximum likelihood servo detector for detecting an error correcting servo code recorded on a disc storage medium |

| US6201652B1 (en) * | 1998-05-29 | 2001-03-13 | Stmicroelectronics, Inc. | Method and apparatus for reading and writing gray code servo data to magnetic medium using synchronous detection |

| US6604223B1 (en) | 1998-08-17 | 2003-08-05 | Seagate Technology Llc | System and method for correcting interference errors in data encoded on storage media |

| US6304407B1 (en) | 1998-10-27 | 2001-10-16 | Maxtor Corporation | Self-writing of servo patterns based on printed reference pattern in rotating disk drive |

| US6397369B1 (en) * | 1998-11-06 | 2002-05-28 | Acorn Technologies, Inc. | Device for using information about the extent of errors in a signal and method |

| US6288860B1 (en) * | 1999-01-04 | 2001-09-11 | Maxtor Corporation | Servo area numbering strategy for computer disk drives |

| EP1066628B1 (en) * | 1999-01-25 | 2003-11-12 | Koninklijke Philips Electronics N.V. | Record carrier and apparatus for scanning the record carrier |

| US6424686B1 (en) | 1999-03-31 | 2002-07-23 | International Business Machines Corporation | Maximum likelihood detection with difference metrics and programmed coefficients |

| US6526104B1 (en) | 1999-03-31 | 2003-02-25 | International Business Machines Corporation | Maximum likelihood detection with programmed coefficients |

| US6657802B1 (en) * | 1999-04-16 | 2003-12-02 | Infineon Technologies Corporation | Phase assisted synchronization detector |

| WO2000063904A1 (en) * | 1999-04-20 | 2000-10-26 | Koninklijke Philips Electronics N.V. | A servo format for disks, preferably hard disks |

| US6594217B1 (en) * | 1999-06-22 | 2003-07-15 | Cirrus Logic, Inc. | Servo synch mark processing in a disk drive system |

| US6480984B1 (en) * | 1999-06-23 | 2002-11-12 | Agere Systems Inc. | Rate (M/N) code encoder, detector, and decoder for control data |

| US6606728B1 (en) | 1999-06-23 | 2003-08-12 | Agere Systems Inc. | Rate (M/N) code encoder, detector, and decoder for control data |

| JP2001028111A (ja) * | 1999-07-13 | 2001-01-30 | Hitachi Ltd | 磁気ディスク装置 |

| JP3886300B2 (ja) * | 1999-07-21 | 2007-02-28 | 富士通株式会社 | 信号処理装置及びその信号処理方法 |

| US6353315B1 (en) | 1999-08-27 | 2002-03-05 | Maxtor Corporation | Method and apparatus for using the data interface of a disk drive to identify and characterize disk flaws |

| US6446236B1 (en) | 1999-10-13 | 2002-09-03 | Maxtor Corporation | Reading encoded information subject to random and transient errors |

| US6594103B1 (en) | 1999-11-12 | 2003-07-15 | Acorn Technologies, Inc. | Read channel generating absolute value servo signal |

| US6545836B1 (en) * | 1999-11-12 | 2003-04-08 | Acorn Technologies, Inc. | Servo control apparatus and method using absolute value input signals |

| US6704156B1 (en) | 2000-01-31 | 2004-03-09 | Maxtor Corporation | Self-writing of servo patterns in a disk drive using a printed reference pattern |

| US6657800B1 (en) * | 2001-02-14 | 2003-12-02 | Stmicroelectronics, Inc. | Viterbi detector and method for recovering a binary sequence from a read signal |

| US6587291B2 (en) | 2001-05-07 | 2003-07-01 | Maxtor Corporation | Asynchronously sampling wide bi-phase codes |

| US7382568B2 (en) * | 2001-06-28 | 2008-06-03 | Stmicroelectronics, Inc. | Circuit and method for detecting a servo wedge on spin-up of a data-storage disk |

| US7206149B2 (en) * | 2001-06-28 | 2007-04-17 | Stmicroelectronics, Inc. | Circuit and method for detecting a spin-up wedge and a corresponding servo wedge on spin up of a data-storage disk |

| US7830630B2 (en) | 2001-06-28 | 2010-11-09 | Stmicroelectronics, Inc. | Circuit and method for detecting the phase of a servo signal |

| US7027247B2 (en) | 2001-06-28 | 2006-04-11 | Stmicroelectronics, Inc. | Servo circuit having a synchronous servo channel and method for synchronously recovering servo data |

| US20030011918A1 (en) * | 2001-06-28 | 2003-01-16 | Stmicroelectronics, Inc. | Data code and method for coding data |

| US7430082B2 (en) * | 2001-06-28 | 2008-09-30 | Stmicroelectronics, Inc. | Circuit and method for demodulating a servo position burst |

| US7839594B2 (en) * | 2001-06-28 | 2010-11-23 | Stmicroelectronics, Inc. | Data-storage disk having few or no spin-up wedges and method for writing servo wedges onto the disk |

| US7440208B1 (en) * | 2001-09-21 | 2008-10-21 | Maxtor Corporation | Flexible partial response targets for data detectors |

| US6934102B2 (en) * | 2001-12-28 | 2005-08-23 | Stmicroeletronics S.R.L. | Encoding and decoding process and corresponding data detector |

| US7116736B2 (en) | 2002-01-02 | 2006-10-03 | International Business Machines Corporation | Method, system, and program for synchronization and resynchronization of a data stream |

| US6985320B2 (en) * | 2002-01-02 | 2006-01-10 | International Business Machines Corporation | Method and apparatus for encoding data to guarantee isolated transitions in a magnetic recording system |

| US7131052B2 (en) * | 2002-08-12 | 2006-10-31 | International Business Machines Corporation | Algebraic decoder and method for correcting an arbitrary mixture of burst and random errors |

| EP1443509A3 (en) * | 2003-01-28 | 2006-01-11 | Kabushiki Kaisha Toshiba | Signal evaluation method, information recording/reproducing apparatus, information reproducing apparatus, and information recording medium |

| EP1593119A1 (en) * | 2003-02-14 | 2005-11-09 | Bill Richard Baker | Compound phase encoding for printed servo patterns |

| US6912099B2 (en) * | 2003-05-13 | 2005-06-28 | Agere Systems Inc. | Maximum likelihood detection of asynchronous servo data employing interpolation |

| US7499233B1 (en) * | 2004-04-20 | 2009-03-03 | Marvell International Ltd. | Multi-phase control information detection and signal polarity determination |

| US7583458B2 (en) * | 2004-07-28 | 2009-09-01 | Agere Systems Inc. | Channel optimization metrics |

| JP2006065918A (ja) * | 2004-08-25 | 2006-03-09 | Tdk Corp | 磁気記録再生装置 |

| US7206146B2 (en) * | 2004-10-27 | 2007-04-17 | Hitachi Global Storage Technologies Netherlands B.V. | Biphase magnetic pattern detector using multiple matched filters for hard disk drive |

| KR100712503B1 (ko) * | 2005-01-13 | 2007-05-02 | 삼성전자주식회사 | 하드디스크 드라이브의 서보 데이터 작성 방법 및 이를이용한 셀프 서보 기록 방법 |

| US7738202B1 (en) * | 2005-10-07 | 2010-06-15 | Seagate Technology, Llc | Wide-biphase-detector quality monitor for sensing of pin layer reversal |

| US7369343B1 (en) * | 2006-07-27 | 2008-05-06 | Western Digital Technologies, Inc. | Disk drive correcting track address during a write operation |

| US8369190B2 (en) * | 2010-06-15 | 2013-02-05 | Texas Instruments Incorporated | Proximity sensing system |

| JP6050059B2 (ja) * | 2012-08-30 | 2016-12-21 | 日本電産サンキョー株式会社 | データ復調装置、データ復調方法、磁気記録データ再生装置、およびプログラム |

| US9053743B2 (en) | 2013-03-11 | 2015-06-09 | Avago Technologies General Ip (Singapore) Pte. Ltd. | Servo marginalization |

| US9025267B1 (en) * | 2014-06-09 | 2015-05-05 | Western Digital Technologies, Inc. | Data storage device using branch metric from adjacent track to compensate for inter-track interference |

| CN115668824A (zh) * | 2020-04-06 | 2023-01-31 | 维尔塞特公司 | 用于通信系统的多阶段突发检测 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5036408A (en) * | 1988-05-12 | 1991-07-30 | Digital Equipment Corporation | High efficiency disk format and synchronization system |

| US5420730A (en) * | 1990-08-17 | 1995-05-30 | Moon; Ronald R. | Servo data recovery circuit for disk drive having digital embedded sector servo |

| US5170299A (en) * | 1990-08-17 | 1992-12-08 | Quantum Corporation | Edge servo for disk drive head positioner |

| US5089757A (en) * | 1991-03-15 | 1992-02-18 | Maxtor Corporation | Synchronous digital detection of position error signal |

| US5341249A (en) * | 1992-08-27 | 1994-08-23 | Quantum Corporation | Disk drive using PRML class IV sampling data detection with digital adaptive equalization |

| US5341387A (en) * | 1992-08-27 | 1994-08-23 | Quantum Corporation | Viterbi detector having adjustable detection thresholds for PRML class IV sampling data detection |

| US5384671A (en) * | 1993-12-23 | 1995-01-24 | Quantum Corporation | PRML sampled data channel synchronous servo detector |

| US5619539A (en) * | 1994-02-28 | 1997-04-08 | International Business Machines Corporation | Data detection methods and apparatus for a direct access storage device |

| JP2715057B2 (ja) * | 1994-04-05 | 1998-02-16 | クウォンタム・コーポレイション | データ記憶装置においてアンダーシュート誘起タイミング位相ステップを排除する方法およびハードディスクドライブ |

| US5576906A (en) * | 1994-10-11 | 1996-11-19 | Quantum Corporation | Synchronous detection of concurrent servo bursts for fine head position in disk drive |

| US5521945A (en) * | 1995-06-30 | 1996-05-28 | Quantum Corporation | Reduced complexity EPR4 post-processor for sampled data detection |

-

1996

- 1996-07-24 US US08/686,998 patent/US5661760A/en not_active Expired - Lifetime

- 1996-10-17 CN CN96191556A patent/CN1194074A/zh active Pending

- 1996-10-17 DE DE69634476T patent/DE69634476T2/de not_active Expired - Fee Related

- 1996-10-17 WO PCT/US1996/016793 patent/WO1997016011A1/en active IP Right Grant

- 1996-10-17 CA CA002207899A patent/CA2207899A1/en not_active Abandoned

- 1996-10-17 AU AU74589/96A patent/AU7458996A/en not_active Abandoned

- 1996-10-17 EP EP96936744A patent/EP0803158B1/en not_active Expired - Lifetime

- 1996-10-17 JP JP51668397A patent/JP4014633B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JPH10512384A (ja) | 1998-11-24 |

| CN1194074A (zh) | 1998-09-23 |

| CA2207899A1 (en) | 1997-05-01 |

| EP0803158A1 (en) | 1997-10-29 |

| US5661760A (en) | 1997-08-26 |

| WO1997016011A1 (en) | 1997-05-01 |

| EP0803158B1 (en) | 2005-03-16 |

| DE69634476T2 (de) | 2006-02-23 |

| DE69634476D1 (de) | 2005-04-21 |

| EP0803158A4 (ja) | 1997-11-12 |

| AU7458996A (en) | 1997-05-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4014633B2 (ja) | ディスクドライブ、差分距離ビタビ検出器、およびツリー検索ビタビ検出器 | |

| JP3926391B2 (ja) | ディスクドライブのためのワイド・バイフェーズコード化サーボ情報の同期検出 | |

| US5854714A (en) | Digital servo demodulation for sampled amplitude magnetic recording | |

| US5576906A (en) | Synchronous detection of concurrent servo bursts for fine head position in disk drive | |

| US7068461B1 (en) | Servo writing a disk drive by overwriting a harmonic frequency fill pattern in the servo burst area | |

| EP1596390B1 (en) | Data recording system | |

| US6646822B1 (en) | Sampled amplitude read channel employing pipelined reads to reduce the gap between sectors | |

| JP4602694B2 (ja) | 補間を用いた非同期サーボ・データの最尤検出 | |

| US5961658A (en) | PR4 equalization and an EPR4 remod/demod sequence detector in a sampled amplitude read channel | |

| US7457066B2 (en) | Method and apparatus for phase-shift null-burst-pattern | |

| KR0162260B1 (ko) | 고밀도 디스크 드라이브용 서보 제어 시스템과 위치 에러 신호 복조 시스템 및 그 방법 | |

| US5615065A (en) | Phase-compensated servo pattern and position error-sensing detector | |

| US6856480B2 (en) | Phase tolerant servo gray code detector | |

| US6513141B1 (en) | Sampled amplitude read channel employing a trellis sequence detector and a post processor for generating error metrics used to correct errors made by the trellis sequence detector | |

| US5862161A (en) | Sampled amplitude read channel with simplified sequence detector matched to partial erasure | |

| EP0821827A1 (en) | Branch metric compensation for digital sequence detection | |

| JPH02263360A (ja) | ディジタル信号再生装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060926 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20061225 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20070219 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070315 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070605 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070712 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20070904 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20070912 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100921 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100921 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100921 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110921 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110921 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120921 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130921 Year of fee payment: 6 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |