JP3942902B2 - 半導体装置の作製方法 - Google Patents

半導体装置の作製方法 Download PDFInfo

- Publication number

- JP3942902B2 JP3942902B2 JP2002019256A JP2002019256A JP3942902B2 JP 3942902 B2 JP3942902 B2 JP 3942902B2 JP 2002019256 A JP2002019256 A JP 2002019256A JP 2002019256 A JP2002019256 A JP 2002019256A JP 3942902 B2 JP3942902 B2 JP 3942902B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- semiconductor film

- semiconductor

- amorphous

- manufacturing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Landscapes

- Liquid Crystal (AREA)

- Formation Of Insulating Films (AREA)

- Thin Film Transistor (AREA)

Description

【発明の属する技術分野】

本発明は、イオンドーピング法を利用した半導体装置の作製方法に関し、特にイオンドーピング工程の前処理の保護膜成膜方法に関する。尚、本明細書に於いて半導体装置とは、薄膜トランジスタ(Thin-Film-Transistor:以下、TFTと略記)で回路構成される半導体装置全般を指し、例えばアクティブマトリクス形の液晶表示装置又は有機EL(Electro-luminescenceの略)表示装置等の半導体表示装置をその範疇に含むものである。

【0002】

【従来の技術】

近年、アクティブマトリクス型液晶表示装置の需要が急速に高まり、ガラス基板又は石英基板上に形成した半導体膜でTFTを作製する技術開発が盛んに行われている。ガラス基板等の絶縁性基板上に百数十万個もの単位で作製されるTFTは、構成する電気回路の機能に応じて、所定の電気特性を示すものでなければならない。TFTの電気特性の1つに、Vthというパラメータがある。

【0003】

Vthとは、TFTのドレイン電流が流れ始める時のゲート電圧で、チャネル領域に反転層が形成される電圧として定義される。従って、Vthが高い程、TFTの動作電圧が高いということができる。

【0004】

ところで、Vthには、様々な外的要因によって変化し易いという問題がある。例えば、活性層中の汚染不純物、ゲート絶縁膜の固定電荷や可動電荷、活性層/ゲート絶縁膜界面の界面準位、ゲート電極と活性層との仕事関数差等が挙げられる。この場合、活性層中の汚染不純物やゲート絶縁膜中の可動電荷等はプロセスの清浄化により低減できるが、固定電荷や界面準位及び仕事関数差は素子の材質で決定されてしまう為、容易に変更できない。

【0005】

上記の外的要因により、TFTのVthはプラス側/或いはマイナス側にシフトして、変化することになる。TFTの作製工程に於いては、変化し易いVthの制御が重要な技術となっており、Vthの制御技術としてチャネルドープ技術が知られている。チャネルドープとは、ゲート絶縁膜下の活性層中に所定濃度の不純物を添加して、意図的にTFTのVthをシフトさせ、所望のVthを制御する技術である。例えば、Vthがマイナス側にシフトしている場合には、ドーパントにp型の不純物元素を用い、プラス側にシフトしている場合には、ドーパントにn型の不純物元素を用いて、Vthの制御が行われている。

【0006】

この様なチャネルドープには、n型又はp型の不純物元素をドーピングするイオンドーピング法が利用されている。イオンドーピング法とは、質量分離せずに不純物元素を打ち込む方法で、質量分離手段を持たない為、大面積化が容易で、アクティブマトリクス型液晶表示装置の作製に一般に適用されている。尚、イオンドーピング法には、p型不純物としてB(ボロン),Ga(ガリウム),In(インジウム)が使用され、n型不純物としてP(リン),As(砒素),Sb(アンチモン)等が使用されている。

【0007】

【発明が解決しようとする課題】

TFTの活性層であるシリコン系半導体膜に直にチャネルドープ等のドーピング処理を行う場合、シリコン系半導体膜がエッチングされる問題が有る。従来、当該問題の対策として、ドーピング工程の前処理にCVD法によりシリコン酸化膜やシリコン酸窒化膜等の保護膜を堆積して、その上から不純物イオンをドーピング処理していたが、以下の難点が有り、好ましくない。

【0008】

先ず、単なる前処理にCVD法を適用することにより、前処理に掛かる時間が長くなり、不純物イオンのドーピング工程全体の処理時間も長くなる。この為、不純物イオンのドーピング工程全体にとって、単位時間当たりの基板の処理枚数が少なくなり、スループット的に好ましくない。また、プラズマCVD装置や減圧CVD装置等のCVD装置を前処理に適用する為、前処理に掛かる原価が高くなり、全体の生産原価が高くなる点でも好ましくない。従って、シリコン系半導体膜のエッチング防止策として、簡便で原価的に安いエッチング防止策が求められている。

【0009】

本発明は、上記従来技術の問題点を解決することを課題とする。より特定すれば、シリコン系半導体膜へのドーピング工程に於いて、シリコン系半導体膜のエッチング防止策として、簡便で原価的に安い前処理工程を提供することを課題とする。別言すると、当該前処理工程によるシリコン系半導体膜のエッチング防止策を施した半導体装置の作製方法を提供することを課題とする。

【0010】

【課題を解決する為の手段】

〔チャネルドープ前処理の実験〕

TFTの活性層は、非晶質シリコン膜又は多結晶シリコン膜、更には触媒元素を利用して成膜した結晶質シリコン膜等のシリコン系半導体膜からできている為、オゾン含有水処理等の簡便な処理工程により、極薄のシリコン酸化膜であるケミカル酸化膜を成膜することが可能である。当該ケミカル酸化膜がシリコン系半導体膜へのイオンドーピング工程の保護膜として機能できれば、上記従来技術が抱える問題点を解決できる為、表1の実験条件に基づき以下の実験を行った。尚、本明細書でケミカル酸化膜とは、オゾン含有水や過酸化水素水等の酸化作用を有する化学薬液を使用して成膜される酸化膜のことである。当該ケミカル酸化膜の膜厚は、一般に5nm以下である。

【表1】

【0011】

先ず、基板No1〜4の4枚のガラス基板上にプラズマCVD法により膜厚53nmの非晶質シリコン膜を300℃の堆積温度で堆積した。当該非晶質シリコン膜には、自然酸化膜が付いている為、希フッ酸で自然酸化膜を除去した。次に、基板No2と基板No4の2枚の基板について、非晶質シリコン膜の全面をオゾン含有水で酸化することにより、5nm以下のケミカル酸化膜(極薄のシリコン酸化膜)を成膜した。その後、イオンドーピング装置を用いて、基板No1〜4の4枚の基板について、1×1013〜1×1014atoms/cm2の範囲でB元素のドーズ量を振ってドーピング処理を行った。尚、B元素の原料ガスにはジボラン(B2H6)ガスを水素で希釈したものを用い、希釈率は0.1%と1.0%の場合について実験した。イオンドーピング後に、非晶質シリコン膜の残膜厚を測定して、ドーピング処理時のエッチング状態を調査した。

【0012】

本実験の結果を図1に示す。図1から判る様に、オゾン含有水処理により非晶質シリコン膜の表面にケミカル酸化膜を成膜しなかった場合には、非晶質シリコン膜がドーピング処理時にエッチングされること、一方、非晶質シリコン膜の表面にケミカル酸化膜を成膜した場合には、非晶質シリコン膜は殆どエッチングされないことが認められた。また、希釈率0.1%のジボランガスの場合、希釈率1.0%のジボランガスに比較して、非晶質シリコン膜のエッチングがより進行していること、即ち水素イオン比率の大きい方が、非晶質シリコン膜のエッチングが激しいことが認められた。従って、非晶質シリコン膜のエッチングは、水素イオンとの反応が関与しているものと考えられる(図1参照)。

【0013】

本実験の結果は、オゾン含有水による5nm以下のケミカル酸化膜が、ドーピング処理時の水素イオンによる非晶質シリコン膜のエッチングを防止できることを示している。このケミカル酸化膜の成膜は、オゾン含有水による処理に限らず、過酸化水素水による処理でも可能であり、またケミカル酸化膜ではないけれど、酸素を含む雰囲気中で紫外線(UV)を照射することによっても極薄のシリコン酸化膜を成膜することができる。何れの方法で成膜しても、水素イオンによる非晶質シリコン膜のエッチングを防止できると考えられる。

【0014】

本実験に於いては、5nm以下のケミカル酸化膜について検討したが、イオンドーピング装置での水素イオン比率が低い場合は、非晶質シリコン膜表面のダングリングボンドを酸素で終端させることでも、ある程度エッチングを防止できると考えられる。酸素で終端した場合、ダングリングボンドはSi−O結合になっており、Si−O結合(193.5kcal/mol)の結合エネルギーがSi−H結合(≦71.5kcal/mol)に比べて大きい為、水素イオンがSi−O結合に接近しても、水素イオンとの反応が抑制される為である。従って、非晶質シリコン膜表面に存在するダングリングボンドをSi−H結合より結合エネルギーの大きい元素で終端することで、非晶質シリコン膜のエッチングを防止できることが示唆される。

【0015】

尚、Si−H結合及びSi−O結合の結合エネルギーは、応用物理データブック(応用物理学会編)の561頁に記載されている2原子分子の結合強度(表10.35)のデーターより抜粋したものである。

【0016】

以上の実験により、水素イオンが発生する原料ガスを使用してドーピングする場合に有効な、以下の発明が導かれる。尚、水素イオンが発生する原料ガスとしては、ジボラン(B2H6)、ホスフィン(PH3)及びアルシン(AsH3)又はこれら材料を水素で希釈したものが挙げられる。また、質量分離手段を有するイオン注入装置でイオン注入する場合は、基本的に質量分離により水素イオンを無くすことができる為、シリコン膜のエッチングは生じないと考えられる。

【0017】

(発明1)シリコン系半導体膜へのイオンドーピング工程に於いて、CVD法による保護膜の成膜に代わって、前処理にシリコン系半導体膜の表面でのケミカル酸化膜の成膜工程を導入する。

(発明2)シリコン系半導体膜へのイオンドーピング工程に於いて、CVD法による保護膜の成膜に代わって、前処理にシリコン系半導体膜の表面のダングリングボンドをSi−H結合(≦71.5kcal/mol)より結合エネルギーの大きい元素で終端する工程(以下、ダングリングボンド終端工程と略記)を導入する。

【0018】

〔半導体装置の作製方法〕

上記従来技術の問題点を解決する為、半導体装置の作製方法の視点で本発明の構成を記載する。

【0019】

本発明の構成は、絶縁性基板上にシリコン系半導体膜を成膜する第1の工程と、前記シリコン系半導体膜に対して不純物イオンをドーピングする第2の工程とを備えた半導体装置の作製方法に於いて、前記第2の工程は、前処理として、前記シリコン系半導体膜の表面にケミカル酸化膜を成膜すること、又は前記シリコン系半導体膜の表面のダングリングボンドを酸素で終端すること、又は前記シリコン系半導体膜の表面のダングリングボンドをSi−H結合より結合エネルギーの大きい元素で終端することを特徴としている。

【0020】

本発明の他の構成は、絶縁性基板上にシリコンを含む非晶質半導体膜を堆積する第1の工程と、前記シリコンを含む非晶質半導体膜に対してチャネルドープを行う第2の工程と、前記シリコンを含む非晶質半導体膜を熱処理し、シリコンを含む多結晶半導体膜を成膜する第3の工程と、前記シリコンを含む多結晶半導体膜をパターン形成して、TFTの活性層となる半導体層を形成する第4の工程と、前記半導体層上にゲート絶縁膜を堆積する第5の工程と、前記半導体層上に前記ゲート絶縁膜を挟んでゲート電極を形成する第6の工程と、前記ゲート電極をマスクに、前記半導体層に不純物イオンをドーピングする第7の工程とを備えた半導体装置の作製方法に於いて、前記第2の工程は、前処理として、前記シリコンを含む非晶質半導体膜の表面にケミカル酸化膜を成膜すること、又は前記シリコンを含む非晶質半導体膜の表面のダングリングボンドを酸素で終端すること、又は前記シリコンを含む非晶質半導体膜の表面のダングリングボンドをSi−H結合より結合エネルギーの大きい元素で終端することを特徴としている。

【0021】

本発明の他の構成は、絶縁性基板上にシリコンを含む非晶質半導体膜を堆積し、熱処理によりシリコンを含む多結晶半導体膜を成膜する第1の工程と、前記シリコンを含む多結晶半導体膜に対してチャネルドープを行う第2の工程と、前記シリコンを含む多結晶半導体膜をパターン形成して、TFTの活性層となる半導体層を形成する第3の工程と、前記半導体層上にゲート絶縁膜を堆積する第4の工程と、前記半導体層上に前記ゲート絶縁膜を挟んでゲート電極を形成する第5の工程と、前記ゲート電極をマスクに前記半導体層に不純物イオンをドーピングする第6の工程とを備えた半導体装置の作製方法に於いて、前記第2の工程は、前処理として、前記シリコンを含む多結晶半導体膜の表面にケミカル酸化膜を成膜すること、又は前記シリコンを含む多結晶半導体膜の表面のダングリングボンドを酸素で終端すること、又は前記シリコンを含む多結晶半導体膜の表面のダングリングボンドをSi−H結合より結合エネルギーの大きい元素で終端することを特徴としている。

【0022】

本発明の他の構成は、絶縁性基板上にシリコンを含む非晶質半導体膜を堆積し、前記非晶質半導体膜に結晶化の助長作用を有する触媒元素を添加し、熱処理によりシリコンを含む結晶質半導体膜を成膜する第1の工程と、前記シリコンを含む結晶質半導体膜に対してチャネルドープを行う第2の工程と、前記シリコンを含む結晶質半導体膜をパターン形成して、TFTの活性層となる半導体層を形成する第3の工程と、前記半導体層上にゲート絶縁膜を堆積する第4の工程と、前記半導体層上に前記ゲート絶縁膜を挟んでゲート電極を形成する第5の工程と、前記ゲート電極をマスクに前記半導体層に不純物イオンをドーピングする第6の工程とを備えた半導体装置の作製方法に於いて、前記第2の工程は、前処理として、前記シリコンを含む結晶質半導体膜の表面にケミカル酸化膜を成膜すること、又は前記シリコンを含む結晶質半導体膜の表面のダングリングボンドを酸素で終端すること、又は前記シリコンを含む結晶質半導体膜の表面のダングリングボンドをSi−H結合より結合エネルギーの大きい元素で終端することを特徴としている。

【0023】

本発明の他の構成は、絶縁性基板上にシリコンを含む非晶質半導体膜を堆積する第1の工程と、前記シリコンを含む非晶質半導体膜に対してチャネルドープを行う第2の工程と、前記シリコンを含む非晶質半導体膜に結晶化の助長作用を有する触媒元素を添加し、熱処理によりシリコンを含む結晶質半導体膜を成膜する第3の工程と、前記シリコンを含む結晶質半導体膜をパターン形成して、TFTの活性層となる半導体層を形成する第4の工程と、前記半導体層上にゲート絶縁膜を堆積する第5の工程と、前記半導体層上に前記ゲート絶縁膜を挟んでゲート電極を形成する第6の工程と、前記ゲート電極をマスクに前記半導体層に不純物イオンをドーピングする第7の工程とを備えた半導体装置の作製方法に於いて、前記第2の工程は、前処理として、前記シリコンを含む非晶質半導体膜の表面にケミカル酸化膜を成膜すること、又は前記シリコンを含む非晶質半導体膜の表面のダングリングボンドを酸素で終端すること、又は前記シリコンを含む非晶質半導体膜の表面のダングリングボンドをSi−H結合より結合エネルギーの大きい元素で終端することを特徴としている。

【0024】

上記発明の構成に於いて、前記シリコン系半導体膜としては、シリコンを含む半導体膜であれば何でも良く、例えばシリコンを含む非晶質半導体膜でも良いし、シリコンを含む非晶質半導体膜を熱処理して得られるシリコンを含む多結晶半導体膜でも良いし、シリコンを含む非晶質半導体膜に結晶化の助長作用を有する触媒元素を添加した後に熱処理して得られるシリコンを含む結晶質半導体膜でも良い。尚、本明細書に於いては、シリコンを含む非晶質半導体膜、シリコンを含む多結晶半導体膜、及びシリコンを含む結晶質半導体膜なる技術用語を区別して用いている為、技術用語の定義について明確にする。シリコンを含む非晶質半導体膜とは、結晶化により半導体特性を有するシリコンを含む非晶質膜のことで、非晶質シリコン膜も当然に含まれるが、シリコンを含む非晶質半導体膜は全て含まれる。例えば、SixGe1-x(0<X<1)の形式で記載されるシリコンとゲルマニウムの化合物から成る非晶質膜も含まれる。また、シリコンを含む結晶質半導体膜とは、結晶化の助長作用を有する触媒元素を利用して得られる結晶質半導体膜のことで、通常の多結晶半導体膜と比較し、結晶粒が概略同一方向に配向しており、高い電界効果移動度を有する等の特徴がある為、敢えて多結晶半導体膜と区別して、結晶質半導体膜と記載している。

【0025】

此処で、結晶化の助長作用を有する触媒元素について記載する。触媒元素とは、結晶化を助長する為に、シリコンを含む非晶質半導体膜に添加されるもので、Ni(ニッケル)等の金属元素が適用されている。Ni元素以外の触媒元素としては、Fe(鉄),Co(コバルト),Ru(ルテニウム),Rh(ロジウム),Pd(パラジウム),Os(オスミウム),Ir(イリジウム),Pt(白金),Cu(銅),Au(金)等の金属元素が代表的である。当該触媒元素は、通常では選択された1つの元素が適用されるが、2以上の元素を組み合わせて適用しても構わない。尚、本発明者らの実験では、Ni元素が最も好適な触媒元素であることが判明している。

【0026】

また、上記発明の構成に於いて、前記不純物イオンとしては、P(リン)元素とAs(ヒ素)元素で代表されるn型不純物と、B(ボロン)元素で代表されるp型不純物が挙げられる。P元素の場合はホスフィン(PH3)を水素で希釈したイオン源が使用され、As元素の場合はアルシン(AsH3)を水素で希釈したイオン源が使用され、B元素の場合はジボラン(B2H6)を水素で希釈したイオン源が使用されており、何れも水素で希釈している為、ドーピング時に水素イオンが生成される。これらの不純物イオンをシリコン系半導体膜へドーピングする際、当該水素イオンがシリコン系半導体膜のエッチャントとして作用することが考えられている。

【0027】

また、上記発明の構成に於いて、前記シリコン系半導体膜の表面に成膜される前記ケミカル酸化膜としては、オゾン含有水で処理することにより得られる膜厚5nm以下のシリコン酸化膜が代表であるが、過酸化水素水による処理で成膜しても良い。また、厳密なケミカル酸化膜ではないけれど、酸素を含む雰囲気中で紫外線(UV)を照射することによっても、ケミカル酸化膜と同様の作用を有する極薄のシリコン酸化膜を成膜することができる。また、前記ケミカル酸化膜の代わりに、前記シリコン系半導体膜の表面のダングリングボンドを酸素で終端することも考えられ、更にはSi−H結合より結合エネルギーの大きい元素で終端することも考えられる。

【0028】

以上の様に構成された発明によれば、シリコン系半導体膜に不純物イオンをドーピングする際、シリコン系半導体膜の保護膜に簡便な方法で成膜されるケミカル酸化膜を適用できる為、イオンドーピング工程全体のスループットの向上に有効である。また、イオンドーピング工程の前処理に高価格のプラズマCVD装置や減圧CVD装置が不要となる為、生産コストの低減に有効である。尚、ケミカル酸化膜の代わりに、シリコン系半導体膜の表面のダングリングボンドをSi−H結合より結合エネルギーの大きい元素、例えば酸素で終端する場合に於いても、当該終端工程がCVD工程に比較し簡便である為、ケミカル酸化膜と同様の効果を有するものと考える。

【0029】

【発明の実施の形態】

〔実施形態1〕

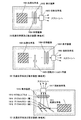

本実施形態では、結晶構造を有するシリコン系半導体膜に対してチャネルドープするTFT作製方法の例として、触媒元素を利用して結晶化される結晶質シリコン膜に対してチャネルドープするTFT作製方法を図2〜3に基づき具体的に記載する。尚、チャネルドープは、nチャネル型TFTに対してのみ行うものとする。

【0030】

先ず、ガラス基板101上に膜厚100nmのシリコン酸窒化膜から成る下地膜102をプラズマCVD法により堆積し、続けて膜厚15〜70nm、より好ましくは膜厚30〜60nmの非晶質シリコン膜103を堆積する。本実施形態では、膜厚50nmの非晶質シリコン膜103をプラズマCVD法により堆積した。堆積の際、非晶質シリコン膜103の表面には、空気中の酸素の影響により、自然酸化膜(図示せず)が付いている為、希フッ酸処理により洗浄する。その後、所定時間のオゾン含有水処理により、非晶質シリコン膜103の表面に極薄のシリコン酸化膜から成るケミカル酸化膜104を成膜する。このケミカル酸化膜104は、後にスピン塗布法により添加される触媒元素を含んだ溶液(以下、触媒元素溶液と略記)であるNi水溶液の濡れ性改善を図る為に行われる。尚、本実施形態では、非晶質シリコン膜103を堆積したが、非晶質シリコン膜103以外にも、シリコンを含む非晶質半導体膜、例えばSixGe1-x(0<X<1)の形式で記載されるシリコンとゲルマニウムの化合物から成る非晶質半導体膜を適用することも可能である。また、ケミカル酸化膜104は、オゾン含有水処理により成膜しているが、過酸化水素水による処理で成膜しても良い(図2−A参照)。

【0031】

次に、触媒元素溶液であるNi水溶液をスピン塗布法により、非晶質シリコン膜103(厳密にはケミカル酸化膜104)の全面に添加する。Ni水溶液のNi濃度は、重量換算で0.1〜50ppm、より好ましくは1〜30ppm程度の濃度範囲が好適である。本実施形態では、Ni濃度が10ppmのNi水溶液をスピン塗布法により添加した。スピン塗布の際、基板を回転して、余分なNi水溶液を吹き飛ばして除去し、非晶質シリコン膜103(厳密にはケミカル酸化膜104)の全面に極薄のNi含有層105を成膜する(図2−B参照)。

【0032】

次に、専用の熱処理炉を使用して、窒素雰囲気中で非晶質シリコン膜103を熱処理する。当該熱処理は、結晶化を助長する触媒元素の作用により、450〜750℃の温度範囲で熱処理することにより、結晶化が達成されるが、熱処理温度が低いと処理時間を長くしなければならず、生産効率が低下するという一般的性質がある。また、600℃以上の熱処理は、基板として適用するガラス基板の耐熱性の問題が表面化してしまう。従って、ガラス基板を使用する場合には、上記熱処理工程の温度は450〜600℃の範囲が妥当である。また、実際の熱処理は、非晶質シリコン膜103の堆積方法によっても、好適な熱処理条件が異なっており、例えば減圧CVD法で堆積した場合は600℃−12時間程度の熱処理が好適であり、プラズマCVD法で堆積した場合は550℃−4時間程度の熱処理で十分なことが判っている。本実施形態に於いては、プラズマCVD法で膜厚50nmの非晶質シリコン膜103を堆積している為、550℃−4時間の熱処理を行うことにより結晶質シリコン膜106を成膜した。この様に、非晶質シリコン膜103の全面にNi水溶液を添加して熱処理する結晶成長法は、Ni元素を添加した非晶質シリコン膜103の表面から縦方向(基板面に対し垂直方向)へ結晶成長が進行する為、発明者らにより縦成長法と命名されている(図2−B参照)。

【0033】

次に、得られた結晶質シリコン膜106の結晶性を改善させる為、結晶質シリコン膜106に対しレーザー照射を行う。結晶質シリコン膜106は電熱炉による熱処理のみでは結晶化が不完全な状態となっており、非晶質成分が不規則に残存している。此処では、結晶化の不完全性を改善する目的で、結晶質シリコン膜106に対しパルス発振型のKrFエキシマレーザー(波長248nm)を適用している。このエキシマレーザーは紫外光を発振する為、被レーザー照射領域に於いて、瞬間的に溶融固化が繰り返される。この為、被レーザー照射領域に於いて、一種の非平衡状態が実現され、Ni元素が非常に移動し易い状態となる。尚、このレーザー照射工程を省略することも可能であるが、当該レーザー照射工程により、結晶性の改善の他に、後のゲッタリング工程の効率を向上させる効果も有している為、当該レーザー照射工程は省略しない方が好ましい(図2−B参照)。

【0034】

次に、得られた結晶質シリコン膜106の表面には、Ni含有層105等の汚染層が付いている為、希フッ酸で洗浄し、結晶質シリコン膜106の表面を清浄化する。その後、チャネルドープの前処理として、所定時間のオゾン含有水処理により、結晶質シリコン膜106の表面に5nm以下の極薄のシリコン酸化膜から成るケミカル酸化膜107を成膜する。尚、本実施形態に於いては、ケミカル酸化膜107をオゾン含有水処理により成膜しているが、過酸化水素水による処理で成膜しても良い。また、厳密なケミカル酸化膜ではないけれど、酸素を含む雰囲気中で紫外線(UV)を照射することによっても、ケミカル酸化膜と同様の作用を有する極薄のシリコン酸化膜を成膜することができる(図2−C参照)。

【0035】

また、チャネルドープ工程で使用されるイオンドーピング装置での水素イオン比率が低い場合は、チャネルドープの前処理として、結晶質シリコン膜106表面のダングリングボンドを酸素等のSi−H結合(≦71.5kcal/mol)より結合エネルギーの大きい元素で終端させることも考えられる。

【0036】

次に、結晶質シリコン膜106のnチャネル型TFTに対応する領域を開口領域とする、チャネルドープ用マスクとなるレジストパターン108を形成する。その後、イオンドーピング装置を使用して、前記レジストパターン108をマスクに、結晶質シリコン膜106のnチャネル型TFTに対応する領域にp型不純物であるB元素をドーピングし、チャネルドープを行う。チャネルドープでは、ジボラン(B2H6)ガスを水素で希釈したイオンソースが使用されている。チャネルドープは、通常、ジボラン希釈率0.01〜1.0%、加速電圧1〜50kV、イオン電流10〜500nA、ドーズ量1×1011〜1×1014atoms/cm2のドーピング条件で処理される。尚、本実施形態に於いては、ジボラン希釈率0.1%、加速電圧15kV、イオン電流50nA、ドーズ量4×1013atoms/cm2のチャネルドープ条件でドーピング処理した(図2−C参照)。

【0037】

次に、チャネルドープのマスクとなったレジストパターン108を除去する。その後、通常のフォトリソグラフィ処理とドライエッチング処理により、結晶質シリコン膜106をパターン形成して、nチャネル型TFTに対応する半導体層109nとpチャネル型TFTに対応する半導体層109pを形成する。此処で、前記半導体層109n,109pの表面には自然酸化膜(又はチャネルドープの前処理で成膜したケミカル酸化膜107)が成膜されている為、希フッ酸処理により除去する。この様にして、結晶質シリコン膜106から成る半導体層109n,109pの表面を清浄化した後に、プラズマCVD法又は減圧CVD法により、膜厚100nmのシリコン酸化膜から成るゲート絶縁膜110を堆積する(図2−D参照)。

【0038】

次に、ゲート電極材料である導電性膜(膜厚400nm)をスパッタ法又はCVD法により堆積し、通常のフォトリソグラフィ処理とドライエッチング処理によりパターン形成し、nチャネル型TFTに対応するゲート電極111nとpチャネル型TFTに対応するゲート電極111pを形成する。此処で適用されるゲート電極材料としては、後工程である、半導体層109n,109pにドーピングされる不純物イオンの活性化を兼ねたゲッタリング用の熱処理温度(550〜650℃程度)に耐え得る耐熱性材料が好ましい。耐熱性材料としては、例えばTa(タンタル),Mo(モリブデン),Ti(チタン),W(タングステン),Cr(クロム)等の高融点金属、及び高融点金属とシリコンの化合物である金属シリサイド、及びn型又はp型の導電性を有する多結晶シリコン等が挙げられる。尚、本実施形態では、膜厚400nmのW金属膜を適用している(図2−E参照)。

【0039】

次に、ゲート電極111n,111pをマスクに、イオンドーピング装置を使用して、n型不純物であるP元素をドーピングする。当該イオンドーピング処理は、加速電圧10〜100kV、ドーズ量1×1014〜1×1016atoms/cm2の条件で処理される。尚、本実施形態に於いては、加速電圧80kV、ドーズ量1.7×1015atoms/cm2の条件でドーピング処理した。当該イオンドーピング処理により、nチャネル型TFTに対応する半導体層109nには、ソース領域及びドレイン領域として機能するn型の導電型を有する高濃度不純物領域(n+領域)113nと、チャネル領域として機能する実質的に真性な領域112nが形成される。また、pチャネル型TFTに対応する半導体層109pには、n型の導電型を有する高濃度不純物領域(n+領域)113pと、チャネル領域として機能する実質的に真性な領域112pが形成されている(図2−E参照)。

【0040】

次に、pチャネル型TFTに対応する半導体層109pの全域を開口領域とするレジストパターン114を形成する。その後、前記レジストパターン114及びpチャネル型TFTに対応するゲート電極111pをマスクに、イオンドーピング装置を使用して、p型不純物であるB元素をドーピングする。当該イオンドーピング処理は、加速電圧10〜100kV、ドーズ量2×1014〜5×1016atoms/cm2の条件で処理される。尚、本実施形態に於いては、加速電圧60kV、ドーズ量2.5×1015atoms/cm2の条件でドーピング処理した。当該イオンドーピング処理により、pチャネル型TFTに対応するn型の高濃度不純物領域113pの導電型が反転し、ソース領域及びドレイン領域として機能するp型の導電型を有する高濃度不純物領域(p+領域)115pが形成される(図3−A参照)。

【0041】

次に、前記レジストパターン114を除去した後、膜厚100〜300nmの無機膜から成る第1の層間絶縁膜116を堆積する。本実施形態では、膜厚150nmのシリコン酸窒化膜から成る第1の層間絶縁膜116をプラズマCVD法により堆積している。その後、半導体層109n,109pにドーピングされた不純物元素(n型不純物とp型不純物)の熱活性化の為、電熱炉により600℃−12時間の熱処理を行う。当該熱処理は不純物元素の熱活性化処理の為に行うものであるが、チャネル領域として機能する実質的に真性な領域112n,112pに含まれる不要な触媒元素(Ni元素)のゲッタリング処理も兼ねている。この方法で製造された結晶質シリコン膜を有するTFTは、チャネル領域の不要な触媒元素(Ni元素)がゲッタリングされることにより、高い電界効果移動度を有しており、またオフ電流の低下等の良好な電気特性を有している。その後、半導体層109n,109p表面のダングリングボンドを終端させる為、410℃−1時間の水素化処理を水素3%含有の窒素雰囲気中で行う(図3−B参照)。

【0042】

次に、前記第1の層間絶縁膜116の上に、膜厚1〜3μmの透明な有機膜から成る第2の層間絶縁膜117を成膜する。本実施形態では、膜厚1.6μmのアクリル樹脂膜から成る第2の層間絶縁膜117を成膜している。その後、通常のフォトリソグラフィ処理とドライエッチング処理により、第2の層間絶縁膜117と前記第1の層間絶縁膜116、更には前記第1の層間絶縁膜116の下層に存在するゲート絶縁膜110にコンタクトホール118を形成する(図3−C参照)。

【0043】

次に、導電性を有する膜厚200〜800nmの金属膜を堆積する。本実施形態では、50nm厚のTi膜と500nm厚のAl−Ti合金膜の積層膜をスパッタ法により堆積する。その後、通常のフォトリソグラフィ処理とドライエッチング処理を行い、金属配線119を形成する。当該金属配線119は、前記コンタクトホール118を介してnチャネル型TFTに対応するソース領域及びドレイン領域113n、及びpチャネル型TFTに対応するソース領域及びドレイン領域115pに各々接続されている(図3−D参照)。

【0044】

以上の様に、触媒元素を利用した結晶質シリコン膜に対して、ケミカル酸化膜の成膜によるチャネルドープ前処理工程とチャネルドープを適用し、TFTを作製することが可能である。チャネルドープの前処理にケミカル酸化膜の成膜工程を適用する理由は、チャネルドープ時の結晶質シリコン膜のエッチングを防止する効果がある為であるが、結晶質シリコン膜表面のダングリングボンドを酸素等のSi−H結合(≦71.5kcal/mol)より結合エネルギーの大きい元素で終端させることでも、ケミカル酸化膜の成膜と同様のエッチング防止効果が期待される。尚、本実施形態では、触媒元素を利用した結晶質シリコン膜に対して、ケミカル酸化膜の成膜によるチャネルドープ前処理工程とチャネルドープを適用しているが、単なる熱処理のみ(触媒元素利用せず)により結晶化される通常の多結晶シリコン膜に対しても、勿論適用可能である。

【0045】

〔実施形態2〕

本実施形態は、非晶質シリコン膜に対してチャネルドープするTFT作製方法の例を図4〜5に基づき具体的に記載する。此処では、チャネルドープは、nチャネル型TFTに対してのみ行うものとし、また、チャネルドープ後の非晶質シリコン膜結晶化工程は、触媒元素を利用して結晶化する場合について記載する。尚、ゲート絶縁膜の堆積以降の工程(実施形態1の図3に示す工程含む)については、基本的に実施形態1と同一である為、省略する。

【0046】

先ず、ガラス基板201上に膜厚100nmのシリコン酸窒化膜から成る下地膜202をプラズマCVD法により堆積し、続けて膜厚15〜70nm、より好ましくは膜厚30〜60nmの非晶質シリコン膜203を堆積する。本実施形態では、膜厚50nmの非晶質シリコン膜203をプラズマCVD法により堆積した。堆積の際、非晶質シリコン膜203の表面には、空気中の酸素の影響により、自然酸化膜(図示せず)が付いている。尚、本実施形態では、非晶質シリコン膜203を堆積したが、非晶質シリコン膜203以外にも、シリコンを含む非晶質半導体膜、例えばSixGe1-x(0<X<1)の形式で記載されるシリコンとゲルマニウムの化合物から成る非晶質半導体膜を適用することも可能である(図4−A参照)。

【0047】

次に、非晶質シリコン膜203の表面に付いている自然酸化膜(図示せず)を希フッ酸で洗浄し、非晶質シリコン膜203の表面を清浄化する。その後、チャネルドープの前処理として、所定時間のオゾン含有水処理により、非晶質シリコン膜203の表面に5nm以下の極薄のシリコン酸化膜から成るケミカル酸化膜204を成膜する。尚、本実施形態に於いては、ケミカル酸化膜204をオゾン含有水処理により成膜しているが、過酸化水素水による処理で成膜しても良い。また、厳密なケミカル酸化膜ではないけれど、酸素を含む雰囲気中で紫外線(UV)を照射することによっても、ケミカル酸化膜と同様の作用を有する極薄のシリコン酸化膜を成膜することができる(図4−B参照)。

【0048】

また、チャネルドープ工程で使用されるイオンドーピング装置での水素イオン比率が低い場合は、チャネルドープの前処理として、非晶質シリコン膜203表面のダングリングボンドを酸素等のSi−H結合(≦71.5kcal/mol)より結合エネルギーの大きい元素で終端させることも考えられる。

【0049】

次に、非晶質シリコン膜203のnチャネル型TFTに対応する領域を開口領域とする、チャネルドープ用マスクとなるレジストパターン205を形成する。その後、イオンドーピング装置を使用して、前記レジストパターン205をマスクに、非晶質シリコン膜203のnチャネル型TFTに対応する領域にp型不純物であるB元素をドーピングし、チャネルドープを行う。チャネルドープでは、ジボラン(B2H6)ガスを水素で希釈したイオンソースが使用されている。チャネルドープは、通常、ジボラン希釈率0.01〜1.0%、加速電圧1〜50kV、イオン電流10〜500nA、ドーズ量1×1011〜1×1014atoms/cm2のドーピング条件で処理される。尚、本実施形態に於いては、ジボラン希釈率0.1%、加速電圧15kV、イオン電流50nA、ドーズ量4×1013atoms/cm2のチャネルドープ条件でドーピング処理した(図4−B参照)。

【0050】

次に、チャネルドープのマスクとなったレジストパターン205を除去する。その後、非晶質シリコン膜203の表面を清浄化する為、希フッ酸処理により洗浄する。その後、所定時間のオゾン含有水処理により、非晶質シリコン膜203の表面に極薄のシリコン酸化膜から成るケミカル酸化膜206を成膜する。このケミカル酸化膜206は、後にスピン塗布法により添加される触媒元素溶液であるNi水溶液の濡れ性改善を図る為に行われる。尚、本実施形態に於いては、ケミカル酸化膜206は、オゾン含有水処理により成膜しているが、過酸化水素水による処理で成膜しても構わない(図4−C参照)。

【0051】

次に、触媒元素溶液であるNi水溶液をスピン塗布法により、非晶質シリコン膜203(厳密にはケミカル酸化膜206)の全面に添加する。Ni水溶液のNi濃度は、重量換算で0.1〜50ppm、より好ましくは1〜30ppm程度の濃度範囲が好適である。本実施形態では、Ni濃度が10ppmのNi水溶液をスピン塗布法により添加した。スピン塗布の際、基板を回転して、余分なNi水溶液を吹き飛ばして除去し、非晶質シリコン膜203(厳密にはケミカル酸化膜206)の全面に極薄のNi含有層207を成膜する(図4−C参照)。

【0052】

次に、専用の熱処理炉を使用して、窒素雰囲気中で非晶質シリコン膜203を熱処理する。本実施形態に於いては、実施形態1と同様に、プラズマCVD法で膜厚50nmの非晶質シリコン膜203を堆積している為、550℃−4時間の熱処理を行うことにより、縦成長法により結晶質シリコン膜208を成膜した。その後、得られた結晶質シリコン膜208の結晶性を改善させる為、結晶質シリコン膜208に対しレーザー照射を行う。当該レーザー照射により、結晶質シリコン膜208の結晶性は大幅に改善されている。本実施例では、パルス発振型のKrFエキシマレーザー(波長248nm)を適用している。このエキシマレーザーは結晶質シリコン膜208の結晶性の改善のみでなく、Ni元素が非常に移動し易い状態となる為、ゲッタリング源によるゲッタリング効率の向上という作用もある(図4−C参照)。

【0053】

次に、通常のフォトリソグラフィ処理とドライエッチング処理により、結晶質シリコン膜208をパターン形成して、nチャネル型TFTに対応する半導体層209nとpチャネル型TFTに対応する半導体層209pを形成する。その後、前記半導体層209n,209pの表面を清浄化する為、希フッ酸処理により洗浄する。半導体層209n,209pの表面を清浄化した後に、プラズマCVD法又は減圧CVD法により、膜厚100nmのシリコン酸化膜から成るゲート絶縁膜210を堆積する。尚、これ以降のTFT作製工程については、実施形態1と同じである為、省略する(図4−D参照)。

【0054】

[TFTの電気特性評価]

実施形態2のTFT作製工程に基づき、nチャネル型TFTを実際に試作し、電気特性の評価を行った。此処では、電気特性の評価結果について記載する。

【0055】

図5はnチャネル型TFTのID−VG(電流−電圧)特性データーで、8個のnチャネル型TFTを半導体測定装置(4155B)で測定したものである。図5−Aは極薄のシリコン酸化膜から成るケミカル酸化膜の成膜工程が有る場合のデーターで、図5−Bはケミカル酸化膜の成膜工程が無い場合のデーターである。尚、測定したnチャネル型TFTのチャネル長(L)とチャネル幅(W)は、L=7.3μmとW=200μmである。

【0056】

図5から判る様に、ケミカル酸化膜成膜が有る場合には、ID−VG特性のnチャネル型TFT毎のばらつきが小さいのに対し、ケミカル酸化膜成膜が無い場合には、ID−VG特性のばらつきが大きい結果が得られた。ID−VG特性ばらつきの原因としては、チャネルドープ時に非晶質シリコン膜が水素イオンでエッチングされ、非晶質シリコン膜の薄膜化が進行し、コンタクト抵抗のばらつきが起こる為と考えられる。

【0057】

上記のID−VG特性評価結果より、極薄のシリコン酸化膜から成るケミカル酸化膜は、チャネルドープの保護膜として全く問題のないことが認められた。

【0058】

以上の様に、非晶質シリコン膜に対して、ケミカル酸化膜成膜によるチャネルドープ前処理工程とチャネルドープを適用し、優れた電気特性を有するTFTを作製することが可能である。

【0059】

【実施例】

〔実施例1〕

本実施例は、非晶質シリコン膜に対しケミカル酸化膜を成膜するチャネルドープ前処理工程をアクティブマトリクス型液晶表示装置の製造工程に適用した例であり、図6〜10に基づき具体的に記載する。また、チャネルドープ後の非晶質シリコン膜の結晶化工程は、触媒元素を利用して結晶化する場合を記載する。

【0060】

先ず、ガラス基板301上にプラズマCVD法により、各々組成比の異なる第1層目のシリコン酸窒化膜302aを50nmと第2層目のシリコン酸窒化膜302bを100nmの膜厚で堆積し、下地膜302を堆積する。尚、此処で用いるガラス基板301としては、石英ガラスまたはバリウムホウケイ酸ガラスまたはアルミノホウケイ酸ガラス等が有る。次に前記下地膜302(302aと302b)上に、プラズマCVD法により、非晶質シリコン膜303aを55nmの膜厚で堆積する。堆積の際、非晶質シリコン膜303aの表面は、処理雰囲気中に混入した空気中の酸素の影響により極薄の自然酸化膜(図示せず)が付いている。尚、本実施例ではプラズマCVD法で非晶質シリコン膜303aを堆積しているが、減圧CVD法で堆積しても構わない(図6−A参照)。

【0061】

また、非晶質シリコン膜303aの堆積に於いては、空気中に存在する炭素,酸素及び窒素が混入する可能性がある。これらの不純物ガスの混入は、最終的に得られるTFT特性の劣化を引き起こすことが経験的に知られており、このことから前記不純物ガスの混入は結晶化の阻害要因として作用すると本発明者らは認識している。従って、前記不純物ガスの混入は徹底的に排除することが好ましく、具体的な濃度範囲としては、炭素及び窒素の場合は共に5×1017atoms/cm3以下とし、酸素の場合は1×1018atoms/cm3以下とするのが好ましい(図6−A参照)。

【0062】

次に、非晶質シリコン膜303aの表面に付いている自然酸化膜(図示せず)を希フッ酸で洗浄し、非晶質シリコン膜303aの表面を清浄化する。その後、チャネルドープの前処理として、所定時間のオゾン含有水処理により、非晶質シリコン膜303aの表面に5nm以下の極薄のシリコン酸化膜から成るケミカル酸化膜304を成膜する。尚、本実施例に於いては、ケミカル酸化膜304をオゾン含有水処理により成膜しているが、過酸化水素水による処理で成膜しても良い。また、厳密なケミカル酸化膜ではないけれど、酸素を含む雰囲気中で紫外線(UV)を照射することによっても、ケミカル酸化膜と同様の作用を有する極薄のシリコン酸化膜を成膜することができる(図6−A参照)。

【0063】

また、チャネルドープ工程で使用されるイオンドーピング装置での水素イオン比率が低い場合は、チャネルドープの前処理として、非晶質シリコン膜303a表面のダングリングボンドを酸素等のSi−H結合(≦71.5kcal/mol)より結合エネルギーの大きい元素で終端させることも考えられる。

【0064】

次に、非晶質シリコン膜303aのnチャネル型TFT401,403に対応する領域と画素TFT404に対応する領域を開口領域とする、チャネルドープ用マスクとなるレジストパターン305〜308を形成する。その後、イオンドーピング装置を使用して、前記レジストパターン305〜308をマスクにp型不純物であるB元素をドーピングし、第1のイオンドーピング処理であるチャネルドープを行う。チャネルドープでは、ジボラン(B2H6)ガスを水素で希釈したイオンソースが使用されている。チャネルドープは、通常、ジボラン希釈率0.01〜1.0%、加速電圧1〜50kV、イオン電流10〜500nA、ドーズ量1×1011〜1×1014atoms/cm2のドーピング条件で処理される。尚、本実施例に於いては、ジボラン希釈率0.1%、加速電圧15kV、イオン電流50nA、ドーズ量4×1013atoms/cm2のチャネルドープ条件でドーピング処理した(図6−A参照)。

【0065】

次に、チャネルドープのマスクとなったレジストパターン305〜308を除去する。その後、非晶質シリコン膜303aの表面を清浄化する為、希フッ酸処理により洗浄する。その後、所定時間のオゾン含有水処理により、非晶質シリコン膜303aの表面に極薄のシリコン酸化膜から成るケミカル酸化膜(図示せず)を成膜する。このケミカル酸化膜(図示せず)は、後にスピン塗布法により添加される触媒元素溶液であるNi水溶液の濡れ性改善を図る為に行われる。尚、本実施例に於いては、ケミカル酸化膜(図示せず)は、オゾン含有水処理により成膜しているが、過酸化水素水による処理成膜しても構わない(図6−B参照)。

【0066】

次に、非晶質シリコン膜303aの全面に、結晶化の助長作用を有する触媒元素溶液であるNi水溶液を添加する。具体的には、Ni化合物であるニッケル酢酸塩を純水に溶解し、重量換算で10ppmの濃度に調整したNi水溶液をスピン処理法により添加する(図6−B参照)。

【0067】

次に、非晶質シリコン膜303a中の含有水素量を5atom%以下に制御する為、当該基板を電熱炉内の窒素雰囲気中で450℃−1時間の条件で熱処理し、非晶質シリコン膜303a中の含有水素の脱水素化処理を行う(図6−B参照)。

【0068】

次に、電熱炉に於いて、550℃−4時間の条件で熱処理することにより、非晶質シリコン膜303aの結晶化を行い、結晶質シリコン膜303bを成膜する。その後、得られた結晶質シリコン膜303bの結晶性を改善させる為、結晶質シリコン膜303bに対しレーザー照射を行う。当該レーザー照射により、結晶質シリコン膜303bの結晶性は大幅に改善される。本実施例では、パルス発振型のKrFエキシマレーザー(波長248nm)を適用している。このエキシマレーザーは結晶質シリコン膜303bの結晶性の改善のみでなく、Ni元素が非常に移動し易い状態となる為、ゲッタリング源によるゲッタリング効率の向上という作用も有している(図6−B参照)。

【0069】

次に、通常のフォトリソグラフィ処理及びドライエッチング処理により、結晶質シリコン膜303bをパターン形成し、TFTのチャネル領域及びソース領域及びドレイン領域と成る半導体層309〜313を形成する(図7−A参照)。

【0070】

次に、前記半導体層309〜313を覆う様に、プラズマCVD法により膜厚100nmのシリコン酸窒化膜から成るゲート絶縁膜314を堆積する。尚、ゲート絶縁膜314の堆積の際、半導体層309〜313の表面を清浄化する為、希フッ酸処理により洗浄する。その後、ゲート絶縁膜314上にゲート電極材料である導電性膜をスパッタ法又はCVD法により堆積する。此処で適用されるゲート電極材料としては、後の不純物元素の活性化を兼ねたゲッタリング用の熱処理温度(550〜650℃程度)に耐え得る耐熱性材料が好ましい。耐熱性材料としては、例えばTa(タンタル),Mo(モリブデン),Ti(チタン),W(タングステン),Cr(クロム)等の高融点金属、及び高融点金属とシリコンの化合物である金属シリサイド、及びn型又はp型の導電型を有する多結晶シリコン等が挙げられる。尚、本実施例では、膜厚400nmのW膜から成るゲート電極膜315をスパッタ法により堆積した(図7−B参照)。

【0071】

上記構造の基板上に、ゲート電極形成用のフォトリソグラフィ処理とドライエッチング処理を行うことにより、ゲート電極322〜325と保持容量用電極326とソース配線として機能する電極327を形成する。ドライエッチングの後、ゲート電極322〜325上にはドライエッチングのマスクであるレジストパターン316〜319が残膜し、同様に保持容量用電極326上にレジストパターン320とソース配線として機能する電極327上にレジストパターン321が残膜している。尚、ドライエッチングに伴い、下地のシリコン酸窒化膜から成るゲート絶縁膜314は膜減りにより、ゲート絶縁膜328の形状に変形している(図8−A参照)。

【0072】

次に、レジストパターン316〜321を残した状態で、ゲート電極322〜325と保持容量用電極326をマスクに、イオンドーピング装置を用いて、第2のイオンドーピング処理である低濃度n型不純物のドーピングを行う。当該イオンドーピング処理は、n型不純物であるP元素を用い、加速電圧10〜100kV、ドーズ量3×1012〜3×1013atoms/cm2の条件で処理される。この第2のイオンドーピング処理により、ゲート電極322〜325と保持容量用電極326の外側に対応する半導体層309〜313に、n型不純物の低濃度不純物領域(n−領域)334〜338が形成される。同時に、ゲート電極322〜325の真下には、TFTのチャネルとして機能する実質的に真性な領域329〜332が形成される。また、保持容量用電極326の真下の半導体層313には、当該領域がTFT形成領域でなく、保持容量405の形成領域である為、容量形成用電極の片側として機能する真性な領域333が形成される(図8−A参照)。

【0073】

次に、当該基板を専用の剥離液で洗浄することにより、ドライエッチングのマスクとなったレジストパターン316〜321を除去する。除去した後、駆動回路406に於けるnチャネル型TFT401,403と画素領域407に於ける画素TFT404をLDD構造にする為、当該領域に存在するゲート電極322,324〜325を被覆する様に、第3のイオンドーピング処理のマスクとなるn+領域形成用のレジストパターン339〜341を形成する。そして、第3のイオンドーピング処理である高濃度n型不純物のドーピングを行う。当該イオンドーピング処理は、加速電圧10〜100kV、ドーズ量1×1014〜1×1016atoms/cm2の条件でドーピング処理される。尚、本実施形態に於いては、加速電圧80kV、ドーズ量1.7×1015atoms/cm2の条件でドーピング処理した。当該イオンドーピング処理により、前記レジストパターン339〜341の外側領域に対応する半導体層309,311〜312にn型不純物の高濃度不純物領域(n+領域)342,344〜345が形成される。この高濃度不純物領域(n+領域)342,344〜345の形成に伴い、既に形成した低濃度不純物領域(n−領域)334,336〜337は、高濃度不純物領域(n+領域)342,344〜345と低濃度不純物領域(n−領域)347〜349に分離され、LDD構造となるソース領域及びドレイン領域が形成される(図8−B参照)。

【0074】

この際、LDD構造形成領域以外の領域である駆動回路406のpチャネル型TFT402の領域と画素領域407の保持容量405の領域に於いては、ゲート電極323と保持容量用電極326をマスクに各々イオンドーピングされる為、ゲート電極323の外側領域に対応する半導体層310にn型不純物の高濃度不純物領域(n+領域)343が形成され、保持容量用電極326の外側領域に対応する半導体層313にもn型不純物の高濃度不純物領域(n+領域)346が形成されている(図8−B参照)。

【0075】

次に、通常のフォトリソグラフィ処理により、pチャネル型TFT402に対応する半導体層310の領域と保持容量405に対応する半導体層313の領域を開口領域とするレジストパターン350〜352を形成する。その後、前記レジストパターン350〜352をマスクに、イオンドーピング装置を用いて、第4のイオンドーピング処理である高濃度p型不純物のドーピングを行う。当該イオンドーピング処理により、pチャネル型TFT402に対応する半導体層310には、ゲート電極323をマスクにp型不純物であるB元素がイオン注入される。この結果、ゲート電極323の外側領域に対応する半導体層310に、p型の導電型を有する高濃度不純物領域(p+領域)353が形成される。前記高濃度不純物領域(p+領域)353には、既にn型不純物であるP元素がドーピングされているが、B元素のドーズ量が2.5×1015atoms/cm2となる様に高濃度にドーピングされる為、p型の導電型を有し、ソース領域及びドレイン領域として機能する高濃度不純物領域(p+領域)353が形成される。また、保持容量405の形成領域に於いても、保持容量用電極326の外側領域に対応する半導体層313にp型の導電型を有する高濃度不純物領域(p+領域)354が同様に形成される(図9−A参照)。

【0076】

次に、前記レジストパターン350〜352を除去した後、膜厚150nmのシリコン酸窒化膜から成る第1の層間絶縁膜355をプラズマCVD法により堆積する。その後、半導体層309〜313にドーピングされた不純物イオン(P元素とB元素)の熱活性化の為、電熱炉に於いて、600℃−12時間の熱処理を行う。当該熱処理は不純物イオンの熱活性化処理の為に行うものであるが、チャネル領域として機能する実質的に真性な領域329〜332及び容量形成用電極の片側として機能する真性な領域333に存在するNi元素を前記不純物イオンによりゲッタリングする目的も兼ねている。尚、前記熱活性化処理を第1の層間絶縁膜355の堆積前に行っても良いが、ゲート電極等の配線材料の耐熱性が弱い場合は、第1の層間絶縁膜355の堆積後に行う方が好ましい。その後、半導体層309〜313のダングリングボンドを終端させる為、410℃−1時間の水素化処理を水素3%含有の窒素雰囲気中で行う(図9−B参照)。

【0077】

次に、前記第1の層間絶縁膜355の上に、膜厚1.6μmのアクリル樹脂膜から成る第2の層間絶縁膜356を成膜する。その後、通常のフォトリソグラフィ処理とドライエッチング処理により、第2の層間絶縁膜356と第1の層間絶縁膜355、更に下層膜であるゲート絶縁膜328を貫通する様に、コンタクトホールを形成する。この際、コンタクトホールは、ソース配線として機能する電極327及び高濃度不純物領域342,344〜345,353〜354と接続する様に形成される(図10−A参照)。

【0078】

次に、駆動回路406の高濃度不純物領域342,344,353と電気的に接続する様に、導電性の金属配線357〜362を形成する。また、画素領域407の接続電極363,365〜366とゲート配線364を同じ導電性材料で形成する。本実施例では、金属配線357〜362、接続電極363,365〜366及びゲート配線364の構成材料として、膜厚50nmのTi膜と膜厚500nmのAl−Ti合金膜の積層膜を適用している。そして、接続電極363は、不純物領域345とソース配線として機能する電極327とを電気的に接続する様に形成されている。接続電極365は、画素TFT404の不純物領域345と電気的に接続する様に形成されており、接続電極366は保持容量405の不純物領域354と電気的に接続する様に形成されている。また、ゲート配線364は、画素TFT404の複数のゲート電極325を電気的に接続する様に形成されている。その後、膜厚80〜120nmのITO(Indium-Ti-Oxide)等の透明導電膜を堆積した後、フォトリソグラフィ処理とエッチング処理により、画素電極367を形成する。画素電極367は、接続電極365を介して、画素TFT404のソース領域及びドレイン領域である不純物領域345と電気的に接続されており、更に接続電極366を介して、保持容量405の不純物領域354とも電気的に接続されている(図10−B参照)。

【0079】

以上の様に、LDD構造のnチャネル型TFTとシングルドレイン構造のpチャネル型TFTを有するアクティブマトリクス型液晶表示装置の製造工程に、ケミカル酸化膜成膜によるチャネルドープ前処理工程を適用することが可能である。尚、チャネルドープ前処理工程に於けるケミカル酸化膜の適用は、チャネルドープ工程での処理能力の増強及び生産原価の低減に有利である。

【0080】

〔実施例2〕

本発明は、TFTで回路構成される半導体装置の作製方法に関するものであり、様々なアクティブマトリクス型の半導体表示装置、例えば液晶表示装置及びEL表示装置の製造に本発明を適用することが可能である。従って、本発明は、様々な分野のアクティブマトリクス型の半導体表示装置(液晶表示装置及びEL表示装置)を組み込んだ電子機器の製造)に適用可能であり、此処では電子機器の具体例を図11〜13に基づき記載する。尚、電子機器としては、ビデオカメラとデジタルカメラとプロジェクター(リア型またはフロント型)とヘッドマウントディスプレイ(ゴーグル型ディスプレイ)とゲーム機とカーナビゲーションとパーソナルコンピュータと携帯情報端末(モバイルコンピュータ,携帯電話,電子書籍等)等が挙げられる。

【0081】

図11−Aは、本体1001と映像入力部1002と表示装置1003とキーボード1004で構成されたパーソナルコンピューターである。本発明を表示装置1003及び他の回路に適用することができる。

【0082】

図11−Bはビデオカメラであり、本体1101と表示装置1102と音声入力部1103と操作スイッチ1104とバッテリー1105と受像部1106で構成される。本発明を表示装置1102及び他の回路に適用することができる。

【0083】

図11−Cはモバイルコンピュータ(モービルコンピュータ)であり、本体1201とカメラ部1202と受像部1203と操作スイッチ1204と表示装置1205で構成される。本発明を表示装置1205及び他の回路に適用することができる。

【0084】

図11−Dはゴーグル型ディスプレイであり、本体1301と表示装置1302とアーム部1303で構成される。本発明を表示装置1302及び他の回路に適用することができる。

【0085】

図11−Eはプログラムを記録した記録媒体(以下、記録媒体と略記)に用いるプレーヤーであり、本体1401と表示装置1402とスピーカー部1403と記録媒体1404と操作スイッチ1405で構成される。尚、この装置は記録媒体としてDVD及びCD等が用いられ、音楽鑑賞またはゲームまたはインターネットに利用可能である。本発明を表示装置1402及び他の回路に適用することができる。

【0086】

図11−Fは携帯電話であり、表示用パネル1501と操作用パネル1502と接続部1503と表示部1504と音声出力部1505と操作キー1506と電源スイッチ1507と音声入力部1508とアンテナ1509で構成される。表示用パネル1501と操作用パネル1502は、接続部1503で接続されている。表示用パネル1501の表示部1504が設置されている面と操作用パネル1502の操作キー1506が設置されている面との角度θは、接続部1503に於いて任意に変えることができる。本発明を表示部1504に適用することができる。

【0087】

図12−Aはフロント型プロジェクターであり、光源光学系及び表示装置1601とスクリーン1602で構成される。本発明を表示装置1601及び他の回路に適用することができる。

【0088】

図12−Bはリア型プロジェクターであり、本体1701と光源光学系及び表示装置1702とミラー1703〜1704とスクリーン1705で構成される。本発明を表示装置1702及び他の回路に適用することができる。

【0089】

尚、図12−Cは、図12−Aの光源光学系及び表示装置1601と図12−Bの光源光学系及び表示装置1702に於ける構造の一例を示した図である。光源光学系及び表示装置1601,1702は、光源光学系1801とミラー1802,1804〜1806とダイクロイックミラー1803と光学系1807と表示装置1808と位相差板1809と投射光学系1810で構成される。投射光学系1810は、投射レンズを備えた複数の光学レンズで構成される。この構成は、表示装置1808を3個使用している為、三板式と呼ばれている。また同図の矢印で示した光路に於いて、実施者は光学レンズ及び偏光機能を有するフィルムまたは位相差を調整する為のフィルムまたはIRフィルム等を適宜に設けても良い。

【0090】

図12−Dは、図12−Cに於ける光源光学系1801の構造の一例を示した図である。本実施例に於いては、光源光学系1801はリフレクター1811と光源1812とレンズアレイ1813〜1814と偏光変換素子1815と集光レンズ1816で構成される。尚、同図に示した光源光学系は一例であり、この構成に限定されない。例えば、実施者は光源光学系に光学レンズ及び偏光機能を有するフィルムまたは位相差を調整するフィルムまたはIRフィルム等を適宜に設けても良い。

【0091】

次の図13−Aは、単板式の例を示したものである。同図に示した光源光学系及び表示装置は、光源光学系1901と表示装置1902と投射光学系1903と位相差板1904で構成される。投射光学系1903は、投射レンズを備えた複数の光学レンズで構成される。同図に示した光源光学系及び表示装置は図12−Aと図12−Bに於ける光源光学系及び表示装置1601,1702に適用できる。また光源光学系1901は図12−Dに示した光源光学系を用いれば良い。尚、表示装置1902にはカラーフィルター(図示しない)が設けられており、表示映像をカラー化している。

【0092】

図13−Bに示した光源光学系及び表示装置は、図13−Aの応用例であり、カラーフィルターを設ける代わりに、RGBの回転カラーフィルター円板1905を用いて表示映像をカラー化している。同図に示した光源光学系及び表示装置は図12−Aと図12−Bに於ける光源光学系及び表示装置1601,1702に適用できる。

【0093】

図13−Cに示した光源光学系及び表示装置は、カラーフィルターレス単板式と呼ばれている。この方式は、表示装置1916にマイクロレンズアレイ1915を設け、ダイクロイックミラー(緑)1912とダイクロイックミラー(赤)1913とダイクロイックミラー(青)1914を用いて表示映像をカラー化している。投射光学系1917は、投射レンズを備えた複数の光学レンズで構成される。同図に示した光源光学系及び表示装置は、図12−Aと図12−Bに於ける光源光学系及び表示装置1601,1702に適用できる。また光源光学系1911としては、光源の他に結合レンズ及びコリメーターレンズを用いた光学系を用いれば良い。

【0094】

以上の様に、本発明の半導体装置の作製方法は、その適用範囲が極めて広く、本発明は様々な分野のアクティブマトリクス型の液晶表示装置及びEL表示装置を組み込んだ電子機器に適用可能である。

【0095】

【発明の効果】

本発明は、TFTで回路構成される半導体装置の作製方法に関し、特にTFT活性層等のシリコン系半導体膜へ不純物イオンをドーピングする際の前処理に関するもので、以下の効果を有している。

【0096】

(効果1)イオンドーピング工程の前処理として、ケミカル酸化膜成膜等の簡便な前処理工程を適用することにより、イオンドーピング工程全体のスループットの向上に有効である。

(効果2)イオンドーピング工程の前処理に高価格なプラズマCVD装置や減圧CVD装置が不要となる為、生産原価の低減に有効である。

【図面の簡単な説明】

【図1】 非晶質シリコン残膜厚のドーズ量依存性を示す実験データーである。

【図2】 TFTの作製工程を示す断面図である。

【図3】 TFTの作製工程を示す断面図である。

【図4】 TFTの作製工程を示す断面図である。

【図5】 nチャネル型TFTのID−VG(電流−電圧)特性データーである。

【図6】 アクティブマトリクス型液晶表示装置の製造工程を示す断面図である。

【図7】 アクティブマトリクス型液晶表示装置の製造工程を示す断面図である。

【図8】 アクティブマトリクス型液晶表示装置の製造工程を示す断面図である。

【図9】 アクティブマトリクス型液晶表示装置の製造工程を示す断面図である。

【図10】アクティブマトリクス型液晶表示装置の製造工程を示す断面図である。

【図11】半導体表示装置を組み込んだ電子機器の例を示す装置概略図である。

【図12】半導体表示装置を組み込んだ電子機器の例を示す装置概略図である。

【図13】半導体表示装置を組み込んだ電子機器の例を示す装置概略図である。

Claims (18)

- 絶縁性基板上にシリコンを含む半導体膜を成膜し、

前記半導体膜の表面にケミカル酸化膜を成膜し、

前記半導体膜に対して不純物イオンをイオンドーピング法を用いてドーピングすることを特徴とする半導体装置の作製方法。 - 絶縁性基板上にシリコンを含む半導体膜を成膜し、

前記半導体膜をオゾン含有水で処理することによって前記半導体膜の表面に酸化膜を成膜し、

前記半導体膜に対して不純物イオンをイオンドーピング法を用いてドーピングすることを特徴とする半導体装置の作製方法。 - 絶縁性基板上にシリコンを含む半導体膜を成膜し、

前記半導体膜を過酸化水素水で処理することによって前記半導体膜の表面に酸化膜を成膜し、

前記半導体膜に対して不純物イオンをイオンドーピング法を用いてドーピングすることを特徴とする半導体装置の作製方法。 - 絶縁性基板上にシリコンを含む半導体膜を成膜し、

前記半導体膜に酸素を含む雰囲気中で紫外線を照射することによって前記半導体膜の表面に酸化膜を成膜し、

前記半導体膜に対して不純物イオンをイオンドーピング法を用いてドーピングすることを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項4のいずれか一項において、

前記シリコンを含む半導体膜として、非晶質半導体膜を成膜することを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項5のいずれか一項において、

前記シリコンを含む半導体膜として、非晶質半導体膜を成膜し、前記非晶質半導体膜を熱処理して多結晶半導体膜を成膜することを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項5のいずれか一項において、

前記シリコンを含む半導体膜として、非晶質半導体膜を成膜し、前記非晶質半導体膜に結晶化の助長作用を有する触媒元素を添加し、前記非晶質半導体膜を熱処理して結晶質半導体膜を成膜することを特徴とする半導体装置の作製方法。 - 請求項7において、

前記触媒元素として、Fe、Co、Ni、Ru、Rh、Pd、Os、Ir、Pt、Cu、Auから選択された少なくとも一つの元素を添加することを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項8のいずれか一項において、

前記不純物イオンとして、イオン源に水素を含む材料を使用することを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項9のいずれか一項において、

前記不純物イオンをイオンドーピング法を用いてドーピングすることによりチャネルドープを行うことを特徴とする半導体装置の作製方法。 - 絶縁性基板上にシリコンを含む非晶質半導体膜を成膜し、

前記非晶質半導体膜の表面にケミカル酸化膜を成膜し、

前記非晶質半導体膜に対して不純物イオンをイオンドーピング法を用いてドーピングし、

前記非晶質半導体膜を熱処理して多結晶半導体膜を形成し、

前記多結晶半導体膜をパターニングすることによってTFTのチャネル領域、ソース領域及びドレイン領域となる半導体層を形成し、

前記半導体層上にゲート絶縁膜を介してゲート電極を形成し、

前記ゲート電極をマスクとして、前記半導体層に不純物イオンをイオンドーピング法を用いてドーピングすることを特徴とする半導体装置の作製方法。 - 絶縁性基板上にシリコンを含む非晶質半導体膜を成膜し、

前記非晶質半導体膜を熱処理して多結晶半導体膜を形成し、

前記多結晶半導体膜の表面にケミカル酸化膜を成膜し、

前記多結晶半導体膜に対して不純物イオンをイオンドーピング法を用いてドーピングし、

前記多結晶半導体膜をパターニングすることによってTFTのチャネル領域、ソース領域及びドレイン領域となる半導体層を形成し、

前記半導体層上にゲート絶縁膜を介してゲート電極を形成し、

前記ゲート電極をマスクとして、前記半導体層に不純物イオンをイオンドーピング法を用いてドーピングすることを特徴とする半導体装置の作製方法。 - 絶縁性基板上にシリコンを含む非晶質半導体膜を成膜し、

前記非晶質半導体膜の表面にケミカル酸化膜を成膜し、

前記非晶質半導体膜に対して不純物イオンをイオンドーピング法を用いてドーピングし、

前記非晶質半導体膜に結晶化の助長作用を有する触媒元素を添加し、熱処理により結晶質半導体膜を形成し、

前記結晶質半導体膜をパターニングすることによってTFTのチャネル領域、ソース領域及びドレイン領域となる半導体層を形成し、

前記半導体層上にゲート絶縁膜を介してゲート電極を形成し、

前記ゲート電極をマスクとして、前記半導体層に不純物イオンをイオンドーピング法を用いてドーピングすることを特徴とする半導体装置の作製方法。 - 絶縁性基板上にシリコンを含む非晶質半導体膜を成膜し、

前記非晶質半導体膜に結晶化の助長作用を有する触媒元素を添加し、熱処理により結晶質半導体膜を形成し、

前記結晶質半導体膜の表面にケミカル酸化膜を成膜し、

前記結晶質半導体膜に対して不純物イオンをイオンドーピング法を用いてドーピングし、

前記結晶質半導体膜をパターニングすることによってTFTのチャネル領域、ソース領域及びドレイン領域となる半導体層を形成し、

前記半導体層上にゲート絶縁膜を介してゲート電極を形成し、

前記ゲート電極をマスクとして、前記半導体層に不純物イオンをイオンドーピング法を用いてドーピングすることを特徴とする半導体装置の作製方法。 - 請求項13または請求項14において、

前記触媒元素として、Fe、Co、Ni、Ru、Rh、Pd、Os、Ir、Pt、Cu、Auから選択された少なくとも一つの元素を添加することを特徴とする半導体装置の作製方法。 - 請求項11乃至請求項15のいずれか一項において、

前記ケミカル酸化膜は、前記半導体膜をオゾン含有水で処理することによって成膜されることを特徴とする半導体装置の作製方法。 - 請求項11乃至請求項15のいずれか一項において、

前記ケミカル酸化膜は、前記半導体膜を過酸化水素水で処理することによって成膜されることを特徴とする半導体装置の作製方法。 - 請求項11乃至請求項15のいずれか一項において、

前記ケミカル酸化膜は、前記半導体膜に酸素を含む雰囲気中で紫外線を照射することによって成膜されることを特徴とする半導体装置の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002019256A JP3942902B2 (ja) | 2001-01-26 | 2002-01-28 | 半導体装置の作製方法 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001019293 | 2001-01-26 | ||

| JP2001-19293 | 2001-01-26 | ||

| JP2002019256A JP3942902B2 (ja) | 2001-01-26 | 2002-01-28 | 半導体装置の作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002313809A JP2002313809A (ja) | 2002-10-25 |

| JP2002313809A5 JP2002313809A5 (ja) | 2005-08-04 |

| JP3942902B2 true JP3942902B2 (ja) | 2007-07-11 |

Family

ID=26608391

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002019256A Expired - Lifetime JP3942902B2 (ja) | 2001-01-26 | 2002-01-28 | 半導体装置の作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3942902B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20050287307A1 (en) * | 2004-06-23 | 2005-12-29 | Varian Semiconductor Equipment Associates, Inc. | Etch and deposition control for plasma implantation |

| JP2007294082A (ja) * | 2006-03-31 | 2007-11-08 | Semiconductor Energy Lab Co Ltd | Nand型不揮発性メモリのデータ消去方法 |

-

2002

- 2002-01-28 JP JP2002019256A patent/JP3942902B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2002313809A (ja) | 2002-10-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7361577B2 (en) | Method of manufacturing semiconductor device | |

| KR100913929B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| KR100659921B1 (ko) | 반도체 장치 및 그의 제조 방법 | |

| US8420546B2 (en) | Manufacturing method of semiconductor device | |

| KR100515279B1 (ko) | 반도체 장치 및 그 제조방법 | |

| JP5244885B2 (ja) | 半導体装置の作製方法 | |

| JP4024508B2 (ja) | 半導体装置の作製方法 | |

| JP4667523B2 (ja) | 半導体装置及びその作製方法 | |

| US20030155594A1 (en) | Semiconductor display device and manufacturing method method thereof | |

| JP4376331B2 (ja) | 半導体装置の作製方法 | |

| KR100631349B1 (ko) | 반도체막과 그의 제조방법, 반도체장치 및 그의 제조방법 | |

| JP4115153B2 (ja) | 半導体装置の製造方法 | |

| JP4056720B2 (ja) | 結晶質半導体膜の作製方法 | |

| KR100929988B1 (ko) | 반도체 디바이스 제조 방법 | |

| JP4450900B2 (ja) | 半導体装置の作製方法 | |

| JP3942902B2 (ja) | 半導体装置の作製方法 | |

| JP4801242B2 (ja) | 半導体装置の作製方法 | |

| JP4514862B2 (ja) | 半導体装置の作製方法 | |

| JP4080168B2 (ja) | 半導体装置の作製方法 | |

| JP4127467B2 (ja) | 半導体装置の作製方法 | |

| JP4137555B2 (ja) | 半導体装置の作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050112 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050112 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20061212 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20061219 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070129 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070220 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070307 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20070403 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20070404 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 3942902 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100413 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100413 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110413 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110413 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120413 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130413 Year of fee payment: 6 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130413 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140413 Year of fee payment: 7 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |