JP3859618B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP3859618B2 JP3859618B2 JP2003132849A JP2003132849A JP3859618B2 JP 3859618 B2 JP3859618 B2 JP 3859618B2 JP 2003132849 A JP2003132849 A JP 2003132849A JP 2003132849 A JP2003132849 A JP 2003132849A JP 3859618 B2 JP3859618 B2 JP 3859618B2

- Authority

- JP

- Japan

- Prior art keywords

- present

- semiconductor

- semiconductor device

- conductive layer

- semiconductor chip

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Description

【発明の属する技術分野】

この発明はμBGA(μBall Grid Array)型半導体装置に関し、特に、積み重ね可能なμBGA型半導体装置に関するものである。

【0002】

【従来の技術】

図13は従来のμBGA型半導体装置の断面構造図を示す。図13に示すように、従来のμBGA型半導体装置1300は、主表面に複数の外部端子1304を有する集積回路が形成された半導体チップ1301と、 導電層1310、およびこの導電層1310を絶縁層1309、および絶縁層1313で挟む構造からなるテープ1308とから構成される。ここで、例えば導電層1310はCu、絶縁層1309はポリイミドやガラスエポキシ、絶縁層1313はソルダーレジストから構成される。

【0003】

また、半導体チップ1301の主表面は、パッシベーション膜1305で覆われている。

【0004】

さらに、導電層1310は、複数の外部端子1304と電気的に接続され、かつ、絶縁層1313に形成された開口部1303aから露出される。

【0005】

さらに、テープ1308は、緩衝膜1307、例えばエラストマーを介して、パッシベーション膜1305上に固着されている。

【0006】

そして、導電層1310と外部端子1304との接続部は、樹脂1302で覆われている。

【0007】

【発明が解決しようとする課題】

しかしながら、従来のμBGA型半導体装置は、外部装置、例えば他の半導体装置と電気的に接続可能な接続部、つまり開口部1303aから露出する導電層1310が半導体チップ1301の主表面のみに形成された構造となっているので、複数の半導体装置を積み重ねて実装することが困難であった。

【0008】

本発明は、複数の半導体装置の積み重ね実装を容易にする半導体装置及び半導体モジュ−ルを提供することを目的とする。

【0009】

【課題を解決するための手段】

そこで本発明の半導体装置は、 主表面に複数の外部端子を有する集積回路が形成された半導体チップと、半導体チップの主表面から半導体チップの裏面まで延在し、かつ半導体チップの主表面側及び裏面側の夫々で半導体チップと固着されるテ−プとを有し、テ−プは、導電層と、この導電層を挟む絶縁層とからなり、かつ導電層と複数の外部端子とが電気的に接続され、かつ半導体チップの主表面及び裏面の夫々に位置する絶縁層に導電層を露出する開口部を夫々に有することを特徴とする。

【0010】

また、本発明の半導体モジュールは、 主表面に複数の外部端子を有する集積回路が形成された半導体チップと、半導体チップの主表面から半導体チップの裏面まで延在し、かつ半導体チップの主表面側及び裏面側の夫々で半導体チップと固着されるテ−プとを有し、テ−プは、導電層と、この導電層を挟む絶縁層とからなり、かつ導電層と複数の外部端子とが電気的に接続され、かつ半導体チップの主表面及び裏面の夫々に位置する絶縁層に導電層を露出する開口部を有する第1の半導体装置と、前記開口部で露出する前記導電層表面と電気的に接続されているパッドを有する第2の半導体装置とを有することを特徴とする。

【0011】

【発明の実施の形態】

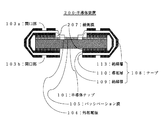

図1は本発明の第1の実施の形態の半導体装置について説明するための断面図である。以下、図1を用いて本発明の第1の実施の形態の半導体装置について説明する。

【0012】

この半導体装置100は、主表面に複数の外部端子104を有する集積回路を形成された半導体チップ101と、導電層110、およびこの導電層110を絶縁層109、および113で挟む構造からなるテープ108とから構成される。ここで、例えば導電層110はCu、絶縁層109はポリイミドやガラスエポキシ、絶縁層113はソルダーレジストなどから構成される。

【0013】

また、半導体チップ101の主表面は、パッシベーション膜105で覆われている。

【0014】

テープ108は、半導体チップ101の主表面から裏面まで延在し、かつ半導体チップ101の主表面側および裏面側の夫々で半導体チップ101と固着されている。

【0015】

さらに、導電層110は、複数の外部端子104と電気的に接続され、かつ、半導体チップ101の主表面および裏面の夫々に位置する絶縁層113に形成された開口部103aおよび103bから露出されている。

【0016】

上述した通り、本発明の第1の実施の形態の半導体装置100では、第1に、半導体装置100の主表面側に開口部103a、裏面側に開口部103bを有するので、開口部103aから露出する導電層110、もしくは、開口部103bから露出する導電層110、もしくは、これら両方と、外部装置、例えば他の半導体装置と電気的に接続できる。つまり、複数の半導体装置の積み重ね実装を容易にすることができる。第2に、開口部103aから露出する導電層110、もしくは、開口部103bから露出する導電層110の一方が他の半導体装置との接続に用いる場合、他方は半導体装置100自身の電気的テストに用いることができる。

【0017】

本発明の第1の実施の形態の半導体装置において、開口部103aおよび開口部103bから夫々露出する導電層110は、金属バンプなどを介して、他の半導体装置などと接続することができる。この場合は、絶縁層113にソルダーレジストなどの、溶かした金属に対して濡れ性が低い絶縁層を用いると、金属バンプを正確に取りつけることができる。

【0018】

さらに、テープ108の代わりに、フレキシブルテープを用いてもよい。

【0019】

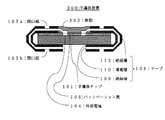

図2は本発明の第2の実施の形態の半導体装置について説明するための断面図である。以下、図2を用いて本発明の第2の実施の形態の半導体装置について説明する。

【0020】

この半導体装置200は、本発明の第1の実施の形態の半導体装置100とほぼ同様の構成のため、詳しい説明は省略する。本実施の形態は、本発明の第1の実施の形態の半導体装置100において、テープ108は、緩衝膜207、例えばエラストマーを介在して半導体チップ101と固着することを特徴とする。

【0021】

本発明の第2の実施の形態の半導体装置200は、本発明の第1の実施の形態の半導体装置100と同様の効果を奏することは言うまでもない。さらに、上記のようにテープ108は緩衝膜207を介在して半導体チップ101と固着されている。緩衝膜207は熱収縮率の差により、テープ108が半導体チップ101から剥がれるのを防ぐように働く。したがって、本発明の第1の実施の形態の半導体装置100の構造に比して、よりテープ108と半導体チップ101が、剥がれにくい構造が得られる。

【0022】

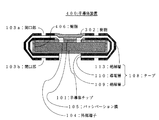

図3は本発明の第3の実施の形態の半導体装置について説明するための断面図である。以下、図3を用いて本発明の第3の実施の形態の半導体装置について説明する。

【0023】

この半導体装置300は、本発明の第1の実施の形態の半導体装置100とほぼ同様の構成のため、詳しい説明は省略する。本実施の形態は、本発明の第1の実施の形態の半導体装置100において、導電層110と外部端子104との接続部が樹脂302で覆われていることを特徴とする。

【0024】

本発明の第3の実施の形態の半導体装置300は、本発明の第1の実施の形態の半導体装置100と同様の効果を奏することは言うまでもない。さらに、上記のように導電層110と外部端子104との接続部が樹脂302で覆われている。このため、本発明の第1の実施の形態の半導体装置100の構造に比して、外部端子104と導電層110が剥がれにくい、堅固な構造を得ることができる。

【0025】

図4は本発明の第4の実施の形態の半導体装置について説明するための断面図である。以下、図4を用いて本発明の第4の実施の形態の半導体装置について説明する。

【0026】

この半導体装置400は、本発明の第1の実施の形態の半導体装置100とほぼ同様の構成のため、詳しい説明は省略する。本実施の形態は、本発明の第1の実施の形態の半導体装置100において、導電層110と外部端子104との接続部を樹脂302が覆い、さらには半導体チップ101の側面および裏面を、樹脂406が夫々覆うことを特徴とする。

【0027】

本発明の第4の実施の形態の半導体装置400は、本発明の第1の実施の形態の半導体装置100と同様の効果を奏することは言うまでもない。さらに、上記のように導電層110と外部端子104との接続部を樹脂302が覆い、さらには半導体チップ101の側面および裏面を、樹脂406が夫々覆っている。このため、本発明の第1の実施の形態の半導体装置100の構造に比して、半導体チップ101の主表面方向からの外力に対してより強い、堅固な構造を得ることができる。

【0028】

図5は本発明の第1の実施の形態の半導体モジュールについて説明するための断面図である。以下、図5を用いて本発明の第1の実施の形態の半導体モジュールについて説明する。

【0029】

この半導体モジュール500は、第1の半導体装置500a、及び第2の半導体装置500bから構成される。ここで、第2の半導体装置500bは、第1の半導体装置500aと同一の構成であるため、第2の半導体装置500bの説明は、第1の半導体装置500aの説明により省略する。

【0030】

この半導体装置500aは、主表面に複数の外部端子504aを有する集積回路を形成された半導体チップ501aと、導電層510a、およびこの導電層510aを絶縁層509a、513aで挟む構造からなるテープ508aとから構成される。ここで、例えば導電層510aはCu、絶縁層509aはポリイミドやガラスエポキシ、絶縁層513aはソルダーレジストから構成される。

【0031】

また、半導体チップ501aの主表面は、パッシベーション膜505aで覆われている。

【0032】

テープ508aは、半導体チップ501aの主表面から裏面まで延在し、かつ半導体チップ501aの主表面側および裏面側の夫々で半導体チップ501aと固着されている。

【0033】

さらに、導電層510aは、複数の外部端子504aと電気的に接続され、かつ、半導体チップ501aの主表面および裏面の夫々に位置する絶縁層513aに形成された開口部523aおよび533aから露出されている。

【0034】

上述したように本発明の第1の実施の形態の半導体モジュ−ル500は、第1の半導体装置500aの開口部533aから露出する導電層510aが、金属バンプ503を介して、第2の半導体装置500bの開口部523bから露出する導電層510bと接続される。このようにして、第1および第2の半導体装置500a、500bからなる半導体モジュール500が得られる。

【0035】

本発明の第1の実施の形態の半導体モジュ−ル500は、上述のような構造を有するので、テープを有する半導体装置の積み重ね実装を容易に行うことが可能となり、かつ容易に実装できるため、実装工程が簡易なため、コストを下げることも可能となる。

【0036】

図6は本発明の第2の実施の形態の半導体モジュールについて説明するための断面図である。以下、図6を用いて本発明の第2の実施の形態の半導体モジュールについて説明する。

【0037】

この半導体モジュール600は、本発明の第1の実施の形態の半導体モジュール500とほぼ同様の構成のため、詳しい説明は省略する。本発明の第2の実施の形態の半導体モジュール600の半導体装置600aおよび600bにおいて、テープ608a、およびテープ608bは、夫々緩衝膜607aおよび607b、例えばエラストマーを介して、半導体チップ601a、及び半導体チップ601bと固着されていることを特徴とする。

【0038】

本発明の第2の実施の形態の半導体モジュール600では、本発明の第1の実施の形態の半導体モジュール500と同様の効果を奏することは言うまでもない。さらに、上記のように緩衝膜607aを有するので、これら緩衝膜607a、607bは熱収縮率の差により、半導体チップ601aとテープ608a、半導体チップ601bとテープ608bが夫々剥がれるのを防ぐように働く。したがって、本発明の第1の実施の形態の半導体モジュール500の構造に比して、半導体チップ601aとテープ608a、半導体チップ601bとテープ608b夫々が剥がれにくい構造が得られる。

【0039】

図7は本発明の第3の実施の形態の半導体モジュールについて説明するための断面図である。以下、図7を用いて本発明の第3の実施の形態の半導体モジュ−ルについて説明する。

【0040】

この半導体モジュール700は、本発明の第1の実施の形態の半導体モジュール500とほぼ同様の構成のため、詳しい説明は省略する。本発明の第3の実施の形態の半導体モジュ−ル700の半導体装置700aおよび700bにおいて、導電層710aと外部端子704a、導電層710bと外部端子704bの夫々の接続部が、夫々樹脂702aおよび702bで覆われていることを特徴とする。

【0041】

本発明の第3の実施の形態の半導体モジュール700は、本発明の第1の実施の形態の半導体モジュ−ル500と同様の効果を奏することは言うまでもない。さらに、上記のように導電層710aと外部端子704a、導電層710bと外部端子704bの夫々の接続部が、夫々樹脂702aおよび702bで覆われている。このため、本発明の第1の実施の形態の半導体モジュール500の構造に比して、導電層710aと外部端子704a、導電層710bと外部端子704bが夫々剥がれにくい、堅固な構造を得ることができる。

【0042】

図8は本発明の第4の実施の形態の半導体モジュールについて説明するための断面図である。以下、図8を用いて本発明の第4の実施の形態の半導体モジュ−ルについて説明する。

【0043】

この半導体モジュール800は、本発明の第1の実施の形態の半導体モジュール500とほぼ同様の構成のため、詳しい説明は省略する。本発明の第4の実施の形態の半導体モジュ−ル800の半導体装置800aおよび800bにおいて、導電層810aと外部端子804aとの接続部を樹脂802aが覆い、半導体チップ801aの側面および裏面を樹脂806aが覆い、導電層810bと外部端子804bとの接続部を樹脂802bが覆い、および半導体チップ801bの側面および裏面を樹脂806bが夫々覆うことを特徴とする。

【0044】

本発明の第4の実施の形態の半導体モジュール800は、本発明の第1の実施の形態の半導体モジュ−ル500と同様の効果を奏することは言うまでもない。さらに、上記のように導電層810aと外部端子804aとの接続部を樹脂802aが覆い、半導体チップ801aの側面および裏面を樹脂806aが覆い、導電層810bと外部端子804bとの接続部を樹脂802bが覆い、および半導体チップ801bの側面および裏面を樹脂806bが夫々覆っている。このため、本発明の第1の実施の形態の半導体モジュール500の構造に比して、半導体チップ801aおよび801bの主表面方向からの外力に対してより強い、堅固な構造を得ることができる。

【0045】

図9は本発明の第5の実施の形態の半導体モジュールについて説明するための断面図である。以下、図9を用いて本発明の第5の実施の形態の半導体モジュ−ルについて説明する。

【0046】

この半導体モジュール900は、半導体装置900aおよびプリント配線基板920から構成される。

【0047】

この半導体装置900aは、主表面に複数の外部端子904を有する集積回路を形成された半導体チップ901と、導電層910、およびこの導電層910を絶縁層909、913で挟む構造からなるテープ908とから構成される。ここで、例えば導電層910はCu、絶縁層909はポリイミドやガラスエポキシ、絶縁層913はソルダーレジストから構成される。

【0048】

また、半導体チップ901の主表面は、パッシベーション膜905で覆われている。

【0049】

テープ908は、半導体チップ901の主表面から裏面まで延在し、かつ半導体チップ901の主表面側および裏面側の夫々で半導体チップ901と固着されている。

【0050】

さらに、導電層910は、複数の外部端子904と電気的に接続され、かつ、半導体チップ901の主表面および裏面の夫々に位置する絶縁層913に形成された開口部903aおよび903bから露出されている。

【0051】

この半導体装置900aの開口部903bで露出する導電層910の表面が、金属バンプ903を用いて、プリント配線基板920上のパッド921と電気的に接続されている。ここで、パッド921は、例えばNi−Auまたは半田から構成されている。

【0052】

上述したように本発明の第5の実施の形態の半導体モジュール900は、導電層910を露出する開口部903aが半導体チップ901の主表面側に設けられている。したがって、半導体装置900aとプリント配線基板920との積み重ね実装を容易にする。さらに、実装に用いられなかった半導体装置の開口部903aから露出する導電層910は、半導体装置900aとプリント配線基板920とが接続されているか否かの電気的テストに用いることができる。

【0053】

図10は本発明の第6の実施の形態の半導体装置モジュールについて説明するための断面図である。以下、図10を用いて本発明の第6の実施の形態の半導体モジュ−ルについて説明する。

【0054】

この半導体モジュール1000は、本発明の第5の実施の形態の半導体モジュール900とほぼ同様の構成のため、詳しい説明は省略する。本発明の第6の実施の形態の半導体モジュ−ル1000の半導体装置1000aにおいて、テープ1008が緩衝膜1007、例えばエラストマーを介して、半導体チップ1001と固着されていることを特徴とする。

【0055】

本発明の第6の実施の形態の半導体モジュール1000は、本発明の第5の実施の形態の半導体モジュ−ル900と同様の効果を奏することは言うまでもない。さらに、上記のような緩衝膜1007を有するので、この緩衝膜1007は熱収縮率の差により、テープ1008が半導体チップ1001から剥がれるのを防ぐように働く。したがって、本発明の第5の実施の形態の半導体モジュール900の構造に比して、よりテープ1008と半導体チップ1001が剥がれにくい構造が得られる。

【0056】

図11は本発明の第7の実施の形態の半導体装置モジュールについて説明するための断面図である。以下、図11を用いて本発明の第7の実施の形態の半導体モジュ−ルについて説明する。

【0057】

この半導体モジュール1100は、本発明の第5の実施の形態の半導体モジュール900aとほぼ同様の構成のため、詳しい説明は省略する。本発明の第7の実施の形態の半導体モジュ−ル1100の半導体装置1100aにおいて、導電層1110と外部端子1104との接続部が樹脂1102で覆われていることを特徴とする。

【0058】

本発明の第7の実施の形態の半導体モジュール1100は、本発明の第5の実施の形態の半導体モジュ−ル900と同様の効果を奏することは言うまでもない。さらに、上記のように導電層1110と外部端子1104との接続部が樹脂1102で覆われている。このため、本発明の第5の実施の形態の半導体モジュール900の構造に比して、外部端子1104と導電層1110が剥がれにくい、堅固な構造を得ることができる。

【0059】

図12は本発明の第8の実施の形態の半導体装置モジュールについて説明するための断面図である。以下、図12を用いて本発明の第8の実施の形態の半導体モジュ−ルについて説明する。

【0060】

この半導体モジュール1200は、本発明の第5の実施の形態の半導体モジュール900とほぼ同様の構成のため、詳しい説明は省略する。本発明の第8の実施の形態の半導体モジュ−ル1200の半導体装置1200aにおいて、導電層1210と外部端子1204との接続部を樹脂1202が覆い、さらには半導体チップ1201の側面および裏面を、樹脂1206が夫々覆うことを特徴とする。

【0061】

本発明の第8の実施の形態の半導体モジュール1200は、本発明の第5の実施の形態の半導体モジュ−ル900と同様の効果を奏することは言うまでもない。さらに、上記のように導電層1210と外部端子1204との接続部を樹脂1202が覆い、さらには半導体チップ1201の側面および裏面を、樹脂1206が夫々覆っている。このため、本発明の第5の実施の形態の半導体モジュール900の構造に比して、半導体チップ1201の主表面方向からの外力に対してより強い、堅固な構造を得ることができる。

【0062】

【発明の効果】

本発明の半導体モジュ−ルは、第1に、半導体装置の主表面側に開口部、裏面側に開口部を有するので、開口部から露出する導電層、もしくは、開口部から露出する導電層、もしくは、これら両方と、外部装置、例えば他の半導体装置と電気的に接続できる。つまり、複数の半導体装置の積み重ね実装を容易にすることができる。第2に、開口部から露出する導電層、もしくは、開口部から露出する導電層の一方が他の半導体装置との接続に用いる場合、他方は半導体装置自身の電気的テストに用いることができる。

【0063】

また、本発明の半導体モジュ−ルにおいて、第1の半導体装置は、開口部から露出する導電層を介して、第2の半導体装置または、プリント配線基板と接続される。したがって、本発明の半導体モジュ−ルは、複数の半導体装置の積み重ね実装を容易に行うことが可能となり、かつ容易に実装できるため、実装工程が簡易なため、コストを下げることも可能となる。

【図面の簡単な説明】

【図1】本発明の第1の実施の形態の半導体装置の構造を断面図で示すものである。

【図2】本発明の第2の実施の形態の半導体装置の構造を断面図で示すものである。

【図3】本発明の第3の実施の形態の半導体装置の構造を断面図で示すものである。

【図4】本発明の第4の実施の形態の半導体装置の構造を断面図で示すものである。

【図5】本発明の第1の実施の形態の半導体モジュールの構造を断面図で示すものである。

【図6】本発明の第2の実施の形態の半導体モジュールの構造を断面図で示すものである。

【図7】本発明の第3の実施の形態の半導体モジュールの構造を断面図で示すものである。

【図8】本発明の第4の実施の形態の半導体モジュールの構造を断面図で示すものである。

【図9】本発明の第5の実施の形態の半導体モジュールの構造を断面図で示すものである。

【図10】本発明の第6の実施の形態の半導体モジュールの構造を断面図で示すものである。

【図11】本発明の第7の実施の形態の半導体モジュールの構造を断面図で示すものである。

【図12】本発明の第8の実施の形態の半導体モジュールの構造を断面図で示すものである。

【図13】従来のμBGA型半導体装置の構造の断面図を示すものである。

【符号の説明】

100:半導体装置

101:半導体チップ

103a:開口部

103b:開口部

104:外部端子

105:パッシベーション膜

108:テープ

109:絶縁層

110:導電層

113:絶縁層

Claims (4)

- 表面と裏面とを有し、前記表面上に形成された電極を有する半導体チップと、

絶縁層に挟まれた導電層を有する、前記半導体チップの前記表面と前記裏面とに固着されたテープと、を含み、

前記テープは、前記半導体チップの前記表面から鈍角に折り曲げられた屈曲部を介して前記半導体チップの前記裏面に延在し、

前記半導体チップの前記表面上に配置された前記テープの前記絶縁層から前記導電層が突出しており、前記導電層の前記突出した部分が前記半導体チップの前記電極に接続されていることを特徴とする半導体装置。 - 請求項1記載の半導体装置において、前記導電層の前記突出した部分を封止する封止樹脂を含むことを特徴とする半導体装置。

- 請求項1または2に記載の半導体装置において、前記テープと前記半導体チップとの間には緩衝膜が設けられていることを特徴とする半導体装置。

- 請求項1〜3のいずれかに記載の半導体装置において、前記半導体チップの側面と前記裏面とが樹脂で覆われていることを特徴とする半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003132849A JP3859618B2 (ja) | 2003-05-12 | 2003-05-12 | 半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003132849A JP3859618B2 (ja) | 2003-05-12 | 2003-05-12 | 半導体装置 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP11744299A Division JP3602000B2 (ja) | 1999-04-26 | 1999-04-26 | 半導体装置および半導体モジュール |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2003347475A JP2003347475A (ja) | 2003-12-05 |

| JP3859618B2 true JP3859618B2 (ja) | 2006-12-20 |

Family

ID=29774788

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003132849A Expired - Fee Related JP3859618B2 (ja) | 2003-05-12 | 2003-05-12 | 半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3859618B2 (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6323060B1 (en) | 1999-05-05 | 2001-11-27 | Dense-Pac Microsystems, Inc. | Stackable flex circuit IC package and method of making same |

| US6262895B1 (en) | 2000-01-13 | 2001-07-17 | John A. Forthun | Stackable chip package with flex carrier |

| US6914324B2 (en) | 2001-10-26 | 2005-07-05 | Staktek Group L.P. | Memory expansion and chip scale stacking system and method |

| US7485951B2 (en) | 2001-10-26 | 2009-02-03 | Entorian Technologies, Lp | Modularized die stacking system and method |

| US7371609B2 (en) | 2001-10-26 | 2008-05-13 | Staktek Group L.P. | Stacked module systems and methods |

| US6940729B2 (en) | 2001-10-26 | 2005-09-06 | Staktek Group L.P. | Integrated circuit stacking system and method |

| US7310458B2 (en) | 2001-10-26 | 2007-12-18 | Staktek Group L.P. | Stacked module systems and methods |

| US7081373B2 (en) | 2001-12-14 | 2006-07-25 | Staktek Group, L.P. | CSP chip stack with flex circuit |

| US7309914B2 (en) | 2005-01-20 | 2007-12-18 | Staktek Group L.P. | Inverted CSP stacking system and method |

| US7417310B2 (en) | 2006-11-02 | 2008-08-26 | Entorian Technologies, Lp | Circuit module having force resistant construction |

| TWI399839B (zh) * | 2009-09-28 | 2013-06-21 | 力成科技股份有限公司 | 內置於半導體封裝構造之中介連接器 |

-

2003

- 2003-05-12 JP JP2003132849A patent/JP3859618B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2003347475A (ja) | 2003-12-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3602000B2 (ja) | 半導体装置および半導体モジュール | |

| JP3893363B2 (ja) | 半導体モジュール | |

| US6812573B2 (en) | Semiconductor device and method for manufacturing the same | |

| US7230341B2 (en) | Electronic device and method of manufacturing the same, circuit board, and electronic instrument | |

| US6740964B2 (en) | Semiconductor package for three-dimensional mounting, fabrication method thereof, and semiconductor device | |

| JP3996315B2 (ja) | 半導体装置およびその製造方法 | |

| US6921980B2 (en) | Integrated semiconductor circuit including electronic component connected between different component connection portions | |

| KR100274333B1 (ko) | 도체층부착 이방성 도전시트 및 이를 사용한 배선기판 | |

| US6958527B2 (en) | Wiring board having interconnect pattern with land, and semiconductor device, circuit board, and electronic equipment incorporating the same | |

| JP3526548B2 (ja) | 半導体装置及びその製造方法 | |

| JPH07503579A (ja) | フリップチップ集積回路の背面接地 | |

| JP3859618B2 (ja) | 半導体装置 | |

| US7611925B2 (en) | Electronic device and method of manufacturing the same, chip carrier, circuit board, and electronic instrument | |

| US20040232540A1 (en) | Electronic device and method of manufacturing the same, circuit board, and electronic instrument | |

| US6458627B1 (en) | Semiconductor chip package and method of fabricating same | |

| JP3836811B2 (ja) | 半導体モジュール | |

| US6969908B2 (en) | Semiconductor device, method of manufacturing the same, circuit board, and electronic instrument | |

| JP3859617B2 (ja) | 半導体装置 | |

| US5422515A (en) | Semiconductor module including wiring structures each having different current capacity | |

| JP4364221B2 (ja) | 半導体装置 | |

| JP3943037B2 (ja) | 半導体装置の製造方法 | |

| JP3458056B2 (ja) | 半導体装置およびその実装体 | |

| JP2003309220A (ja) | 半導体装置 | |

| JP7416607B2 (ja) | 半導体装置 | |

| JP3951869B2 (ja) | 実装基板およびその製造方法、並びに電子回路装置およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060627 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060821 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20060912 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20060919 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090929 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100929 Year of fee payment: 4 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100929 Year of fee payment: 4 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100929 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110929 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110929 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120929 Year of fee payment: 6 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120929 Year of fee payment: 6 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130929 Year of fee payment: 7 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| LAPS | Cancellation because of no payment of annual fees | ||

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |