JP3789583B2 - データ処理装置 - Google Patents

データ処理装置 Download PDFInfo

- Publication number

- JP3789583B2 JP3789583B2 JP03496097A JP3496097A JP3789583B2 JP 3789583 B2 JP3789583 B2 JP 3789583B2 JP 03496097 A JP03496097 A JP 03496097A JP 3496097 A JP3496097 A JP 3496097A JP 3789583 B2 JP3789583 B2 JP 3789583B2

- Authority

- JP

- Japan

- Prior art keywords

- address

- access

- bit

- instruction

- data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000012545 processing Methods 0.000 title claims description 306

- 239000000872 buffer Substances 0.000 claims description 202

- 230000015654 memory Effects 0.000 claims description 126

- 238000000034 method Methods 0.000 claims description 62

- 230000008569 process Effects 0.000 claims description 57

- 230000007423 decrease Effects 0.000 claims description 5

- 230000003247 decreasing effect Effects 0.000 claims description 5

- 238000010586 diagram Methods 0.000 description 62

- 238000004364 calculation method Methods 0.000 description 55

- 230000006870 function Effects 0.000 description 29

- 238000006073 displacement reaction Methods 0.000 description 11

- 230000007246 mechanism Effects 0.000 description 7

- 230000008859 change Effects 0.000 description 6

- 238000005516 engineering process Methods 0.000 description 6

- 230000009467 reduction Effects 0.000 description 3

- 230000004044 response Effects 0.000 description 3

- 125000004122 cyclic group Chemical group 0.000 description 2

- 238000001514 detection method Methods 0.000 description 2

- 230000009191 jumping Effects 0.000 description 2

- 239000000619 acesulfame-K Substances 0.000 description 1

- 238000004458 analytical method Methods 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- 235000019800 disodium phosphate Nutrition 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 230000001343 mnemonic effect Effects 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 238000012805 post-processing Methods 0.000 description 1

- 238000007781 pre-processing Methods 0.000 description 1

- 229920006395 saturated elastomer Polymers 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/34—Addressing or accessing the instruction operand or the result ; Formation of operand address; Addressing modes

- G06F9/355—Indexed addressing

- G06F9/3552—Indexed addressing using wraparound, e.g. modulo or circular addressing

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3824—Operand accessing

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3885—Concurrent instruction execution, e.g. pipeline or look ahead using a plurality of independent parallel functional units

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Software Systems (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Memory System (AREA)

- Executing Machine-Instructions (AREA)

- Information Transfer Systems (AREA)

- Advance Control (AREA)

Description

【発明の属する技術分野】

この発明は、高性能なデータ処理装置に関するものであり、特に、サーキュラバッファを効率よくアクセスするためのアドレッシング機能を有するデータ処理装置に関するものである。

【0002】

【従来の技術】

ディジタル・シグナル・プロセッサ(DSP)は、ディジタル信号処理を高速に実現する専用のプロセッサである。DSPでは、サーキュラバッファを効率よく扱うために、モジュロアドレッシング(巡回アドレッシング)を備えるものが多い。

【0003】

DSPでは、一般的に1クロックサイクルに1回以上の積和演算を行うために、2つ以上の独立にアクセス可能なデータメモリ、もしくは、複数のポートを備えたメモリを持つ。ただし、ワードサイズは16ビット、24ビット等様々であるが、基本的に1つのメモリについては1ワードアクセスしか行わない。しかし、データメモリを1系統しか持たないプロセッサタイプのデータ処理装置で1クロックサイクルに1回以上の積和演算を実現しようとする場合、2つの以上のデータを1サイクルで取り込む必要がある。さらに、1サンプル毎に逐次処理を行う場合、1つのワードデータのアクセスと2つのワードデータのアクセスとが混在する。このような1ワードアクセスと2ワードアクセスが混在する状況で正しくモジュロアドレッシングを実現したものはなかった。

【0004】

また、一般的なDSPでは、例えば、USP4,908,748に開示されたDSPのように、サーキュラーバッファのサイズを指定し、ポインタの更新後のアドレスとサーキュラーバッファのサイズのもとに、更新後のアドレスをモディファイするかどうかを判定している。このように、ポインタの更新後にアドレスの判定を行うと1クロックサイクルに行う処理内容が多くなり、高性能化のための動作周波数向上の妨げとなる。

【0005】

更新前のアドレスに基づいて、アドレスのモディファイを行うかどうかを判定するDSPも存在する。そのDSPは、サーキュラーバッファ領域の範囲を示す開始アドレス(rb)と終了アドレス(re)とを保持し、ポストインクリメントでアドレスが終了アドレスと一致した場合には、開始アドレス(rb)をアドレスの更新値として書き戻す。しかし、このようなDSPでは、1インクリメント時にしかモジュロアドレッシング機能が動作しないという問題点があった。

【0006】

【発明が解決しようとする課題】

DSPの演算ではモジュロアドレッシングの領域をワードアドレスで設定するため、自動インクリメント、自動デクリメントでは1ワードアクセスしかできなく、モジュロアドレッシングの設定方法も1つしかないという問題点があった。更に、モジュロアドレッシングの領域で2ワードアクセスを行う場合、2ワードアクセスしか行えないという問題点があった。

【0007】

また、インクリメントとデクリメントとでサーキュラバッファの開始アドレスと終了アドレスとが反対になるため、開始及び終了のアドレス設定を行う手間が生じるという問題点があった。

【0008】

この発明は、以上のような問題点を解消するためになされたもので、モジュロアドレッシングにおいて異なる2つのデータ単位でアクセス可能なデータ処理装置あるいはインクリメントとデクリメントとで開始アドレスと終了アドレスの設定に手間を要しないデータ処理装置を得ることを目的とする。

【0009】

【課題を解決するための手段】

この発明にかかる請求項1記載のデータ処理装置は、nビット及び2nビットデータ単位でアクセス可能なサーキュラバッファ領域が確保されたメモリを有し、nビットデータ単位に前記メモリにアクセスし、次にアクセスすべきnビットデータを特定するアドレス更新を行うことを規定した第1のメモリアクセス命令と、2nビットデータ単位で前記メモリにアクセスし、次にアクセスすべき2nビットデータを特定する前記アドレス更新を行うことを規定した第2のメモリアクセス命令とが少なくとも実行可能な装置であって、前記サーキュラバッファ領域の開始アドレス情報を付与する開始アドレス情報付与手段と、前記サーキュラバッファの領域の終了アドレス情報を付与する終了アドレス情報付与手段とを備え、前記開始アドレス情報は少なくとも前記サーキュラーバッファ領域上の2nビットデータを特定可能なアドレスを指示し、前記終了アドレス情報は少なくとも前記サーキュラーバッファ領域上の2nビットデータを特定可能なアドレスを指示し、前記開始アドレス情報が指示するアドレスから前記終了アドレス情報が指示するアドレスへの方向がアドレス更新方向として規定され、前記サーキュラバッファの領域上のアクセス対象のアドレスを規定したアクセスアドレスと前記終了アドレス情報の指示するアドレスとを比較して比較結果情報を出力する比較手段と、前記第1及び第2のメモリアクセス命令処理時に、前記アドレス更新方向において、前記アクセスアドレスの次に配置されるアドレスを演算して演算アドレスを出力するアドレス演算手段とをさらに備え、前記アドレス演算手段は、前記第1のメモリアクセス命令処理時に、前記アクセスアドレスの次に配置されるnビットデータを特定するアドレスを前記演算アドレスとし、前記第2のメモリアクセス命令処理時に、前記アクセスアドレスの次に配置される2nビットデータを特定するアドレスを前記演算アドレスとし、前記比較結果情報に基づき、前記開始アドレス情報の指示するアドレスに基づく値あるいは前記演算アドレスを選択して次のアクセス対象となるアドレスを規定した次期アクセスアドレスを決定するアクセスアドレス決定手段をさらに備え、前記アクセスアドレス決定手段は、前記第1のメモリアクセス命令の処理時には、前記終了アドレス情報が指示するアドレスと前記アクセスアドレスとの間で、nビットデータを特定するアドレス部分が等価であるという第1の条件が成立すると判定すると、前記開始アドレス情報の指示するアドレスに関連し、かつ前記サーキュラーバッファ領域上のnビットデータを特定可能なnビットアクセスアドレスを前記次期アクセスアドレスとし、前記第1の条件が不成立であると判定すると、前記演算アドレスを前記次期アクセスアドレスとし、前記第2のメモリアクセス命令の処理時には、前記終了アドレス情報が指示するアドレスと前記アクセスアドレスとの間で、2nビットデータを特定するアドレス部分が等価であるという第2の条件が成立すると判定すると、前記開始アドレス情報の指示するアドレスに関連し、かつ前記サーキュラーバッファ領域上の2nビットデータを特定可能な2nビットアクセスアドレスを前記次期アクセスアドレスとし、前記第2の条件が不成立であると判定すると、前記演算アドレスを前記次期アクセスアドレスとしている。

【0010】

また、請求項2記載のデータ処理装置は、前記第1及び第2のメモリアクセス命令はそれぞれ前記アドレス更新をアドレスを増加させて行う第1及び第2のインクリメント処理を含み、前記アドレス更新方向はアドレスが増加する方向に規定され、前記開始アドレス情報付与手段は、前記開始アドレス情報を保持する開始アドレス情報保持手段を含み、前記終了アドレス情報付与手段は、前記終了アドレス情報を保持する終了アドレス情報保持手段を含んだものである。

【0011】

また、請求項3記載のデータ処理装置は、前記開始アドレス情報が指示するアドレスは前記サーキュラーバッファ領域上のnビットデータを特定可能なアドレスを含み、前記終了アドレス情報が指示するアドレスは前記サーキュラーバッファ領域上のnビットデータを特定可能なアドレスを含み、前記nビットアクセスアドレスは前記開始アドレス情報が指示するアドレスを含み、前記2nビットアクセスアドレスは前記開始アドレス情報が指示するアドレスを含んだものである。

【0012】

また、請求項4記載のデータ処理装置は、前記開始アドレス情報が指示するアドレスは前記サーキュラーバッファ領域上の2nビットデータを特定可能なアドレスを含み、前記終了アドレス情報が指示するアドレスは前記サーキュラーバッファ領域上の2nビットデータを特定可能なアドレスを含み、前記アクセスアドレス決定手段が用いた前記第1の条件は、前記終了アドレス情報が指示するアドレスで特定される前記サーキュラーバッファ領域上の2nビットデータを構成する2つのnビットデータのうち、後半のnビットデータを特定するアドレスに前記アクセスアドレスが一致するという条件を含み、前記nビットアクセスアドレスは前記開始アドレス情報が指示するアドレスを含み、前記2nビットアクセスアドレスは前記開始アドレス情報が指示するアドレスを含んだものである。

【0013】

また、請求項5記載のデータ処理装置は、前記第1及び第2のアクセス命令はそれぞれアドレスを減少させて前記アドレス更新を行う第1及び第2のデクリメント処理を含み、前記アドレス更新方向はアドレスが減少する方向に規定され、前記開始アドレス情報付与手段は、前記開始アドレス情報を保持する開始アドレス情報保持手段を含み、前記終了アドレス情報付与手段は、前記終了アドレス情報を保持する終了アドレス情報保持手段を含んだものである。

【0014】

また、請求項6記載のデータ処理装置は、前記開始アドレス情報が指示するアドレスは前記サーキュラーバッファ領域上のnビットデータを特定可能なアドレスを含み、前記終了アドレス情報が指示するアドレスは前記サーキュラーバッファ領域上のnビットデータを特定可能なアドレスを含み、前記nビットアクセスアドレスは前記開始アドレス情報が指示するアドレスを含み、前記2nビットアクセスアドレスは、前記開始アドレス情報が指示するアドレスのうち2nビットデータを特定可能なアドレス部分と、2nビットデータ単位でアクセス可能にするための固定データとからなるアドレスを含んだものである。

【0015】

また、請求項7記載のデータ処理装置は、前記開始アドレス情報が指示するアドレスは前記サーキュラーバッファ領域上の2nビットデータを特定可能なアドレスを含み、前記終了アドレス情報が指示するアドレスは前記サーキュラーバッファ領域上の2nビットデータを特定可能なアドレスを含み、前記nビットアクセスアドレスは、前記開始アドレス情報の指示するアドレスにより特定した前記サーキュラーバッファ領域上の2nビットデータを構成する2つのnビットデータのうち、後半のnビットデータを特定するアドレスを含み、前記2nビットアクセスアドレスは前記開始アドレス情報が指示するアドレスを含んだものである。

【0016】

また、請求項8記載のデータ処理装置は、前記サーキュラーバッファ領域上の下限アドレスを保持する下限アドレス保持手段と、前記サーキュラーバッファ領域上の上限アドレスを保持する上限アドレス保持手段とをさらに備え、前記第1及び第2のメモリアクセス命令はそれぞれアドレスを増加させて前記アドレス更新を行う第1及び第2のインクリメント処理を含み、前記第1及び第2のメモリアクセス命令が前記第1及び第2のインクリメント処理を行う命令の場合、前記アドレス更新方向はアドレスが増加する方向に規定され、前記第1及び第2のアクセス命令はそれぞれアドレスを減少させて前記アドレス更新を行う第1及び第2のデクリメント処理をさらに含み、前記第1及び第2のメモリアクセス命令が前記第1及び第2のデクリメント処理を行う命令の場合、前記アドレス更新方向はアドレスが減少する方向に規定され、前記開始アドレス情報付与手段は、実行対象の前記第1及び第2のメモリアクセス命令の内容を指示する実行命令情報、前記下限アドレス及び前記上限アドレスを受け、前記実行命令情報が前記第1あるいは第2のインクリメント処理を指示するとき、前記下限アドレスを指示する前記開始アドレス情報を付与し、前記実行命令情報が前記第1あるいは第2のデクリメント処理を指示するとき、前記上限アドレスを指示する前記開始アドレス情報を付与する第1の選択手段を含み、前記終了アドレス情報付与手段は、前記実行命令情報、前記下限アドレス及び前記上限アドレスを受け、前記実行命令情報が前記第1あるいは第2のインクリメント処理を指示するとき、前記上限アドレスを指示する前記終了アドレス情報を付与し、前記実行命令情報が前記第1あるいは第2のデクリメント処理を指示するとき、前記下限アドレスを指示する前記終了アドレス情報を付与する第2の選択手段を含んだものである。

【0017】

また、請求項9記載のデータ処理装置は、前記下限アドレス及び前記上限アドレスは前記サーキュラーバッファ領域上のnビットデータを特定可能なアドレスを含み、前記nビットアクセスアドレスは前記開始アドレス情報が指示するアドレスを含み、前記2nビットアクセスアドレスは、前記第2のメモリアクセス命令が前記第2のインクリメント処理を行う命令の場合に前記開始アドレス情報が指示するアドレスとなり、前記第2のメモリアクセス命令が前記第2のデクリメント処理を行う命令の場合に、前記開始アドレス情報が指示するアドレスのうち2nビットデータを特定可能なアドレス部分と、2nビットデータ単位でアクセス可能にするための固定データとからなるアドレスを含んだものである。

【0018】

また、請求項10記載のデータ処理装置は、前記下限アドレス及び前記上限アドレスは前記サーキュラーバッファ領域上の2nビットデータを特定可能なアドレスを含み、前記アクセスアドレス決定手段が用いた前記第1の条件は、前記第1のメモリアクセス命令が前記第1のインクリメント処理を行う命令の場合に、前記終了アドレス情報が指示するアドレスで特定される前記サーキュラーバッファ領域上の2nビットデータを構成する2つのnビットデータのうち、後半のnビットデータを特定するアドレスに前記アクセスアドレスが一致するという条件となり、前記nビットアクセスアドレスは、前記第1のメモリアクセス命令が前記第1のインクリメント処理を行う命令の場合に、前記開始アドレス情報が指示するアドレスとなり、前記第1のメモリアクセス命令が前記第1のデクリメント処理を行う命令の場合に、前記開始アドレス情報の指示するアドレスにより特定した前記サーキュラーバッファ領域上の2nビットデータを構成する2つのnビットデータのうち後半のアドレスのnビットデータを特定するアドレスとなり、前記2nビットアクセスアドレスは前記開始アドレス情報が指示するアドレスを含んだものである。

【0019】

また、請求項11記載のデータ処理装置は、前記第1及び第2のメモリアクセス命令は、前記メモリからデータを取り込むロード命令を含んだものである。

【0020】

また、請求項12記載のデータ処理装置は、前記第1及び第2のメモリアクセス命令は、前記メモリにデータを格納するストア命令を含んだものである。

【0024】

【発明の実施の形態】

<基本構成>

本発明の実施の形態1であるデータ処理装置について説明する。本実施の形態で用いるデータ処理装置は、16ビットプロセッサであり、アドレス及びデータのビット長は16ビットとする。

【0025】

図1に本データ処理装置のレジスタセットを示す。本データ処理装置は、ビット順、バイト順に関してビッグエンディアンを採用しており、ビット位置はMSBがビット0になる。

【0026】

16本のレジスタR0〜R15はデータやアドレス値を格納する。レジスタR0〜R14は汎用レジスタであり、レジスタR13はサブルーチンジャンプ時の戻り先アドレスを格納するためのリンク(LINK)レジスタとして割り当てられている。レジスタR15はスタックポインタSPであり、割り込み用のスタックポインタSPIとユーザ用のスタックポインタSPUとが後で説明するプロセッサ・ステータス・ワードPSWによって切り替えられる。以後、スタックポインタSPIとSPUとを総称して、スタックポインタSPと呼ぶ。

【0027】

特別な場合を除き、4ビットのレジスタ指定フィールドでオペランドとなる各レジスタの番号が指定される。本データ処理装置では、例えば、レジスタR0とR1とのように2つのレジスタをペアにして、処理する命令を備えている。この場合、偶数番号のレジスタを指定し、このレジスタのペアとなるレジスタは、レジスタ番号を1プラスした奇数番号のレジスタが暗黙的に指定される。CR0〜CR3、CR7〜CR11は各々16ビットの制御レジスタである。各制御レジスタも、汎用レジスタと同様、通常レジスタの番号が4ビットで示される。レジスタCR0は、プロセッサ・ステータス・ワード(PSW)を格納し、データ処理装置の動作モードを指定するビットや演算結果を示すフラグからなる。

【0028】

図2はレジスタCR0内のPSWの構成を示す図である。同図に示すように、PSWのビット番号0はスタックモードを示すSMビット41である。SMビット41が“0”の場合は割り込みモードであることを示し、レジスタR15としてスタックポインタSPIが用いられる。“1”の場合はユーザーモードであることを示し、レジスタR15としてスタックポインタSPUが用いられる。PSWのビット番号5は割り込みイネーブルを指定するIEビット42であり、“0”の場合は割り込みをマスク(アサートされても無視)し、“1”の場合は割り込みを受け付ける。本データ処理装置では、ゼロオーバーヘッドのループ処理を実現するためのリピート機能がインプリメントされている。PSWのビット番号6はリピート状態を示すRPビット43であり、“0”の場合はリピート中でないことを、“1”の場合はリピート中であることを示す。また、本データ処理装置では、サーキュラーバッファをアクセスするためのアドレッシングであるモジュロアドレッシング機能がインプリメントされている。PSWのビット番号7はモジュロイネーブルを指定するMDビット44であり、“0”の場合はモジュロアドレッシングをディスエーブル状態にし、“1”の場合はモジュロアドレッシングをイネーブル状態にする。PSWのビット番号8は、アキュムレータのデータフォーマットを指定するFXビット45であり、“0”の場合は乗算結果を整数フォーマットでアキュムレータに格納し、“1”の場合は乗算結果を固定小数点フォーマットとして1ビット右にシフトしてアキュムレータに格納する。PSWのビット番号9はサチュレーションモードを指定するSTビット46である。“0”の場合はアキュムレータに演算結果を格納する際、演算結果を40ビットとして書き込む。“1”の場合はアキュムレータに演算結果を格納する際、32ビットで表現できる値にリミット処理して書き込む。”h’”を16進表記とすると、演算結果がh'007fffffffより大きい値の場合には、アキュムレータにh'007fffffffを書き込み、演算結果がh'ff80000000より小さい値の場合には、アキュムレータにh'ff80000000を書き込む。PSWのビット番号12は実行制御フラグ(F0フラグ)47であり、比較命令の比較結果などがこのフラグにセットされる。PSWのビット番号13も実行制御フラグ(F1フラグ)48であり、比較命令等によりF0フラグ47を更新する際に、更新前のF0フラグ47の値が、F1フラグにコピーされる。PSWのビット番号15はキャリー・フラグ(Cフラグ)49であり、加減算命令実行時のキャリーがこのフラグにセットされる。

【0029】

図1のレジスタCR2はプログラムカウンタPCであり、実行中の命令アドレスを示す。本データ処理装置が処理する命令は、基本的に32ビット固定長であり、PC(もしくはCR2)は、32ビットを1ワードとした命令ワードアドレスを保持する。

【0030】

レジスタCR1はバックアップ・プロセッサ・ステータス・ワード(BPSW)であり、例外や割り込みが検出された場合の実行中のプロセッサ・ステータス・ワードPSWの値を退避・保持するためのレジスタである。レジスタCR3はバックアップ・プログラム・カウンタ(BPC)であり、プログラム・カウンタPCの値を待避・保持するためのレジスタである。レジスタCR7〜CR9は、リピート関連のレジスタであり、リピート中であっても割り込みを受け付けられるように、ユーザーが値を読み書きできるようになっている。レジスタCR7はリピート・カウンタ(RPT_C)であり、リピート回数を示すカウント値を保持する。レジスタCR8はリピート・スタート・アドレス(RPT_S)であり、リピートを行うブロックの先頭の命令アドレスを保持する。レジスタCR9はリピート・エンド・アドレス(RPT_E)であり、リピートを行うブロックの最後の命令のアドレスを保持する。

【0031】

レジスタCR10,CR11は、モジュロ・アドレッシングを行うための制御レジスタである。レジスタCR10は、モジュロ・スタート・アドレス(MOD_S)を、レジスタCR11は、モジュロ・エンド・アドレス(MOD_E)を保持する。レジスタCR10,CR11は共に、最初と最終のデータ・ワード(16ビット)・アドレスを保持する。インクリメントでモジュロアドレッシングを利用する場合には、モジュロ・スタート・アドレスMOD_Sとして小さい方のアドレスが、モジュロ・エンド・アドレスMOD_Eとして大きい方のアドレスがセットされ、インクリメントするレジスタ値がモジュロ・エンド・アドレスMOD_Eと一致した場合、インクリメント結果として、モジュロ・スタート・アドレスMOD_Sのアドレス値が、レジスタに書き戻される。

【0032】

図1に40ビットのアキュムレータA0、A1を示す。各アキュムレータA0,A1は、積和演算結果の上位16ビットを保持するA0H、A1H、積和演算結果の下位16ビットを保持するA0L、A1L、積和演算結果の上位からあふれたビットを保持する8ビットのガードビットA0G、A1Gからなる。

【0033】

本データ処理装置は2ウェイのVLIW(Very Long Instruction Word)命令セットを処理する。図3は、本データ処理装置の命令フォーマットを示す。基本命令長は32ビット固定であり、32ビット境界に整置されている。各32ビットの命令コードは、命令のフォーマットを示す2ビットのフォーマット指定ビット(FMビット)51と、15ビットの左コンテナ52と右コンテナ53から構成される。各コンテナ52、53はそれぞれ15ビットからなるショートフォーマットのサブ命令を格納できるほか、2つで1つの30ビットのロングフォーマットのサブ命令を格納できる。今後、簡単のため、ショートフォーマットのサブ命令をショート命令、ロングフォーマットのサブ命令をロング命令と呼ぶ。

【0034】

FMビット51は命令のフォーマット及び2つのショート命令の実行順序を指定する。FMビット51が“11”の場合は、コンテナ52、53の30ビットで1つのロング命令を保持することを示し、それ以外の場合は各コンテナ52、53がそれぞれショート命令を保持することを示す。さらに、2つのショート命令を保持する場合、FMビット51で実行順序を指定する。“00”のときは、2つのショート命令を並列に実行することを示す。“01”のときは、左コンテナ52に保持されているショート命令を実行した後に、右コンテナ53に保持されているショート命令を実行することを示す。“10”のときは、右コンテナ53に保持されているショート命令を実行した後に、左コンテナ52に保持されているショート命令を実行することを示す。このように、シーケンシャルに実行する2つのショート命令も含めて1つの32ビット命令にエンコード出来るようにして、コード効率の向上を図っている。

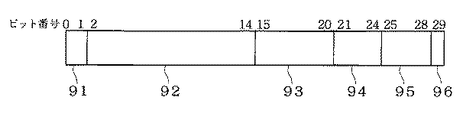

【0035】

図4〜図7に典型的な命令のビット割り付けの例を示す。図4は2つのオペランドを持つショート命令のビット割り付けを示す。フィールド61、64は、オペレーションコードフィールドである。フィールド64に、アキュムレータ番号を指定する場合もある。フィールド62、63には、オペランドとして参照あるいは更新されるデータの格納位置を、レジスタ番号やアキュムレータ番号で指定する。フィールド63は、4ビットの小さな即値を指定する場合もある。図5は、ショートフォーマットの分岐命令の割り付けを示しており、オペレーションコードフィールド71と8ビットの分岐変位フィールド72からなる。分岐変位は、PC値と同様、命令ワード(32ビット)のオフセットで指定される。図6は、16ビットの変位や即値を持つ3オペランド命令やロード/ストア命令のフォーマットを示しており、オペレーションコードフィールド81、ショートフォーマットと同様レジスタ番号等を指定するフィールド82、83、16ビットの変位や即値等を指定する拡張データフィールド84とからなる。図7は、右コンテナ53側にオペレーションコードを持つロングフォーマットの命令のフォーマットを示しており、2ビットのフィールド91が“01”になっている。93と96はオペレーションコードフィールドで、94と95はレジスタ番号等を指定するフィールドである。92は予約フィールドであり必要に応じてオペレーションコードやレジスタ番号等の指定に使用される。

【0036】

上述以外に、NOP(ノー・オペレーション)のように、15ビットすべてがオペレーションコードとなる命令や、1オペランド命令等、特殊な命令のビット割り付けを持つものもある。

【0037】

本データ処理装置の各サブ命令は、RISCライクな命令セットとなっている。メモリデータのアクセスを行う命令はロード/ストア命令のみであり、演算命令はレジスタ/アキュムレータ中のオペランドや即値オペランドに対して演算を行う。オペランドデータのアドレッシングモードとしては、レジスタ間接モード、ポストインクリメント付きレジスタ間接モード、ポストデクリメント付きレジスタ間接モード、プッシュモード、レジスタ相対間接モードの5種類ある。各々のニーモニックは、”@Rsrc”、”@Rsrc+”、”@Rsrc−”、”−SP”、” (disp16、Rsrc)”で示される。Rsrcはベースアドレスを指定するレジスタ番号を、disp16は16ビットの変位値を示す。オペランドのアドレスはバイトアドレスで指定される。

【0038】

レジスタ相対間接モード以外のモードは、図4に示す命令フォーマットとなる。フィールド63でベースレジスタ番号が指定され、フィールド62でメモリからロードしてきた値を書き込むレジスタの番号もしくはストアする値を保持するレジスタの番号が指定される。レジスタ間接モードは、ベースレジスタとして指定されたレジスタの値がオペランドアドレスとなる。ポストインクリメント付きレジスタ間接モードは、ベースレジスタとして指定されたレジスタの値がオペランドアドレスとなり、このベースレジスタの値がオペランドのサイズ(バイト数)分ポストインクリメントされて、書き戻される。ポストデクリメント付きレジスタ間接モードは、ベースレジスタとして指定されたレジスタの値がオペランドアドレスとなり、このベースレジスタの値がオペランドのサイズ(バイト数)分ポストデクリメントされて、書き戻される。プッシュモードは、ストア命令で、かつ、ベースレジスタがレジスタR15の場合にのみ使用可能であり、スタックポインタ(SP)値がオペランドのサイズ(バイト数)分プリデクリメントされた値が、オペランドアドレスとなり、デクリメントされた値がSPに書き戻される。

【0039】

レジスタ相対間接モードは図6に示す命令フォーマットとなる。フィールド83でベースレジスタ番号が指定され、フィールド82でメモリからロードしてきた値を書き込むレジスタの番号もしくはストアする値を保持するレジスタの番号が指定される。フィールド84はオペランド格納位置のベースアドレスからの変位値を指定する。レジスタ相対間接モードは、ベースレジスタとして指定されたレジスタの値に16ビットの変位値を加算した値がオペランドアドレスとなる。

【0040】

ポストインクリメント付きレジスタ間接モードとポストデクリメント付きレジスタ間接モードでは、PSW中のMDビット44を“1”に設定する事により、モジュロアドレッシングモードが使用できる。

【0041】

ジャンプ命令のジャンプ先アドレス指定には、ジャンプ先アドレスをレジスタ値で指定するレジスタ間接と、ジャンプ命令のPCからの分岐変位で指定するPC相対間接とがある。PC相対間接については、分岐変位を8ビットで指定するショートフォーマットと、分岐変位を16ビットで指定するロングフォーマットの2種類ある。また、オーバーヘッドなしにループ処理を実現するリピート機能を起動するためのリピート命令も備える。

【0042】

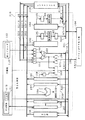

図8に本データ処理装置100の機能ブロック構成を示す。データ処理装置100は、MPUコア部101と、MPUコア部101からの要求により命令データのアクセスを行う命令フェッチ部102、内蔵命令メモリ103、MPUコア部101からの要求によりオペランドデータのアクセスを行うオペランドアクセス部104、内蔵データメモリ105、命令フェッチ部102とオペランドアクセス部104からの要求を調停し、データ処理装置100の外部メモリのアクセス等を行う外部バスインターフェイス部106からなる。

【0043】

MPUコア部101は、命令キュー111、制御部112、レジスタファイル115、第1演算部116、第2演算部117、PC部118からなる。

【0044】

命令キュー111は、2エントリの32ビット命令バッファと有効ビット、及び入出力ポインタ等からなり、FIFO(先入れ先出し)方式で制御される。命令キュー111は、命令フェッチ部102でフェッチされた命令データを一時保持し、制御部112に送る。

【0045】

制御部112は、前述の命令キュー111の制御、パイプライン制御、命令の実行、命令フェッチ部102やオペランドアクセス部104とのインターフェイスなど、MPUコア部101のすべての制御を行う。また、制御部112には、命令キュー111から送られる命令コードをデコードするための命令デコード部119があり、2つのデコーダを含む。第1デコーダ113は、第1演算部116で実行する命令をデコードし、第2デコーダ114は、第2演算部117で実行する命令をデコードする。32ビットの命令のデコードの第1サイクルでは、必ず左コンテナ52(図3)の命令コードが第1デコーダ113で解析され、右コンテナ53の命令コードが第2デコーダ114で解析される。従って、最初に実行する命令はその命令を実行する演算器に対応した位置に置かれなければならない。

【0046】

ただし、FMビット51及び左コンテナ52のビット0とビット1とのデータは両方のデコーダで解析される。また、拡張データの切り出しを行うために、右コンテナ53のデータが第1デコーダ113に送られるが、解析は行われない。2つのショート命令をシーケンシャルに実行する場合、先行して実行される命令のデコード中に後で実行する側の命令が図示していないプリデコーダでデコードされ、どちらのデコーダでデコードすべきかを判定する。後で実行される命令がどちらのデコーダでも処理できる命令の場合は第1デコーダ113でデコードする。先行する命令のデコード後、後で実行する命令の命令コードが選択されたデコーダに取り込まれ、解析される。

【0047】

レジスタファイル115は、レジスタR0〜R15(図1)の値を保持し、第1演算部116、第2演算部117、PC部118、オペランドアクセス部104に複数のバスで結合されている。

【0048】

図9に、第1演算部116の詳細ブロック構成を示す。第1演算部116は、レジスタファイル115と、各々S1バス301、S2バス302、S3バス303によって結合されており、これら3つのバス301〜303を介してレジスタファイル115からデータを読み出し、演算器等にリードオペランドとなるデータやストアデータを転送する。S1バス301は偶数番号のレジスタにのみに、S2バス302は奇数番号のレジスタにのみに結合されており、S1バス301とS2バス302でレジスタペアの2ワードを並列に転送することもできる。S3バス303は全レジスタに結合されている。

【0049】

また、第1演算部116は、レジスタファイル115と、各々D1バス311、Wバス314で結合されており、D1バス311を介して演算結果や転送データをレジスタファイル115に転送し、Wバス314でロードしたバイトデータをレジスタファイル115に転送する。D1バス311、Wバス314とも、全レジスタに結合されている。さらに、レジスタファイル115はオペランドアクセス部104と32ビットのODバス322で結合されており、1ワードのデータもしくはレジスタペアの2ワードを並列に転送することが可能である。ODバス322の上位/下位16ビットは、任意のレジスタファイルに書き込みができるようにレジスタファイル115の全レジスタに結合されている。

【0050】

AAラッチ151、ABラッチ152は、ALU153の入力ラッチである。AAラッチ151は、S1バス301、S2バス302もしくはS3バス303を介して読み出されたレジスタ値を取り込む。同ラッチ151は、ゼロクリアする機能も備えている。ABラッチ152は、S3バス303を介して読み出されたレジスタ値もしくは第1デコーダ113でデコードの結果生成された16ビットの即値を取り込み、また、ゼロクリアする機能も備えている。

【0051】

ALU153では、主として転送、比較、算術論理演算、オペランドアドレスの計算/転送、オペランドアドレス値のインクリメント/デクリメント、ジャンプ先アドレスの計算/転送等が行われる。演算結果やアドレスモディファイの結果はセレクタ155、D1バス311を介して、レジスタファイル115中の命令で指定されたレジスタに書き戻される。例えば、ALU153がインクリメント(デクリメント)の計算を行う場合、AAラッチ151に保持されたベースアドレスとABラッチ152に保持された増加(減少)アドレス値とを加算処理を行う。ABラッチ152には2ワードアクセスの場合に“4”、1ワードアクセスの場合に“2”が保持される。

【0052】

また、指定された条件が成立した場合には“1”を不成立の場合には“0”をレジスタに書き込む条件セット命令を実行するために、セレクタ155は演算結果の最下位ビットに制御部112から出力されたデータを埋め込む機能を備える。この場合、演算結果はゼロが出力されるように制御される。AOラッチ154は、オペランドのアドレスを保持するラッチであり、ALU153でのアドレス計算結果もしくはAAラッチ151に保持されたベースアドレスの値を選択的に保持し、OAバス321を介してオペランドアクセス部104に出力する。また、ジャンプ先アドレスやリピートエンドアドレスを計算した場合には、ALU153の出力が、JAバス323を介してPC部118に転送される。

【0053】

モジュロ演算部700はMOD_S156、MOD_E157、比較器158、ラッチ159からなる。MOD_S156及びMOD_E157は、それぞれ図1のCR10(モジュロ・スタート・アドレス(MOD_S)を保持)及びCR11(モジュロ・エンド・アドレス(MOD_E)を保持)に対応して設けられる制御レジスタである。比較器158は、MOD_E157の値とS3バス303上のベースアドレスの値とを比較する。MOD_S156は、ラッチ159を介してセレクタ155に結合されている。詳細な動作については、後述する。

【0054】

ストアデータ(SD)レジスタ160は、16ビットのレジスタ2本からなり、S1バス301もしくはS2バス302の一方、もしくは、S1バス301とS2バス302の両方に出力されたストアデータを一時保持する。SDレジスタ160に保持されたデータは、ラッチ161を介して整置回路162に転送される。整置回路162では、オペランドのアドレスに従って、ストアデータが32ビット境界に整置され、ラッチ163、ODバス322を介してオペランドアクセス部104に出力される。

【0055】

また、オペランドアクセス部104でロードされたバイトデータは、ODバス322を介して、16ビットのロードデータ(LD)レジスタ164に取り込まれる。LDレジスタ164の値は、ラッチ165を介して、整置回路166に転送される。整置回路166では、バイト整置及びバイトデータのゼロ/符号拡張を行う。整置、拡張後のデータが、Wバス314を介してレジスタファイル115中の指定されたレジスタに書き込まれる。1ワード(16ビット)ロード、2ワード(32ビット)ロードの場合にはLDレジスタを介さず、ODバス322からレジスタファイル115にロードした値が直接書き込まれる。

【0056】

制御部112中のPSW部171は図1のレジスタCR0の値を保持するPSWラッチ172や、PSW更新回路等からなり、演算結果や命令の実行によりPSWラッチ172の値を更新する。PSWラッチ172に値を転送する場合、S3バス303に出力されたデータがTPSWラッチ167を介して、必要なビット(アサインされているビット)のみ転送される。PSWラッチ172の値を読み出す場合には、PSW部171からD1バス311に出力され、レジスタファイル115に書き込まれる。BPSWラッチ168は図1のレジスタCR1に相当するレジスタである。例外処理時には、D1バス311に出力されたPSWの値がBPSWラッチ168に書き込まれる。BPSWラッチの値をレジスタファイル115に転送する場合には、BPSWラッチ168の値はS3バス303に読み出され、レジスタファイルなど必要な場所に転送される。アサインされていないビットは強制的にゼロがS3バス303に出力される。例外からの復帰時には、BPSWラッチ168の値は、直接TPSWラッチ167を介して、必要なビット(アサインされているビット)のみPSWラッチ172に転送される。

【0057】

図10は、PC部118の詳細ブロック図である。命令アドレス(IA)レジスタ181は、次にフェッチする命令のアドレスを保持し、次にフェッチする命令のアドレスを命令フェッチ部102に出力する。引き続き後続の命令をフェッチする場合には、IAレジスタ181からラッチ182を介して転送されたアドレス値がインクリメンタ183で1インクリメントされて、IAレジスタ181に書き戻される。ジャンプやリピート等によりシーケンスが切り替わる場合には、IAレジスタ181はJAバス323を介して転送されるジャンプ先アドレス、リピートブロック開始アドレスを取り込む。

【0058】

RPT_Sレジスタ184、RPT_Eレジスタ186、RPT_Cレジスタ188はリピート制御用の制御レジスタであり、それぞれ図1のレジスタCR8、レジスタCR9、レジスタCR7に対応する。RPT_Eレジスタ186はリピートを行うブロックの最終命令のアドレスを保持する。この最終アドレスは、リピート命令処理時に第1演算部116で計算され、JAバス323を介してRPT_Eレジスタ186に取り込まれる。比較器187は、リピートを行うブロックの最終命令のアドレスを保持するRPT_Eレジスタ186の値と、フェッチアドレスを保持しているIAレジスタ181の値とを比較する。もし、リピート処理中であり、リピートする回数を保持するRPT_Cレジスタ188の値が“1”でなく、かつ、2つのアドレスが一致した場合、RPT_Sレジスタ184に保持されているリピートを行うブロックの開始アドレスが、ラッチ185、JAバス323を介して、IAレジスタ181に転送される。リピートの終了アドレスの命令が実行されるたびに、RPT_Cレジスタ188の値は、ラッチ189を介してデクリメンタ190で“1”だけデクリメントされる。デクリメントした値が、“0”であった場合には、PSW中のRPビット43をクリアし、リピート処理を終了する。RPT_Sレジスタ184、RPT_Eレジスタ186、RPT_Cラッチ188は、D1バス311からの入力ポートとS3バス303への出力ポートを持ち、必要に応じてリピート時の初期設定や待避復帰が行なわれる。

【0059】

実行ステージPC(EPC)194は実行中の命令のPC値を保持し、次命令PC(NPC)191は次に実行する命令のPC値を保持する。NPC191は、実行段階でジャンプが起こった場合、JAバス323上のジャンプ先アドレス値を取り込み、リピートで分岐が起こった場合には、ラッチ185からリピートを行うブロックの先頭アドレスを取り込む。それ以外の場合には、ラッチ192を介して転送されたNPC191の値が、インクリメンタ193でインクリメントされ、NPC191に書き戻される。サブルーチンジャンプ命令の場合には、ラッチ192の値が戻り先アドレスとしてD1バス311に出力され、レジスタファイル115中のリンクレジスタとして定義されているレジスタR13に書き戻される。また、次の命令が実行状態に入る場合には、ラッチ192の値がEPC194に転送される。実行中の命令のPC値を参照する場合には、EPC194の値がS3バス303に出力され、第1演算部116に転送される。BPC196は、図1で示したレジスタセットのレジスタCR3に対応する。例外や割り込み等が検出された場合には、EPC194の値がラッチ195を介してBPC196に転送される。BPC196は、D1バス311からの入力ポートとS3バス303への出力ポートを持ち、必要に応じて待避復帰が行なわれる。

【0060】

図11に、第2演算部117の詳細ブロック図を示す。第2演算部117は、レジスタファイル115と、各々S4バス304、S5バス305で結合されており、この2つのバス304,305を介してデータをレジスタファイル115から読み出す。S4バス304とS5バス305でレジスタペアの2ワードを並列に転送することも可能である。また、第2演算部117は、レジスタファイル115と、D2バス312、D3バス313で結合されており、この2つのバス312,313を介してデータをレジスタファイル115内の各レジスタに書き込むことができる。D2バス312は偶数番号のレジスタのみに、D3バス313は奇数番号のレジスタのみに各々結合されている。D2バス312とD3バス313でレジスタペアの2ワードを並列に転送することもできる。

【0061】

アキュムレータ208は、図1のアキュームレータA0,A1の2本の40ビットアキュムレータに相当する。

【0062】

201は40ビットのALUであり、ビット番号0からビット番号7までの8ビットがアキュムレータのガードビット用加算器、ビット番号8からビット番号23までの16ビットが算術論理演算器、ビット番号24からビット番号39までの16ビットがアキュムレータの下位16ビットを加算するための加算器になっており、40ビットまでの加減算と、16ビットの論理演算を行う。

【0063】

Aラッチ202、Bラッチ203は、ALU201の40ビット入力ラッチである。Aラッチ202は、S4バス304からレジスタ値をビット番号8からビット番号23の位置に取り込むか、シフタ204を介して、アキュムレータ208の値をそのままもしくは16ビット算術右シフトした値を取り込む。シフタ205は、アキュムレータ208の値を配線206(ガードビット8ビット)、S4バス304(上位16ビット)、S5バス305(下位16ビット)を介して取り込むか、レジスタの値をS5バス305のみ、もしくは、S4バス304とS5バス305の両方を介して16ビットもしくは32ビットのデータを右詰めで取り込み、40ビットに符号拡張する。シフタ205は、入力したデータを左3ビットから右2ビットの任意のシフト量で算術シフトし出力する。Bラッチ203は、S5バス305上のデータをビット番号8からビット番号23の位置に取り込むか、乗算器の出力、もしくは、シフタ205の出力を取り込む。Aラッチ202、Bラッチ203は、各々ゼロクリアしたり定数の値に設定したりする機能も持つ。

【0064】

ALU201の出力は、サチュレーション回路209に出力される。サチュレーション回路209は、上位16ビット、もしくは、上位下位あわせた32ビットにする際に、ガードビットを見て、各々16ビットもしくは32ビットで表現できる最大値もしくは最小値にクリッピングする機能を備える。もちろんそのまま出力する機能もある。サチュレーション回路209の出力は配線207に結合されている。

【0065】

デスティネーションオペランドがアキュムレータ208の場合には、配線207の値がアキュムレータ208に書き込まれる。デスティネーションオペランドがレジスタの場合は、配線207の値が、D2バス312やD3バス313を介して、レジスタファイル115に書き込まれる。1ワード転送の場合にはデスティネーションレジスタの番号が偶数の場合D2バス312に、奇数の場合にはD3バス313に出力される。2ワード転送の場合には、上位側の16ビットデータがD2バス312に、下位側のビットデータがD3バス313に出力される。また、転送命令、絶対値の計算、最大値設定命令や、最小値設定命令を実行するために、Aラッチ202とBラッチ203の出力が、配線207に結合されており、Aラッチ202とBラッチ203の値をアキュムレータ208やレジスタファイル115に転送することが可能である。

【0066】

プライオリティエンコーダ210は、ラッチB203の値を取り込み、固定小数点フォーマットの数を正規化するのに必要なシフト量を計算し、レジスタファイル115に書き戻すために結果をD2バス312もしくはD3バス313に出力する。

【0067】

Xラッチ212、Yラッチ213は乗算器の入力レジスタであり、各々、S4バス304、S5バス305の16ビットの値を取り込み、17ビットにゼロ拡張もしくは符号拡張する機能を備える。乗算器211は、17ビットx17ビットの乗算器であり、Xラッチ212に格納された値とYラッチ213に格納された値との乗算を行う。積和命令や積差命令の場合には、乗算結果はPラッチ214に取り込まれ、Bラッチ203に送られる。乗算命令でデスティネーションオペランドがアキュムレータ208の場合には、乗算結果をアキュムレータ208に書き込む。

【0068】

バレルシフタ215は、40ビットもしくは16ビットのデータに対して、左右16ビットまでの算術/論理シフトが可能である。シフトデータは、アキュムレータ208の値もしくはS4バス304を介してレジスタの値がシフトデータ(SD)ラッチ217に取り込まれる。シフト量については、即値もしくはレジスタ値がS5バス305を介してシフト量(SC)ラッチ216に取り込まれる。バレルシフタ215はSDラッチ217のデータをSCラッチ216で指定されるシフト量だけ、オペレーションコードで指定されたシフトを行う。シフト結果は、サチュレーション回路209に出力され、ALUでの演算結果と同様、必要に応じてサチュレーションが行われ、配線207に出力される。配線207に出力された値は、アキュムレータ208もしくはD2バス312、D3バス313を介してレジスタファイル115に書き戻される。

【0069】

即値ラッチ218は、第2デコーダ114で生成された6ビットの即値を16ビットに拡張して保持し、S5バス305を介して演算器に転送する。ビット操作命令のビットマスクもここで生成される。

【0070】

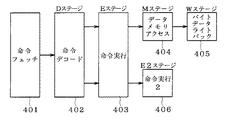

次に本データ処理装置のパイプライン処理について説明する。図12はパイプライン処理を示す図である。本データ処理装置は、命令データのフェッチを行う命令フェッチ(IF)ステージ401、命令の解析を行う命令デコード(D)ステージ402、演算実行を行う命令実行(E)ステージ403、データメモリのアクセスを行うメモリアクセス(M)ステージ404、メモリからロードしたバイトオペランドをレジスタへ書き込むライトバック(W)ステージ405の5段のパイプライン処理を行う。Eステージ403での演算結果のレジスタへの書き込みはEステージ403で完了し、ワード(2バイト)、2ワード(4バイト)ロード時のレジスタへの書き込みはMステージ404で完了する。積和/積差演算に関しては、更に乗算と加算の2段のパイプラインで命令の実行を行う。後段の処理を命令実行2(E2)ステージ406と呼ぶ。連続する積和/積差演算を1回/1クロックサイクルのスループットで実行できる。

【0071】

IFステージ401では、主として命令のフェッチ、命令キュー111の管理、リピート制御が行われる。命令フェッチ部102、内蔵命令メモリ103、外部バスインターフェイス部106、命令キュー111、PC部118のIAレジスタ181、ラッチ182、インクリメンタ183、比較器187等や制御部112のIFステージステージ制御、命令フェッチ制御、PC部118制御等を行う部分が、このIFステージ401の制御で動作する。IFステージ401は、Eステージ403のジャンプで初期化される。

【0072】

フェッチアドレスは、IAレジスタ181で保持される。Eステージ403でジャンプが起こるとJAバス323を介してジャンプ先アドレスを取り込み、初期化を行う。シーケンシャルに命令データをフェッチする場合には、インクリメンタ183でアドレスをインクリメントする。リピート処理中に、比較器187でIAレジスタ181の値とRPT_E186の値が一致していることが検出され、かつ、RPT_Cの値が1でなければ、シーケンスの切り替え制御が行われる。この場合、RPT_S184に保持されている値がラッチ185、JAバス323を介してIAレジスタ181に転送される。

【0073】

IAレジスタ181の値は命令フェッチ部102に送られ、命令フェッチ部102が命令データのフェッチを行う。対応する命令データが内蔵命令メモリ103にある場合には、内蔵命令メモリ103から命令コードを読み出す。この場合、1クロックサイクルで32ビットの命令のフェッチを完了する。対応する命令データが内蔵命令メモリ103にない場合には、外部バスインターフェイス部106に命令フェッチ要求を出す。外部バスインターフェイス部106は、オペランドアクセス部104からの要求とを調停し、命令の取り込みが可能になったら、外部のメモリから命令データを取り込み、命令フェッチ部102に送る。外部バスインターフェイス部106は、最小2クロックサイクルで外部メモリのアクセスを行うことが可能である。命令フェッチ部102は取り込まれた命令を、命令キュー111に転送する。命令キュー111は2エントリのキューになっており、FIFO制御で取り込まれた命令コードを、命令デコード部119に出力する。

【0074】

Dステージ402では、命令デコード部119でオペレーションコードの解析を行い、第1演算部116、第2演算部117、PC部118等で命令の実行を行うための制御信号群を生成する。Dステージ402は、Eステージ403のジャンプで初期化される。命令キュー111から送られてくる命令コードが無効な場合には、アイドルサイクルとなり、有効な命令コードが取り込まれるまで待つ。Eステージ403が次の処理を開始できない場合には、演算器等に送る制御信号を無効化し、Eステージ403での先行命令の処理の終了を待つ。例えば、Eステージ403で実行中の命令がメモリアクセスを行う命令であり、Mステージ404でのメモリアクセスが終了していない場合にこのような状態になる。

【0075】

Dステージ402では、シーケンシャル実行を行う2命令の分割や、2サイクル実行命令のシーケンス制御も行う。さらに、スコアボードレジスタ(図示せず)を用いたロードオペランドの干渉チェックや第2演算部117での演算器の干渉チェック等も行い、干渉が検出された場合には、干渉が解消されるまで制御信号の出力を抑止する。図13は、ロードオペランド干渉の例を示す。ワードもしくは2ワードのロード命令の直後にロードするオペランドを参照する積和演算命令がある場合、レジスタへのロードが完了するまで、積和演算命令の実行開始を抑止する。この場合、メモリアクセスが1クロックサイクルで終了する場合でも、1クロックサイクルストールが起こる。バイトデータをロードする場合には、更にWステージでレジスタファイルへの書き込みが完了するため、更に1サイクルストール期間が延びる。図14は、演算ハードウェア干渉の例を示す。積和演算命令の直後に加算器を使用する丸め命令がある場合、先行の積和演算命令の演算が終了するまで丸め命令の実行開始を抑止する。この場合、1クロックサイクルストールが起こる。積和演算命令が連続する場合には、ストールは起こらない。

【0076】

第1デコーダ113は、主として第1演算部116のすべて、PC部118のIFステージ401で制御される部分以外、レジスタファイル115のS1バス301、S2バス302、S3バス303への読み出し制御とD1バス311からの書き込み制御に関する実行制御信号を生成する。命令に依存するMステージ404やWステージ405での処理に必要な制御信号もここで生成され、パイプラインの処理の流れに付随して転送される。第2デコーダ114は、主として第2演算部117での実行制御、レジスタファイル115のS4バス304、S5バス305への読み出し制御とD2バス312、D3バス313からの書き込み制御に関する実行制御信号を生成する。

【0077】

Eステージ403では、演算、比較、制御レジスタを含むレジスタ間転送、ロード/ストア命令のオペランドアドレス計算、ジャンプ命令のジャンプ先アドレスの計算、ジャンプ処理、EIT(例外、割り込み、トラップの総称)検出と各EITのベクタテーブルへのジャンプ等、メモリアクセスと積和/積差演算命令の加算処理を除く命令実行に関するほとんどすべての処理を行う。

【0078】

割り込みイネーブルの場合の割り込みの検出は、必ず32ビット命令の切れ目で行われる。32ビット命令の中にシーケンシャルに実行する2つのショート命令がある場合に、この2つのショート命令間で割り込みを受け付けることはない。

【0079】

Eステージ403で処理中の命令がオペランドアクセスを行う命令であり、Mステージ404でメモリアクセスが完了しない場合には、Eステージ403での完了は待たされる。ステージ制御は制御部112で行われる。

【0080】

Eステージ403において、第1演算部116では、算術論理演算、比較、転送を行う。モジュロの制御を含むメモリオペランドのアドレスや、分岐先のアドレス計算もこのALU153で行われる。オペランドとして指定されたレジスタの値が、S1バス301、S2バス302、S3バス303に読み出され、別途取り込まれる即値、変位等の拡張データとともに、ALU153で演算が行われ、演算結果がD1バス311を介してレジスタファイル115に書き戻される。ロード/ストア命令の場合には、演算結果はAOラッチ154、OAバス321を介して、オペランドアクセス部104に送られ、ジャンプ命令の場合には、ジャンプ先アドレスがJAバス323を介して、PC部118に送られる。ストアデータはS1バス301、S2バス302を介して、レジスタファイル115から読み出され、SDレジスタ160、ラッチ161で保持され、整置回路166で整置が行われる。また、PC部118では、実行中の命令のPC値の管理、次に実行する命令のアドレスの生成が行われる。第1演算部116、PC部118に含まれる制御レジスタ(アキュムレータを除く)とレジスタファイル115間の転送は、S3バス303、D1バス311を介して行われる。

【0081】

Eステージ403において、第2演算部117では、算術論理演算、比較、転送、シフト他積和演算の加算以外のすべての演算実行が行われる。オペランドの値が、レジスタファイル115や即値レジスタ218、アキュムレータ208等から、S4バス304、S5バス305やその他の専用経路を介して各演算器に転送され、指定された演算を行い、アキュムレータ208やD2バス312、D3バス313を介してレジスタファイル115に書き戻される。

【0082】

第1演算部116及び第2演算部117での演算結果によるPSW172中のフラグ値の更新制御も、Eステージ403で行われる。しかし、演算結果の確定がEステージ403の遅い時期になるため、実際のPSW172の値の更新は、次サイクルで行われる。データ転送によるPSW172の更新は、対応するサイクルで完了する。

【0083】

第2デコーダ114で生成された積和/積差演算の加減算実行のための実行制御信号は、Eステージ403制御のもとに保持される。メモリアクセス情報、ロードレジスタ情報は、Mステージ404に送られる。Eステージ403のステージ制御も制御部112で行われる。

【0084】

Mステージ404では、第1演算部116から送られたアドレスでオペランドのメモリアクセスが行われる。オペランドアクセス部104は、オペランドが内蔵データメモリ105やチップ内IO(図示せず)にある場合には、内蔵データメモリ105やチップ内IOに対し、1クロックサイクルでメモリのリードもしくはライトを行う。オペランドが内蔵データメモリ105やチップ内IOでない場合には、外部バスインターフェイス部106にデータアクセス要求を出す。外部バスインターフェイス部106は、外部のメモリに対してデータアクセスを行い、ロードの場合には読み出されたデータをオペランドアクセス部104に転送する。外部バスインターフェイス部106は、最小2クロックサイクルで外部メモリのアクセスを行うことが可能である。ロードの場合には、オペランドアクセス部104は読み出されたデータを、ODバス322を介して転送する。バイトデータの場合はLDレジスタ164に、ワードもしくはダブルワードデータの場合にはレジスタファイル115に直接書き込む。ストアの場合には、整置されたストアデータの値が、整置回路162からODバス322を介してオペランドアクセス部104に転送され、対象となるメモリへの書き込みが行われる。Mステージ404のステージ制御も制御部112で行われる。

【0085】

Wステージ405において、LDレジスタ164に保持されたロードオペランド(バイト)は、ラッチ165で保持され、整置回路166で整置、ゼロ/符号拡張された後に、Wバス314を介してレジスタファイル115へ書き込まれる。

【0086】

E2ステージ406では、積和/積差演算の加減算処理をALU201で行い、加減算結果をアキュムレータ208に書き戻す。

【0087】

本データ処理装置は、入力クロックに基づいて同一周波数の非重複2相のクロック信号を生成し、内部制御に使用する。最短の場合、各パイプラインステージは、内部の1クロックサイクルで処理を終了する。ここでは、クロック制御の詳細については、本発明に直接関係ないので説明を省略する。

【0088】

各サブ命令の処理例について説明する。加減算、論理演算、比較等の演算命令やレジスタ間の転送命令は、IFステージ401、Dステージ402、Eステージ403の3段で処理を終了する。演算やデータ転送をEステージ403で行う。

【0089】

積和/積差命令は、乗算を行うEステージ403と加減算を行うE2ステージの2クロックサイクルで演算実行を行うため、4段の処理となる。

【0090】

バイトロード命令は、IFステージ401、Dステージ402、Eステージ403、Mステージ404、Wステージ405の5段で処理を終了する。ワード/2ワードロードやストア命令は、IFステージ401、Dステージ402、Eステージ403、Mステージ404の4段で処理を終了する。

【0091】

非整置アクセスの場合には、オペランドアクセス部104でMステージ404の制御のもと2回のアクセスに分割され、メモリアクセスが行われる。

【0092】

実行に2サイクルかかる命令では、第1、第2命令デコーダ113、114で、2サイクルかけて処理し、各サイクル毎に各々実行制御信号を出力し、2サイクルかけて演算実行を行う。

【0093】

ロング命令は、1つの32ビット命令が1つのロング命令で構成されており、この1つのロング命令の処理で32ビット命令の実行が完了する。パラレル実行する2つの命令は、2つのショート命令で処理サイクルの大きい方の命令の処理に律速される。例えば、2サイクル実行の命令と1サイクル実行の命令の組み合わせの場合には、2サイクルかかる。シーケンシャル実行の2つのショート命令の場合には、各サブ命令の組み合わせになり、デコード段階で各命令がシーケンシャルにデコードされ、実行される。例えば、Eステージ403で1サイクルで実行が完了する加算命令が2つの場合には、Dステージ402、Eステージ403とも各命令に1サイクル、計2サイクルかけて処理する。Eステージ403における先行命令の実行と並列して、Dステージ402で後続命令のデコードが行われる。

【0094】

<実施の形態1の特徴部>

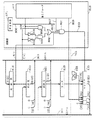

図15は、実施の形態1のデータ処理装置における特徴部であるモジュロアドレッシング機能を実現する部分の構成を模式的に示す回路図である。図中、制御部112では、モジュロ演算に関する部分のみ示している。各ラッチのイネーブル信号等は簡単のため省略している。また、論理図も分かりやすいように極力正論理で示している。158は比較器であり、S3バス303で転送されるベースアドレス値とMOD_E157に保持されたモジュロ・エンド・アドレスの比較を行う。比較器158では、2つのフィールドについて独立して比較結果を制御部112に送る。ビット0からビット13の上位14ビットが一致した場合に一致信号511が“1”になり、不一致の場合には一致信号511が“0”になる。ビット14が一致した場合に一致信号512が“1”になり、不一致の場合には一致信号512が“0”になる。

【0095】

MOD_E157は15ビットのラッチであり、D1バス311からの入力ポートと、S3バス303、比較器158への出力ポートを持つ。MOD_E157の値がS3バス303に出力される場合には、ビット15に“0”が出力される。モジュロ・スタート・アドレスを保持するMOD_S156は、15ビットのラッチであり、D1バス311からの入力ポートと、S3バス303、16ビットのラッチ159への出力ポートを持つ。MOD_S156の値がS3バス303に出力される場合には、ビット15に“0”が出力される。セレクタ155は、選択信号510に基づいてALU153の出力とラッチ159に保持されたモジュロ・スタート・アドレス値を選択的にD1バス311に出力する。ラッチ159の値を選択する場合、ビット15には“0”が出力される。また、2ワードアクセスでポストデクリメントの際に“0”、それ以外の場合に“1”になる、ローアクティブのポストデクリメント2ワードアクセス信号509が第1デコーダ113で生成され、ビット14についてはこの信号509とラッチ159のビット14との論理積がANDゲート503で求められてセレクタ155に出力される。すなわち、2ワードアクセスでポストデクリメントの場合には、強制的にビット14に“0”が出力され、それ以外の場合には、ラッチ159のビット14の値がそのまま出力される。

【0096】

制御部112内では、命令のデコード結果や比較器158の比較結果に基づいて、セレクタ155の選択信号510が生成される。PSW部171からは、モジュロイネーブルを指定するMDビット44の値が信号線506で出力される。第1デコーダ113からは命令デコードの結果として、メモリアクセス命令でポスト・インクリメント/デクリメント時に“1”となるポスト更新信号507、2ワードアクセス時に“1”となる2ワードアクセス信号508が出力される。

【0097】

ANDゲート501及びORゲート502において、これらの情報を基に選択信号510が生成される。すなわち、ORゲート502は一致信号512及び2ワードアクセス信号508の論理和演算を行ってその出力をANDゲート501に出力する。ANDゲート501はORゲート502の出力、一致信号511、MDビット44の値(信号線506上に現れる)及びポスト更新信号507の論理積演算を行って、その出力を選択信号510として出力する。

【0098】

したがって、1ワードアクセス時(2ワードアクセス信号508が“0”)において、モジュロ・アドレッシングがイネーブル状態(信号線506が“1”)で、ポスト・インクリメント/デクリメントを行うロード/ストア命令処理時(ポスト更新信号507が“1”)で、S3バス303で転送されるオペランドのアドレスとMOD_E157の上位14ビットが一致し(一致信号511が“1”)、かつ、オペランドのアドレスとMOD_E157のビット14とが一致(一致信号512が“1”)した場合に、選択信号510が“1”になり、上記条件を満たさない場合には、選択信号510は“0”になる。

【0099】

一方、2ワードアクセス時(2ワードアクセス信号508が“1”)において、モジュロ・アドレッシングがイネーブル状態で、ポスト・インクリメント/デクリメントを行うロード/ストア命令処理時で、S3バス303で転送されるオペランドのアドレスとMOD_E157の上位14ビットが一致すれば、選択信号510が“1”になる。上記条件を満たさない場合には、選択信号510は“0”になる。

【0100】

アドレスレジスタのポスト更新を行うロード/ストア命令実行時に、選択信号が“0”の場合には、ALU153での加減算結果がポインタの更新値として、D1バス311を介してレジスタファイル115に書き戻される。選択信号が“1”の場合には、ラッチ159に保持されたモジュロ・スタート・アドレスの値がポインタの更新値として、D1バス311を介してレジスタファイル115に書き戻される。この際、2ワードアクセスでポストデクリメントの場合(信号509が“0”)には、ANDゲート503により強制的に“0”がセレクタ155のビット14として出力され、それ以外の場合には、ラッチ159のビット14の値がそのまま出力される。また、セレクタ155のビット15には、強制的に“0”が出力される。

【0101】

モジュロ・アドレッシングがディスエーブル状態の場合には、選択信号510は必ず“0”になり、セレクタ155では常にALU153の出力が選択される。

【0102】

次に、いくつかのサーキュラバッファでのロード/ストア命令の実行例におけるアドレスの更新について説明する。MDビット44は“1”とする。まず、ポストインクリメントでモジュロアドレッシングを使用する場合について説明する。

【0103】

本データ処理装置では、サーキュラバッファの境界アクセス時に4バイト境界の非整置アクセスを行った場合の動作は保証していない。2ワードアクセスを行う場合は、必ず4バイト境界に整置された状態でアクセスを行う。

【0104】

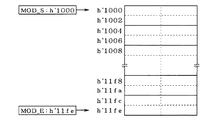

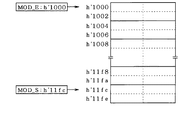

図16は、2つの境界が共に4バイト整置されているサーキュラバッファの例を示す説明図である。h’は16進表記であることを示す。h’1000番地からh’11ff番地の256ワード(512バイト)がサーキュラバッファの領域になっており、MOD_S156にはバッファ領域の先頭ワードアドレスであるh’1000の上位15ビットを、MOD_E157には最後のワードアドレスであるh’11feの上位15ビットがセットされる。

【0105】

1ワードアクセスでポストインクリメント処理を行う場合、第1デコーダ113から出力されるポスト更新信号507は“1”、2ワードアクセス信号508は“0”、ポストデクリメント2ワードアクセス信号509(ローアクティブ)は“1”になる。ベースアドレスレジスタの値がh’11feの場合、一致信号511、512が共に“1”となってANDゲート501の出力である選択信号510が“1”となり、その結果、セレクタ155はモジュロ・スタート・アドレスの値(ラッチ159の出力+“0”(ビット15))を選択して、D1バス311を介してベースアドレスレジスタにh’1000を書き戻す。

【0106】

一方、それ以外の場合には、一致信号511、512のいずれかが“0”になるため、セレクタ155は、ALU153の出力、すなわち、ベースアドレスレジスタの初期値に“2”が加算された値を選択してベースアドレスレジスタに書き戻す。例えば、ベースアドレスレジスタの値がh’11fcの場合、ベースアドレスレジスタにはh’11feが書き戻される。

【0107】

2ワードアクセスでポストインクリメント処理を行う場合、第1デコーダ113から出力されるポスト更新信号507は“1”、2ワードアクセス信号508は“1”、ポストデクリメント2ワードアクセス信号509(ローアクティブ)は“1”になる。ベースアドレスレジスタの値がh’11fcの場合、一致信号511が“1”となるため、一致信号512が“0”となっても、選択信号510が“1”となり、その結果、セレクタ155ではモジュロ・スタート・アドレスの値が選択され、ベースアドレスレジスタには、h’1000が書き戻される。

【0108】

一方、それ以外の場合には、一致信号511が“0”になるため、ベースアドレスレジスタの初期値に“4”が加算された値がベースアドレスレジスタに書き戻される。

【0109】

このように、1ワードアクセスのポストインクリメント処理と2ワードアクセスのポストインクリメント処理との間で共通のMOD_S156及びMOD_E157の設定で、実施の形態1のデータ処理装置は、ポストインクリメント処理で1ワードアクセスする場合にも、2ワードアクセスする場合にも正しく動作する。

【0110】

図17は、開始位置は4バイト整置されているが、終了位置が4バイト非整置のサーキュラバッファの例を示す説明図である。同図に示すように、h’1000番地からh’11fd番地の255ワードがサーキュラバッファの領域になっており、MOD_S156にはバッファ領域の先頭ワードアドレスであるh’1000の上位15ビットが、MOD_E157には最後のワードアドレスであるh’11fcの上位15ビットがセットされる。

【0111】

図17で示した構成のサーキュラバッファに対し、ベースアドレスレジスタの値がh’11fcで1ワードアクセスを行う場合、ベースアドレスレジスタには、h’1000が書き戻される。それ以外の1ワードアクセスの場合には、ベースアドレスレジスタの初期値に“2”が加算された値がベースアドレスレジスタに書き戻される。終了位置が4バイト非整置なので、ベースアドレスレジスタの値がh’11fcで2ワードアクセスを行うことは意味がない。配列の計算などポインタの自動更新機能を活用するために、境界を意識して奇数ワードのサーキュラバッファを使用する場合には有効である。

【0112】

図18は、開始位置は4バイト非整置で、終了位置が4バイト整置されているサーキュラバッファの例を示す説明図である。同図に示すように、h’1002番地からh’11ff番地の255ワードがサーキュラバッファの領域になっており、MOD_S156にはバッファ領域の先頭ワードアドレスであるh’1002の上位15ビットが、MOD_E157には最後のワードアドレスであるh’11feの上位15ビットがセットされる。

【0113】

ベースアドレスレジスタの値がh’11feで1ワードアクセスを行う場合、ベースアドレスレジスタには、h’1002が書き戻される。それ以外の1ワードアクセスの場合には、ベースアドレスレジスタの初期値に“2”が加算された値がベースアドレスレジスタに書き戻される。ベースアドレスレジスタの値がh’11fcで2ワードアクセスを行う場合、ベースアドレスレジスタには、h’1002が書き戻される。それ以外の2ワードアクセスの場合には、ベースアドレスレジスタの初期値に“4”が加算された値がベースアドレスレジスタに書き戻される。この場合も、ポインタの自動更新機能を活用する目的で、境界を意識して奇数ワードのサーキュラバッファを使用する場合には有効である。

【0114】

図19は、開始位置、終了位置共に4バイト整置されていないサーキュラバッファの例を示す説明図である。同図に示すように、h’1002番地からh’11fd番地の254ワードがサーキュラバッファの領域になっており、MOD_S156にはバッファ領域の先頭ワードアドレスであるh’1002の上位15ビットが、MOD_E157には最後のワードアドレスであるh’11fcの上位15ビットがセットされる。

【0115】

ベースアドレスレジスタの値がh’11fcで1ワードアクセスを行う場合、ベースアドレスレジスタには、h’1002が書き戻される。それ以外の場合には、ベースアドレスレジスタの初期値に“2”が加算された値がベースアドレスレジスタに書き戻される。2ワードアクセスを行う場合も、最初のワードと最後のワードは1ワードアクセスする必要がある。この場合も、ポインタの自動更新機能を活用する目的で、境界を意識してサーキュラバッファを使用する場合には有効である。ただし、この場合はサーキュラーバッファのサイズが2ワードの整数倍なので、バッファの境界を整置して使用した方が効率はよい。

【0116】

図16〜図19のいずれの場合も、1ワードアクセスする場合には、開始/終了位置の境界によらず正しく処理が行われる。また、境界を意識し、モジュロアドレッシングによるアドレスの自動更新機能を使うことを目的とする場合には、すべての場合で有効である。1ワードアクセスと2ワードアクセスとが混在する場合には、サーキュラーバッファの開始/終了位置を4バイト境界に整置するように、バッファ領域をとれば境界を意識せずアクセスすることが可能である。奇数ワードデータの場合も、1ワード分余分に領域を確保すれば、2つの境界を4バイト境界に整置することが可能である。必ず倍精度(32ビット)のデータを保持する場合、複素数のように2つのワードのペアを保持する場合には、サーキュラーバッファの開始/終了位置を4バイト境界に整置し、必ず2ワードアクセスを行うようにすればよい。

【0117】

上述のように、実施の形態1のデータ処理装置は、ポストインクリメント処理によって1ワードアクセスのみならず2ワードアクセスを行う場合に、サーキュラーバッファに効率よくアクセスすることが可能となり、プログラムのコードサイズの削減、処理サイクル数の低減に寄与する。これに伴い、特定のアプリケーションを実行時に消費する電力を抑えることができる。

【0118】

また、1ワードアクセスあるいは2ワードアクセス場合も、サーキュラーバッファの最初のワードと最後のワードのアドレスをそれぞれ設定すればよいので、設定が統一されており分かりやすい。

【0119】

次に、ポストデクリメント処理を行う場合について説明する。ただし、ポストインクリメントの場合と異なり、オペランドのアクセスサイズとポインタの更新サイズは必ずしも一致しないため、1ワードアクセスと2ワードアクセスが混在する場合には、ポインタ値の補正が必要になる。

【0120】

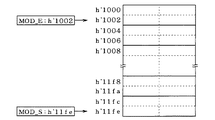

図20は、2つの境界が共に4バイト整置されているサーキュラバッファの例を示す説明図である。同図に示すように、h’1000番地からh’11ff番地の256ワード(512バイト)がサーキュラバッファの領域になっており、MOD_S156にはバッファ領域の最後のワードアドレスであるh’11feの上位15ビットが、MOD_E157には最初のワードアドレスであるh’1000の上位15ビットがセットされる。

【0121】

ポストデクリメント処理で1ワードアクセスを行う場合、第1デコーダ113から出力されるポスト更新信号507は“1”、2ワードアクセス信号508は“0”、ポストデクリメント2ワードアクセス信号509(ローアクティブ)は“1”になる。ベースアドレスレジスタの値がh’1000の場合、一致信号511、512が共に“1”となって選択信号510が“1”となり、その結果、セレクタ155はモジュロ・スタート・アドレスの値(ラッチ159の出力+“0”(ビット15))を選択して、D1バス311を介してレジスタファイル115内のベースアドレスレジスタにh’11feを書き戻す。

【0122】

それ以外の場合には、一致信号511、512のいずれかが“0”になるため、セレクタ155はALU153の出力、すなわち、ベースアドレスレジスタの初期値に“2”が減算された値を選択して、ベースアドレスレジスタに書き戻す。例えば、ベースアドレスレジスタの値がh’1002の場合、ベースアドレスレジスタにはh’1000が書き戻される。

【0123】

ポストデクリメント処理で2ワードアクセスを行う場合、第1デコーダ113から出力されるポスト更新信号507は“1”、2ワードアクセス信号508は“1”、ポストデクリメント2ワードアクセス信号509(ローアクティブ)は“0”になる。ベースアドレスレジスタの値がh’1000の場合、一致信号511、512が共に“1”となって選択信号510が“1”となり、その結果、セレクタ155はモジュロ・スタート・アドレスの値(ラッチ159の上位14ビット出力+“00”(ビット14,15))を選択してh’11fcをベースアドレスレジスタに書き戻す。

【0124】

セレクタ155の出力のビット14が“0”になるのはローアクティブのポストデクリメント2ワードアクセス信号509が“0”のため、ANDゲート503によってラッチ159の出力のビット14が強制的に0にクリアされることによる。

【0125】

それ以外の場合には、一致信号511が“0”になるため、セレクタ155は、ALU153の出力、すなわちベースアドレスレジスタの初期値に“4”が減算された値を選択してベースアドレスレジスタに書き戻す。

【0126】

このように、1ワードアクセスのポストデクリメント処理と2ワードアクセスのポストデクリメント処理との間で共通のMOD_S156及びMOD_E157の設定で、実施の形態1のデータ処理装置は、ポストデクリメント処理で1ワードアクセスする場合にも、2ワードアクセスする場合にも正しく動作する。

【0127】

図21は、開始位置は4バイト整置されているが、終了位置が4バイト非整置のサーキュラバッファの例を示す。h’1000番地からh’11fd番地の255ワードがサーキュラバッファの領域になっており、MOD_S156には最後のワードアドレスであるh’11fcの上位15ビットが、MOD_E157にはバッファ領域の先頭ワードアドレスであるh’1000の上位15ビットがセットされる。

【0128】

ベースアドレスレジスタの値がh’1000で1ワードアクセスのポストデクリメント処理を行う場合、ベースアドレスレジスタには、h’11fcが書き戻される。それ以外の1ワードアクセスの場合には、ベースアドレスレジスタの初期値に“2”が減算された値がベースアドレスレジスタに書き戻される。

【0129】

ベースアドレスレジスタの値がh’1000で2ワードアクセスのポストデクリメント処理を行う場合、ベースアドレスレジスタには、h’11fcが書き戻される。それ以外の2ワードアクセスの場合には、ベースアドレスレジスタの初期値に“4”が減算された値がベースアドレスレジスタに書き戻される。この場合、境界を意識したアクセスが必要となる。

【0130】

図22は、開始位置は4バイト非整置で、終了位置が4バイト整置されているサーキュラバッファの例を示す。h’1002番地からh’11ff番地の255ワードがサーキュラバッファの領域になっており、MOD_S156には最後のワードアドレスであるh’11feの上位15ビットが、MOD_E157にはバッファ領域の先頭ワードアドレスであるh’1002の上位15ビットがセットされる。

【0131】

ベースアドレスレジスタの値がh’1002で1ワードアクセスのポストデクリメント処理を行う場合、ベースアドレスレジスタには、h’11feが書き戻される。それ以外の1ワードアクセスの場合には、ベースアドレスレジスタの初期値に“2”が減算された値がベースアドレスレジスタに書き戻される。

【0132】

ベースアドレスレジスタの値がh’1000で2ワードアクセスのポストデクリメント処理を行うことには意味がないので、動作は保証していない。それ以外の2ワードアクセスの場合には、ベースアドレスレジスタの初期値に“4”が減算された値がベースアドレスレジスタに書き戻される。この場合も、境界を意識したアクセスが必要となる。

【0133】

図23は、開始位置、終了位置共に4バイト整置されていないサーキュラバッファの例を示す。h’1002番地からh’11fd番地の254ワードがサーキュラバッファの領域になっており、MOD_S156にはバッファ領域の最後のワードアドレスであるh’11fcの上位15ビットが、MOD_E157には先頭ワードアドレスであるh’1002の上位15ビットがセットされる。

【0134】

ベースアドレスレジスタの値がh’1002で1ワードアクセスのポストデクリメント処理を行う場合、ベースアドレスレジスタには、h’11fcが書き戻される。それ以外の場合には、ベースアドレスレジスタの初期値に“2”が減算された値がベースアドレスレジスタに書き戻される。

【0135】

2ワードアクセスのポストデクリメント処理を行う場合も、最初のワードと最後のワードは1ワードアクセスする必要がある。この場合も、ポインタの自動更新機能を活用する目的で、境界を意識して奇数ワードのサーキュラバッファを使用する場合には有効である。ただし、この場合はサーキュラーバッファのサイズが2ワードの整数倍なので、バッファの境界を整置して使用した方が効率はよい。

【0136】

図20〜図23で示したいずれの場合も、1ワードアクセスのポストデクリメント処理を行う場合には、開始/終了位置の境界によらず正しく処理が行われる。また、境界を意識し、モジュロアドレッシングによるアドレスの自動更新機能を使うことを目的とする場合には、すべての場合で有効である。必ず1ワードアクセスする場合は、開始/終了位置の境界を4バイト整置してなくもよい。

【0137】

上述のように、実施の形態1のデータ処理装置は、ポストデクリメント処理によって1ワードのみならず2ワードアクセスを行う場合にも、サーキュラーバッファに効率良くアクセスすることが可能となり、プログラムのコードサイズの削減、処理サイクル数の低減に寄与する。また、いずれの場合も、サーキュラーバッファの最初のワードと最後のワードのアドレスを設定すればよいので、設定が統一されており、分かりやすい。

【0138】

また、実施の形態1のデータ処理装置は、ポストインクリメント処理及びポストデクリメント処理時において、アドレスの計算と並列にベースアドレスの初期値に基づく判定処理可能となるため、動作周波数の向上による高速化が容易である。

【0139】

ここまで、サーキュラーバッファの様々な境界についての説明を行ったが、奇数ワードの境界の場合には制限が多い。許されるならば奇数ワードの場合は1ワード分無駄なデータ領域を追加し、2つの境界を2ワード整置して使用する方が効率はよい。特に境界を意識したくない場合は、2ワード整置して使用する。

【0140】

次に、実施の形態1のデータ処理装置を用いて1サンプル毎に逐次処理を行う256タップのFIR(有限インパルス応答)フィルタの処理例について述べる。FIRフィルタ処理プログラム例を図24に示す。図24において、“||”は2つのショート命令を並列に実行することを示す。FIRフィルタ処理では、下記の数1に示す計算を行う。数1においてA[i]は係数であり、D[i]はデータであり、iの値が小さい程、最新のデータを意味する。256回の積和演算となる。データ、係数とも16ビットの場合について説明する。

【0141】

【数1】

【0142】

図24のプログラム部分521では、データポインタ(D[0]のアドレス)の整置条件が判定される。4バイト整置されている場合にはプログラム部分522が実行され、そうでない場合にはプログラム部分523が実行される。プログラム部分524は両者の共通の後処理を行う。

【0143】

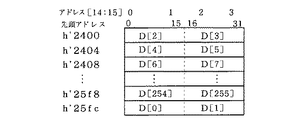

図25に初期状態での係数及びデータの内蔵データメモリ105中の割り当てを示す。係数はh’2000番地〜h’21ff番地の256ワード(512バイト)に係数の配列が配置され、h’2400番地〜h’25ff番地の256ワード(512バイト)にデータの配列が配置されている。

【0144】

このプログラムを実行する前に、レジスタr8にはデータのポインタ(D[0]のアドレス)が、レジスタr9には係数の先頭アドレス(A[0]のアドレス)がセットされているものとする。また、MOD_S156にはサーキュラーバッファとして使用するデータアレイ領域の先頭ワードアドレスであるh’2400が、MOD_E157にはデータアレイ領域の最終ワードアドレスであるh’25feが、PSW21中のMDビット44には“1”がセットされており、モジュロアドレッシングがイネーブル状態になっているものとする。

【0145】

プログラム部分521において、btst命令でレジスタr8に格納されているデータポインタのビット14(LSBから2ビット目)をテストする。ビット14が0、すなわち、4バイト整置されている場合には、F0フラグ47に“0”がセットされる。ビット14が“1”、すなわち、4バイト整置されていない場合にはF0フラグ47に“1”がセットされる。brf0t命令では、F0フラグ47が“1”(4バイト非整置)の場合ラベルoddで始まるのプログラム部分523が実行され、F0フラグ47が“0”(4バイト整置)の場合引き続くラベルevenで始まるプログラム部分522が実行される。

【0146】

”mac a0,rn,rm”命令は、レジスタrmに保持されている符号付きの16ビット数とレジスタrnに保持されている符号付きの16ビット数との乗算結果を、アキュムレータa0に加算し書き戻す。”repi #c,label”命令は、次の命令からlabelのついた命令までを、c回繰り返し実行することを示すブロックリピート命令である。”clrac a0”命令は、a0をゼロクリアする。

【0147】

プログラム部分522では、すべてのオペランドが2ワード単位でアクセスされ、所望の積和演算が実行される。積和の結果は、a0に保持される。プログラム部分523では、D[0]のアドレスが4バイト境界に乗っていないため、D[0]とD[255]のみ1ワード単位でアクセスされ、その他の部分は2ワードアクセスを行う。このようにして、いずれの場合も1クロックサイクルに1回の積和演算が実現される。プログラム部分522の最後の”bra end”命令は、ラベルendのついている命令まで無条件に分岐する命令である。プログラム部分524の”rachi r0、a0,#0”の命令は、a0に保持されている固定少数点フォーマットの数値を16ビットに丸め、サチュレーションをかけて、レジスタr0に転送する命令である。

【0148】

図25の状態では、プログラム部分522が実行され、すべてのデータが2ワードアクセスされる。1サンプル後、前回の最も古いデータD[255]が格納されたいた領域531の位置に最新データのD[0]が上書きされ、ポインタがh’25feに更新されて、図26で示す状態になる。

【0149】

図26で示す状態では、まずプログラム部分523の前処理でD[0]532が1ワードアクセスで読み出される。レジスタr8はモジュロ機構が動作し、h’2400に更新され、その後、領域533のD[1]から領域534のD[254]まで2ワードアクセスでロードされる。そして、最後の領域535のD[255]は1ワードアクセスでロードされる。

【0150】

さらに、次のサンプル入力時には、サーキュラバッファは図27の状態になる。データポインタは、h’25fcに更新される。この状態でもプログラム部分522が実行され、すべてのデータが2ワードアクセスされる。h’25fcの状態で2ワードアクセスを行うと、レジスタr8はh’2400に更新される。

【0151】

このように、1サンプル毎に処理するFIRフィルタ処理では、1ワードアクセスと2ワードアクセスが混在するが、実施の形態1のデータ処理装置によれば、サーキュラバッファの境界を1ワードアクセスする場合にも、2ワードアクセスを行う場合にも正しくポインタの更新がなされる。したがって、ユーザーはサーキュラバッファの境界を意識することなくプログラミングできプログラムのコードサイズも削減でき、プログラム中の条件判定等による処理性能の低下を招くこともなく、実施の形態1のデータ処理を用いて効率よく逐次処理を行うことができる。

【0152】

実施の形態1では、1ワードアクセスあるいは2ワードアクセスのポストデクリメント及びポストデクリメント処理でロード/ストア命令を実行可能なデータ処理装置について述べたが、さらに4ワード等より多くのデータを一度に転送するロード/ストア命令をインプリメントする場合にも、本発明の技術を応用して使用可能である。例えば、1ワードアクセス、2ワードアクセス及び4ワードアクセスを実行可能にする場合、3つのレベル(4ワードレベル、2ワードレベル、1ワードレベル)の一致信号を基に判定を行えばよい。

【0153】

また、アドレスのビット長は16ビットになっているが、24ビットや32ビット等任意のビット長であってもよい。また、データの基本データ長を16ビットにしているが、24ビットDSPのように24ビットにしたり、汎用プロセッサのように32ビットにしてもよい。

【0154】

また、上述の実施の形態1では、バイトアドレスを管理しているが、一般のDSPのように16ビットや24ビット、32ビットを1ワードとして、ワードアドレスを管理するような場合にも本発明は適用可能である。

【0155】

上述の実施の形態1では、2ワードアクセスのポストインクリメント及びポストデクリメント処理時に、一致信号511が“1”の場合、ビット14の一致・不一値を指示する一致信号512を参照することなくポインタ値(ベースアドレスレジスタの値)の入れ替えを行っている。すなわち、上述の実施の形態1では、2ワードアクセス時に一致信号511が“1”であれば、MOD_E157のアドレス値とポインタ値との間において、2ワードデータを特定するアドレス部分が等価であるとみなしている。

【0156】

上記ポインタの入れ替え以外にも、2ワードアクセスのポストインクリメント処理(ポストデクリメント処理)時に、一致信号511が“1”でかつビット14が“0”であるとき(2ワードデータを構成する2つの1ワードデータのうち、前半の1ワードデータを特定するアドレスにポインタ値が一致する)、はじめてポインタ値の入れ替えを行うように構成してもよい。すなわち、2ワードアクセス時に一致信号511が“1”でかつビット14が“0”であれば、MOD_E157のアドレス値とポインタ値との間において、2ワードデータを特定するアドレス部分が等価であるとみなしてもよい。

【0157】

上述の実施の形態1ではビット15の値を無視してアドレスの上位15ビットのみで判定を行っているが、ビット15が“0”であることを判定条件に加えてもよい。

【0158】

上述の実施の形態1では、MOD_S156、MOD_E157は、物理的に15ビットしか保持しないようにしているが、16ビット保持するようにし、ビット15は無視するような構成にしてもよいし、ビット15も比較に使用するように構成してもよい。比較に使用する場合には、MOD_S156のビット15に必ず“0”を設定するようにして、16ビットすべてを比較するようにすればよい。

【0159】

また、MOD_S156、MOD_E157には、ワードアドレスを設定しているが、境界のバイトアドレスを設定するようにしてもよい。ビット15を無視すれば、上述の実施の形態1の動作と全く同じになる。

【0160】

上述の実施の形態1では、MOD_S156、MOD_E157には、アドレスの最上位ビット(MSB)までのすべてのアドレス値を保持するようになっているが、アドレスの上位数ビットは保持しないようにし、下位ビットのみで判定を行うようにすれば、複数の領域に形成された複数のサーキュラーバッファに対して、同じ設定で同時にモジュロ機構が動作するようにできる。ただし、比較しない上位ビットについては、更新前の値をそのまま出す等の処理が必要になる。

【0161】

上述の実施の形態1では、上位14ビットとビット14の2つの比較結果を出力するようにしているが、ワードアドレスがマッチしたことを示す情報と、2ワードアドレスがマッチした情報が含まれていれば、どのような形態で演算結果を出力してもよい。

【0162】

上述の実施の形態1では、インクリメント時にもデクリメント時にも動作可能な実施例が示されているが、インクリメント時のみあるいはデクリメント時にのみ動作するようにしてもよい。

【0163】

上述の実施の形態1では、一般的なプロセッサの構成を示しているが、DSPのように、アドレスレジスタとデータレジスタ(アキュムレータ等)を分けるような構成にしてもよい。また、DSPのように、複数のメモリを独立にアクセスできるような構成にしても、本発明の技術は有効である。

【0164】

上述の実施の形態1では、規定された場合以外の動作は保証していないが、上記規定された場合以外の時に例外を検出する等の処理を行ってもよい。例えば、奇数アドレスの場合にはアドレス例外を起こす等の処理を行ってもよい。

【0165】

<実施の形態2.>

実施の形態1のデータ処理装置では巡回方向に応じて、プログラムでMOD_S156とMOD_E157とにサーキュラーバッファの境界値をセットする場合について説明した。

【0166】

実施の形態2のデータ処理装置ではサーキュラバッファの領域を上限アドレスと下限アドレスをワードアドレスで指定し、ハードウエアで比較アドレスと出力アドレスの選択を行うように構成される。モジュロアドレッシングの制御を行う部分は実施の形態1と異なるが、その他の基本的な仕様および構成は実施の形態1と同じである。

【0167】

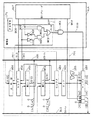

図28は、サーキュラバッファのアドレスをワードアドレスでセットするMOD_U650とMOD_L651を示す。同図に示すように、サーキュラーバッファの境界アドレスを指定する制御レジスタとして、実施の形態1のMOD_E157とMOD_S156の代わりに、MOD_U650とMOD_E157とがインプリメントされている。

【0168】

MOD_U650は15ビットのラッチで、モジュロ演算の対象となる領域の上限アドレスがワードアドレスでセットされる。MOD_L651は15ビットのラッチで、モジュロ演算の対象となる領域の下限アドレスがワードアドレスでセットされる。但し、下限アドレスは上限アドレスより小さいアドレスである。MOD_U650、MOD_L651に保持されない最下位ビット(ビット15)は“0”固定であり、書き込み時は無視され、読み出し時は常に“0”となる。

【0169】

図29は、実施の形態2のデータ処理装置の特徴部であるモジュロアドレッシング機能を実現する部分の構成を示す模式的に示す回路図である。制御部616は実施の形態1の制御部112に相当し、モジュロ演算の制御に関する部分以外はほぼ同じである。モジュロ演算部702は実施の形態1のモジュロ演算部700に相当する。各ラッチのイネーブル信号等は簡単のため省略している。また、論理図も分かりやすいように極力正論理で示している。

【0170】

図29で示す回路以外の回路部分は実施の形態1のデータ処理装置とほぼ同じである。同図において、セレクタ614は第1デコーダ617で生成されるポストインクリメント信号613の制御下で、MOD_U650あるいはMOD_L651の値を選択的に比較器158に出力する。ポストインクリメント信号613はメモリアクセス命令(ロード命令,ストア命令)でポストインクリメント時に“1”、ポストデクリメント時に“0”となる。すなわち、セレクタ614は、ポストインクリメント信号613が“1”でポストインクリメントを指示する場合に、MOD_U650の値を選択して比較器158に出力し、ポストインクリメント信号613が“0”でポストデクリメントを指示する場合に、MOD_L651の値を選択して比較器158に出力する。

【0171】

比較器158は、S3バス303で転送されるベースアドレス値とセレクタ614から出力されたアドレスとの比較を行う。比較器158では、2つのフィールドについて独立して比較結果を制御部616に送る。ビット0からビット13の上位14ビットが一致した場合に一致信号611が“1”になり、不一致の場合には一致信号611が“0”になる。ビット14が一致した場合に一致信号612が“1”になり、不一致の場合には一致信号612が“0”になる。

【0172】

サーキュラバッファの上限アドレスを保持するMOD_U650は15ビットのラッチであり、D1バス311からの入力ポートと、S3バス303、セレクタ615、セレクタ614への出力ポートを持つ。MOD_U650の値がS3バス303に出力される場合には、ビット15として“0”が出力される。

【0173】

サーキュラバッファの下限アドレスを保持するMOD_L651は、15ビットのラッチであり、D1バス311からの入力ポートと、S3バス303、セレクタ614、セレクタ615への出力ポートを持つ。MOD_L651の値がS3バス303に出力される場合には、ビット15として“0”が出力される。

【0174】

セレクタ615は、第1デコーダ617で生成されるポストインクリメント信号613で制御下でMOD_U650あるいはMOD_L651の値を選択的にラッチ159に出力する。すなわち、セレクタ615は、ポストインクリメント信号613が“1”でポストインクリメントを指示する場合に、MOD_L651の値を選択してラッチ159に出力し、ポストインクリメント信号613が“0”でポストデクリメントを指示する場合に、MOD_U650の値を選択してラッチ159に出力する。

【0175】

セレクタ155は、選択信号610に基づいてALU153の出力とラッチ159に保持されたアドレス値を選択的にD1バス311に出力し、ラッチ159の値を選択する場合、ビット15として“0”を出力する。また、2ワードアクセスでポストデクリメントの際に“0”、それ以外の場合に“1”になる、ローアクティブのポストデクリメント2ワードアクセス信号609が第1デコーダ617で生成され、ビット14についてはこの信号とラッチ159のビット14とのANDゲート603による論理積が、セレクタ155のビット14に出力される。すなわち、ポストデクリメント2ワードアクセス信号609が“0”で2ワードアクセスのポストデクリメントを指示する場合には、強制的にセレクタ155のビット14に“0”が出力され、それ以外の場合には、ラッチ159のビット14の値がそのままセレクタ155のビット14に出力される。

【0176】

制御部616内では、命令のデコード結果や比較器158の比較結果に基づいて、セレクタ155の選択信号610が生成される。PSW部171からは、モジュロイネーブルを指定するMDビット44の値が信号線606で出力される。第1デコーダ617からは命令デコードの結果として、メモリアクセス命令でポスト・インクリメント/デクリメント時に“1”となるポスト更新信号607、2ワードアクセス時に“1”となる2ワードアクセス信号608が出力される。ANDゲート601及びORゲート602において、これらの情報を基に選択信号610が生成される。すなわち、ORゲート602は一致信号612及び2ワードアクセス信号608の論理和を出力し、ANDゲート601はMDビット44の値(信号線606上)、ポスト更新信号607、一致信号611及びORゲート602の出力値の論理積を選択信号610として出力する。

【0177】

したがって、1ワードアクセス時(2ワードアクセス信号608が“0”)において、モジュロ・アドレッシングがイネーブル状態(信号線606が“1”)で、ポスト・インクリメント/デクリメントを行うロード/ストア命令処理時(ポスト更新信号607が“1”)で、かつ、S3バス303で転送されるオペランドのアドレスとセレクタ614で選択されたアドレスの上位14ビットとが一致し(一致信号611が“1”)した場合に、選択信号610が“1”になり、上記条件を満たさない場合には選択信号610は“0”になる。

【0178】

一方、2ワードアクセス時(2ワードアクセス信号608が“1”)において、モジュロ・アドレッシングがイネーブル状態で、ポスト・インクリメント/デクリメントを行うロード/ストア命令処理時で、選択信号610が“1”になり、上記条件を満たさない場合には、選択信号610は“0”になる。

【0179】

アドレスレジスタのポスト更新を行うロード/ストア命令実行時で、選択信号610が“0”の場合には、ALU153での加減算結果がポインタの更新値として、D1バス311を介してレジスタファイル115に書き戻される。選択信号610が“1”の場合には、ラッチ159に保持されたアドレスの値がポインタの更新値として、D1バス311を介してレジスタファイル115に書き戻される。この際、2ワードアクセスでポストデクリメントの場合には、ANDゲート603により強制的に“0”がセレクタ155のビット14として出力され、それ以外の場合には、ラッチ159のビット14の値がそのまま出力される。また、セレクタ155のビット15には、強制的に“0”が出力される。

【0180】

モジュロ・アドレッシングがディスエーブル状態の場合には、選択信号610は必ず“0”になり、セレクタ155では常にALU153の出力が選択される。

【0181】

一例として次に、サーキュラバッファ領域をアクセスするロード/ストア命令の実行時におけるアドレスの更新について説明する。このとき、MDビット44は“1”とする。

【0182】

本データ処理装置では、サーキュラバッファの境界アクセス時に4バイト境界の非整置アクセスを行った場合の動作は保証していない。2ワードアクセスを行う場合は、必ず4バイト境界に整置された状態でアクセスを行う。

【0183】

図30は、2つの境界が共に4バイト整置されているサーキュラバッファの例を示す。h’は16進表記であることを示す。h’1000番地からh’11ff番地の256ワード(512バイト)がサーキュラバッファの領域になっており、MOD_L651にはバッファ領域の下限ワードアドレスであるh’1000を、MOD_U650には上限のワードアドレスであるh’11feをセットする。

【0184】

ポストインクリメント処理を行う場合、1ワードアクセス,2ワードアクセスに関係なく、第1デコーダ617から出力されるポストインクリメント信号613は“1”になるため、セレクタ614はMOD_U650の値を選択して比較器158の出力し、セレクタ615はMOD_L651の値を選択してラッチ159に出力する。

【0185】

ポストインクリメント処理で1ワードアクセスを行う場合、第1デコーダ617から出力されるポストインクリメント信号613は“1”、ポスト更新信号607は“1”、2ワードアクセス信号608は“0”、ポストデクリメント2ワードアクセス信号609(ローアクティブ)は“1”になる。

【0186】

この状態で、ベースアドレスレジスタの値がh’11feの場合、一致信号611、612が共に“1”となって選択信号610が“1”となり、その結果、セレクタ155はラッチ159に保持された値(MOD_L651の値)を選択して、D1バス311を介してレジスタファイル115のベースアドレスレジスタにh’1000を書き戻す。

【0187】

それ以外の場合には、一致信号611、612のいずれかが“0”になるため、選択信号610が“0”となり、セレクタ155はALU153の出力、すなわち、ベースアドレスレジスタの初期値に“2”が加算された値をベースアドレスレジスタに書き戻す。例えば、ベースアドレスレジスタの値がh’11fcの場合、ベースアドレスレジスタにはh’11feが書き戻される。

【0188】

ポストインクリメント処理で2ワードアクセスを行う場合、第1デコーダ617から出力されるポストインクリメント信号613は“1”、ポスト更新信号607は“1”、2ワードアクセス信号608は“1”、ポストデクリメント2ワードアクセス信号609(ローアクティブ)は“1”になる。

【0189】

この状態で、ベースアドレスレジスタの値がh’11fcの場合、一致信号611が“1”であり2ワードアクセス信号608が“1”であるため、一致信号612が“0”となっても、選択信号610が“1”となり、その結果、セレクタ155はラッチ159の出力値(セレクタ615の値)を選択してベースアドレスレジスタにh’1000を書き戻す。

【0190】

それ以外の場合には、一致信号611が“0”になり選択信号610が“0”となるため、セレクタ155はALU153の出力、すなわち、ベースアドレスレジスタの初期値に“4”が加算された値をベースアドレスレジスタに書き戻す。

【0191】

このように、実施の形態2のデータ処理装置は、サーキュラーバッファの上限ワードアドレス及び下限ワードアドレスをそれぞれMOD_U650及びMOD_L651で保持する設定で、ポストインクリメント処理で1ワードアクセスする場合にも、ポストインクリメント処理で2ワードアクセスする場合にも正しく動作する。

【0192】

ポストデクリメント処理を行う場合、1ワードアクセス,2ワードアクセスに関係なく、第1デコーダ617から出力されるポストインクリメント信号613は“0”になるため、セレクタ614はMOD_L651の値を選択して比較器158の出力し、セレクタ615はMOD_U650の値を選択してラッチ159に出力する。

【0193】

ポストデクリメント処理で1ワードアクセスを行う場合、第1デコーダ617から出力されるポストインクリメント信号613は“0”、ポスト更新信号607は“1”、2ワードアクセス信号608は“0”、ポストデクリメント2ワードアクセス信号609は“1”になる。

【0194】

この状態で、ベースアドレスレジスタの値がh’1000の場合、一致信号611、612が共に“1”となって選択信号610が“1”となり、その結果、セレクタ155はラッチ159の出力値(MOD_U650の値)を選択して、ベースアドレスレジスタに、h’11feを書き戻される。

【0195】

それ以外の場合には、一致信号611、612のいずれかが“0”になり、選択信号610が“0”となるため、セレクタ155はALU153の出力、すなわち、ベースアドレスレジスタの初期値に“2”が減算された値をベースアドレスレジスタに書き戻す。例えば、ベースアドレスレジスタの値がh’1002の場合、ベースアドレスレジスタにはh’1000が書き戻される。

【0196】

ポストデクリメント処理で2ワードアクセスを行う場合、第1デコーダ617から出力されるポストインクリメント信号613は“0”、ポスト更新信号607は“1”、2ワードアクセス信号608は“1”、ポストデクリメント2ワードアクセス信号609は“0”になる。

【0197】

この状態で、ベースアドレスレジスタの値がh’1000の場合、一致信号611、612が共に“1”となって選択信号610が“1”となり、その結果、セレクタ155はラッチ159の出力値(MOD_U650の値)を選択する。この際、ローアクティブのポストデクリメント2ワードアクセス信号609が“0”のため、ラッチ159の出力値のビット14がANDゲート603によって強制的に“0”に設定される。したがって、セレクタ155はベースアドレスレジスタに、h’11fcを書き戻す。

【0198】

それ以外の場合には、一致信号611が“0”になり選択信号610が“0”となるるため、セレクタ155はALU153の出力、すなわち、ベースアドレスレジスタの初期値に“4”が減算された値をベースアドレスレジスタに書き戻す。

【0199】

このように、実施の形態2のデータ処理装置は、ポストインクリメント処理と全く同じ値をMOD_U650及びMOD_L651に設定しても、ポストデクリメント処理で1ワードアクセスする場合にも、2ワードアクセスする場合にも正しく動作する。

【0200】

実施の形態2では、2つの境界が共に4バイト整置されているサーキュラバッファについてのみ述べたが、何れか一方が4バイト整置されていないサーキュラバッファの場合も実施の形態1と同様に正しく動作する。

【0201】

上述のように、実施の形態2のデータ処理装置は、1ワードのみならず2ワードアクセスを行う場合にも、効率の良いサーキュラーバッファのアクセスが可能となり、プログラムのコードサイズの削減、処理サイクル数の低減に寄与する。

【0202】

さらに、実施の形態1と異なり、ポストインクリメント処理,ポストデクリメント処理に関係なく、サーキュラーバッファの領域の上限及び下限のワードアドレスをMOD_U650及びMOD_L651にそれぞれ設定すれば、ポストインクリメント処理の場合にもポストデクリメント処理の場合にも正しく動作するので、インクリメント処理とデクリメント処理で制御レジスタの設定を変更する必要がなくなるため、その分、プログラムのコードサイズの削減、処理サイクル数の低減が可能となる。

【0203】

また、実施の形態2のデータ処理装置は、ポストインクリメント処理及びポストデクリメント処理時において、アドレスの計算と並列にベースアドレスの初期値に基づく判定処理可能となるため、動作周波数の向上による高速化が容易である。

【0204】

実施の形態1と同様、実施の形態2のデータ処理装置は様々な場合に、本技術は適用できる。

【0205】

上述の実施の形態2では、アドレスのビット長が16ビットの例を示したが、24ビットや32ビット等任意のビット長であってもよい。また、データの基本データ長を16ビットにしているが、24ビットにしたり、32ビットにしてもよい。また、バイトアドレスを管理しているが、16ビットや24ビット、32ビットを1ワードとして、ワードアドレスを管理してもよい。

【0206】

実施の形態2では、1ワードアクセスあるいは2ワードアクセスのポストデクリメント及びポストデクリメント処理でロード/ストア命令を実行可能なデータ処理装置について述べたが、さらに4ワード等より多くのデータを一度に転送するロード/ストア命令をインプリメントする場合にも、本発明の技術を応用して使用可能である。例えば、1ワードアクセス、2ワードアクセス及び4ワードアクセスを実行可能にする場合、3つのレベル(4ワードレベル、2ワードレベル、1ワードレベル)の一致信号を基に判定を行えばよい。

【0207】

上述の実施の形態2では、実施の形態1と同様、2ワードアクセスのポストインクリメント処理(デクリメント処理)時に一致信号611が“1”のときビット14の値を参照することなくポインタ値の入れ替えを行っているが、2ワードアクセスのポストインクリメント(デクリメント)処理で、一致信号611が“1”でかつビット14が“0”である(2ワードデータを構成する2つの1ワードデータのうち、前半の1ワードデータを特定するアドレスにポインタ値が一致する)とき、はじめてポインタ値の入れ替えを行うように構成してもよい。

【0208】

上述の実施の形態2では、MOD_U650、MOD_L651は、物理的に15ビットしか保持しないようにしているが、16ビット保持するようにし、ビット15は無視するような構成にしてもよいし、ビット15も比較に使用するように構成してもよい。比較に使用する場合には、MOD_U650,MOD_L651のビット15に必ず“0”を設定するようにして、16ビットすべてを比較するようにすればよい。

【0209】

また、MOD_U650、MOD_L651には、ワードアドレスを設定しているが、境界のバイトアドレスを設定するようにしてもよい。ビット15を無視すれば、上述の実施の形態2の動作と同じになる。

【0210】

上述の実施の形態2では、MOD_U650、MOD_L651には、アドレスの最上位ビット(MSB)までのすべてのアドレス値を保持するようになっているが、アドレスの上位数ビットは保持しないようにし、下位ビットのみで判定を行うようにすれば、複数の領域に形成された複数のサーキュラーバッファに対して、同じ設定で同時にモジュロ機構が動作するようにできる。ただし、比較しない上位ビットについては、更新前の値をそのまま出す等の処理が必要になる。

【0211】

上述の実施の形態2では、上位14ビットとビット14の2つの比較結果を出力するようにしているが、ワードアドレスがマッチしたことを示す情報と、2ワードアドレスがマッチした情報が含まれていれば、どのような形態で演算結果を出力してもよい。

【0212】

上述の実施の形態2では、一般的なプロセッサの構成を示しているが、DSPのように、アドレスレジスタとデータレジスタ(アキュムレータ等)を分けるような構成にしてもよい。また、DSPのように、複数のメモリを独立にアクセスできるような構成にしても、本発明の技術は有効である。

【0213】

上述の実施の形態2では、規定された場合以外の動作は保証していないが、上記規定された場合以外の時に例外を検出する等の処理を行ってもよい。例えば、奇数アドレスの場合にはアドレス例外を起こす等の処理を行ってもよい。

【0214】

<実施の形態3.>

実施の形態1のデータ処理装置はモジュロ・アドレッシングを利用するとき、MOD_S156にモジュロ・アドレッシング領域の最初のアドレスを、MOD_E157にモジュロ・アドレッシング領域の最後のアドレスを、各々ワードアドレスで指定する。実施の形態3では最初のアドレスと最後のアドレスを2ワードアドレスで指定するデータ処理装置について説明する。実施の形態3のデータ処理装置は、モジュロアドレッシングの制御を行う部分は実施の形態1と異なるが、その他の基本的な仕様および構成は実施の形態1と同じである。

【0215】

図31は、サーキュラバッファの領域を2ワードアドレスでセットするMOD_E850とMOD_S851を示す。MOD_E850は実施の形態1のMOD_E157に相当し、MOD_S851は実施の形態1のMOD_S156に相当する。MOD_E850及びMOD_S851は14ビットのラッチである。したがって、実施の形態1のMOD_E857及びMOD_S156に比べ、保持する情報量を1ビット省略することができる。

【0216】

MOD_E850及びMOD_S851は、インクリメント処理でモジュロアドレッシングを利用する場合には、MOD_S851に小さい方のアドレスが、MOD_E850には大きい方のアドレスがセットされ、デクリメント処理でモジュロアドレッシングを利用する場合には、MOD_S851には大きい方のアドレスが、MOD_E850には小さい方のアドレスがセットされる。この実施の形態3ではサーキュラーバッファの境界は必ず2ワード整置されていなければならない。

【0217】

図32は、実施の形態3のデータ処理装置における特徴部であるモジュロアドレッシング機能を実現する部分の構成を模式的に示す回路図である。制御部816は実施の形態1の制御部112に相当し、モジュロ演算の制御に関する部分以外はほぼ同じである。モジュロ演算部703は実施の形態1のモジュロ演算部700に相当する。各ラッチのイネーブル信号等は簡単のため省略している。また、論理図も分かりやすいように正論理で示している。

【0218】

図32以外の部分は実施の形態1とほぼ同じである。比較器852は、S3バス303で転送されるベースアドレス値とMOD_E850に保持されたモジュロ・エンド・アドレスの比較を行い、比較結果を制御部816に送る。比較器852はビット0からビット13の14ビットが一致した場合に一致信号811を“1”にし、不一致の場合には一致信号811を“0”にする。

【0219】

モジュロ・エンド・アドレスを保持するMOD_E850は14ビットのラッチであり、D1バス311からの入力ポートと、S3バス303、比較器852への出力ポートを持つ。MOD_E850の値がS3バス303に出力される場合には、ビット14、ビット15に“0”が出力される。モジュロ・スタート・アドレスを保持するMOD_S851は、14ビットのラッチであり、D1バス311からの入力ポートと、S3バス303、14ビットのラッチ853への出力ポートを持つ。MOD_S851の値がS3バス303に出力される場合には、ビット14、ビット15に“0”が出力される。

【0220】

セレクタ155は、選択信号810に基づいてALU153の出力とラッチ853に保持されたモジュロ・スタート・アドレス値を選択的にD1バス311に出力する。ラッチ853の値を選択する場合、ビット14としてポストデクリメント1ワードアクセス信号809をそのまま出力し、ビット15として“0”を出力する。ポストデクリメント1ワードアクセス信号809は第1デコーダ817で生成され、メモリアクセス命令で1ワードアクセスのポストデクリメント処理を行う場合に“1”、それ以外の場合に“0”になる信号である。

【0221】

制御部816内では、命令のデコード結果や比較器852の比較結果に基づいて、セレクタ155の選択信号810が生成される。PSW部171からは、モジュロイネーブルを指定するMDビット44の値が信号線806を介して出力される。第1デコーダ817は、上記命令デコードの結果として、ポストデクリメント1ワードアクセス信号809以外に、メモリアクセス命令でポストインクリメント及びポストデクリメント時に“1”となるポスト更新信号807、メモリアクセス命令で1ワードアクセスでポストインクリメント処理を実行する場合に“1”、それ以外の場合に“0”になるポストインクリメント1ワードアクセス信号808を出力する。

【0222】

ANDゲート801、ORゲート802、ANDゲート803、ANDゲート804、インバータ805及びインバータ812において、これらの情報を基に選択信号810が生成される。すなわち、ポストインクリメント1ワードアクセス信号808がANDゲート804に入力されるとともに、インバータ805を介してANDゲート803に入力され、S3バス303上のビット14の情報がANDゲート804に入力されるとともに、インバータ812を介してANDゲート803に入力される。そして、ORゲート802は、ANDゲート803及び804の出力の論理和をANDゲート801に出力する。ANDゲート801は、ポスト更新信号807、信号線806上に信号、ORゲート802の出力及び一致信号811の論理積を選択信号810としてセレクタ155に出力する。

【0223】

したがって、メモリアクセス命令で1ワードアクセスのポストインクリメント処理が行われる(ポストインクリメント1ワードアクセス信号808が“1”)場合、オペランドのアドレスのビット14が“1”/“0”で信号線813の“1”/“0”が決定する。一方、メモリアクセス命令で1ワードアクセスのポストインクリメント処理以外の処理が行われる(ポストインクリメント1ワードアクセス信号808が“0”)場合、オペランドのアドレスのビット14の“0”/“1”で信号線813の“1”/“0”が決定する。なお、アドレスのビット14が“1”である場合とは、アドレスのビット0〜ビット13で特定される2ワードデータを構成する2つの1ワードデータのうち、後半の1ワードデータを特定することを意味する。

【0224】

そして、モジュロ・アドレッシングがイネーブル状態(信号線806が“1”)、ポスト・インクリメント/デクリメント処理を行うロード/ストア命令処理時(ポスト更新信号807が“1”)において、S3バス303で転送されるオペランドのアドレスの上位14ビットとMOD_E850の値が一致(一致信号811が“1”)し、かつ、信号線813が“1”の場合に、選択信号810が“1”になる。上記条件を満たさない場合には、選択信号810は“0”になる。

【0225】

アドレスレジスタのポスト更新を行うロード/ストア命令実行時に、選択信号が“0”の場合には、ALU153での加減算結果がポインタの更新値として、D1バス311を介してレジスタファイル115に書き戻される。選択信号が“1”の場合には、ラッチ853に保持されたモジュロ・スタート・アドレスの値がポインタの更新値として、D1バス311を介してレジスタファイル115に書き戻される。

【0226】

モジュロ・アドレッシングがディスエーブル状態の場合には、選択信号810は必ず“0”になり、セレクタ155では常にALU153の出力が選択される。

【0227】

一例として次に、サーキュラバッファ領域をアクセスするロード/ストア命令の実行時におけるアドレスの更新について説明する。MDビット44は“1”とする。まず、ポストインクリメントでモジュロアドレッシングを使用する場合について説明する。

【0228】

本データ処理装置では、サーキュラバッファの境界アクセス時に4バイト境界の非整置アクセスを行った場合の動作は保証していない。2ワードアクセスを行う場合は、必ず4バイト境界に整置された状態でアクセスを行う。

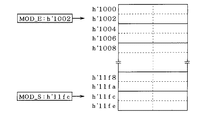

【0229】

図33は、インクリメントでアクセスする際のサーキュラバッファの例を示す説明図である。h’は16進表記であることを示す。h’1000番地からh’11ff番地の256ワード(512バイト)がサーキュラバッファの領域になっており、MOD_S851にはバッファ領域の開始の2ワードアドレスであるh’1000の上位14ビットを、MOD_E850には最後の2ワードアドレスであるh’11fcの上位14ビットをセットする。

【0230】

1ワードアクセスでポストインクリメント処理を行う場合、第1デコーダ817から出力されるポスト更新信号807は“1”、ポストインクリメント1ワードアクセス信号808は“1”、ポストデクリメント1ワードアクセス信号809は“0”になる。

【0231】

したがって、ベースアドレスレジスタの値がh’11feの場合、一致信号811が“1”、ベースアドレスレジスタのビット14が“1”となるため、選択信号810が“1”となり、セレクタ155はラッチ853に保持されたモジュロ・スタート・アドレスの値を選択し、D1バス311を介してレジスタファイル115のベースアドレスレジスタに出力する。このとき、ポストデクリメント1ワードアクセス信号809が0となるため、ベースアドレスレジスタには、h’1000が書き戻される。それ以外の場合には、信号線813が“0”となるため、セレクタ155は、ALU153の出力、すなわち、ベースアドレスレジスタの初期値に“2”が加算された値をベースアドレスレジスタに書き戻す。例えば、ベースアドレスレジスタの値がh’11fcの場合、ベースアドレスレジスタにはh’11feが書き戻される。

【0232】

2ワードアクセスでポストインクリメント処理を行う場合、第1デコーダ817から出力されるポスト更新信号807は“1”、ポストインクリメント1ワードアクセス信号808は“0”、ポストデクリメント1ワードアクセス信号809は“0”になる。

【0233】

したがって、ベースアドレスレジスタの値がh’11fcの場合、一致信号811が“1”、ベースアドレスレジスタのビット14が“0”となるため、選択信号810が“1”となり、セレクタ155はラッチ853に保持されたモジュロ・スタート・アドレスの値を選択する。このとき、ポストデクリメント1ワードアクセス信号809が“0”となるため、ベースアドレスレジスタには、h’1000が書き戻される。それ以外の場合には、一致信号811が“0”もしくはベースアドレスレジスタのビット14が“1”となるため、セレクタ155は、ALU153の出力、すなわち、ベースアドレスレジスタの初期値に“4”が加算された値をベースアドレスレジスタに書き戻す。

【0234】

このように、1ワードアクセスのポストインクリメント処理と2ワードアクセスのポストインクリメント処理との間で共通のMOD_S851及びMOD_E850の設定で、実施の形態3のデータ処理装置は、ポストインクリメント処理で1ワードアクセスする場合にも、2ワードアクセスする場合にも正しく動作する。

【0235】

図34は、ポストデクリメント処理でアクセスする際のサーキュラバッファの例を示す。h’は16進表記であることを示す。h’1000番地からh’11ff番地の256ワード(512バイト)がサーキュラバッファの領域になっており、MOD_S851にはバッファ領域の開始の2ワードアドレスであるh’11fcの上位14ビットを、MOD_E850には最後の2ワードアドレスであるh’1000の上位14ビットをセットする。

【0236】

1ワードアクセスのポストデクリメント処理を行う場合、第1デコーダ817から出力されるポスト更新信号807は“1”、ポストインクリメント1ワードアクセス信号808は“0”、ポストデクリメント1ワードアクセス信号809は“1”になる。

【0237】

したがって、ベースアドレスレジスタの値がh’1000の場合、一致信号811が“1”、ベースアドレスレジスタのビット14が“0”となるため、選択信号810が“1”となり、セレクタ155はラッチ853で保持されたモジュロ・スタート・アドレスの値を選択する。このとき、ポストデクリメント1ワードアクセス信号809が“1”となるため、ベースアドレスレジスタには、h’11feが書き戻される。それ以外の場合には、一致信号811が“0”もしくはベースアドレスレジスタのビット14が“1”となるため、セレクタ155は、ALU153の出力、すなわち、ベースアドレスレジスタの初期値に“2”が減算された値をベースアドレスレジスタに書き戻す。例えば、ベースアドレスレジスタの値がh’1002の場合、ベースアドレスレジスタにはh’1000が書き戻される。

【0238】

2ワードアクセスのポストデクリメント処理を行う場合、第1デコーダ817から出力されるポスト更新信号807は“1”、ポストインクリメント1ワードアクセス信号808は“0”、ポストデクリメント1ワードアクセス信号809は“0”になる。ベースアドレスレジスタの値がh’1000の場合、一致信号811が“1”、ベースアドレスレジスタのビット14が“0”となるため、選択信号810が“1”となり、セレクタ155はラッチ853に保持されたモジュロ・スタート・アドレスの値を選択する。このとき、ポストデクリメント1ワードアクセス信号809が“0”となるため、ベースアドレスレジスタには、h’11fcが書き戻される。それ以外の場合には、一致信号811が“0”もしくはベースアドレスレジスタのビット14が“1”となるため、セレクタ155は、ALU153の出力、すなわち、ベースアドレスレジスタの初期値に“4”が減算された値をベースアドレスレジスタに書き戻す。

【0239】

このように、1ワードアクセスのポストデクリメント処理と2ワードアクセスのポストデクリメント処理との間で共通のMOD_S851及びMOD_E850の設定で、実施の形態3のデータ処理装置は、ポストデクリメント処理で1ワードアクセスする場合にも、2ワードアクセスする場合にも正しく動作する。

【0240】

上述のように、必ず2ワード単位でサーキュラバッファを構成するという制限は加わるが、実施の形態3のデータ処理装置は、実施の形態1と同様、ポストインクリメント処理あるいはポストデクリメント処理によって1ワードのみならず2ワードアクセスを行う場合にも、効率の良いサーキュラーバッファのアクセスが可能となり、プログラムのコードサイズの削減、処理サイクル数の低減に寄与する。

【0241】

また、実施の形態3のデータ処理装置は、ポストインクリメント処理及びポストデクリメント処理時において、アドレスの計算と並列にベースアドレスの初期値に基づく判定処理可能となるため、動作周波数の向上による高速化が容易である。

【0242】

実施の形態1と同様、上述の実施の形態3で説明した様々な場合にも、本発明は適用できる。

【0243】

上述の実施の形態3では、アドレスのビット長が16ビットの例を示したが、24ビットや32ビット等任意のビット長であってもよい。また、データの基本データ長を16ビットにしているが、24ビットにしたり、32ビットにしてもよい。また、バイトアドレスを管理しているが、16ビットや24ビット、32ビットを1ワードとして、ワードアドレスを管理してもよい。

【0244】

上述の実施の形態3では、1ワードアクセスと2ワードアクセスの場合について述べたが、4ワード等より多くのデータを一度に転送するロード/ストア命令をインプリメントする場合にも同じ技術が使用可能である。4ワード転送の場合、MOD_E850、MOD_S851に4ワードアドレスを設定し、ビット13、14を別途判定するようにすればよい。

【0245】

上述の実施の形態3では、アドレスの上位15ビットのみで判定を行っているが、ビット15が“0”であることを判定条件に追加してもよい。

【0246】

上述の実施の形態3では、MOD_E850、MOD_S851は、物理的に14ビットしか保持しないようにしているが、16ビット保持するようにし、ビット14及びビット15は無視するような構成にしてもよいし、比較に使用するように構成してもよい。比較に使用する場合には、MOD_S851のビット14及びビット15に必ず“0”を設定するようにして、16ビットすべてを比較するようにすればよい。

【0247】

また、MOD_E850、MOD_S851には、ワードアドレスを設定しているが、境界のバイトアドレスを設定するようにしてもよい。ビット15を無視すれば、上述の実施の形態3の動作と同じになる。

【0248】

上述の実施の形態3では、MOD_E850、MOD_S851には、アドレスの最上位ビット(MSB)までのすべてのアドレス値を保持するようになっているが、アドレスの上位数ビットは保持しないようにし、下位ビットのみで判定を行うようにすれば、複数の領域に形成された複数のサーキュラーバッファに対して、同じ設定で同時にモジュロ機構が動作するようにできる。ただし、比較しない上位ビットについては、更新前の値をそのまま出す等の処理が必要になる。

【0249】

上述の実施の形態3では、インクリメント時にもデクリメント時にも動作可能な実施例が示されているが、インクリメント時のみあるいはデクリメント時にのみ動作するようにしてもよい。

【0250】

上述の実施の形態3では、一般的なプロセッサの構成を示しているが、DSPのように、アドレスレジスタとデータレジスタ(アキュムレータ等)を分けるような構成にしてもよい。また、DSPのように、複数のメモリを独立にアクセスできるような構成にしても、本技術は有効である。

【0251】

上述の実施の形態3では、規定された場合以外の動作は保証していないが、上記規定された場合以外の時に例外を検出する等の処理を行ってもよい。例えば、奇数アドレスの場合にはアドレス例外を起こす等の処理を行ってもよい。

【0252】

<実施の形態4.>

実施の形態2のデータ処理装置はモジュロ・アドレッシングを利用するとき、MOD_U650にモジュロ・アドレッシング領域の上限のアドレスを、MOD_L651にモジュロ・アドレッシング領域の下限のアドレスを、各々ワードアドレスで指定する。実施の形態4では上限のアドレスと下限のアドレスを2ワードアドレスで指定するデータ処理装置について説明する。モジュロアドレッシングの制御を行う部分は実施の形態2と異なるが、その他の基本的な仕様および構成は実施の形態2と同じである。

【0253】

図35は、サーキュラバッファのアドレスを2ワードアドレスでセットするMOD_U950とMOD_L951を示す。MOD_U950は実施の形態2のMOD_U650に相当し、MOD_L951は実施の形態2のMOD_L651に相当する。MOD_U950は14ビットのラッチで、モジュロ演算の対象となる領域の上限のアドレスが2ワードアドレスでセットされる。MOD_L951は14ビットのラッチで、モジュロ演算の対象となる領域の下限のアドレスが2ワードアドレスでセットされる。但し、下限のアドレスは上限のアドレスより小さいアドレスである。したがって、実施の形態4のMOD_U950及びMOD_L951は、実施の形態2のMOD_U650及びMOD_L651に比べ、保持する情報量を1ビット省略することができる。

【0254】

MOD_U950、MOD_L9651に保持されないビット14、ビット15は“0”固定であり、書き込み時は無視され、読み出し時は常に“0”となる。この実施の形態ではサーキュラーバッファの境界は必ず2ワード整置されていなければならない。

【0255】

図36は、実施の形態4のデータ処理装置の特徴部であるモジュロアドレッシング機能を実現する部分の構成模式的に示す回路図である。制御部916は実施の形態1の制御部112に相当し、モジュロ演算の制御に関する部分以外はほぼ同じである。モジュロ演算部704は実施の形態1のモジュロ演算部700に相当する。各ラッチのイネーブル信号等は簡単のため省略している。また、論理図も分かりやすいように正論理で示している。図36以外の部分は実施の形態1とほぼ同じである。

【0256】

セレクタ952は、第1デコーダ917で生成されるポストインクリメント信号913で制御される。ポストインクリメント信号913はメモリアクセス命令でポスト・インクリメント時に“1”、ポストデクリメント時に“0”となる。セレクタ952は、ポストインクリメント信号913が“1”でポストインクリメントを指示する場合にMOD_U950の値を選択して比較器954に出力し、ポストインクリメント信号913が“0”でポストデクリメントを指示する場合にMOD_L951の値を選択して比較器954に出力される。

【0257】

比較器954は、S3バス303で転送されるベースアドレス値とセレクタ952から出力されたアドレスとの比較を行い、比較結果である一致信号911を制御部916に送る。この際、ビット0からビット13の上位14ビットが一致した場合に一致信号911が“1”になり、不一致の場合には一致信号911が“0”になる。

【0258】

サーキュラバッファの上限アドレスを保持するMOD_U950は14ビットのラッチであり、D1バス311からの入力ポートと、S3バス303、セレクタ952、セレクタ953への出力ポートを持つ。MOD_U950の値がS3バス303に出力される場合には、ビット14、ビット15に“0”が出力される。

【0259】

サーキュラバッファの下限アドレスを保持するMOD_L951は、14ビットのラッチであり、D1バス311からの入力ポートと、S3バス303、セレクタ952、セレクタ953への出力ポートを持つ。MOD_L951の値がS3バス303に出力される場合には、ビット14、ビット15に“0”が出力される。

【0260】

セレクタ953は、第1デコーダ917で生成されるポストインクリメント信号913で制御される。すなわち、セレクタ953はポストインクリメント信号913が“1”でポストインクリメント処理を指示する場合にはMOD_L951の値を選択してラッチ955に出力し、ポストインクリメント信号913が“0”でポストデクリメント処理を指示する場合にはMOD_U950の値を選択してラッチ955に出力する。

【0261】

セレクタ155は、選択信号910に基づいてALU153の出力とラッチ955に保持されたアドレス値を選択的にD1バス311に出力する。このとき、ラッチ955の値を選択する場合、ビット14としてポストデクリメント1ワードアクセス信号909をそのまま出力し、ビット15として“0”を出力する。ポストデクリメント1ワードアクセス信号909は第1デコーダ917で生成され、メモリアクセス命令(ロード/ストア命令)が1ワードアクセスのポストデクリメント処理を行う場合に“1”、それ以外の場合に“0”になる。

【0262】

制御部916内では、命令のデコード結果や比較器954の比較結果に基づいて、セレクタ155に出力する選択信号910が生成される。PSW部171からは、モジュロイネーブルを指定するMDビット44の値が信号線906で出力される。第1デコーダ917からは命令デコードの結果として、メモリアクセス命令でポスト・インクリメント/デクリメント時に“1”となるポスト更新信号907、メモリアクセス命令で1ワードアクセスでポスト・インクリメントの際に“1”、それ以外の場合に“0”になるポストインクリメント1ワードアクセス信号908が出力される。

【0263】

ANDゲート901、ORゲート902、ANDゲート903、ANDゲート904、インバータ905及びインバータ912において、これらの情報を基に選択信号910が生成される。すなわち、ポストインクリメント1ワードアクセス信号908がANDゲート904に入力されるとともに、インバータ905を介してANDゲート903に入力され、S3バス303上のビット14の情報がANDゲート904に入力されるとともに、インバータ812を介してANDゲート903に入力される。そして、ORゲート902は、ANDゲート903及び904の出力の論理和をANDゲート901に出力する。ANDゲート901は、ポスト更新信号907、信号線906上に信号、ORゲート902の出力及び一致信号911の論理積を選択信号910としてセレクタ155に出力する。

【0264】

したがって、メモリアクセス命令で1ワードアクセスのポストインクリメント処理が行われる(ポストインクリメント1ワードアクセス信号908が“1”)場合、オペランドのアドレスのビット14が“1”/“0”で信号線914の“1”/“0”が決定する。一方、メモリアクセス命令で1ワードアクセスのポストインクリメント処理以外の処理が行われる(ポストインクリメント1ワードアクセス信号908が“0”)場合、オペランドのアドレスのビット14の“0”/“1”で信号線914の“1”/“0”が決定する。

【0265】

そして、モジュロ・アドレッシングがイネーブル状態(信号線906が“1”)、ポスト・インクリメント/デクリメント処理を行うロード/ストア命令処理時(ポスト更新信号907が“1”)において、S3バス303で転送されるオペランドのアドレスの上位14ビットとセレクタ952の出力値とが一致(一致信号911が“1”)し、かつ、信号線914が“1”の場合に、選択信号910が“1”になる。上記条件を満たさない場合には、選択信号910は“0”になる。

【0266】

アドレスレジスタのポスト更新を行うロード/ストア命令実行時に、選択信号910が“0”の場合には、ALU153での加減算結果がポインタの更新値として、D1バス311を介してレジスタファイル115に書き戻される。選択信号910が“1”の場合には、ラッチ955に保持されたアドレスの値がポインタの更新値として、D1バス311を介してレジスタファイル115に書き戻される。

【0267】

また、モジュロ・アドレッシングがディスエーブル状態の場合には、選択信号910は必ず“0”になり、セレクタ155では常にALU153の出力が選択される。

【0268】

一例として次に、サーキュラバッファ領域をアクセスするロード/ストア命令の実行時におけるアドレスの更新について説明する。MDビット44は“1”とする。

【0269】

本データ処理装置では、サーキュラバッファの境界アクセス時に4バイト境界の非整置アクセスを行った場合の動作は保証していない。2ワードアクセスを行う場合は、必ず4バイト境界に整置された状態でアクセスを行う。

【0270】

図37は、サーキュラバッファの例を示す説明図である。h’は16進表記であることを示す。h’1000番地からh’11ff番地の256ワード(512バイト)がサーキュラバッファの領域になっており、MOD_L951にはバッファ領域の下限2ワードアドレスであるh’1000の上位14ビットを、MOD_U950には上限の2ワードアドレスであるh’11fcの上位14ビットをセットする。

【0271】

ポストインクリメント処理を行う場合、1ワードアクセス,2ワードアクセスに関係なく、第1デコーダ917から出力されるポストインクリメント信号913は“1”になるため、セレクタ952はMOD_U950の値を選択して比較器954に出力し、セレクタ953はMOD_L951の値を選択してラッチ955に出力する。

【0272】

1ワードアクセスのポストインクリメント処理を行う場合、第1デコーダ917から出力されるポストインクリメント信号913は“1”、ポスト更新信号907は“1”、ポストインクリメント1ワードアクセス信号908は“1”、ポストデクリメント1ワードアクセス信号909は“0”になる。

【0273】

この状態で、ベースアドレスレジスタの値がh’11feの場合、一致信号911が“1”、ベースアドレスレジスタのビット14が“1”となるため、選択信号910が“1”となる。その結果、セレクタ155はラッチ955の値(MOD_L951の値)を選択してベースアドレスレジスタに、h’1000を書き戻す。それ以外の場合には、アドレス変更信号914が“0”となるため、セレクタ155は、ALU153の出力、すなわち、ベースアドレスレジスタの初期値に“2”が加算された値をベースアドレスレジスタに書き戻す。例えば、ベースアドレスレジスタの値がh’11fcの場合、ベースアドレスレジスタにはh’11feが書き戻される。

【0274】

2ワードアクセスのポストインクリメント処理を行う場合、第1デコーダ917から出力されるポストインクリメント信号913は“1”、ポスト更新信号907は“1”、ポストインクリメント1ワードアクセス信号908は“0”、ポストデクリメント1ワードアクセス信号909は“0”になる。

【0275】

この状態で、ベースアドレスレジスタの値がh’11fcの場合、一致信号911が“1”、ベースアドレスレジスタのビット14が“0”となるため、選択信号910が“1”となる。その結果、セレクタ155はラッチ955の値(MOD_L951の値)を選択してベースアドレスレジスタにh’1000を書き戻す。それ以外の場合には、アドレス変更信号914が“0”となるため、セレクタ155は、ALU153の出力、すなわち、ベースアドレスレジスタの初期値に“4”が加算された値をベースアドレスレジスタに書き戻す。

【0276】

このように、実施の形態4のデータ処理装置は、サーキュラーバッファの上限ワードアドレス及び下限ワードアドレスをそれぞれMOD_U650及びMOD_L651で保持する設定で、ポストインクリメント処理で1ワードアクセスする場合にも、ポストインクリメント処理で2ワードアクセスする場合にも正しく動作する。

【0277】

ポストデクリメント処理を行う場合、1ワードアクセス,2ワードアクセスに関係なく、第1デコーダ917から出力されるポストインクリメント信号913は“0”になるため、セレクタ952はMOD_L951の値を選択して比較器954に出力し、セレクタ953はMOD_U950の値を選択してラッチ955に出力する。

【0278】

ポストデクリメント1ワードアクセスを行う場合、第1デコーダ917から出力されるポストインクリメント信号913は“0”、ポスト更新信号907は“1”、ポストインクリメント1ワードアクセス信号908は“0”、ポストデクリメント1ワードアクセス信号909は“1”になる。

【0279】

この状態で、ベースアドレスレジスタの値がh’1000の場合、一致信号911が“1”、ベースアドレスレジスタのビット14が“0”となるため、選択信号910が“1”となる。その結果、セレクタ155はラッチ955の値(MOD_U950の値)を選択する。このとき、ポストデクリメント1ワードアクセス信号909が“1”のため、セレクタ155はビット14の出力として“1”を出力する。したがって、セレクタ155はベースアドレスレジスタにh’11feを書き戻す。それ以外の場合には、アドレス変更信号914が“0”となるため、セレクタ155は、ALU153の出力、すなわち、ベースアドレスレジスタの初期値に“2”が減算された値をベースアドレスレジスタに書き戻す。例えば、ベースアドレスレジスタの値がh’1002の場合、ベースアドレスレジスタにはh’1000が書き戻される。

【0280】

2ワードアクセスのポストデクリメント処理を行う場合、第1デコーダ917から出力されるポストインクリメント信号913は“0”、ポスト更新信号907は“1”、ポストインクリメント1ワードアクセス信号908は“0”、ポストデクリメント1ワードアクセス信号909は“0”になる。

【0281】

この状態で、ベースアドレスレジスタの値がh’1000の場合、一致信号911が“1”、ベースアドレスレジスタのビット14が“0”となるため、選択信号910が“1”となる。その結果、セレクタ155はラッチ955の値(MOD_U950の値)を選択してベースアドレスレジスタに、h’11fcを書き戻す。それ以外の場合には、アドレス変更信号914が“0”となるため、セレクタ155は、ALU153の出力、すなわち、ベースアドレスレジスタの初期値に“4”が減算された値をベースアドレスレジスタに書き戻す。

【0282】

このように、実施の形態4のデータ処理装置は、ポストインクリメント処理と全く同じ値をMOD_U650及びMOD_L651に設定しても、ポストデクリメント処理で1ワードアクセスする場合にも、2ワードアクセスする場合にも正しく動作する。

【0283】

上述のように、必ず2ワード単位でサーキュラバッファを構成するという制限は加わるが、実施の形態4のデータ処理装置は、実施の形態2と同様に1ワードのみならず2ワードアクセスを行う場合にも、効率の良いサーキュラーバッファのアクセスが可能となり、プログラムのコードサイズの削減、処理サイクル数の低減に寄与する。いずれの場合も、ポストインクリメント/ポストデクリメントを意識せずにサーキュラーバッファの上限アドレスと下限アドレスを2ワードアドレスで設定すればよいので、設定が統一されており、分かりやすい。

【0284】

また、実施の形態4のデータ処理装置は、ポストインクリメント処理及びポストデクリメント処理時において、アドレスの計算と並列にベースアドレスの初期値に基づく判定処理可能となるため、動作周波数の向上による高速化が容易である。

【0285】

実施の形態1と同様、上述の実施の形態4で説明した様々な場合にも、本発明を適用できる。

【0286】

上述の実施の形態4では、アドレスのビット長が16ビットの例を示したが、24ビットや32ビット等任意のビット長であってもよい。また、データの基本データ長を16ビットにしているが、24ビットにしたり、32ビットにしてもよい。また、バイトアドレスを管理しているが、16ビットや24ビット、32ビットを1ワードとして、ワードアドレスを管理してもよい。

【0287】

上述の実施の形態4では、1ワードアクセスと2ワードアクセスの場合について述べたが、4ワード等より多くのデータを一度に転送するロード/ストア命令をインプリメントする場合にも同じ技術が使用可能である。4ワード転送の場合、MOD_U950、MOD_L951に4ワードアドレスを設定し、ビット13、14を別途判定するようにすればよい。

【0288】

上述の実施の形態4では、アドレスの上位15ビットのみで判定を行っているが、ビット15が“0”であることを判定条件に追加してもよい。

【0289】

上述の実施の形態4では、MOD_E950、MOD_S951は、物理的に14ビットしか保持しないようにしているが、16ビット保持するようにし、ビット14及びビット15は無視するような構成にしてもよいし、比較に使用するように構成してもよい。比較に使用する場合には、MOD_S951のビット14及びビット15に必ず“0”を設定するようにして、16ビットすべてを比較するようにすればよい。

【0290】

また、MOD_U950、MOD_L951には、ワードアドレスを設定しているが、境界のバイトアドレスを設定するようにしてもよい。ビット15を無視すれば、上述の実施の形態4の動作と同じになる。

【0291】

上述の実施の形態4では、MOD_U950、MOD_L951には、アドレスの最上位ビット(MSB)までのすべてのアドレス値を保持するようになっているが、アドレスの上位数ビットは保持しないようにし、下位ビットのみで判定を行うようにすれば、複数の領域に形成された複数のサーキュラーバッファに対して、同じ設定で同時にモジュロ機構が動作するようにできる。ただし、比較しない上位ビットについては、更新前の値をそのまま出す等の処理が必要になる。

【0292】

上述の実施の形態4では、一般的なプロセッサの構成を示しているが、DSPのように、アドレスレジスタとデータレジスタ(アキュムレータ等)を分けるような構成にしてもよい。また、DSPのように、複数のメモリを独立にアクセスできるような構成にしても、本技術は有効である。

【0293】

上述の実施の形態4では、規定された場合以外の動作は保証していないが、上記規定された場合以外の時に例外を検出する等の処理を行ってもよい。例えば、奇数アドレスの場合にはアドレス例外を起こす等の処理を行ってもよい。

【0294】

<実施の形態5.>

実施の形態2のデータ処理装置ではモジュロ・アドレッシングを利用するとき、MOD_U650にモジュロ・アドレッシング領域の上限のアドレス、MOD_L651にモジュロ・アドレッシング領域の下限のアドレスをワードアドレスで指定する。実施の形態5のデータ処理装置では上限のアドレスと下限のアドレスを1ワードアドレスで指定する点は実施の形態2と同じであるが、実施の形態2と異なり1ワードアクセスのポストインクリメント処理と1ワードアクセスのポストデクリメントのみを処理対象としている。モジュロアドレッシングの制御を行う部分は実施の形態2と異なるが、その他の基本的な仕様および構成は実施の形態2と同じである。

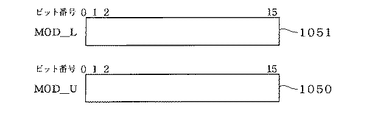

【0295】

図38は、サーキュラバッファの上限及び下限アドレスを1ワードアドレスでセットするMOD_U1050とMOD_L1051を示す。MOD_U1050は実施の形態2のMOD_U650に相当し、MOD_L1051は実施の形態2のMOD_L651に相当する。MOD_U1050は16ビットのラッチで、モジュロ演算の対象となる領域の上限のアドレスの1ワードアドレスがセットされる。MOD_L1051は16ビットのラッチで、モジュロ演算の対象となる領域の下限のアドレスの1ワードアドレスがセットされる。但し、下限のアドレスは上限のアドレスより小さいアドレスである。モジュロアドレッシングを機能させる場合、MOD_U1050とMOD_L1051のビット15には、必ず“0”がセットされなければならない。

【0296】

図39は、実施の形態5のデータ処理装置の特徴部であるモジュロアドレッシング機能を実現する部分の構成を示す模式的に示した回路図である。制御部1016は実施の形態1の制御部112に相当し、モジュロ演算の制御に関する部分以外はほぼ同じである。モジュロ演算部705は実施の形態1のモジュロ演算部700に相当する。各ラッチのイネーブル信号等は簡単のため省略している。また、論理図も分かりやすいように正論理で示している。図39以外の部分は実施の形態1とほぼ同じである。

【0297】

セレクタ1052は、第1デコーダ1017で生成されるポストインクリメント信号1013で制御される。ポストインクリメント信号1013はメモリアクセス命令でポスト・インクリメント時に1、ポスト・デクリメント時に“0”となる。したがって、セレクタ1052は、ポストインクリメント信号1013が“1”でポストインクリメント処理を指示する場合にはMOD_U1050の値を選択して比較器1054に出力し、ポストインクリメント信号1013が“0”でポストデクリメント処理を指示するの場合にはMOD_L1051の値を選択して比較器1054に出力する。

【0298】

比較器1054は、S3バス303で転送されるベースアドレス値とセレクタ1052から出力されたアドレスとの比較を行い、比較結果を一致信号1011として制御部1016に送る。この際、ビット0からビット15が一致した場合に一致信号1011が“1”になり、不一致の場合には一致信号1011が“0”になる。

【0299】

サーキュラバッファの上限アドレスを保持するMOD_U1050は16ビットのラッチであり、D1バス311からの入力ポートと、S3バス303、セレクタ1052、セレクタ1053への出力ポートを持つ。サーキュラバッファの下限アドレスを保持するMOD_L1051は、16ビットのラッチであり、D1バス311からの入力ポートと、S3バス303、セレクタ1052、セレクタ1053への出力ポートを持つ。

【0300】

セレクタ1053は、第1デコーダ1017で生成されるポストインクリメント信号1013で制御される。すなわち、セレクタ1053は、ポストインクリメント信号1013が“1”でポストインクリメントを指示する場合にはMOD_L1051の値が選択してラッチ1055に出力し、ポストインクリメント信号1013が“0”でポストデクリメントを指示する場合にはMOD_U1050の値を選択してラッチ1055に出力する。

【0301】

セレクタ1060は、選択信号1010に基づいてALU153の出力あるいはラッチ1055に保持されたアドレス値を選択的にD1バス311に出力する。制御部1016内では、命令のデコード結果や比較器1054の比較結果に基づいて、セレクタ1060の選択信号1010が生成される。PSW部171からは、モジュロイネーブルを指定するMDビット44の値が信号線1006で出力される。第1デコーダ1017からは命令デコードの結果として、メモリアクセス命令でポスト・インクリメント/デクリメント時に“1”となるポスト更新信号1007が出力される。

【0302】

ANDゲート1001において、これらの情報を基に選択信号1010が生成される。すなわち、ANDゲート1001は、ポスト更新信号1007、信号線1006上の信号及び一致信号1011の論理積を演算して選択信号1010を出力する。

【0303】

モジュロ・アドレッシングがイネーブル状態(信号線1006が“1”)、かつ、ポスト・インクリメント/デクリメントを行うロード/ストア命令処理時(ポスト更新信号1007が“1”)で、S3バス303で転送されるオペランドのアドレスとセレクタ1052で選択されたアドレスが一致し(一致信号1011が“1”)した場合に、選択信号1010が“1”になる。条件を満たさない場合には、選択信号1010は“0”になる。

【0304】

アドレスレジスタのポスト更新を行うロード/ストア命令実行時に、選択信号が“0”の場合には、ALU153での加減算結果がポインタの更新値として、D1バス311を介してレジスタファイル115に書き戻される。選択信号が“1”の場合には、ラッチ955に保持されたアドレスの値がポインタの更新値として、D1バス311を介してレジスタファイル115に書き戻される。モジュロ・アドレッシングがディスエーブル状態の場合には、選択信号1010は必ず“0”になり、セレクタ1060では常にALU153の出力が選択される。

【0305】

一例として次に、サーキュラバッファ領域をアクセスするロード/ストア命令の実行時におけるアドレスの更新について説明する。MDビット44は“1”とする。

【0306】

実施の形態5のデータ処理装置は、必ず1ワードアクセスでサーキュラーバッファをアクセスする。

【0307】

図40は、サーキュラバッファの例を示す説明図である。実施の形態5のデータ処理装置では、サーキュラーバッファ領域はワード整置されておればよく、2ワード整置条件とは関係なく同じ動作をする。h’は16進表記であることを示す。h’1000番地からh’11ff番地の256ワード(512バイト)がサーキュラバッファの領域になっており、MOD_L1051にはバッファ領域の下限の1ワードアドレスであるh’1000を、MOD_U1050には上限の1ワードアドレスであるh’11feをセットする。

【0308】

ポストインクリメント処理を行う場合、第1デコーダ1017から出力されるポストインクリメント信号1013は“1”になるため、セレクタ1052はMOD_U1050の値を選択して比較器1054に出力し、セレクタ1053はMOD_L1051の値を選択してラッチ1055に出力する。

【0309】

1ワードアクセスのポストインクリメント処理を行う場合、第1デコーダ1017から出力されるポストインクリメント信号1013は“1”、ポスト更新信号1007は“1”になる。

【0310】

この状態で、ベースアドレスレジスタの値がh’11feの場合、一致信号1011が“1”となるため、選択信号1010が“1”となる。その結果、セレクタ1060はラッチ1055の値(MOD_L1051の値)を選択してベースアドレスレジスタに、h’1000を書き戻す。それ以外の場合には、一致信号1011が“0”となるため、セレクタ1060はALU153の出力、すなわち、ベースアドレスレジスタの初期値に“2”が加算された値をベースアドレスレジスタに書き戻す。例えば、ベースアドレスレジスタの値がh’11fcの場合、ベースアドレスレジスタにはh’11feが書き戻される。

【0311】

ポストインクリメント処理を行う場合、第1デコーダ1017から出力されるポストインクリメント信号1013は“0”になるため、セレクタ1052はMOD_L1051の値を選択して比較器1054に出力し、セレクタ1053はMOD_U1050の値を選択してラッチ1055に出力する。

【0312】

ポストデクリメント1ワードアクセスを行う場合、第1デコーダ1017から出力されるポストインクリメント信号1013は“0”、ポスト更新信号1007は“1”になる。

【0313】

この状態で、ベースアドレスレジスタの値がh’1000の場合、一致信号1011が“1”となるため、選択信号1010が“1”となる。その結果、セレクタ1060はラッチ1055の値(MOD_U1050の値)を選択してベースアドレスレジスタにh’11feを書き戻す。それ以外の場合には、一致信号1011が“0”となるため、セレクタ1060は、ALU153の出力、すなわち、ベースアドレスレジスタの初期値に“2”が減算された値をベースアドレスレジスタに書き戻す。例えば、ベースアドレスレジスタの値がh’1002の場合、ベースアドレスレジスタにはh’1000が書き戻される。

【0314】

このように、同じMOD_U1050及びMOD_L1051の設定で、実施の形態5のデータ処理装置は、ポストインクリメント1ワードアクセスする場合にも、ポストデクリメント1ワードアクセスする場合にも正しく動作する。

【0315】

このように、実施の形態5のデータ処理装置は、ポストインクリメント処理と全く同じ値をMOD_U650及びMOD_L651に設定しても、ポストデクリメント処理を正しく実行することができる。

【0316】

上述のように、1ワードのみにしかモジュロ機構が機能しないと言う制限は加わるが、実施の形態5のデータ処理装置は、実施の形態4と同様に効率の良いサーキュラーバッファのアクセスが可能となり、プログラムのコードサイズの削減、処理サイクル数の低減に寄与する。

【0317】

ポストインクリメント/ポストデクリメントを意識せずにサーキュラーバッファの上限アドレスと下限アドレスを1ワードアドレスで設定すればよいので、設定が統一されており、分かりやすい。

【0318】

また、実施の形態5のデータ処理装置は、ポストインクリメント処理及びポストデクリメント処理時において、アドレスの計算と並列にベースアドレスの初期値に基づく判定処理可能となるため、動作周波数の向上による高速化が容易である。

【0319】

実施の形態1と同様、上述の実施の形態5で説明した様々な場合にも、本発明は適用できる。

【0320】

上述の実施の形態5では、アドレスのビット長が16ビットの例を示したが、24ビットや32ビット等任意のビット長であってもよい。また、データの基本データ長を16ビットにしているが、24ビットにしたり、32ビットにしてもよい。また、バイトアドレスを管理しているが、16ビットや24ビット、32ビットを1ワードとして、ワードアドレスを管理してもよい。

【0321】

上述の実施の形態5では、1ワードアクセスのみをモジュロアドレッシングの処理対象としているが、2ワードアクセスのみあるいは4ワードアクセスのみ等を他のアクセスサイズを処理対象にしてもよい。例えば、2ワードアクセスのみの場合、MOD_U1050、MOD_L1051に2ワードアドレスを設定し、管理するようにすればよい。

【0322】

上述の実施の形態5では、アドレスの16ビットすべてで比較判定を行う例を示したが、上位15ビットのみで判定を行うようにしてもよい。

【0323】

上述の実施の形態5では、MOD_U1050、MOD_L1051は、物理的に16ビット持っているが、上位15ビットのみを保持するようにして、15ビットの比較を行うようにしてもよい。奇数アドレス時の動作を保証しない場合、どのように動作してもかまわない。

【0324】

上述の実施の形態5では、MOD_U1050、MOD_L1051には、アドレスの最上位ビット(MSB)までのすべてのアドレス値を保持するようになっているが、アドレスの上位数ビットは保持しないようにし、下位ビットのみで判定を行うようにすれば、複数の領域に形成された複数のサーキュラーバッファに対して、同じ設定で同時にモジュロ機構が動作するようにできる。ただし、比較しない上位ビットについては、更新前の値をそのまま出す等の処理が必要になる。

【0325】

上述の実施の形態5では、一般的なプロセッサの構成を示しているが、DSPのように、アドレスレジスタとデータレジスタ(アキュムレータ等)を分けるような構成にしてもよい。また、DSPのように、複数のメモリを独立にアクセスできるような構成にしても、本技術は有効である。

【0326】

上述の実施の形態5では、規定された場合以外の動作は保証していないが、上記規定された場合以外の時に例外を検出する等の処理を行ってもよい。例えば、奇数アドレスの場合にはアドレス例外を起こす等の処理を行ってもよい。

【0327】

【発明の効果】

この発明における請求項1記載のデータ処理装置のアクセスアドレス決定手段は、第1のメモリアクセス命令の処理時には、終了アドレス情報が指示するアドレスとアクセスアドレスとの間で、nビットデータを特定するアドレス部分が等価であるという第1の条件が成立すると判定すると、開始アドレス情報の指示するアドレスに関連し、かつサーキュラーバッファ領域上のnビットデータを特定可能なnビットアクセスアドレスを次期アクセスアドレスとし、第1の条件が不成立であると判定すると、演算アドレスを次期アクセスアドレスとし、第2のメモリアクセス命令の処理時には、終了アドレス情報が指示するアドレスとアクセスアドレスとの間で、2nビットデータを特定するアドレス部分が等価であるという第2の条件が成立すると判定すると、開始アドレス情報の指示するアドレスに関連し、かつサーキュラーバッファ領域上の2nビットデータを特定可能な2nビットアクセスアドレスを次期アクセスアドレスとし、第2の条件が不成立であると判定すると、演算アドレスを次期アクセスアドレスとしている。

【0328】

したがって、nビットデータ単位でアクセスする第1のメモリアクセス命令と2nビットデータ単位でアクセスする第2のメモリアクセス命令とで共通の開始アドレス情報及び終了アドレス情報を与えるだけで、請求項1記載のデータ処理装置は、第1及び第2のメモリアクセス命令を混在して実行しても、サーキュラーバッファ領域上を効率的にモジュロアドレッシング(巡回アドレッシング)することができる。

【0329】

請求項2記載のデータ処理装置において、第1及び第2のメモリアクセス命令はそれぞれアドレス更新をアドレスを増加させて行う第1及び第2のインクリメント処理を含み、アドレス更新方向はアドレスが増加する方向に規定される。

【0330】

したがって、開始アドレス情報が指示するアドレスをサーキュラーバッファ領域の下限アドレスとし、終了アドレス情報が指示するアドレスをサーキュラーバッファ領域の上限アドレスとして設定することにより、請求項2記載のデータ処理装置は、サーキュラーバッファ領域上の下限アドレスから上限アドレスにかけて効率的にモジュロアドレッシングすることができる。

【0331】