JP3704094B2 - リセット信号発生回路 - Google Patents

リセット信号発生回路 Download PDFInfo

- Publication number

- JP3704094B2 JP3704094B2 JP2002028426A JP2002028426A JP3704094B2 JP 3704094 B2 JP3704094 B2 JP 3704094B2 JP 2002028426 A JP2002028426 A JP 2002028426A JP 2002028426 A JP2002028426 A JP 2002028426A JP 3704094 B2 JP3704094 B2 JP 3704094B2

- Authority

- JP

- Japan

- Prior art keywords

- reset signal

- power supply

- voltage

- circuit

- supply voltage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 title claims description 23

- 230000003287 optical effect Effects 0.000 claims description 9

- 238000010586 diagram Methods 0.000 description 15

- 230000007423 decrease Effects 0.000 description 6

- 239000008186 active pharmaceutical agent Substances 0.000 description 4

- 230000007257 malfunction Effects 0.000 description 4

- 238000004088 simulation Methods 0.000 description 3

- 238000004364 calculation method Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000000903 blocking effect Effects 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 238000000034 method Methods 0.000 description 1

- 230000002265 prevention Effects 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

Images

Landscapes

- Electronic Switches (AREA)

Description

【発明の属する技術分野】

本発明は、コンピユータ等の電子装置に組込まれ、電源投入時や電源遮断時にリセット信号を出力するリセット信号発生回路に関する。

【0002】

【従来の技術】

一般に、IC等が組込まれたコンピユータ等の電子装置には、リセット信号発生回路が組込まれている。このリセット信号発生回路は電源投入時にローレベルのリセット信号を出力する。そして、電源電圧Vpが予め指定された例えば4.5v等の下限電圧を超えるとリセット信号を解除する。また、電源遮断した時や停電発生時に電源電圧Vpが例えば5v等の規定電圧から4.5vの下限電圧以下に低下すると、ローレベルのリセット信号を出力する。コンピユータ等の電子装置は、このローレベルのリセット信号の出力期間中においては、通常の処理動作を停止する。また、必要に応じてメモリの初期化等の処理を行う。

【0003】

図10は一般的なリセット信号発生回路の回路図である。

【0004】

電源1から直流の電源電圧Vpが電源スイッチ2を介して図示しないコンピユータ本体及びリセット信号出力回路3へ供給される。リセット信号出力回路3内において、電源ライン4と接地間に一対の抵抗R1、R2で分圧された分圧電圧V1が、トランジスタQ1のベースに印加されている。このトランジスタQ1のコレクタには電源ライン4から抵抗R3を介して電源電圧Vpが印加されている。

【0005】

電源ライン4と接地間に、抵抗R4、トランジスタQ2、抵抗R5の直列回路が接続されている。トランジスタQ2のベースにトランジスタQ1のコレクタ電圧が印加されている。さらに、電源ライン4と接地間に、抵抗R6、トランジスタQ3の直列回路が接続されている。トランジスタQ3のベースにトランジスタQ2のエミッタ電圧が印加されている。したがって、トランジスタQ2、Q3はダーリントン回路を構成する。

【0006】

トランジスタQ2のコレクタ電圧が出力端子5を介してリセット信号6として図示しないコンピユータ本体へ印加される。

【0007】

なお、電源ライン4と出力端子5間にはプルアップ抵抗R7が接続され、出力端子5と接地間にはプルダウン抵抗R8が接続されている。

【0008】

このように構成された、リセット信号発生回路の動作を、図11のタイムチャートを用いて説明する。図11のタイムチャートは、電源スイッチ2の投入時と電源スイッチ2の遮断時におけるリセット信号6の信号電圧VRSTの変化を示す。

【0009】

一般に、トランジスタには例えば0.7〜0.8v等の動作しきい値電圧が存在し、この動作しきい値電圧以下の電圧をベースに印加しても動作しないか、又は動作しても不安定になる。ダーリントン回路の場合は、回路全体の動作しきい値電圧は倍の1.4〜1.6vとなる。

【0010】

電源スイッチ2の投入前においては、リセット信号出力回路3自体に電源電源電圧Vpが供給されないので、リセット信号6の信号電圧VRSTは0v(ボルト)である。時刻t1 にて電源スイッチ2が投入されると、電源電圧Vpは上昇を開始する。しかし、この時点では、抵抗R1、R2の分圧電圧V1は低く、トランジスタQ1は導通しないので、抵抗R3を介して電源電圧VpがトランジスタQ2のベースに印加されている。さらに、この時点では、トランジスタQ2のベースに印加されている電源電圧Vpは動作しきい値電圧に達していないので、このトランジスタQ2は導通しない。よって、このトランジスタQ2にダーリントン接続されたトランジスタQ 3も導通しない。その結果、リセット信号出力回路3の出力端子5には抵抗R6で分圧された電源電圧Vpに比例する電圧が現れ、この電圧がリセット信号6の信号電圧VRSTとなる。

【0011】

時刻t2にで、電源電圧Vpがダーリントン接続されたトランジスタQ2、Q3の動作しきい値電圧(1.4〜1.6v)に達すると、トランジスタQ2、Q3が導通して、リセット信号6の信号電圧VRSTが0vとなる。

【0012】

さらに、電源電圧Vpが上昇して、時刻t3 にて、下限電圧(=4.5v)に達すると、抵抗R1、R2の分圧電圧V1が上昇して、トランジスタQ1が導通して、トランジスタQ1のコレクタ電圧が低下する。よって、トランジスタQ2、Q3が遮断され、リセット信号6の信号電圧VRSTは抵抗R6で分圧された電源電圧Vpに比例する電圧となる。

【0013】

そして、時刻t4 にて、電源電圧Vpが規定値(=5.0v)になると、リセット信号6の信号電圧VRSTも一定値となる。

【0014】

なお、時刻t5にて、電源スイッチ2を遮断した場合も、電源投入時とほぼ同じ動作を行う。

【0015】

図12は、図10に示すリセット信号発生回路における各抵抗R1〜R8、各トランジスタQ1〜Q3に実際の値を設定して、計算機で電源電圧Vpとリセット信号6の信号電圧VRSTとの関係をシミュレーション演算した結果を示す図である。

【0016】

【発明が解決しようとする課題】

しかしながら、図10に示すリセット信号発生回路には改良すべき次のような課題がある。

【0017】

すなわち、図11に示すように、電源スイッチ2を投入した電源投入時刻t1 から直ちにローレベルのリセット信号6が出力されるのではなく、電源投入時刻t1から電源電圧Vpが動作しきい値電圧(=1.4〜1.6v)に達する時刻t2までの期間に、元来不要な三角波形状の微小波形7が生じ、その後に、ローレベルのリセット信号6が出力される。

【0018】

また、図12に示すシミュレーション演算結果においても、電源電圧Vpが0vから動作しきい値電圧に達するまでの間に、元来不要な三角波形状の微小波形7が生じる。

【0019】

電源投入時点から、ローレベルのリセット信号6の出力まえに、電源電圧Vpがコンピユータ本体又は電子装置に提供される。この期間における電源電圧Vpの最大値は前述した動作しきい値電圧(=1.4〜1.6v)である。従来、この電圧値では、コンピユータ本体又は電子装置は起動することはないが、近年、ICの駆動電圧の低電圧化が進んでいること、あるいはバックアップ時の電源低下により駆動電圧が低下すること(+5vが3vとか)から、前述した動作しきい値電圧(=1.4〜1.6v)でも動作する懸念がある。しかし、このような低電圧で駆動すると、語動作したり、誤ったデータをメモリに書込む懸念がある。

【0020】

このような不都合を回避するために、図13に示すように、電源ライン4とリセット信号出力回路3の出力端子5との間に、この出力端子5へ電圧を供給する電源電圧供給回路8を介挿したリセット信号発生回路が提唱されている(特許第2695696号)。

【0021】

そして、この提案のリセット信号発生回路においては、電源電圧供給回路8の動作しきい値電圧をリセット信号出力回路3の動作しきい値電圧より高い値に設定している。このように構成することにより、電源電圧Vpが小さい期間にリセット信号出力回路3から出力されるリセット信号6の不安定性が解消される。

【0022】

しかし、この手法においては、電源電圧供給回路8は、電源ライン4と接地間にトランジスタQ4と抵抗R9と直列接続されるプルダウン方式であるので、TTL IC等のようにプルアップ特性を有した負荷にリセット信号6が供給された場合、前述した微小波形7の信号レベルか引上げられて、前述と同様の問題が生じる。

【0023】

さらに、出力されるリセット信号6の出力インピーダンスが高い場合で、かつ雑音防止用のコンデンサが介挿されていた場合は、リセット信号6の立上がり特性が低下する。

【0024】

本発明は、このような事情に鑑みてなされたものであり、電源投入時や電源遮断時においてたとえ電源電圧がリセット信号出力回路の動作しきい値電圧以下の状態期間においてもリセット信号出力端子の出力信号レベルを確実にローレベル状態に維持でき、リセット信号が入力されるコンピユータ本体や電子装置に誤動作が生じることが未然に防止でき、さらに、リセット信号が出力されていない状態時においても低い出力インピーダンスを維持できるリセット信号発生回路を提供することを目的とする。

【0025】

【課題を解決するための手段】

上記課題を解消するために、本発明のリセット信号発生回路は、入力された電源電圧が下限値以下のときローレベルのリセット信号を出力すると共に、下限値より低い動作しきい値電圧を有するリセット信号出力回路と、このリセット信号出力回路のリセット信号の出力端子と接地との間に介挿され、電源電圧が下限値以下で導通し下限値を超えると遮断するディプレッション型のスイッチング回路とを備えている。

【0026】

このように構成されたリセット信号発生回路においては、リセット信号出力回路のリセット信号の出力端子と接地との間にディプレッション型のスイッチング回路が介挿されている。

【0027】

したがって、電源電圧が下限電圧以下の状態においては、スイッチング回路は導通しているので、リセット信号出力回路におけるリセット信号出力端子の出力信号レベルは、たとえ、電源電圧がリセット信号出力回路の動作しきい値電圧以下であっても接地レベル、すなわちローレベルを維持している。

【0028】

電源が投入されると、電源電圧は上昇を開始し電源電圧が動作しきい値電圧まで上昇する期間においては、リセット信号出力回路は動作しないので、電源とリセット信号出力回路のリセット信号の出力端子との間に接続されたプルアップ抵抗により、出力端子の信号レベルは上昇しようとするが、前述したように、スイッチング回路が導通しているので、リセット信号の出力端子は接地レベルを維持している。

【0029】

したがって、このリセット信号が印加されるコンピユータ本体は、電源投入時点から電源電圧が上昇を開始し動作しきい値電圧まで上昇する期間においてもローレベルのリセット信号が出力されていると判断する。したがって、この期間においてコンピユータ本体や電子装置が誤動作をすることはない。

【0030】

電源電圧が動作しきい置電圧に達すると、リセット信号出力回路は正常に動作開始し、正規のローレベルのリセット信号を出力する。そして、電源電圧が下限電圧を超えると、ローレベルのリセット信号は解除される。

【0031】

なお、電源電圧が下限電圧を超えた時点においては、スイッチング回路は遮断しているので、リセット信号の出力端子はハイレベルを維持している。

【0032】

また別の発明におけるリセット信号発生回路においては、スイッチング回路を、ゲート端子が接地されたn型FETとゲート端子に電源電圧が印加されたp型FETとの直列回路で構成している。

【0033】

図5に示すように、互いに、動作特性が異なるn型のFETとp型のFETとの直列回路で、電源電圧Vpが前記1.4〜1.6vの動作しきい値電圧までは、図4に示すようにドレイン電流IDは増加し、動作しきい値電圧近傍でピークとなり、この動作しきい値電圧を過ぎると、ドレイン電流IDは減少し、電源電圧Vpが4.5vの下限電圧近傍で0値近傍に低下する。すなわち、この直列回路においては、下限電圧以下で導通し、下限電圧を超えると遮断する。

【0034】

また、別の発明のリセット信号発生回路においては、スイッチング回路を、電源電圧でオン・オフ制御されるディプレッション型の光MOSカプラで構成している。

【0035】

このように構成されたリセット信号発生回路においては、電源スイッチが投入されていない状態又は微小電圧時においては、リセット信号出力回路のリセット信号の出力端子と接地間に介挿されたディプレッション型の光MOSカプラは導通している。そして、電源電圧が例えば下限値を超えると光MOSカプラは遮断される。

【0036】

したがって、電源電圧が動作しきい値電圧以下のときにおいても、リセット信号出力回路のリセット信号の出力端子はローレベル状態を維持している。

【0037】

また、遮断状態の光MOSカプラは高いインピーダンス特性を有するので、リセット信号が出力されていない状態時において高い出力インピーダンスを維持できる。

【0038】

さらに、別のリセット信号発生回路においては、リセット信号出力回路のリセット信号の出力端子と電源からの電源ラインとの間に、電源電圧が下限値以下で遮断し下限値を超えると導通するエンハンスメント型の第2のスイッチング回路が介挿されている。

また、別のリセット信号発生回路においては、リセット信号出力回路のリセット信号の出力端子と電源からの電源ラインとの間に、電源電圧が下限値より小さい所定電圧以下で遮断し当該所定電圧を超えると導通するエンハンスメント型の第2のスイッチング回路が介挿されている。

【0039】

このように構成されたリセット信号発生回路においては、プルアップ抵抗に並列にこのエンハンスメント型の第2のスイッチング回路が接続されている。したがって、電源電圧が下限値を超えると、プルアップ抵抗の機能を停止でき、リセット信号出力回路のリセット信号の出力端子に電源電圧を直接印加できる。したがって、たとえ、リセット信号の出力端子と接地間に介挿されたスイッチング回路が遮断状態時においても、低い出力インピーダンスを維持できる。

【0040】

【発明の実施の形態】

以下、本発明の各実施形態を図面を用いて説明する。

(第1実施形態)

図1は本発明の第1実施形態に係るリセット信号発生回路の回路構成図である。図10に示す従来のリセット信号発生回路と同一部分には同一符号を付して重複する部分の詳細説明を省略する。

【0041】

この第1実施形態のリセット信号発生回路においては、リセット信号出力回路3のリセット信号6の出力端子5と接地間に第1のスイッチング回路9が接続されている。さらに、電源1の電源ライン4と前記リセット信号6の出力端子5との間に第2のスイッチング回路10が接続されている。

【0042】

前記第1のスイッチング回路9は、ゲート端子が接地されたn型FET11とゲート端子が電源ライン4に接続されたp型FET12との直列回路で構成されている。より具体的には、n型FET11のドレイン端子Dがリセット信号6の出力端子5に接続され、このn型FET11のソース端子Sがp型FET12のソース端子Sに接続されている。P型FET12のドレイン端子Dは接地されている。

【0043】

この第1のスイッチング回路9の動作を図3、図4及び図5を用いて説明する。説明を簡単にするために、この第1のスイッチング回路9は電源ライン4と接地間に介挿されているとする。

【0044】

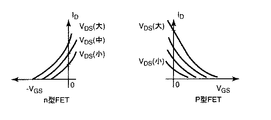

一般に、n型のn型FET11においては、図5(a)に示すように、ドレイン・ソース間電圧VDSが上昇しかつゲート・ソース間電圧VGSが上昇するとドレイン電流IDが上昇する。一方、p型FET12においては、図5(b)に示すように、ドレイン・ソース間電圧VDSが低下しかつゲート・ソース間電圧VGSが上昇するとドレイン電流IDが減少する。

【0045】

ここで、n型のn型FET11がなくて、p型FET12のみの場合を考える。この場合、ゲート・ソース間電圧VGSは0であるので、電源電圧Vp(=ドレイン・ソース間電圧VDS)が上昇すると、ドレイン電流IDが増加する。

【0046】

よって、ゲート端子が接地されたn型FET11をp型FET12と電源ライン4との間に介挿することにより、電源電圧Vpの上昇に応じて、p型FET12におけるゲート・ソース間電圧VGSを低下させている。

【0047】

また、n型FET11のゲート端子は接地されでいるので、電源電圧Vpが上昇すると、ゲート・ソース間電圧VGSは(―)方向へ変化するので、電源電圧Vpが上昇すると、ドレイン電流IDが減少する。

【0048】

したがって、電源電圧Vpの上昇に応じて、それそれドレイン電流IDに対する特性ば異なる特性を有するn型FET11とp型FET12とを直列接続した第1のスイッチング回路9における、このスイッチング回路9に印加される電源電圧Vpを変化させた場合におけるドレイン電流IDは図4に示す特性13となる。

【0049】

この特性13にて理解できるように、リセット信号出力回路3の1.4〜1.6vの動作しきい値電圧近傍でドレイン電流IDは最大値を示し、この動作しきい値電圧を超えると減少し、4.5vの下限電圧を超えるとほぼ0mAに低下する。よって、この第1のスイッチング回路9は、電源電圧Vpが下限値以下で導通し、下限値を超えると遮断するディプレッション型のスイッチング回路を構成する。

【0050】

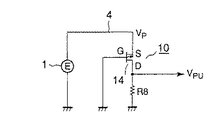

また、電源ライン4とリセット信号6の出力端子5との間に接続された第2のスイッチング回路10は、ソース端子Sが電源ライン4に接続され、ドレイン端子Dが信号の出力端子5に接続され、ゲート端子Gが接地されたMOSp型FET14で構成されている。

【0051】

次に、この第2のスイッチング回路10の動作を図6及び図7を用いて説明する。説明を簡単にするために、この第2のスイッチング回路10は電源ライン4と接地間に介挿されているとする。

【0052】

ゲート端子Gは接地されているので、電源電圧Vpが上昇して、ゲート・ソース間電圧V GS が、このp型FET14が持っているスレッショルド電圧から決まる電圧、例えば、3.1vに達すると、このp型FET14は導通する。導通後、電源電圧Vpがさらに上昇すると、MOSp型FET14のドレイン・ソース電圧VDSは上昇し、ドレイン電流ID は増加するので、プルダウン抵抗R6の上端から取出されたリセット信号の信号レベルであるプルアップ電圧VPUは、電源電圧Vpの上昇に応じて上昇する。

【0053】

したがって、電源電圧Vpを変化させた場合におけるプルアップ電圧VPUは図7に示す特性15となる。

この特性15にて理解できるように、この第2のスイッチング回路10は、電源電圧Vpの3.1v以上で導通し、その電圧を下回ると遮断しているエンハンスメント型のスイッチング回路を構成する。

【0054】

次に、このように構成された第1のスイッチング回路9と第2のスイッチング回路10とが組込まれた第1実施形態のリセット信号発生回路の動作説明を行う。

【0055】

電源スイッチ2が投入されて電源電圧Vpが例えば1.4〜1.6vの動作しきい値電圧に達するまでは、リセット信号出力回路3は動作しないので、このリセット信号出力回路3からローレベルのリセット信号は出力されない。しかし、電源電圧Vpが例えば1.4〜1.6vの動作しきい値電圧に達するまでの期間においては、第1のスイッチング回路9は導通しているので、リセット信号出力回路3の出力端子5の信号レベルは強制的に接地レベルとなる。

【0056】

したがって、このリセット信号発生回路全体としては、電源スイッチ2が投入されて電源電圧Vpが例えば1.4〜1.6vの動作しきい値電圧に達するまでの期間において、あたかもローレベルのリセット信号6を出力しているのと同等になる。したがって、このリセット信号発生回路からのリセット信号6を用いるコンピユータ等が誤動作を起こすことはない。

【0057】

図2は、図1に示す第1実施形態のリセット信号発生回路における各抵抗R1〜R8、各トランジスタQ1〜Q3、第1、第2のスイッチング回路9、10に実際の値を設定して、計算機で電源電圧Vpとリセット信号6の信号電圧VRSTとの関係をシミュレーション演算した結果を示す図である。

【0058】

この図2の特性でも理解できるように、電源スイッチ2を投入してから電源電圧Vpが下限電圧に達するまで、ローレベルのリセット信号6を継続して出力する。

【0059】

さらに、FETを用いた第1、第2のスイッチング回路9、10で、信号出力端子5と接地間、及び信号出力端子5と電源間を開閉制御しているので、このリセット信号発生回路におけるローレベルのリセット信号6の出力期間における出力インピーダンスを低インピーダンスに制御でき、リセット信号6が出力されていないハイレベル期間における出力インピーダンスも低インピーダンスに制御できる。その結果、このリセット信号発生回路からのリセット信号6を用いるコンピユータ等の動作特性を向上できる。

【0060】

(第2実施形態)

図8は本発明の第2実施形態に係るリセット信号発生回路の回路構成図である。図1に示す第1実施形態のリセット信号発生回路と同一部分には同一符号を付して重複する部分の詳細説明を省略する。

【0061】

この第2実施形態のリセット信号発生回路においては、リセット信号出力回路3のリセット信号6の出力端子5と接地間に接続された第1のスイッチング回路として、電源電圧Vpでオン・オフ制御されるディプレッション型の光MOSカプラ16が用いられている。

【0062】

この光MOSカプラ16は、図示するように、電源ライン4と接地間に介挿された発光ダイオード17と、リセット信吾出力回路3の出力端子5と接地間に介挿されたフォトFET18とで構成されている。このフォトFET18は、光が照射されていない状態においては導通しており、光が照射されると遮断される特性を有する。

【0063】

したがって、このディプレッション型の光MOSカプラ16全体としての特性は、図9に示すように、電源電圧Vpが0vから4.5vの下限電圧に達するまでは導通している。そして、電源電圧が例えば下限値を超えると遮断される。 したがって、電源電圧Vpが動作しきい値電圧以下のときにおいても、リセット信号出力回路3のリセット信号の出力端子5はローレベル状態を維持している。

【0064】

また、遮断状態の光MOSカプラ16は高いインピーダンス特性を有するので、ローレベルのリセット信号6が出力されていない状態時において高い出力インピーダンスを維持できる。

【0065】

したがって、上述した第1実施形態のリセット信号発生回路とほぼ同様の効果を奏することができる。

【0066】

【発明の効果】

以上説明したように、本発明のリセット信号発生回路においては、リセット信号出力回路のリセット信号出力端子と接地との間に、電源電圧が下限値以下で導通し下限値を超えると遮断するディプレッション型のスイッチング回路を介挿している。

【0067】

したがって、電源投入時や電源遮断時において、たとえ電源電圧がリセット信号出力回路の動作しきい値電圧以下の状態期間においても、リセット信号出力端子の出力信号レベルを確実のローレベル状態に維持でき、リセット信号が入力されるコンピユータ本体や電子装置の誤動作が生じることが未然に防止できる。

【0068】

さらに、リセット信号が出力されている状態においても、リセット信号が出力されていない状態時においても低い出力インピーダンスを維持でき、このリセット信号発生回路からのリセット信号6を用いるコンピユータ等の動作特性を向上できる。

【図面の簡単な説明】

【図1】本発明の第1実施形態に係わるリセット信号発生回路の回路構成図

【図2】同リセット信号発生回路の動作特性図

【図3】同リセット信号発生回路に組込まれた第1のスイッチング回路を取出して示す図

【図4】同第1のスイッチング回路の動作特性図

【図5】同第1のスイッチング回路に組込まれた各FETの動作特性図

【図6】同リセット信号発生回路に組込まれた第2のスイッチング回路を取出して示す図

【図7】同第2のスイッチング回路の動作特性図

【図8】本発明の第2実施形態に係わるリセット信号発生回路の回路構成図

【図9】同リセット信号発生回路に組込まれた第1のスイッチング回路の動作特性図

【図10】従来のリセット信号発生回路の回路構成図

【図11】同従来リセット信号発生回路の動作特性図

【図12】同じく従来リセット信号発生回路の動作特性図

【図13】他の従来のリセット信号発生回路の回路構成図

【符号の説明】

1…電源

2…電源スイッチ

3…リセット信号出力回路

4…電源ライン

5…出力端子

6…リセット信号

9…第1のスイッチング回路

10…第2のスイッチング回路

11…n型FET

12…p型FET

14…MOSp型FET

16…光MOSカプラ

Claims (5)

- 電源(1)から供給された電源電圧(Vp)が下限値以下のときローレベルのリセット信号(6)を出力すると共に、前記下限値より低い動作しきい値電圧を有するリセット信号出力回路(3)と、

このリセット信号出力回路の前記リセット信号の出力端子(5)と接地との間に介挿され、前記電源電圧が前記下限値以下で導通し前記下限値を超えると遮断するディプレッション型のスイッチング回路(9、16)と

を備えたリセット信号発生回路。 - 前記スイッチング回路(9)は、ゲート端子が接地されたn型FET(11)とゲート端子に前記電源電圧(Vp)が印加されたp型FET(12)との直列回路であることを特徴とする請求項1記載のリセット信号発生回路。

- 前記スイッチング回路(16)は、前記電源電圧でオン・オフ制御されるディプレッション型の光MOSカプラであることを特徴とする請求項1記載のリセット信号発生回路。

- 前記リセット信号出力回路の前記リセット信号の出力端子(5)と前記電源(1)からの電源ライン(4)との間に、前記電源電圧(Vp)が前記下限値以下で遮断し前記下限値を超えると導通するエンハンスメント型の第2のスイッチング回路(10)を介挿したことを特徴とする請求項1乃至3のいずれか1項記載のリセット信号発生回路。

- 前記リセット信号出力回路の前記リセット信号の出力端子(5)と前記電源(1)からの電源ライン(4)との間に、前記電源電圧(Vp)が前記下限値より小さい所定電圧以下で遮断し当該所定電圧を超えると導通するエンハンスメント型の第2のスイッチング回路(10)を介挿したことを特徴とする請求項1乃至3のいずれか1項記載のリセット信号発生回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002028426A JP3704094B2 (ja) | 2002-02-05 | 2002-02-05 | リセット信号発生回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002028426A JP3704094B2 (ja) | 2002-02-05 | 2002-02-05 | リセット信号発生回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2003229750A JP2003229750A (ja) | 2003-08-15 |

| JP3704094B2 true JP3704094B2 (ja) | 2005-10-05 |

Family

ID=27749646

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002028426A Expired - Fee Related JP3704094B2 (ja) | 2002-02-05 | 2002-02-05 | リセット信号発生回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3704094B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20030079442A (ko) * | 2002-04-04 | 2003-10-10 | 삼성전자주식회사 | 다중 순차적 리셋 회로 |

| JP5310023B2 (ja) * | 2009-01-23 | 2013-10-09 | ミツミ電機株式会社 | レギュレータ用半導体集積回路 |

| JP2017041704A (ja) * | 2015-08-18 | 2017-02-23 | ラピスセミコンダクタ株式会社 | 半導体装置及び無効化方法 |

-

2002

- 2002-02-05 JP JP2002028426A patent/JP3704094B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2003229750A (ja) | 2003-08-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100643041B1 (ko) | 역구동가능한 모스 출력 드라이버 | |

| US6879191B2 (en) | Voltage mismatch tolerant input/output buffer | |

| US5926056A (en) | Voltage tolerant output buffer | |

| US7924084B2 (en) | Semiconductor device | |

| KR960003529B1 (ko) | 반도체 메모리 장치의 칩 초기화 신호 발생회로 | |

| US8018264B2 (en) | Interface circuit | |

| KR960704322A (ko) | 개선된 데이타 출력 버퍼(improved data output buffer) | |

| US4746818A (en) | Circuit for maintaining the state of an output despite changes in the state of input | |

| US6169420B1 (en) | Output buffer | |

| US5157270A (en) | Reset signal generating circuit | |

| JP3704094B2 (ja) | リセット信号発生回路 | |

| JP6585827B2 (ja) | センサ装置 | |

| KR20220108490A (ko) | 정전기 보호 회로 | |

| US20050001660A1 (en) | Power-on reset circuit | |

| JP3311751B2 (ja) | 低電力型電圧感知回路 | |

| JP2000029551A (ja) | Cmos基準電圧生成器を含む集積回路 | |

| JP2018074567A (ja) | ネイティブトランジスタを使用する電力検波回路 | |

| US8018268B1 (en) | Over-voltage tolerant input circuit | |

| KR102617255B1 (ko) | 전자 장치 및 그의 동작 방법 | |

| US6720821B2 (en) | Methods and systems for generating interim voltage supplies | |

| US5825221A (en) | Output circuit of semiconductor device | |

| CN111063329A (zh) | 一种带温度检测的蜂鸣器驱动电路 | |

| JPH06318852A (ja) | 半導体集積回路装置 | |

| JP2023182877A (ja) | 電子装置 | |

| JP3869145B2 (ja) | 出力回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20050216 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20050419 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050620 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050719 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050721 |

|

| R150 | Certificate of patent (=grant) or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313532 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080729 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090729 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090729 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100729 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110729 Year of fee payment: 6 |

|

| LAPS | Cancellation because of no payment of annual fees |