JP2020055152A - 液滴吐出装置及び画像形成方法 - Google Patents

液滴吐出装置及び画像形成方法 Download PDFInfo

- Publication number

- JP2020055152A JP2020055152A JP2018185888A JP2018185888A JP2020055152A JP 2020055152 A JP2020055152 A JP 2020055152A JP 2018185888 A JP2018185888 A JP 2018185888A JP 2018185888 A JP2018185888 A JP 2018185888A JP 2020055152 A JP2020055152 A JP 2020055152A

- Authority

- JP

- Japan

- Prior art keywords

- power supply

- selection information

- circuit

- waveform signal

- drive

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Ink Jet (AREA)

- Particle Formation And Scattering Control In Inkjet Printers (AREA)

Abstract

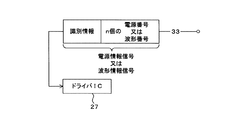

【解決手段】液滴吐出装置は、ノズルに対応する駆動素子をN個有するヘッドと、電源回路21〜25と、電源選択情報に従って各駆動素子に接続する電源回路を選択するN個の電源回路セレクタ、及び波形信号選択情報に従って各駆動素子に出力する波形信号を選択するN個の波形信号セレクタを備え、波形信号に従って駆動素子の駆動を行う駆動回路27と、画像データに基づいて駆動素子毎に、前記電源選択情報及び波形信号選択情報を決定し、これらを一つの信号線33を介して駆動回路27にシリアル伝送する制御回路51とを備える。制御回路51は、前記電源選択情報を駆動回路27へ伝送した後、前記画像データの受信が終了するまでの間に、前記電源選択情報を駆動回路27へ再送する。

【選択図】図3

Description

本願発明者は、回路の構成を簡素化するために、描画データメモリと、COM選択回路及びスイッチング回路とを、例えば1つの配線によって接続することを考えた。この場合、1つの配線を介して、COM選択データ及び吐出データが送られることになる。COM選択データ又は吐出データをCOM選択回路又はスイッチング回路に入力するために、COM選択データ及び吐出データのヘッダ部分にいずれのデータであるかを識別する識別データを付与させる。しかし、静電気等のノイズによって識別データの内容が変わってしまうと、適切なデータがスイッチング回路に入力されない虞がある。この場合、画素毎に指定するドットのサイズに対応して液滴がノズルから吐出されず、画質が悪くなることがある。

そして、印刷中に、駆動素子に接続する電源回路を選択する電源選択情報を再送するので、ノイズ等が生じて駆動素子が異なる電源回路に接続されている場合に、適切な電源回路に接続し直すことができ、良好な画質が得られる。

以下本発明を実施の形態1に係る印刷装置1を示す図面に基づいて説明する。図1は、印刷装置1を示す平面図である。印刷装置1は、例えば、インクジェットプリンタである。なお、図1に示すように、便宜上、本明細書において、前後左右それぞれの方向を矢印で示す方向として説明する。印刷装置1は筐体2を備える。

電源回路21〜電源回路25には、それぞれ電圧センサV及び電流センサIが接続されている。なお、電源回路21〜電源回路25には、電圧センサV及び電流センサIのいずれかを接続することにしてもよい。

制御線33には、電圧を検出する電圧検出回路36が接続されている。

図4に示すように、ドライバIC27は波形信号生成回路200を備える。波形信号生成回路200は、制御線31から受信した制御信号に従って、互いに異なる7つの波形信号(0)〜(6)の波形信号を生成する。波形信号(0)〜(6)は、駆動信号生成回路30が備えるトランジスタを制御するパルス信号である。各波形信号(0)〜(6)は、互いにパルスの幅またはパルスの数などが異なっている。波形信号生成回路により生成された各波形信号(0)〜(6)は、それぞれn個の電源回路セレクタ90(1)〜(n)に供給される。

ヘッドユニット11のFPGA51は、外部装置9から吐出開始命令を受信したとき、電源情報信号をドライバIC27に送る。FPGA51は、例えば各ノズルの吐出口11aから均一に液滴を吐出できるように、各駆動素子111に接続する電源回路を選択する。ドライバIC27は、電源選択情報に従って、電源回路セレクタ90により、各駆動素子111を電源選択情報で指定されたいずれかの電源回路に接続する。

その後、FPGA51は、外部装置9から画像データを受信すると、画像データを波形信号選択情報に変換し、波形信号選択情報をドライバIC27に送る。ドライバIC27は、波形信号選択情報に従って、波形信号セレクタ91により、駆動素子111毎に波形信号選択情報で指定されたいずれかの波形信号を選択する。

FPGA51は、画像データを受信し続けるので、FPGA51は、一度、電源情報信号を送った後は、ドライバIC27に、波形信号情報を送り続けることになる。

ドライバIC27が波形信号選択情報を保持している状態で、静電気等のノイズが発生し、識別情報がローレベルからハイレベルになったとき、本来は、波形信号選択情報としての意味を有していた情報が、電源選択情報とされる場合がある。この場合、ドライバIC27は、各駆動素子111を、当初の電源選択情報で選択された電源回路とは異なる電源回路に接続する。FPGA51は、電源選択情報を、画像データを受信している間には送らないため、各駆動素子111が不適切な電源回路に接続され、各ノズルから吐出される液滴が当初設定した大きさとは異なる大きさとなり、画質が悪化する。

電源情報信号の再送は、例えば画像データとして、1ライン分の画素がないデータを受信した場合、異常を検知した場合等に行う。

1ラインとは、記録媒体100の搬送方向に直交する方向に並ぶ、先頭画素から最終画素までの画素群をいう。1ライン分の画素がない空白データを受信した場合、印刷画像に影響を与えることなく、電源情報信号を送ることができる。

異常は、波形信号選択情報に基づいて推定される各電源回路の電圧又は電流値と、電圧センサV又は電流センサIにより実測した各電源回路の電圧又は電流値とに基づいて検知する。また、異常は、制御線33に接続した電圧検出回路36により検出した電圧に基づいて検知してもよい。

FPGA51は、以下の電源情報送信処理を適宜の間隔で行う。

FPGA51は、外部装置9から吐出開始命令を受信したか否かを判定する(S1)。FPGA51は吐出開始命令を受信していないと判定した場合(S1:NO)、電源情報送信処理を終了する。

FPGA51は吐出開始命令を受信したと判定した場合(S1:YES)、ドライバIC27に電源情報信号を送信し、電源選択情報を送る(S2)。ドライバIC27は、電源選択情報に従って、電源回路セレクタ90により、各駆動素子111をそれぞれ指定された電源回路に接続する。

FPGA51は画像データに従って、駆動素子111毎に波形信号を決定し、波形情報信号をドライバIC27に送信し、波形信号選択情報を送る(S4)。ドライバIC27は、波形信号選択情報に従って、波形信号セレクタ91により、駆動素子111毎に波形を選択し、選択された波形に従って、駆動素子111を駆動する。これにより各駆動素子111に対応した各ノズルの吐出口11aからインクが吐出される。

FPGA51は画像データの受信が終了していないと判定した場合(S6:NO)、処理をS3へ戻す。

FPGA51は画像データの受信が終了したと判定した場合(S6:YES)、電源情報送信処理を終了する。

そして、当初の電源選択情報により選択された電源回路に駆動素子111を接続することができるので、各ノズルの吐出口11aから吐出される液滴が画像データに基づき設定したドットサイズとなり、良好な画質が得られる。

図8は、FPGA512による変形例1の電源情報送信処理を示すフローチャートである。

FPGA51は、以下の電源情報送信処理を適宜の間隔で行う。

FPGA51は、外部装置9から吐出開始命令を受信したか否かを判定する(S11)。FPGA51は吐出開始命令を受信していないと判定した場合(S11:NO)、電源情報送信処理を終了する。

FPGA51は吐出開始命令を受信したと判定した場合(S11:YES)、ドライバIC27に電源情報信号を送信し、電源選択情報を送る(S12)。ドライバIC27は、電源選択情報に従って、電源回路セレクタ90により、各駆動素子111をそれぞれ指定された電源回路に接続する。

FPGA51は画像データに従って、駆動素子111毎に波形信号を決定し、波形情報信号をドライバIC27に送信し、波形信号選択情報を送る(S14)。ドライバIC27は、波形信号選択情報に従って、波形信号セレクタ91により、駆動素子111毎に波形を選択し、選択された波形に従って、駆動素子111を駆動する。これにより各駆動素子111に対応した各ノズルの吐出口11aからインクが吐出される。

FPGA51は、各電源回路の電圧又は電流値を電圧センサV又は電流センサIにより取得する(S16)。

FPGA51は、前記絶対値がa以下でないと判定した場合(S17:NO)、処理をS12へ戻す。

FPGA51は画像データの受信が終了したと判定した場合(S18:YES)、電源情報送信処理を終了する。

電源選択情報の再送により、当初の電源選択情報により選択された電源回路に駆動素子111を接続することができるので、各ノズルの吐出口11aから吐出される液滴が画像データに基づき設定したドットサイズとなり、以後、良好な画質が得られる。

図9は、FPGA512による変形例2の電源情報送信処理を示すフローチャートである。

FPGA51は、以下の電源情報送信処理を適宜の間隔で行う。

FPGA51は、外部装置9から吐出開始命令を受信したか否かを判定する(S21)。FPGA51は吐出開始命令を受信していないと判定した場合(S21:NO)、電源情報送信処理を終了する。

FPGA51は吐出開始命令を受信したと判定した場合(S21:YES)、ドライバIC27に電源情報信号を送信し、電源選択情報を送る(S22)。ドライバIC27は、電源選択情報に従って、電源回路セレクタ90により、各駆動素子111をそれぞれ指定された電源回路に接続する。

FPGA51は画像データに従って、駆動素子111毎に波形信号を決定し、波形情報信号をドライバIC27に送信し、波形信号選択情報を送る(S24)。ドライバIC27は、波形信号選択情報に従って、波形信号セレクタ91により、駆動素子111毎に波形を選択し、選択された波形に従って、駆動素子111を駆動する。これにより、各駆動素子111に対応した各ノズルの吐出口11aからインクが吐出される。

FPGA51は電圧が閾値b以下でないと判定した場合(S25:NO)、処理をS22へ戻す。

FPGA51は電圧が閾値b以下であると判定した場合(S25:YES)、画像データの受信が終了したか否かを判定する(S26)。FPGA51は画像データの受信が終了していないと判定した場合(S26:NO)、処理をS23へ戻す。

FPGA51は画像データの受信が終了したと判定した場合(S26:YES)、電源情報送信処理を終了する。

電源選択情報の再送により、当初の電源選択情報により選択された電源回路に駆動素子111を接続することができるので、各ノズルの吐出口11aから吐出される液滴が画像データに基づき設定したドットサイズとなり、以後、良好な画質が得られる。

以下、実施の形態2に係る印刷装置1について説明する。図10は、印刷装置1を示す概略斜視図である。実施の形態2に係る印刷装置1は、記録媒体100の移動方向に交差する方向(走査方向、図10における左方向及び右方向に沿う方向)に、インクジェットヘッドが移動するスキャン方式の印刷装置である。インクジェットヘッドが移動すること以外は、実施の形態1に係る印刷装置1と同様の構成を有する。

ヘッドユニット18のFPGA51は、外部装置9から吐出開始命令を受信したとき、電源情報信号をドライバIC27に送る。FPGA51は、例えば各ノズルの吐出口11aから均一に液滴を吐出できるように、各駆動素子111に接続する電源回路を選択する。ドライバIC27は、電源選択情報に従って、電源回路セレクタ90により、各駆動素子111を電源選択情報で指定されたいずれかの電源回路に接続する。

その後、FPGA51は、外部装置9から画像データを受信すると、画像データを波形信号選択情報に変換し、波形信号選択情報をドライバIC27に送る。ドライバIC27は、波形信号選択情報に従って、波形信号セレクタ91により、駆動素子111毎に波形信号選択情報で指定されたいずれかの波形を選択する。

波形信号セレクタ91にて選択された波形信号は、電源回路セレクタ90にて選択された電源回路によって、所定の電圧を印加され、駆動信号生成回路30に入力される。駆動素子111は、入力された波形信号によって定められるパルス幅やパルス数、及び選択された電源回路の出力電圧によって定められる波高値の駆動信号に基づいて駆動され、ノズルの吐出口11aから、ドットサイズデータに対応した液滴量のインクが吐出され、記録媒体100に画像が形成される。

FPGA51は、画像データを受信し続けるので、FPGA51は、一度、電源情報信号を送った後は、ドライバIC27に、波形信号情報を送り続ける。

図11は、FPGA512による電源情報送信処理を示すフローチャートである。

FPGA51は、以下の電源情報送信処理を適宜の間隔で行う。

FPGA51は、外部装置9から吐出開始命令を受信したか否かを判定する(S31)。FPGA51は吐出開始命令を受信していないと判定した場合(S31:NO)、電源情報送信処理を終了する。

FPGA51は吐出開始命令を受信したと判定した場合(S31:YES)、ドライバIC27に電源情報信号を送信し、電源選択情報を送る(S32)。ドライバIC27は、電源選択情報に従って、電源回路セレクタ90により、各駆動素子111をそれぞれ指定された電源回路に接続する。

FPGA51は画像データに従って、駆動素子111毎に波形信号を決定し、波形情報信号をドライバIC27に送信し、波形信号選択情報を送る(S34)。ドライバIC27は、波形信号選択情報に従って、波形信号セレクタ91により、駆動素子111毎に波形を選択し、選択された波形に従って、駆動素子111を駆動する。これにより、各駆動素子111に対応した各ノズルの吐出口11aからインクが吐出される。

FPGA51はキャリッジ14の移動方向が反転したと判定した場合(S35:YES)、処理をS32へ戻す。

FPGA51はキャリッジ14の移動方向が反転していないと判定した場合(S35:NO)、画像データの受信が終了したか否かを判定する(S36)。FPGA51は画像データの受信が終了していないと判定した場合(S36:NO)、処理をS33へ戻す。

FPGA51は画像データの受信が終了したと判定した場合(S36:YES)、電源情報送信処理を終了する。

11a 吐出口

14 キャリッジ

21〜26 電源回路

27 ドライバIC(駆動回路)

33 制御線(信号線)

36 電圧検出回路

51 FPGA(制御回路)

V 電圧センサ

I 電流センサ

Claims (7)

- N個のノズルにそれぞれ対応する駆動素子をN個有するヘッドと、

複数の電源回路と、

前記複数の電源回路の中から、N個の電源選択情報に従って各駆動素子に接続する電源回路を選択する、N個の電源回路セレクタ、及び

N個の波形信号選択情報に従って各駆動素子に出力する波形信号を選択する、N個の波形信号セレクタを備え、選択した前記波形信号に従ってN個の駆動素子の駆動を行う駆動回路と、

画素毎に形成するドットサイズを指定する複数のドットサイズデータで構成された画像データを受信し、

前記画像データに基づいて、前記駆動素子毎に、前記電源選択情報及び前記波形信号選択情報を決定し、

決定した前記電源選択情報及び前記波形信号選択情報を一つの信号線を介して前記駆動回路にシリアル伝送する制御回路と

を備え、

前記制御回路は、

前記電源選択情報を前記駆動回路へ伝送した後、

前記画像データの受信が終了するまでの間に、前記電源選択情報を前記駆動回路へ再送する、液滴吐出装置。 - 前記ヘッドを走査方向に往復移動させるキャリッジを備え、

前記制御回路は、前記キャリッジの移動方向が反転したときに再送する、請求項1に記載の液滴吐出装置。 - 前記制御回路は、前記画像データとして、1ライン分の画素がないデータを受信したときに再送する、請求項1に記載の液滴吐出装置。

- 前記制御回路は、異常を検知したときに再送する、請求項1に記載の液滴吐出装置。

- 前記異常は、前記波形信号選択情報に基づいて推定される各電源回路の電圧又は電流値と、実測した各電源回路の電圧又は電流値とに基づいて検知される、請求項4に記載の液滴吐出装置。

- 前記信号線の電圧を検出する検出する検出回路を備え、

前記異常は、前記検出回路が検出した電圧に基づいて検知される、請求項4に記載の液滴吐出装置。 - 画素毎に形成するドットサイズを指定する複数のドットサイズデータで構成された画像データを受信し、

N個のノズルにそれぞれ対応するN個の駆動素子毎に、各駆動素子に接続する電源回路を夫々選択するN個の電源選択情報を決定し、

前記駆動素子を駆動する駆動回路へ前記電源選択情報をシリアル伝送し、

該電源選択情報に基づいて各駆動素子を電源回路に接続し、

前記画像データに基づいて、前記駆動素子毎に、各駆動素子に出力する波形信号を選択するN個の波形信号選択情報を決定し、

前記波形信号選択情報を前記駆動回路にシリアル伝送し、

各駆動素子に出力する波形信号を選択し、

前記画像データの受信が終了するまでの間に、前記電源選択情報を前記駆動回路へ再送し、

画像を形成する画像形成方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2018185888A JP7135684B2 (ja) | 2018-09-28 | 2018-09-28 | 液滴吐出装置及び画像形成方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2018185888A JP7135684B2 (ja) | 2018-09-28 | 2018-09-28 | 液滴吐出装置及び画像形成方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2020055152A true JP2020055152A (ja) | 2020-04-09 |

| JP7135684B2 JP7135684B2 (ja) | 2022-09-13 |

Family

ID=70106012

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018185888A Active JP7135684B2 (ja) | 2018-09-28 | 2018-09-28 | 液滴吐出装置及び画像形成方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP7135684B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN114347654A (zh) * | 2020-10-13 | 2022-04-15 | 精工电子打印科技有限公司 | 液体喷射头及液体喷射记录装置 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6027195A (en) * | 1996-11-12 | 2000-02-22 | Varis Corporation | System and method for synchronizing the piezoelectric clock sources of a plurality of ink jet printheads |

| JP2006205521A (ja) * | 2005-01-27 | 2006-08-10 | Fuji Xerox Co Ltd | 液滴吐出装置 |

| JP2006272905A (ja) * | 2005-03-30 | 2006-10-12 | Seiko Epson Corp | 液体吐出装置 |

| JP2008188889A (ja) * | 2007-02-05 | 2008-08-21 | Fuji Xerox Co Ltd | 容量性負荷の駆動回路及び画像形成装置 |

| JP2017177755A (ja) * | 2016-03-31 | 2017-10-05 | ブラザー工業株式会社 | 制御回路、インクジェットヘッドシステム及び制御方法 |

| JP2019177676A (ja) * | 2018-03-30 | 2019-10-17 | ブラザー工業株式会社 | 液滴吐出装置 |

-

2018

- 2018-09-28 JP JP2018185888A patent/JP7135684B2/ja active Active

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6027195A (en) * | 1996-11-12 | 2000-02-22 | Varis Corporation | System and method for synchronizing the piezoelectric clock sources of a plurality of ink jet printheads |

| JP2006205521A (ja) * | 2005-01-27 | 2006-08-10 | Fuji Xerox Co Ltd | 液滴吐出装置 |

| JP2006272905A (ja) * | 2005-03-30 | 2006-10-12 | Seiko Epson Corp | 液体吐出装置 |

| JP2008188889A (ja) * | 2007-02-05 | 2008-08-21 | Fuji Xerox Co Ltd | 容量性負荷の駆動回路及び画像形成装置 |

| JP2017177755A (ja) * | 2016-03-31 | 2017-10-05 | ブラザー工業株式会社 | 制御回路、インクジェットヘッドシステム及び制御方法 |

| JP2019177676A (ja) * | 2018-03-30 | 2019-10-17 | ブラザー工業株式会社 | 液滴吐出装置 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN114347654A (zh) * | 2020-10-13 | 2022-04-15 | 精工电子打印科技有限公司 | 液体喷射头及液体喷射记录装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP7135684B2 (ja) | 2022-09-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US11192358B2 (en) | Droplet ejecting device and method for transmitting, to drive circuit, a plurality of items of information used to drive a plurality of drive elements | |

| JP2016112722A (ja) | インクジェットヘッド、及び、印刷装置 | |

| US11420441B2 (en) | Printing apparatus and printing method | |

| JP7135684B2 (ja) | 液滴吐出装置及び画像形成方法 | |

| JP2010036424A (ja) | 液体吐出装置 | |

| JP6862736B2 (ja) | 電源選択回路、回路、ヘッドモジュール、及び印刷装置 | |

| JP2022040747A (ja) | 液体吐出装置、その制御方法及びプログラム | |

| JP2019064151A (ja) | 液滴吐出装置及びコンピュータプログラム | |

| JP2013180537A (ja) | 液体吐出装置及びヘッド制御回路 | |

| JP2017213806A (ja) | 素子基板、記録ヘッド、及び記録装置 | |

| CN110315845B (zh) | 电源基板及打印装置 | |

| US11338580B2 (en) | Printing apparatus and printing method | |

| JP4655134B2 (ja) | 液滴噴射装置 | |

| JP2016215524A (ja) | 液体吐出装置 | |

| JP2021160170A (ja) | 印刷装置 | |

| US20250108610A1 (en) | Printing method and printing apparatus | |

| CN115122767B (zh) | 液体喷出装置 | |

| JP2018171854A (ja) | 液体吐出装置及び液体吐出装置の電圧設定方法 | |

| US7762646B2 (en) | Head substrate, printhead, head cartridge, and printing apparatus using the printhead or head cartridge | |

| US10391764B2 (en) | Element substrate, printhead, and printing apparatus | |

| JP2010000631A (ja) | 液体吐出方法 | |

| CN111483222B (zh) | 打印头以及激活系统 | |

| JP2010228447A (ja) | 流体噴射装置 | |

| JP2021160187A (ja) | 液体吐出ヘッド、及び液体吐出ヘッドを備える印刷装置 | |

| JP2011207114A (ja) | 液体吐出装置、及び、液体吐出制御方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20210924 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20220722 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20220802 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20220815 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7135684 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |