以下の実施の形態では特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

さらに、以下の実施の形態では便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明などの関係にある。

また、以下の実施の形態において、要素の数など(個数、数値、量、範囲などを含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合などを除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良いものとする。

また、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。

また、以下の実施の形態において、構成要素等について、「Aからなる」、「Aよりなる」、「Aを有する」、「Aを含む」と言うときは、特にその要素のみである旨明示した場合等を除き、それ以外の要素を排除するものでないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。

(実施の形態1)

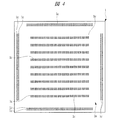

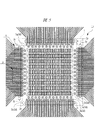

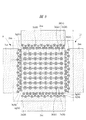

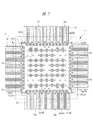

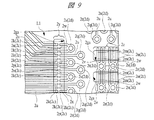

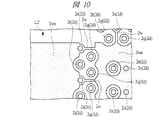

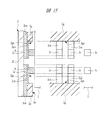

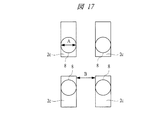

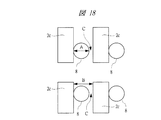

図1は本発明の実施の形態1の半導体装置の構造の一例を一部破断して示す斜視図、図2は図1に示す半導体装置の構造の一例を示す断面図、図3は図2のA部の構造の一例を拡大して示す部分拡大断面図、図4は図1に示す半導体装置に搭載される半導体チップの電極パッドの配列の一例を示す平面図である。また、図5は図1に示す半導体装置に組み込まれる配線基板の第1配線層(L1)のチップ下部付近の配線パターンの一例を示す平面図、図6は図1に示す半導体装置に組み込まれる配線基板の第2配線層(L2)のチップ下部付近の配線パターンの一例を示す平面図、図7は図1に示す半導体装置に組み込まれる配線基板の第3配線層(L3)のチップ下部付近の配線パターンの一例を示す平面図、図8は図1に示す半導体装置に組み込まれる配線基板の第4配線層(L4)のチップ下部付近の配線パターンの一例を示す平面図である。さらに、図9は図5のA部の構造の一例を拡大して示す部分拡大平面図、図10は図6のA部の構造の一例を拡大して示す部分拡大平面図、図11は図7のA部の構造の一例を拡大して示す部分拡大平面図、図12は図8のA部の構造の一例を拡大して示す部分拡大平面図、図13は図5のB部の構造の一例を拡大して示す部分拡大平面図である。また、図14は図1に示す半導体装置に搭載される半導体チップのパッド配置と基板構造の関係の一例を示すデータ図、図15は本発明の実施の形態1の半導体装置における周辺パッド用の配線基板のボンディング電極とバンプと半導体チップの電極パッドの位置関係の一例を拡大して示す部分拡大断面図と部分拡大平面図、図16は本発明の実施の形態1の半導体装置における中央パッド用の配線基板のボンディング電極の形状の一例を拡大して示す部分拡大平面図、図17は本発明の実施の形態1の半導体装置のフリップチップ接続部におけるバンプサイズと基板のボンディング電極の大きさの関係の一例を示す平面図、図18は本発明の実施の形態1の半導体装置のフリップチップ接続部におけるバンプサイズと基板のボンディング電極の大きさの関係の一例を示す平面図である。

図1及び図2に示す本実施の形態1の半導体装置は、配線基板の上面2a上に半導体チップ1がフリップチップ実装で半田接続されて成る半導体パッケージであり、本実施の形態1では、前記半導体装置の一例として、前記配線基板の下面2bに外部端子である複数の半田ボール5がグリッド状に設けられたBGA9を取り上げて説明する。したがって、本実施の形態1の半導体装置は、フリップチップ実装タイプのBGA9であり、例えば、数百ピン以上の外部端子を備えた多ピンの半導体パッケージである。

次に、BGA9の詳細構成について説明すると、上面2aと上面2aの反対側の下面2bとを備えた配線基板である多層配線基板2と、主面1aと主面1aの反対側の裏面1bとを備え、かつ多層配線基板2の上面2a上にフリップチップ実装された半導体チップ1と、多層配線基板2の下面2bにアレイ状に配置されて設けられた複数の外部端子である半田ボール5とから成る。

ここで、半導体チップ1は、その主面1aに複数の表面電極である電極パッド1cが形成されており、多層配線基板2の上面2aにフェイスダウン実装でフリップチップ接続されている。すなわち、半導体チップ1は、その主面1aと多層配線基板2の上面2aとが対向した状態で配置されており、この状態で多層配線基板2上に搭載されている。その際、半導体チップ1は多層配線基板2に半田接続で電気的に接続されており、複数の半田バンプ8を介してフリップチップ接続されている。

また、多層配線基板(BGA基板ともいう)2の上面2aには、図5に示すように、半導体チップ1をフリップチップ実装する領域に複数のボンディング電極2cが形成されている。つまり、多層配線基板2の上面2aのチップ搭載領域には、半導体チップ1の電極パッド1cと半田バンプ8を介してフリップチップ接続を行う複数のボンディング電極2cが形成されている。

まず、多層配線基板2の上面2aにおけるチップ搭載領域のうち、半導体チップ1の主面1aの周縁部に対応した第1領域2yには、複数のボンディング電極2cが2列で形成されている。また、第1領域2yより内側の領域である第2領域2zには、複数の電源/GND用ボンディング電極(コア電源用ボンディング電極2mとGND用ボンディング電極2n)がアレイ状に形成されている。ここで、前記電源/GNDとは、半導体チップ1に形成された集積回路に供給される動作電位であり、電源電位は、例えば外部電源用として3.0V、内部電源(コア電源)として1.5Vが設定され、また、GND電位は、接地電位0Vが設定される。

すなわち、多層配線基板2の上面2aのチップ搭載領域の中央部付近である第2領域2zには、複数の前記電源/GND用ボンディング電極がアレイ状に形成されている。なお、第2領域2zの周囲の領域に第1領域2yが形成されており、この第1領域2yに複数のボンディング電極2cが2列で配置されている。

一方、多層配線基板2の下面2bには、図2に示すように複数のランド2jがアレイ状に形成され、それぞれのランド2jに外部端子である半田ボール5が接続されている。

なお、多層配線基板2と半導体チップ1との間に位置するフリップチップ接続部及びその周囲にはアンダーフィル樹脂6が充填されており、フリップチップ接続部を固めて保護している。

さらに、多層配線基板2の上面2aの周縁部には、半導体チップ1を囲んだ状態にスティフナリング7が取り付けられている。スティフナリング7は、リング状テープ7aによって多層配線基板2に接着されている。スティフナリング7の上部にはヒートスプレッダ4が設けられている。ヒートスプレッダ4は、半導体チップ1上の放熱樹脂3とスティフナリング7/ヒートスプレッダ4間の接着材(例えば、テープ材)7bを介して、スティフナリング7及び半導体チップ1の裏面1bに接合されている。

これにより、半導体チップ1から発せられる熱は放熱樹脂3を介してヒートスプレッダ4に伝わり、ヒートスプレッダ4から外方に放散されるとともに、半田バンプ8を介して多層配線基板2を経て半田ボール5から実装基板に伝わる。また前記熱は、ヒートスプレッダ4から接着材7b及びスティフナリング7を介して多層配線基板2に伝わり、多層配線基板2を経て半田ボール5から実装基板へと伝わって放散される。

また、本実施の形態1のBGA9の多層配線基板2は、図3に示すように、基材の層であるコア層2h(図19参照)を有していないコアレス基板であり、ビルドアップ層2fと、ビルドアップ層2fの表側の面(多層配線基板2の上面2a)に形成された複数のボンディング電極2cと、ビルドアップ層2fの裏側の面(多層配線基板2の下面2b)に形成された複数のランド2jと、表側のボンディング電極2cと裏側のランド2jとを電気的に接続するスルーホール(配線)2dと、ビルドアップ層2fに形成された内部配線2e等とを有している。

なお、それぞれのボンディング電極2cの周囲、及び複数のランド2jの周囲には絶縁膜であるソルダレジスト膜2gが形成されている。

また、上面2a側のボンディング電極2cとこれに対応する下面2b側のランド2jとは、ビルドアップ層2fに形成されたスルーホール(配線)2dやビアホール配線2i(図2参照)、あるいは内部配線2eを介して電気的に接続されている。

ここで、図4に示すように、半導体チップ1は、例えば、シリコンによって形成され、その主面1aには、複数の表面電極である電極パッド1cが形成されている。すなわち、主面1aの周縁部には、各辺に沿って2列で複数の電極パッド1cが設けられており、さらに、周縁部に設けられた複数の電極パッド列の内側の領域には、複数の電極パッド1cがアレイ状に配置されて設けられている。

また、図2に示すようにチップ−基板間に塗布されたアンダーフィル樹脂6は、例えば、エポキシ系樹脂などである。さらにスティフナリング7やヒートスプレッダ4は、熱伝導率の高い金属によって形成され、また、フリップチップ接続の半田バンプ8及び外部端子である半田ボール5は、例えば、鉛フリー半田等の半田材から成る。

また、多層配線基板2におけるボンディング電極2c、ビアホール配線2i、内部配線2e及びスルーホール2d等は、例えば、純銅または銅に少量(1%以下)のアルミニウム、シリコン(Si)等の不純物が添加された銅合金から成る。

本実施の形態1のBGA9の多層配線基板2は、コア層2h(図19参照)を有していない厚さの薄いコアレス基板である。コアレス基板を採用することで、スルーホール2dを形成する際に、レーザー加工やフォトリソ加工等で貫通孔を形成することができ、その結果、スルーホールピッチを小さくすることができ、さらにバンプピッチも小さくすることができる。上記コアレス基板の厚さは、0.2mm以下であり、本実施の形態1の場合、例えば0.03〜0.05mm程度である。

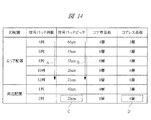

ここで、図14は、本実施の形態1のBGA9の多層配線基板2の構造を決める上でのパッド配置と基板構造の関係を示すものであり、本発明者が検討したデータである。本発明は、多ピン化をコスト低減化して実現するものであり、そのためには多ピン化を図る上で、スルーホールピッチやバンプピッチを小さく形成する必要があるとともに、コスト低減化を図る上では多層配線基板2の配線層の層数をなるべく減らすことが必要となる。

すなわち、配線層の層数を多数形成可能であるのなら、スルーホールピッチやバンプピッチを小さく形成することは容易であるが、コストが高くなるためこれは採用不可である。

今回、図14に示すように信号パッドピッチを従来の64μmから20μm程度に小さくすることで、配線層の層数を低減しつつ多ピン化を図ることができることを導き出しており、したがって、信号パッドピッチを20μm程度に小さくする(図14のB矢印の方向)ことができるような条件を見出す必要がある。

図14に示すように信号パッド列数をエリア配置で4列から12列に増やす(図14のA矢印の方向)と、信号パッドピッチを64μmから21μmに減らすことができるが、コアレス基板(多層配線基板2)の配線層の層数が6層必要となってしまいコスト低減化を図ることができない。

そこで、信号パッド配置を周辺配置の2列とすることで、信号パッドピッチを20μmとすることができ(図14のC部)、さらにコアレス基板を採用することで配線層の層数を4層に抑えることができる(図14のD部)。これにより、多層配線基板2のコストの低減化を図ることができる。なお、信号パッドピッチの20μmについては、信号パッド列数を周辺配置で2列とし、コア有り基板を採用して配線層の層数を8層とすることでも実現可能であるが、その場合、配線層の層数が8層であるため、コストの低減化を図ることができない。

したがって、本実施の形態1のBGA9の多層配線基板2では、信号パッド列数を周辺配置で2列とし、コアレス基板を採用して配線層の層数を4層とすることで、薄い多層配線基板2を実現するとともにコストの低減化も図ることができる。すなわち、コアレス基板を採用したことで薄い多層配線基板2を実現して、スルーホールピッチを150〜200μmと小さくすることができ、さらにバンプピッチも100〜150μmと小さくすることができる。

これにより、信号パッドピッチを20μm程度にすることができ、多ピン化が図れるとともに、配線層の層数を4層として少なくできるため、多層配線基板2のコストの低減化も図ることが可能になる。

次に、図5〜図13を用いて、本実施の形態1の多層配線基板2の4層の配線層の各層の配線パターンについて説明する。

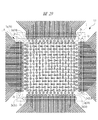

図5は、図2に示す多層配線基板2の最も上面2a側の配線層である第1配線層L1の配線パターンを示す図であり、フリップチップ接続が行われる半導体チップ1の主面1aと対向する配線層である。この第1配線層L1では、半導体チップ1の主面1aの周縁部に対応した第1領域2yには、複数のボンディング電極2cが2列で形成されている。また、第1領域2yより内側の領域である第2領域2zには、複数の電源/GND用ボンディング電極(図9に示すコア電源用ボンディング電極2mとGND用ボンディング電極2n)がアレイ状に形成されている。

つまり、チップ搭載領域の中央部付近である第2領域2zには、図9に示すような複数のコア電源用ボンディング電極2mとGND用ボンディング電極2nとがアレイ状に形成されており、さらに、第2領域2zの周囲の第1領域2yには、複数のボンディング電極2cが2列で形成されている。

また、図9及び図13に示すように第1領域2yの複数のボンディング電極2cは、複数の信号用ボンディング電極2kを含んでおり、複数のボンディング電極2cのうちの複数の信号用ボンディング電極2kは、内側と外側に振り分けて引き出されている。さらに、信号用ボンディング電極2kから内側に引き出された複数の信号用配線2uは、それぞれスルーホール2dを介して他の層の配線部2ca(図15参照)と電気的に接続されており、図5に示すように、複数のスルーホール2dは、第1領域2yと第2領域2zの間の領域に配置されている。

なお、図13に示すように、第1領域2yに配置された複数のボンディング電極2cのうち、複数の信号用ボンディング電極2kのみに注目すると、外側列と内側列とで2列に配置された複数のボンディング電極2cにおいて、前記外側列の信号用ボンディング電極2kに電気的に接続された信号用配線2uは外側に引き出され、一方、前記内側列の信号用ボンディング電極2kに電気的に接続された信号用配線2uは内側に引き出されている。

つまり、外側列のボンディング電極2cは、引き出し配線によって外側に引き出され、一方、内側列のボンディング電極2cは、引き出し配線によって内側に引き出されている。したがって、図9に示すように、内側列の信号用ボンディング電極2kから内側に引き出された複数の信号用配線2uは、それぞれ信号用スルーホール2qに電気的に接続されており、これら複数の信号用スルーホール2qは、第1領域2yと第2領域2zの間の領域に配置されている。なお、本実施の形態1の例では第1領域2yの2列に配置された複数のボンディング電極2cのうち、外側列は全て信号用ボンディング電極2kである。

また、第1領域2yに配置された複数のボンディング電極2cは、信号用ボンディング電極2k以外にも、図13に示すように複数のGND用ボンディング電極2nと複数のIO電源用ボンディング電極2pを含んでおり、これら複数のGND用ボンディング電極2nと複数のIO電源用ボンディング電極2pは、何れも第1領域2yの内側列に設けられている。

また、第1領域2yより内側の領域には、GND用ボンディング電極2nとGND用配線2wを介して電気的に接続された複数のGND用スルーホール2s、及びIO電源用ボンディング電極2pとIO電源用配線2xを介して電気的に接続された複数のIO電源用スルーホール2tがそれぞれ設けられている。すなわち、複数のGND用スルーホール2s及び複数のIO電源用スルーホール2tは、それぞれ第1領域2yと第2領域2zの間の領域に配置されている。

したがって、図5に示すように、第1領域2yと第2領域2zの間の領域には、複数の信号用スルーホール2qと、複数のGND用スルーホール2sと、複数のIO電源用スルーホール2tが配置されている。

一方、図5及び図9に示すように第2領域2zには、複数の電源/GND用ボンディング電極が形成されているが、このうち、複数の電源用ボンディング電極のそれぞれは、コア電源用ボンディング電極2mである。つまり、第2領域2zには、複数のコア電源用ボンディング電極2mと複数のGND用ボンディング電極2nがアレイ状に形成されており、コア電源用ボンディング電極2mにはコア電源用配線2vを介してコア電源用スルーホール2rが形成されており、さらに、GND用ボンディング電極2nにはGND用配線2wを介してGND用スルーホール2sが形成されている。

したがって、第2領域2zには、複数のコア電源用スルーホール2rと複数のGND用スルーホール2sとがアレイ状に配置されている。

なお、第1領域2yと第2領域2zの間の領域に形成された複数のスルーホール2d(信号用スルーホール2q、GND用スルーホール2s、IO電源用スルーホール2t)、及び第2領域2zに形成された複数のスルーホール2d(コア電源用スルーホール2r、GND用スルーホール2s)は、共にスルーホールピッチが150〜200μmの狭ピッチで形成されている。

次に、図6は、多層配線基板2の第1配線層L1の下層の配線層である第2配線層L2の配線パターンを示す図である。すなわち、多層配線基板2の上面2aから下面2bに向かう方向の上面2a側から2番目の配線層(上面2aの次の配線層)の配線パターンを示すものである。

図6に示すように、第2配線層L2には、主に、GNDプレーン2waが広い面積で形成されている。このGNDプレーン2waは、第1配線層L1のGND用ボンディング電極2nとGND用配線2wやGND用スルーホール2sを介して電気的に接続されている。

さらに、第2配線層L2には、図10に示すように、複数の信号用スルーホール2q、IO電源用スルーホール2t及びコア電源用スルーホール2rがGNDプレーン2waとは絶縁された状態でそれぞれ配置されている。

なお、第2配線層L2にGNDプレーン2waが形成されているのは、第1配線層L1に複数の信号用配線2uが形成されているため、これらの信号用配線2uの近くにGNDプレーン2waを設けることで信号用配線2uがノイズを受けにくくして信号の安定化を図るものである。

すなわち、第1配線層L1に形成された複数の信号用配線2uは、図13に示すように、第1配線層L1においても近傍(両隣)にGND用配線2wやIO電源用配線2xが配置されており、さらに加えて直下の第2配線層L2に図10に示すGNDプレーン2waが形成されているため、電源やGNDによって囲まれた状態となっており、したがって、ノイズの影響を受けにくく、信号の安定化を図ることができる。

次に、図7は、多層配線基板2の第2配線層L2の下層の配線層である第3配線層L3の配線パターンを示す図である。すなわち、多層配線基板2の上面2aから下面2bに向かう方向の上面2a側から3番目の配線層(第2配線層L2の次の配線層)の配線パターンを示すものである。

図7及び図11に示すように第3配線層L3には、その中央付近にコア電源プレーン2vaが形成されているとともに、その周囲には細長い複数のIO電源プレーン2xaが形成されている。すなわち、多層配線基板2の上面2aから下面2bに向かう方向において、GNDプレーン2waが形成された第2配線層L2の次の(下層の)第3配線層L3に電源プレーンであるコア電源プレーン2vaとIO電源プレーン2xaが形成されている。

ここで、コア電源プレーン2vaは、第1配線層L1の第2領域2zの複数のコア電源用ボンディング電極2mとコア電源用配線2vやコア電源用スルーホール2rを介して電気的に接続されている。一方、IO電源プレーン2xaは、第1配線層L1の第1領域2yの複数のIO電源用ボンディング電極2pとIO電源用配線2xやIO電源用スルーホール2tを介して電気的に接続されている。

以上のように、多層配線基板2では第1配線層L1の中央の第2領域2zに設けられた複数のGND用ボンディング電極2nに電気的に接続されたGNDプレーン2waは、第2配線層L2に配置され、同じく第1配線層L1の第2領域2zに設けられた複数のコア電源用ボンディング電極2mに電気的に接続されたコア電源プレーン2vaは、第3配線層L3に配置されている。つまり、第1配線層L1のGNDと電源がそれぞれ第2配線層L2と第3配線層L3に切り分けて配置されている。

これは各スルーホール2dの直径と配置ピッチの両者が小さいからこそ可能になるものであり、レーザー加工によって形成された貫通孔から成るスルーホール2dを第1配線層L1の第2領域2zに密度高く形成可能であるからこそ実現できる構造である。

また、第3配線層L3には、複数の信号用配線2uが設けられている。第3配線層L3の信号用配線2uは、第1配線層L1の第1領域2yの信号用ボンディング電極2kと信号用配線2uや信号用スルーホール2qを介して電気的に接続されている。つまり、第1配線層L1の第1領域2yの複数の信号用ボンディング電極2kのうち、内側に引き出された複数の信号用配線2uが第1領域2yと第2領域2zの間に配置された信号用スルーホール2qを介して第3配線層L3の信号用配線2uに電気的に接続されており、さらに第3配線層L3において複数の信号用配線2uのそれぞれは、信号用スルーホール2qから外側に引き出されている。

言い換えると、第1配線層L1の第1領域2yの複数の信号用ボンディング電極2kのうち、内側に引き出された複数の信号用配線2uと信号用スルーホール2qを介して電気的に接続された第3配線層L3(他の層)の信号用配線(配線部)2uは、この第3配線層L3において外側に引き出されている。したがって、第1配線層L1において、信号用スルーホール2qは、全て第2領域2zの外側に形成されている。

なお、第3配線層L3において信号用配線2uは、2本ずつセットで配置され、2本の信号用配線2uの左右両側には細長いIO電源プレーン2xaが配置されている。

本実施の形態1のBGA9は数百ピン以上の多ピンの半導体装置であり、少ない配線層で所望数の信号用ピンに繋ぐ信号用配線2uの引き回しを実現するためには、第1配線層L1において第1領域2yより外側へのみの信号用配線2uの引き出しでは信号用配線2uの数が足りないため、第1領域2yより内側の領域(第1領域2yと第2領域2zの間の領域)にも信号用スルーホール2qを配置して、他の配線層(ここでは、第3配線層L3)で信号用配線2uを外側に引き出すことで、少ない配線層の数百ピン以上の多ピンの半導体装置の構造を可能にしている。

そのため、コアレス基板等の薄い基板を採用してチップ下の第2領域2zに形成する複数のスルーホール2dのスルーホール径とスルーホールピッチを小さくすることで、第1配線層L1の第1領域2yと第2領域2zの間にも複数の信号用スルーホール2qを形成するための領域が確保することができ、この第1領域2yと第2領域2zの間に複数の信号用スルーホール2qを配置することで、前記少ない配線層の数百ピン以上の多ピンの半導体装置の構造を可能にできる。

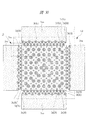

次に、図8は、多層配線基板2の第3配線層L3の下層の配線層である第4配線層L4の配線パターンを示す図である。すなわち、多層配線基板2の上面2aから下面2bに向かう方向の上面2a側から4番目の配線層(第3配線層L3の次の配線層)の配線パターンを示すものである。

図8及び図12に示すように第4配線層L4には、第2配線層L2のGNDプレーン2waとGND用スルーホール2sを介して電気的に接続されたGNDプレーン2waや、第3配線層L3のコア電源プレーン2vaとコア電源用スルーホール2rを介して接続された複数のコア電源プレーン2va等が設けられており、それぞれのプレーンと電気的に接続されたGND用、電源用、及び信号用の各ランド2jが設けられている。各ランド2jには、BGA9の外部端子となる半田ボール5が接続されている。

なお、第4配線層L4のGNDプレーン2waは、複数のGND用スルーホール2sのみを介して第2配線層L2のGNDプレーン2waとダイレクトに電気的に接続されている。したがって、多層配線基板2におけるGND電位の安定化を図ることができる。

次に、図15と図16は多層配線基板2の上面2aにおいて、ソルダレジスト膜2gの開口部2gaに露出する配線部2caとボンディング電極2cの構造を示すものであり、図15は上面2aの第1領域2yでの周辺パッド用のボンディング電極2cを示しており、一方、図16は上面2aの第2領域2zでのエリア配置用のボンディング電極2cを示している。どちらのボンディング電極2cにおいても、フリップチップ接続では、ボンディング電極2c上に形成されたメッキ層2cbと半田バンプ8を接続させてフリップチップ接続を行うが、その際、本実施の形態1のBGA9では信号パッドピッチが20μmと小さいため、半田バンプ8を例えば円柱形状とすることで狭パッドピッチによるフリップチップ接続を実現させることができる。

次に、図17と図18は、フリップチップ接続部におけるチップ側のバンプサイズと基板側の配線の最小間隔の関係の一例を示すものである。図17に示すバンプサイズAと配線の間隔Bの関係において、半田バンプ8が図18に示すように位置ずれした際に半田バンプ8とボンディング電極2cの間に隙間Cが形成されるように、バンプサイズ(半田バンプ8のサイズ)A<基板配線(ボンディング電極2c)の間隔Bとすることで、半田バンプ8が位置ずれした際にも電気的なショートの発生を防ぐことができる。

本実施の形態1のBGA9によれば、多ピンのBGA9において、多層配線基板2の上面2aのチップ周縁部に対応した領域(第1領域2y)に配置された複数の信号用ボンディング電極2kが内側と外側に振り分けて引き出されており、内側に引き出された複数の信号用配線2uと接続する複数の信号用スルーホール2qが、複数の信号用ボンディング電極2kの電極列の領域である第1領域2yと複数のコア電源用ボンディング電極2mとGND用ボンディング電極2nが配置された中央の第2領域2zとの間の領域に配置されていることで、チップのパッドピッチを詰めることができる。

すなわち、多層配線基板2として、薄いコアレス基板を用いたことでチップ下の第2領域2zに形成する複数のスルーホール2dのスルーホール径とスルーホールピッチを小さくすることができ、上面2a(第1配線層L1)の第1領域2yと第2領域2zの間にも複数の信号用スルーホール2qを形成するための領域を確保することができる。

その結果、第1領域2yに形成された複数の信号用ボンディング電極2kを内側と外側に振り分けて引き出すことができ、したがって、チップのパッドピッチを詰めることができるとともに、信号用ボンディング電極2kを周辺配置(第1領域2y)に対応させ、かつコア電源用ボンディング電極2mやGND用ボンディング電極2nをエリア配置(第2領域2z)に対応させて配置することができる。

これにより、多層配線基板2の層数を増やすことなく、チップシュリンク化にも対応可能となる。

すなわち、再配線を採用することなく、かつ多層配線基板2の層数を増やさずに多ピン化を図れるため、多ピンのBGA9のコストの低減化を図ることができるとともに、チップシュリンク化にも対応することができる。なお、フリップチップ接続タイプの半導体装置は、ワイヤボンディングタイプの半導体装置に比べてコストが高いため、本実施の形態1のBGA9のようなフリップチップ接続タイプの半導体装置のコスト低減化は非常に有効である。

また、再配線を採用することなく電極パッド1cのエリア配置が行えるため、チップ設計としても容易に行うことができる。

また、多層配線基板2では、スルーホール径を小さくしたことで、第2領域2zのコア電源は、そのままコア電源用スルーホール2rを介して第4配線層L4のコア電源用のランド2jに接続されるため、配線層の層数を増やすことなく、ピン数を増やして多ピン化に対応させることができる。

また、半導体チップ1の電極パッド1cのエリア配置が可能なため、チップシュリンク化が行われた多ピンの半導体装置においても半導体チップ1の電極パッド1cのエリア配置を実現することができる。

さらに、チップシュリンク化が行われた半導体チップ1においてもその電極パッド1cのエリア配置を実現することができるため、半導体チップ1の中央部付近である第2領域2zに複数のコア電源用ボンディング電極2mを配置することができ、チップシュリンク化が行われた多ピンのBGA9において電源の安定化を図ることができる。

特に、BGA9が高パワーデバイス用途の場合には、電源の安定化を図ることができるため、非常に有効である。

次に本実施の形態1の変形例について説明する。

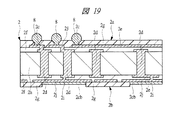

図19は本発明の実施の形態1の半導体装置に組み込まれる第1変形例の配線基板の構造の一例を拡大して示す部分拡大断面図である。図19に示す第1変形例の多層配線基板2は、コア層2hを有する配線基板であり、コア層2hを薄くすることで基板の厚さを薄くした配線基板である。

図19に示すコア層2hを薄くした多層配線基板2においても、コア層2hが薄いため径の小さいドリルを用いて小さい孔径の貫通孔を形成することができ、コアレス基板のスルーホール径やスルーホールピッチと同程度のスルーホール2dを形成することができる。

その結果、コア層2hを有する多層配線基板2を用いた半導体装置の場合においても、コアレス基板の多層配線基板2を用いた半導体装置の場合と同程度の効果を得ることができる。上記コア層2hを有する多層配線基板2の厚さは、例えば0.4mmや0.6mm程度であり、上記実施の形態1で説明したコアレス基板に比べてその厚さは厚くなるが、基板の剛性を向上することが可能である。ここでは、厚さ0.4mm以上で、かつ1.0mm以下の基板をコア層2hを有する薄型の多層配線基板2と称し、上記コア層2hを有する薄型の多層配線基板2は、例えば、パッケージサイズが、20〜35mm□程度と比較的大きめで、かつ高信頼性が要求される車載用途の半導体パッケージ基板として用いられる。

また、上記実施の形態1で説明したコアレス基板は、例えば、パッケージサイズが、10〜20mm□程度と比較的小さく、小型化が要求される携帯電話等のモバイル用途の半導体パッケージ基板として用いられる。

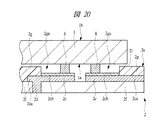

次に、図20は本発明の実施の形態1の半導体装置に組み込まれる第2変形例の配線基板の構造の一例を拡大して示す部分拡大断面図である。図20に示す第2変形例の半導体装置は、フリップチップ接続構造において、半導体チップ1と多層配線基板2のソルダレジスト膜2gとの隙間Dが5μm程度と小さいため、アンダーフィル樹脂6(図2参照)が入りにくいことがあるため、前記アンダーフィル樹脂6を充填しない構造とするものである。

したがって、アンダーフィル樹脂6を充填しないことでアンダーフィル樹脂6の充填ムラが生じることを防止できる。なお、配線部2caの表面にはニッケル−金等からなるメッキ層2cbが形成されている。

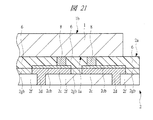

次に、図21は本発明の実施の形態1の半導体装置に組み込まれる第3変形例の配線基板の構造の一例を拡大して示す部分拡大断面図である。図21に示す第3変形例の半導体装置は、フリップチップ接続構造において、多層配線基板2に図20に示すようなソルダレジスト膜2gが設けられていない構造のものであり、ソルダレジスト膜2gの代わりとして、配線部2caと同等の高さの絶縁膜2gbを設けて基板表面の平坦化を行うものである。

これにより、多層配線基板2と半導体チップ1の主面1aとの間隔を15μm程度に広げ、そこにアンダーフィル樹脂6を充填するものである。

したがって、多層配線基板2と半導体チップ1の主面1aとの隙間が広げられたため、アンダーフィル樹脂6の充填ムラを低減することができる。

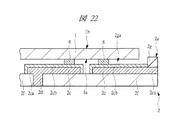

次に、図22は本発明の実施の形態1の半導体装置に組み込まれる第4変形例の配線基板の構造の一例を拡大して示す部分拡大断面図である。図22に示す第4変形例の半導体装置は、フリップチップ接続構造において、多層配線基板2の上面2aにおけるチップ搭載領域の全面にソルダレジスト膜2gが設けられていない構造のものであり、前記ソルダレジスト膜2gは、チップ搭載領域の外側のみに設けられている。この場合、配線部2caの露出部分には全面的にニッケル−金等からなるメッキ層2cbが形成されている。

その結果、多層配線基板2と半導体チップ1の主面1aとの隙間が広がるため、アンダーフィル樹脂6の充填ムラを低減することができる。

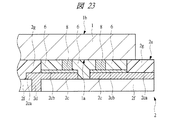

次に、図23は本発明の実施の形態1の半導体装置に組み込まれる第5変形例の配線基板の構造の一例を拡大して示す部分拡大断面図である。図24に示す第5変形例の半導体装置は、フリップチップ接続構造において、半田バンプ8が設けられた半導体チップ1をボンディング電極2c上に配置した後、半田バンプ8を溶かし、その後、アンダーフィル樹脂6を充填して最後に加熱してアンダーフィル樹脂6を硬化させたものである。

これにより、アンダーフィル樹脂6の充填ムラを低減することができる。

次に、図24は本発明の実施の形態1の第6変形例の半導体装置に組み込まれる配線基板の構造の一例を示す平面図、図25は図24に示す配線基板を用いた半導体装置の構造の一例を示す断面図である。図25に示す第6変形例の半導体装置は、フリップチップ接続に金バンプ11を用いたBGA10であり、したがって、図24に示すボンディング電極2cの表面には、錫メッキが施されている。

また、図24に示すように多層配線基板2の上面2a(図25参照)は、図22に示す多層配線基板2のようにチップ搭載領域のみにソルダレジスト膜2gが形成されていない構造となっており、前記チップ搭載領域の周囲にソルダレジスト膜2gが形成されている。したがって、BGA10においても、図25に示すようにアンダーフィル樹脂6を充填ムラを発生させることなく充填することができる。なお、ソルダレジスト膜2gの開口部2gaでアンダーフィル樹脂6の流れを止めることが可能な構造となっている。

次に、図26は本発明の実施の形態1の半導体装置の第7変形例の配線基板のボンディング電極の形状と半導体チップの電極パッドとの関係の一例を示す平面図である。図26に示す第7変形例の半導体装置は、フリップチップ接続に用いられる半田バンプ8の形状を、多層配線基板2の半田バンプ8が接続する配線部2caの延在方向に沿った長方形とするものである。

これによって、配線部2caの配線幅が20μmと細い場合であってもフリップチップ接続の半田バンプ8による接続面積を確保することができる。

次に、図27は本発明の実施の形態1の第8変形例の半導体装置の構造を示す部分拡大断面図である。図27に示す第8変形例の半導体装置は、搭載される半導体チップ1の厚さを薄くしたBGA13であるとともに、多層配線基板2の上面2aの半導体チップ1の周囲に積層用半田バンプ12をボンディング電極2cに接続して搭載したものである。

BGA13においては、半導体チップ1を薄くすることで半導体チップ1の裏面1b側にも封止用樹脂を周り込ませることができ、封止体15内に半導体チップ1を埋め込んで多層配線基板2をチップ内蔵基板とすることができる。半導体チップ1を覆う封止体15とソルダレジスト膜2gとを接続した上面部2gcを平坦にすることで、積層用半田バンプ12を上面部2gcから突出させることができる。

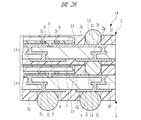

また、図28は本発明の実施の形態1の第9変形例の半導体装置の構造を示す部分拡大断面図である。図28に示す第9変形例の半導体装置は、図28に示すBGA13を2段に積層したPOP(Package On Package) 14である。

すなわち、半導体チップ1を薄くすることでチップ内蔵型の多層配線基板2を有したBGA13を形成し、これらのBGA13を複数段に積層してPOP14を構成することも可能である。

(実施の形態2)

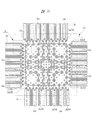

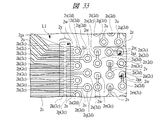

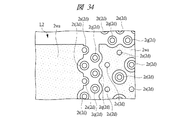

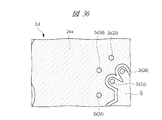

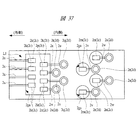

図29は本発明の実施の形態2の半導体装置に組み込まれる配線基板の第1配線層(L1)のチップ下部付近の配線パターンの一例を示す平面図、図30は本発明の実施の形態2の半導体装置に組み込まれる配線基板の第2配線層(L2)のチップ下部付近の配線パターンの一例を示す平面図、図31は本発明の実施の形態2の半導体装置に組み込まれる配線基板の第3配線層(L3)のチップ下部付近の配線パターンの一例を示す平面図、図32は本発明の実施の形態2の半導体装置に組み込まれる配線基板の第4配線層(L4)のチップ下部付近の配線パターンの一例を示す平面図である。また、図33は図29のA部の構造の一例を拡大して示す部分拡大平面図、図34は図30のA部の構造の一例を拡大して示す部分拡大平面図、図35は図31のA部の構造の一例を拡大して示す部分拡大平面図、図36は図32のA部の構造の一例を拡大して示す部分拡大平面図、図37は本発明の実施の形態2の半導体装置に組み込まれる変形例の配線基板の構造の一例を拡大して示す部分拡大平面図である。

本実施の形態2は、多層配線基板2を有する半導体装置において、実施の形態1のBGA9よりピン数を低減する場合の構造の一例を示すものである。ここでは、多層配線基板2の第1配線層L1の第2領域2zにおいて、図33に示すコア電源用ボンディング電極2mとGND用ボンディング電極2nの数を減らして半導体装置のピン数の低減化を図っている。つまり、第1配線層L1の第2領域2zにおけるボンディング電極2c(コア電源用ボンディング電極2mとGND用ボンディング電極2n)の数を、実施の形態1のBGA9の多層配線基板2の第2領域2zのボンディング電極2cの数に比べて減らしている。

図29〜図36を用いて、本実施の形態2の多層配線基板2の4層の配線層の各層の配線パターンについて説明する。

図29及び図33は第1配線層L1、図30及び図34は第2配線層L2、図31及び図35は第3配線層L3、図32及び図36は第4配線層L4の配線パターンをそれぞれ示すものである。それぞれの図において、第1領域2y、及びこの第1領域2yと第2領域2zの間の領域の配線パターンについては、実施の形態1の多層配線基板2のものと全く同じである。

実施の形態1と異なっている点について説明すると、図29に示す第1配線層L1の配線パターンにおいて、第2領域2zのボンディング電極2cの数が、実施の形態1のものより少なくなっており、これによって、半導体装置のピン数の低減化を図ることができる。図33に示すように、第2領域2zに設けられたGND用ボンディング電極2nは、GND用配線2w及びGND用スルーホール2sを介して、図30及び図34に示す第2配線層L2のGNDプレーン2waと電気的に接続されている。

一方、第1配線層L1の第2領域2zのコア電源用ボンディング電極2mは、コア電源用配線2v及びコア電源用スルーホール2rを介して図31及び図35に示す第3配線層L3のコア電源プレーン2vaと電気的に接続されている。

また、図32及び図36に示すように第4配線層L4には、第2配線層L2のGNDプレーン2waとGND用スルーホール2sを介して電気的に接続されたGNDプレーン2waや、第3配線層L3のコア電源プレーン2vaとコア電源用スルーホール2rを介して接続された複数のコア電源プレーン2va(2j)等が設けられており、それぞれのプレーンと電気的に接続されたGND用、電源用、及び信号用の各ランド2jが設けられている。

なお、実施の形態1の多層配線基板2の配線パターンと同様に、実施の形態2の多層配線基板2についても、第1配線層L1の第1領域2yの複数の信号用ボンディング電極2kのうち、内側に引き出された複数の信号用配線2uと信号用スルーホール2qを介して電気的に接続された第3配線層L3(他の層)の信号用配線(配線部)2uは、この第3配線層L3において外側に引き出されている。したがって、第1配線層L1において、信号用スルーホール2qは、全て第2領域2zの外側に形成されている。

また、第3配線層L3において信号用配線2uは、2本ずつセットで配置され、2本の信号用配線2uの左右両側には細長いIO電源プレーン2xaが配置されている。

本実施の形態1のBGA9と同様、本実施の形態2の半導体装置も多ピンの半導体装置であり、少ない配線層で所望数の信号用ピンに繋ぐ信号用配線2uの引き回しを実現するためには、第1配線層L1において第1領域2yより外側へのみの信号用配線2uの引き出しでは信号用配線2uの数が足りない。そのため、第1領域2yより内側の領域(第1領域2yと第2領域2zの間の領域)にも信号用スルーホール2qを配置して、他の配線層(ここでは、第3配線層L3)で信号用配線2uを外側に引き出すことで、少ない配線層の半導体装置の多ピン化構造を可能にしている。

そのため、コアレス基板等の薄い基板を採用してチップ下の第2領域2zに形成する複数のスルーホール2dのスルーホール径とスルーホールピッチを小さくすることで、第1配線層L1の第1領域2yと第2領域2zの間にも複数の信号用スルーホール2qを形成するための領域を確保することができ、この第1領域2yと第2領域2zの間に複数の信号用スルーホール2qを配置することで、前記少ない配線層の多ピンの半導体装置の構造を可能にできる。

なお、本実施の形態2の多層配線基板2の第1配線層L1、第2配線層L2、第3配線層L3及び第4配線層L4におけるその他の配線パターンについては、実施の形態1の多層配線基板2の各配線層の配線パターンと同じであるため、その重複説明は省略する。

また、本実施の形態2の多層配線基板2を有する半導体装置によって得られる効果についても、実施の形態1の半導体装置(BGA9)によって得られる効果と同様であり、その重複説明は省略する。

次に、本実施の形態2の変形例について説明する。

図37は本実施の形態2の変形例の配線基板の構造を示す図であり、第1配線層L1の第1領域2yにおける複数のボンディング電極2cが千鳥配置で設けられているものである。すなわち、第1配線層L1の第1領域2yに2列で配置された複数のボンディング電極2cが千鳥配置で設けられているものである。この場合、図4に示す半導体チップ1の主面1aの周縁部に2列で配置された複数の電極パッド1cも千鳥配置にすることでフリップチップ実装が可能となる。

これにより、多層配線基板2の配線ルールが、ライン/スペース=20μm/20μmの場合には、ボンディング電極2cの配置ピッチを20μmにすることができる。その結果、狭パッドピッチ化への対応が可能になり、半導体装置の更なる多ピン化を実現することができる。

以上、本発明者によってなされた発明を発明の実施の形態に基づき具体的に説明したが、本発明は前記発明の実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

例えば、前記実施の形態1では、多層配線基板2の上面2aの周縁部の第1領域2yにおけるボンディング電極2cの配置が並列(千鳥配置ではない)配置の場合について説明したが、実施の形態1のBGA9の多層配線基板2においても、上面2aの第1領域2y(第2領域2zも含む)のボンディング電極2cの配置を千鳥配置としてもよい。

このように実施の形態1のBGA9において多層配線基板2の上面2aの第1領域2yのボンディング電極2cの配置を千鳥配置とすることで、BGA9においても更なる狭パッドピッチ化への対応が可能になり、BGA9の更なる多ピン化を実現することができる。

また、前記実施の形態1では、半導体装置の構造の一例として、スティフナリング7が取り付けられたBGA9の場合を取り上げて説明したが、スティフナリング7は設けられていなくても良い。その場合、ヒートスプレッダ4は、半導体チップ1の裏面1bのみに放熱樹脂3等を介して接合される。