JP2014095897A - 液晶表示装置 - Google Patents

液晶表示装置 Download PDFInfo

- Publication number

- JP2014095897A JP2014095897A JP2013211596A JP2013211596A JP2014095897A JP 2014095897 A JP2014095897 A JP 2014095897A JP 2013211596 A JP2013211596 A JP 2013211596A JP 2013211596 A JP2013211596 A JP 2013211596A JP 2014095897 A JP2014095897 A JP 2014095897A

- Authority

- JP

- Japan

- Prior art keywords

- liquid crystal

- source line

- pixel electrode

- display device

- crystal display

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3614—Control of polarity reversal in general

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

- G09G3/3659—Control of matrices with row and column drivers using an active matrix the addressing of the pixel involving the control of two or more scan electrodes or two or more data electrodes, e.g. pixel voltage dependant on signal of two data electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0852—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor being a dynamic memory with more than one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0209—Crosstalk reduction, i.e. to reduce direct or indirect influences of signals directed to a certain pixel of the displayed image on other pixels of said image, inclusive of influences affecting pixels in different frames or fields or sub-images which constitute a same image, e.g. left and right images of a stereoscopic display

- G09G2320/0214—Crosstalk reduction, i.e. to reduce direct or indirect influences of signals directed to a certain pixel of the displayed image on other pixels of said image, inclusive of influences affecting pixels in different frames or fields or sub-images which constitute a same image, e.g. left and right images of a stereoscopic display with crosstalk due to leakage current of pixel switch in active matrix panels

Abstract

【解決手段】オフ電流が著しく低いトランジスタを用いて、アクティブマトリクス型の液晶表示装置のスイッチングトランジスタを形成し、容量素子の面積を低減した上で、画素電極左端と第1のソース線が形成する寄生容量と、画素電極の右端が第2のソース線と形成する寄生容量の容量値を概略同程度とし、第1のソース線と第2のソース線に互いに極性のことなるビデオ信号を入力する液晶表示装置である。

【選択図】図1

Description

上記課題において、画像品質を維持するためには画素電極の電位を長時間保持する必要がある。画素電極の電位を保持している間、画素電極はトランジスタによってソース線と理想的には絶縁されており、フローティング状態となって電荷を保持している。しかしながら、トランジスタのソース−ドレイン間のリーク電流(オフ電流)が大きくなると、画素電極からソース線に電荷が移動し、画素電極の電位が変化してしまう。すなわち、アクティブマトリクス型の液晶表示装置において、画素電極の電位の保持時間は、各画素のトランジスタのオフ電流に大きく依存する。言い換えると、オフ電流の著しく低いトランジスタを画素に用いることにより、画素電極の電位を長時間保持することが可能となる。

また、オフ電流の著しく低いトランジスタを用いることにより、リーク電流による画素電極の電位の変化を抑制できることを示したが、画素電極の電位が変化する要因は、これだけに限られない。画素電極の電位が保持されている間、画素電極はフローティング状態となっており、容量素子の容量値が小さい場合、画素電極に形成された寄生容量によって当該画素電極の電位が変化するクロストークと呼ばれる現象が発生する。

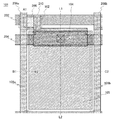

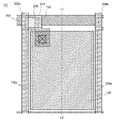

まず、本発明の一態様に係る液晶表示装置の画素の回路構成について図1乃至図6を用いて説明する。

画素101において、画像の表示には、トランジスタ102を介して画素電極に与えられたビデオ信号に対応する電位を保持し、液晶素子103の液晶層に当該電位を印加し続けることが必要である。画素電極は、ビデオ信号に対応する電位を保持している間、トランジスタ102をオフ状態とすることにより、ソース線と絶縁されており、フローティング状態となって電荷を保持している。しかしながら、トランジスタ102のソース−ドレイン間のリーク電流が大きくなると、保持していた電荷が画素電極からソース線に移動し、画素電極の電位が変化する。

しかしながら、画素電極の電位が変化する要因は、スイッチングトランジスタのリーク電流だけではない。ここで、図1(B)に画素101(Gi,Sj)の構成を示す。ここで、図1(B)では、液晶素子103に代わり画素電極105を図示している。上述の通り、画素101(Gi,Sj)は、ソース線Sjおよびソース線Sj+1に挟まれており、これらのソース線は画素電極105と十分近い距離に配置される。これにより、画素電極105とソース線Sjの間に第1の寄生容量106aが生じ、画素電極105とソース線Sj+1の間に第2の寄生容量106bが生じる。

図3(A)および図3(B)にソースライン反転駆動を行ったときに各画素に入力されるビデオ信号の極性を模式的に示す。図3(A)および図3(B)において、列方向に振られた符号はゲート線の符号G1〜Gmに対応しており、行方向に振られた符号はソース線の符号S1〜Snに対応している。+の符号が振られた画素には正の極性のビデオ信号が入力されており、−の符号が振られた画素には負の極性のビデオ信号が入力されている。また、図3(A)があるフレームに入力されるビデオ信号の極性を表しており、図3(B)は、図3(A)の次のフレームに入力されるビデオ信号の極性を表している。なお、図3(A)および図3(B)において、i行目は奇数の行に、j列目は奇数の列に、m行目は偶数の行に、n列目は偶数の列に対応している。

図3(C)および図3(D)にドット反転駆動を行ったときに各画素に入力されるビデオ信号の極性を模式的に示す。図3(C)および図3(D)において、列方向に振られた符号、行方向に振られた符号、+の符号、−の符号の意味は図3(A)および図3(B)と同様である。また、図3(C)と図3(D)の関係も図3(A)と図3(B)と同様である。なお、図3(C)および図3(D)において、i行目は奇数の行に、j列目は奇数の列に、m行目は偶数の行に、n列目は偶数の列に対応している。

図4(A)および図4(B)にゲートライン反転駆動を行ったときに各画素に入力されるビデオ信号の極性を模式的に示す。図4(A)および図4(B)において、列方向に振られた符号、行方向に振られた符号、+の符号、−の符号の意味は図3(A)および図3(B)と同様である。また、図4(A)と図4(B)の関係も図3(A)と図3(B)と同様である。なお、図4(A)および図4(B)において、i行目は奇数の行に、j列目は奇数の列に、m行目は偶数の行に、n列目は偶数の列に対応している。

図4(C)および図4(D)にフレーム反転駆動を行ったときに各画素に入力されるビデオ信号の極性を模式的に示す。図4(C)および図4(D)において、列方向に振られた符号、行方向に振られた符号、+の符号、−の符号の意味は図3(A)および図3(B)と同様である。また、図4(C)と図4(D)の関係も図3(A)と図3(B)と同様である。なお、図4(C)および図4(D)において、i行目は奇数の行に、j列目は奇数の列に、m行目は偶数の行に、n列目は偶数の列に対応している。

図4(C)に示すように、フレーム反転駆動においては、1つのフレーム期間内に入力されるビデオ信号の極性はすべての画素で同じである。図4(D)に示すように、次のフレーム期間内に入力されるビデオ信号の極性は、前のフレーム期間内に入力されるビデオ信号の極性とは逆になる。

ここで、図3および図4に示した任意の画素に注目すると、ソースライン反転駆動およびドット反転駆動では、図5(A)に示すようにソース線Sjに入力されるビデオ信号の極性(図5(A)では正の極性)とソース線Sj+1に入力されるビデオ信号の極性(図5(A)では負の極性)が互いに異なっている。それに対して、ゲートライン反転駆動およびフレーム反転駆動では、図5(B)に示すようにソース線Sjに入力されるビデオ信号の極性(図5(B)では正の極性)とソース線Sj+1に入力されるビデオ信号の極性(図5(B)では正の極性)が互いに同一である。

ここで、図1(A)に示す液晶表示装置を、ソースライン反転駆動を用いて動作させる場合のタイミングチャートを図6に示す。図6に示すタイミングチャートは、第1フレーム期間と第2フレーム期間における、ゲート線Gi、ソース線S1〜Snの電位と、これらのゲート線とソース線に接続された画素101(Gi,S1)〜画素101(Gi,Sn)の画素電極105の電位の変化を示している。

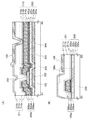

次に、本発明の一態様に係る液晶表示装置の画素の具体的な構成について図7乃至図12を用いて説明する。

また、画素電極の平面形状は、一般的に画素電極の左端の長さと右端の長さが大きく変わらない。そのため、距離d1と、距離d2との差が、−10%以上10%以下であればよく、−5%以上5%以下であればより好ましいとも言える。

基板200としては、透光性を有している基板が好ましく、例えば、ガラス、セラミックス、プラスチックを用いることができる。プラスチックとしては、FRP(Fiberglass−Reinforced Plastics)板、PVF(ポリビニルフルオライド)フィルム、ポリエステルフィルムまたはアクリル樹脂フィルムを用いることができる。

ゲート線202は、アルミニウム、チタン、クロム、コバルト、ニッケル、銅、イットリウム、ジルコニウム、モリブデン、ルテニウム、銀、タンタルおよびタングステンを一種以上含む導電膜を、単層で、または積層で用いることができる。また、ゲート線202と同じ層に設けられる容量線204も同様の材料を用いて形成すればよい。

ゲート絶縁膜205は、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルを一種以上含む絶縁膜を、単層で、または積層で用いればよい。なお、本明細書等において酸化窒化シリコンとは、その組成として、窒素よりも酸素の含有量が多いものを指し、窒化酸化シリコンとは、その組成として、酸素よりも窒素の含有量が多いものを指す。

上記のように酸化物半導体膜206に用いる酸化物半導体は、シリコンよりもバンドギャップが広いことが好ましい。例えば、バンドギャップが2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上の酸化物半導体を用いる。

また、酸化物半導体膜206に用いる酸化物半導体としては、非晶質酸化物半導体、単結晶酸化物半導体、及び多結晶酸化物半導体など様々な結晶状態のものを用いることができる。酸化物半導体として、CAAC−OS(C Axis Aligned Crystalline Oxide Semiconductor)膜を用いるのが好ましい。

また、酸化物半導体膜206は、組成や原子数比の異なる複数の酸化物半導体層が積層された構造としてもよい。また、結晶性の異なる酸化物半導体層どうしを積層しても良い。すなわち、単結晶酸化物半導体、多結晶酸化物半導体、非晶質酸化物半導体、及びCAAC−OSを適宜組み合わせた構成としてもよい。ここで、積層する各酸化物半導体層の構成元素を同一にすることで、各酸化物半導体層における界面の欠陥準位を低減し、当該酸化物半導体膜を用いたトランジスタの経時変化や信頼性試験によるしきい値電圧の変動量を低減することができる。

ソース線208a、ソース線208bおよびトランジスタ102のソース電極およびドレイン電極の他方として機能する導電膜210は同じ層に形成される。これらは、アルミニウム、チタン、クロム、コバルト、ニッケル、銅、イットリウム、ジルコニウム、モリブデン、ルテニウム、銀、タンタルおよびタングステンを一種以上含む導電膜を、単層で、または積層で用いればよい。

保護絶縁膜211は、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルを一種以上含む絶縁膜を、単層で、または積層で用いればよい。

画素電極105は、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、酸化インジウムスズ、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性の導電性材料を用いることができる。

なお、図7において本発明の一態様に係る液晶表示装置として、容量線204を設けて容量素子104を形成する構成を示したが、本発明はこれに限られるものではない。容量線を意図的に設けなくても十分な容量を画素電極に形成できる場合、図11に示すように容量線を設けない画素構成の液晶表示装置としても良い。このとき、容量線を含んで構成される容量素子は存在しないので、等価回路図上において容量素子の容量値は0fFということになる。なお、図11に示す液晶表示装置の画素構成は、容量線を設けていないことを除けば、図7に示す液晶表示装置の画素構成と同じなので、詳細は図7などに関する記載を参酌することができる。

また、図7において本発明の一態様に係る液晶表示装置は、複数の画素がマトリクス状に配置されるストライプ配置を想定しているが、本発明はこれに限られるものではない。例えば、図12(A)に示すように、複数の画素をデルタ配置で配列する構成とすることもできる。ただし、図7および図11に示す画素構成では、ソース線が直線状に列方向に延伸して設けられるが、図12(A)に示すように画素をデルタ配置する場合、ソース線が画素111のデルタ配置に合わせてS字状に屈曲して列方向に延伸して設けられる。なお、図12(A)に示す画素構成は、ソース線がS字状に屈曲して列方向に延伸して設けられていること以外は、図11に示す液晶表示装置の画素構成と同じである。また、図12(A)に示す画素構成において容量線は設けられていないが、図7に示す画素構成と同様に容量線を設けることができる。よって、図12に示す液晶表示装置の画素構成の詳細は図7および図11に関する記載を参酌することができる。

次に、図7および図8に示した液晶表示装置の作製工程の一例について図13および図14を用いて説明する。図13および図14は、図7に示す一点鎖線A1−A2およびB1−B2に対応する断面図である。

次に、本発明の一態様に係る液晶表示装置の具体的な構成について、図16を用いて説明する。

次に本発明の一態様に係る液晶表示装置を備えた電子機器について図17を用いて説明する。このような電子機器としては、テレビ受像器、ビデオカメラ、デジタルカメラ等のカメラ、ゴーグル型ディスプレイ、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、コンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、高機能携帯電話(スマートフォン)、携帯型遊技機、電子書籍、またはタブレット型端末等)、記録媒体を備えた画像再生装置(具体的には、記録媒体を再生し、その画像を表示しうる表示装置を備えた装置)などが挙げられる。以下に具体的な構成を示す。

101 画素

102 トランジスタ

103 液晶素子

104 容量素子

105 画素電極

106a 寄生容量

106b 寄生容量

111 画素

200 基板

202 ゲート線

204 容量線

205 ゲート絶縁膜

206 酸化物半導体膜

208a ソース線

208b ソース線

210 導電膜

211 保護絶縁膜

212 配線

215 導電膜

218 配線

222 開口

224 開口

226 開口

400 対向基板

402 画素部

403 ソース線駆動回路

404 ゲート線駆動回路

405 シール材

408 液晶層

412 トランジスタ

415 接続端子電極

416 端子電極

418 FPC

419 異方性導電膜

431 対向電極

432 絶縁層

433 絶縁層

435 構造体

600 筐体

601 ボタン

602 マイクロフォン

603 表示部

604 スピーカ

605 カメラ

611 筐体

612 筐体

613 表示部

614 表示部

615 マイクロフォン

616 スピーカ

617 操作ボタン

618 スタイラス

620 筐体

621 筐体

622 表示部

623 表示部

624 具

625 操作スイッチ

631 筐体

632 表示部

633 支持台

640 筐体

641 操作ボタン

643 表示部

650 筐体

651 表示部

653 スピーカ

655 操作キー

656 接続端子

657 ポインティングデバイス

658 外部接続ポート

Claims (6)

- 行方向に延伸して設けられた複数のゲート線と、

列方向に延伸して設けられた複数のソース線と、

前記複数のゲート線および前記複数のソース線と電気的に接続され、マトリクス状に設けられた複数の画素と、を有し、

前記複数の画素の一は、

第1のゲート線および第1のソース線と電気的に接続された、酸化物半導体を含むトランジスタと、

前記トランジスタと電気的に接続された画素電極と、を含み、

前記第1のソース線に入力されるビデオ信号の極性は、当該第1のソース線と前記画素電極を挟んで隣接して設けられる第2のソース線に入力されるビデオ信号の極性と互いに異なり、

前記画素電極と前記第1のソース線との間に形成される寄生容量の容量値に対する、前記画素電極と前記第2のソース線との間に形成される寄生容量の容量値の差分が、−10%以上10%以下である、液晶表示装置。 - 前記画素電極は、前記第1のソース線と前記第2のソース線との2等分線に対して概略左右対称な平面形状を有する、請求項1に記載の液晶表示装置。

- 前記画素電極の第1の配線側の端部と前記第1の配線との距離と、前記画素電極の第2の配線側の端部と前記第2の配線との距離とが概略同一である、請求項1に記載の液晶表示装置。

- 前記複数のゲート線と同じ層に複数の容量線が設けられ、

前記画素において、前記容量線の一を含む容量素子の容量値が30fF以下となる、請求項1乃至3のいずれか一に記載の液晶表示装置。 - 前記ゲート線と、前記ソース線は、1インチあたり300本以上の密度で設けられる、請求項1乃至4のいずれか一に記載の液晶表示装置。

- 前記酸化物半導体は、シリコンよりもバンドギャップが広く、且つシリコンよりも真性キャリア密度が低い請求項1乃至5のいずれか一に記載の液晶表示装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013211596A JP2014095897A (ja) | 2012-10-12 | 2013-10-09 | 液晶表示装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012226973 | 2012-10-12 | ||

| JP2012226973 | 2012-10-12 | ||

| JP2013211596A JP2014095897A (ja) | 2012-10-12 | 2013-10-09 | 液晶表示装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2014095897A true JP2014095897A (ja) | 2014-05-22 |

| JP2014095897A5 JP2014095897A5 (ja) | 2016-10-20 |

Family

ID=50474887

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013211596A Withdrawn JP2014095897A (ja) | 2012-10-12 | 2013-10-09 | 液晶表示装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US20140104151A1 (ja) |

| JP (1) | JP2014095897A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2021510426A (ja) * | 2018-01-11 | 2021-04-22 | アプライド マテリアルズ インコーポレイテッドApplied Materials,Incorporated | 金属酸化物スイッチを含み小型蓄電コンデンサを備えた薄膜トランジスタ |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6290576B2 (ja) | 2012-10-12 | 2018-03-07 | 株式会社半導体エネルギー研究所 | 液晶表示装置及びその駆動方法 |

| US20140111558A1 (en) * | 2012-10-23 | 2014-04-24 | Semiconductor Energy Laboratory Co., Ltd. | Display device and program |

| JP6216125B2 (ja) | 2013-02-12 | 2017-10-18 | 株式会社半導体エネルギー研究所 | 発光装置 |

| JP5811228B2 (ja) * | 2013-06-24 | 2015-11-11 | 大日本印刷株式会社 | 画像処理装置、表示装置並びに画像処理方法及び画像処理用プログラム |

| US9257290B2 (en) * | 2013-12-25 | 2016-02-09 | Shenzhen China Star Optoelectronics Technology Co., Ltd. | Low temperature poly-silicon thin film transistor and manufacturing method thereof |

| KR102367921B1 (ko) | 2014-03-14 | 2022-02-25 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 회로 시스템 |

| WO2016038508A1 (en) | 2014-09-12 | 2016-03-17 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

| CN105138177A (zh) * | 2015-09-10 | 2015-12-09 | 深圳市华星光电技术有限公司 | 触控显示面板及触控显示装置 |

| US10573667B2 (en) | 2015-12-11 | 2020-02-25 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

| WO2018130930A1 (en) | 2017-01-16 | 2018-07-19 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0922023A (ja) * | 1995-07-06 | 1997-01-21 | Toshiba Corp | アクティブマトリクス型液晶表示装置 |

| JP2002250937A (ja) * | 2001-02-27 | 2002-09-06 | Matsushita Electric Ind Co Ltd | アクティブマトリクス液晶表示素子 |

| US20070236414A1 (en) * | 2006-03-28 | 2007-10-11 | Hsiang-Lin Lin | Liquid Crystal Display |

| JP2008216475A (ja) * | 2007-03-01 | 2008-09-18 | Hitachi Displays Ltd | 表示装置および表示装置の製造方法 |

| JP2011138118A (ja) * | 2009-12-04 | 2011-07-14 | Semiconductor Energy Lab Co Ltd | 表示装置 |

| JP2011150315A (ja) * | 2009-12-24 | 2011-08-04 | Semiconductor Energy Lab Co Ltd | 表示装置 |

| JP2012032799A (ja) * | 2010-07-01 | 2012-02-16 | Semiconductor Energy Lab Co Ltd | 液晶表示装置の駆動方法 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100940909B1 (ko) * | 2003-06-10 | 2010-02-08 | 엘지디스플레이 주식회사 | 반사투과형 액정표시장치 |

| KR100532087B1 (ko) * | 2003-06-20 | 2005-11-30 | 엘지.필립스 엘시디 주식회사 | 액정표시장치 |

| KR20050008040A (ko) * | 2003-07-14 | 2005-01-21 | 삼성에스디아이 주식회사 | 주사 전극 라인을 사용하여 저장 캐페시터가 형성된필드-순차형 액정 디스플레이 패널 |

| CN100568457C (zh) * | 2003-10-02 | 2009-12-09 | 株式会社半导体能源研究所 | 半导体装置的制造方法 |

| US20060147845A1 (en) * | 2005-01-05 | 2006-07-06 | Flanigan Kyle Y | Electrically reconfigurable photolithography mask for semiconductor and micromechanical substrates |

| KR101476841B1 (ko) * | 2006-12-28 | 2014-12-24 | 엘지디스플레이 주식회사 | 시야각 제어 액정표시장치 |

| TWI332646B (en) * | 2007-04-03 | 2010-11-01 | Au Optronics Corp | Lcd and driving method thereof |

| RU2444068C2 (ru) * | 2008-01-10 | 2012-02-27 | Шарп Кабусики Кайся | Подложка активной матрицы и жидкокристаллическое устройство отображения |

| US20110221797A1 (en) * | 2008-11-20 | 2011-09-15 | Ken Inada | Image display device |

| KR101681642B1 (ko) * | 2009-10-27 | 2016-12-02 | 삼성디스플레이 주식회사 | 액정 표시 장치 및 이의 제조 방법 |

| US8988624B2 (en) * | 2011-06-23 | 2015-03-24 | Apple Inc. | Display pixel having oxide thin-film transistor (TFT) with reduced loading |

| JP5520897B2 (ja) * | 2011-08-11 | 2014-06-11 | 株式会社ジャパンディスプレイ | 液晶表示装置 |

| CN102629053A (zh) * | 2011-08-29 | 2012-08-08 | 京东方科技集团股份有限公司 | 阵列基板及显示装置 |

-

2013

- 2013-10-09 JP JP2013211596A patent/JP2014095897A/ja not_active Withdrawn

- 2013-10-10 US US14/050,931 patent/US20140104151A1/en not_active Abandoned

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0922023A (ja) * | 1995-07-06 | 1997-01-21 | Toshiba Corp | アクティブマトリクス型液晶表示装置 |

| JP2002250937A (ja) * | 2001-02-27 | 2002-09-06 | Matsushita Electric Ind Co Ltd | アクティブマトリクス液晶表示素子 |

| US20070236414A1 (en) * | 2006-03-28 | 2007-10-11 | Hsiang-Lin Lin | Liquid Crystal Display |

| JP2008216475A (ja) * | 2007-03-01 | 2008-09-18 | Hitachi Displays Ltd | 表示装置および表示装置の製造方法 |

| JP2011138118A (ja) * | 2009-12-04 | 2011-07-14 | Semiconductor Energy Lab Co Ltd | 表示装置 |

| JP2011150315A (ja) * | 2009-12-24 | 2011-08-04 | Semiconductor Energy Lab Co Ltd | 表示装置 |

| JP2012032799A (ja) * | 2010-07-01 | 2012-02-16 | Semiconductor Energy Lab Co Ltd | 液晶表示装置の駆動方法 |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2021510426A (ja) * | 2018-01-11 | 2021-04-22 | アプライド マテリアルズ インコーポレイテッドApplied Materials,Incorporated | 金属酸化物スイッチを含み小型蓄電コンデンサを備えた薄膜トランジスタ |

| JP7171738B2 (ja) | 2018-01-11 | 2022-11-15 | アプライド マテリアルズ インコーポレイテッド | 金属酸化物スイッチを含み小型蓄電コンデンサを備えた薄膜トランジスタ |

| US11895872B2 (en) | 2018-01-11 | 2024-02-06 | Applied Materials, Inc. | Thin film transistor with small storage capacitor with metal oxide switch |

Also Published As

| Publication number | Publication date |

|---|---|

| US20140104151A1 (en) | 2014-04-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7407253B2 (ja) | 表示装置、電子機器 | |

| JP7434388B2 (ja) | 半導体装置 | |

| JP2014095897A (ja) | 液晶表示装置 | |

| JP2020205427A (ja) | 液晶表示装置 | |

| KR102378241B1 (ko) | 표시 장치 | |

| TWI703713B (zh) | 顯示裝置 | |

| JP6556998B2 (ja) | 表示装置 | |

| US9269315B2 (en) | Driving method of semiconductor device | |

| JP2022058513A (ja) | 表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160902 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160902 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170531 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170606 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170801 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180123 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20180320 |