JP2012209339A - フィン型電界効果トランジスタ - Google Patents

フィン型電界効果トランジスタ Download PDFInfo

- Publication number

- JP2012209339A JP2012209339A JP2011072295A JP2011072295A JP2012209339A JP 2012209339 A JP2012209339 A JP 2012209339A JP 2011072295 A JP2011072295 A JP 2011072295A JP 2011072295 A JP2011072295 A JP 2011072295A JP 2012209339 A JP2012209339 A JP 2012209339A

- Authority

- JP

- Japan

- Prior art keywords

- bulk

- region

- field effect

- effect transistor

- fin

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 230000005669 field effect Effects 0.000 title claims abstract description 64

- 239000000758 substrate Substances 0.000 claims abstract description 25

- 230000005684 electric field Effects 0.000 claims abstract description 14

- 239000004065 semiconductor Substances 0.000 claims description 90

- 230000000694 effects Effects 0.000 abstract description 11

- 238000000034 method Methods 0.000 abstract description 6

- 239000010410 layer Substances 0.000 description 65

- 229910052751 metal Inorganic materials 0.000 description 10

- 239000002184 metal Substances 0.000 description 10

- 239000011229 interlayer Substances 0.000 description 7

- 238000005520 cutting process Methods 0.000 description 6

- 238000005229 chemical vapour deposition Methods 0.000 description 5

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 4

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 4

- 229910052814 silicon oxide Inorganic materials 0.000 description 4

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 3

- 239000012535 impurity Substances 0.000 description 3

- 239000000463 material Substances 0.000 description 3

- 229910052719 titanium Inorganic materials 0.000 description 3

- 239000010936 titanium Substances 0.000 description 3

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 2

- 230000007935 neutral effect Effects 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 210000004690 animal fin Anatomy 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 230000001681 protective effect Effects 0.000 description 1

- 238000004335 scaling law Methods 0.000 description 1

- 239000002210 silicon-based material Substances 0.000 description 1

- 230000001629 suppression Effects 0.000 description 1

Images

Landscapes

- Thin Film Transistor (AREA)

Abstract

【課題】フィン型電界効果トランジスタはその動作原理から、低消費電力化を図るためには、動作時のバルク領域は完全空乏化される必要があった。結果として、プロセスばらつきがバルク領域のばらつきを生み、消費電力にばらつきを与えるという問題が生じていた。

【解決手段】本発明のフィン型電界効果トランジスタは、ゲート絶縁膜を介してチャネル領域に電界を印加するためのゲート電極を備えるフィン型電界効果トランジスタにおいて、バルク領域に所定の電位を印加するためのバルク電極を、ゲート電極と別に備えられている。このような構造にすることで、フィンの幅を空乏層程度に保つことを必要せず、基板電位を変化させることでデバイスの特性を変化させる、基板バイアス効果によって消費電力を削減することが可能となる。

【選択図】図1

【解決手段】本発明のフィン型電界効果トランジスタは、ゲート絶縁膜を介してチャネル領域に電界を印加するためのゲート電極を備えるフィン型電界効果トランジスタにおいて、バルク領域に所定の電位を印加するためのバルク電極を、ゲート電極と別に備えられている。このような構造にすることで、フィンの幅を空乏層程度に保つことを必要せず、基板電位を変化させることでデバイスの特性を変化させる、基板バイアス効果によって消費電力を削減することが可能となる。

【選択図】図1

Description

本発明は、MOS電界効果型トランジスタ(以下、MOSFETと記載する)に関し、起立型のチャネルを有するフィン型電界効果トランジスタに関するものである。

近年の電子機器は、小型化や低消費電力化しているために、それに用いるLSIもまた微細化や低消費電力化の要求がある。多くの場合、搭載する半導体素子のサイズをスケーリング則に従って微細化することで対応してきた。

半導体産業におけるスケーリング則とは、MOSFETのサイズと電源電圧とを1/κ倍にすれば、MOSFETの動作が保証された上で、スイッチング速度が1/κ倍に、消費電力は1/κ2倍となるという、公知の法則である。

しかし、さらに低い電源電圧下で一定の性能を維持するためには、MOSFETのしきい値電圧を低く設定する必要がある。そのためには、ゲート絶縁膜の薄膜化が必要となる。 ところが、ゲート絶縁膜の薄膜化は、スタンバイリーク電流の増大を招き、LSIの消費電力が増大してしまうという問題が生じる。

近年のLSIにあっては、電子機器の小型化や低消費電力化の流れから、低消費電力化は必要不可欠であり、低消費電力化を可能とした新たな半導体素子が提案されてきている。

近年のLSIにあっては、電子機器の小型化や低消費電力化の流れから、低消費電力化は必要不可欠であり、低消費電力化を可能とした新たな半導体素子が提案されてきている。

そのような新たな半導体素子の代表的なものの1つとして、フィン型電界効果トランジスタが提案されている。

フィン型電界効果トランジスタとは、起立型のチャネル領域を有するMOSFETである。起立したチャネル領域は、半導体基板の上部に絶縁膜を設け、その上部に形成する半導体層(単結晶シリコン材料)にソース領域やドレイン領域、バルク領域(この中にチャネル領域を形成する)を備える。この半導体層の形状が魚のヒレに似ていることからフィン型電界効果トランジスタと呼ばれる。

フィン型電界効果トランジスタとは、起立型のチャネル領域を有するMOSFETである。起立したチャネル領域は、半導体基板の上部に絶縁膜を設け、その上部に形成する半導体層(単結晶シリコン材料)にソース領域やドレイン領域、バルク領域(この中にチャネル領域を形成する)を備える。この半導体層の形状が魚のヒレに似ていることからフィン型電界効果トランジスタと呼ばれる。

フィン型電界効果トランジスタは、多くの場合は半導体層の垂直端面にチャネル領域を設ける構造である。このため、その半導体層の垂直方向の高さがMOSFETのチャネル幅となる。そして、このチャネル領域である半導体層の垂直端面にゲート電極を備えている。

フィン型電界効果トランジスタは、このように半導体基板の上部に起立した半導体層を有しているため、半導体基板内にチャネル領域を有する通常のMOSFET(便宜的に、バルク型MOSFETと称することにする)と比べて小型化できるという特徴がある。

また、半導体層に対して複数のゲート電極を設けることもできるため、ゲート電極が1つの場合に比べてしきい値のばらつきを抑制し、低いしきい値を有するMOSFETを構成することができる(例えば、特許文献1参照。)。

特許文献1に示した従来技術は、フィン型電界効果トランジスタを構成する半導体層上面を厚い絶縁膜で覆い、左右の側壁(垂直端面)に分離された2つのゲート電極を設けてこれを配線で連結した構造である。

特許文献1に示した従来技術によるフィン型電界効果トランジスタは、ゲート電極が複

数個存在し、起立した半導体層の左右の垂直端面から電界を印加できるため、空乏層が素早くバルク領域(バルク型MOSFETで言うところの基板領域)を覆い、ピンチオフする前にトランジスタ動作を始めることができる。

ゲート電極が1つしかないMOSFETの場合は、チャネル領域から空乏層方向への電位変化が急であるのに対し特許文献1に示した従来技術によるフィン型電界効果トランジスタは、その電位の変化も比較的安定する。加えて、複数のゲート電極が分離された構造のため、通常のフィン型電界効果トランジスタよりしきい値の制御に適している。

数個存在し、起立した半導体層の左右の垂直端面から電界を印加できるため、空乏層が素早くバルク領域(バルク型MOSFETで言うところの基板領域)を覆い、ピンチオフする前にトランジスタ動作を始めることができる。

ゲート電極が1つしかないMOSFETの場合は、チャネル領域から空乏層方向への電位変化が急であるのに対し特許文献1に示した従来技術によるフィン型電界効果トランジスタは、その電位の変化も比較的安定する。加えて、複数のゲート電極が分離された構造のため、通常のフィン型電界効果トランジスタよりしきい値の制御に適している。

ところで、フィン型電界効果トランジスタのような、バルク型MOSFETではない半導体素子の構造には、部分空乏型と完全空乏型の2種類がある。部分空乏型は、バルク領域を完全に空乏化せず一部中性領域を有するものであって、完全空乏型はバルク領域をすべて空乏化するものである。

一般的に、部分空乏型は、ソース領域やドレイン領域の耐圧を高くすることができるという特徴がある。しかし、バルク領域内に中性領域が存在するため、基板浮遊効果に対する対策を講じる必要がある。

完全空乏型は部分空乏型に比べて、ソース領域やドレイン領域とバルク領域との間の接合容量が小さく、電流駆動能力の指標となるサブスレッショルド特性が良いという特徴がある。また、基板浮遊効果が大変少ないという特徴もある。そして、オフリーク電流が小さくできるので、換言すれば、オフリーク電流を同じにすれば、動作電圧を下げることができる。

完全空乏型は部分空乏型に比べて、ソース領域やドレイン領域とバルク領域との間の接合容量が小さく、電流駆動能力の指標となるサブスレッショルド特性が良いという特徴がある。また、基板浮遊効果が大変少ないという特徴もある。そして、オフリーク電流が小さくできるので、換言すれば、オフリーク電流を同じにすれば、動作電圧を下げることができる。

部分空乏型と完全空乏型とは、それぞれ利点があり、用途によって使い分けがなされているが、半導体素子の低消費電力化という観点で言えば、完全空乏型が有利である。低い動作電圧で動作するということは、すなわち、しきい値も下げることができるからである。

フィン型電界効果トランジスタにあっては、低電圧駆動、低消費電力化するためには、ゲート電極から電圧を印加してトランジスタ動作させるときに、少なくともバルク領域が完全空乏化していなければならない。

特許文献1に示した従来技術によるフィン型電界効果トランジスタのように、起立した半導体層の垂直端面にチャネル領域を設け、そこに対向して2つのゲート電極を備えると、その半導体層の厚さが厚いと、そのチャネル領域は完全空乏化できない。無理に完全空乏化しようとすると、ゲート電極からの電界をさらに上げなければならず、低消費電力化の流れに逆行してしまう。

また、このような状況を回避するために、チャネル領域となる起立した半導体層の平面的な厚さを薄くしようとすると、製造工程における加工ばらつき(寸法ばらつき)の影響を受けてしまい、電気特性が安定した半導体素子を構成することはできない。

特許文献1に示した従来技術は、2つのゲート電極からの電界によりしきい値を制御できるという利点があるものの、バルク領域を完全空乏化した状態で電気的に安定して動作させることは困難であるから、低消費電力化が困難である。また、半導体素子の電気特性

を安定させることもまた難しい。

を安定させることもまた難しい。

本発明は、このような問題を解決するためになされたものである。フィン型電界効果トランジスタの低消費電力化と電気特性の安定化とを両立したフィン型電界効果トランジスタを提供できる。

上記目的を達成するために、本発明のフィン型電界効果トランジスタは、下記記載の構造を採用する。

本発明のフィン型電界効果トランジスタは、半導体基板上に設ける絶縁膜と、絶縁膜上に設ける半導体層と、を備え、半導体層の所定の部分にバルク領域、ソース領域、チャネル領域、ドレイン領域を備え、チャネル領域の前記半導体層表面にゲート絶縁膜を備え、ゲート絶縁膜を介して前記チャネル領域に電界を印加するためのゲート電極を備えるフィン型電界効果トランジスタにおいて、バルク領域に所定の電位を印加するためのバルク電極を、ゲート電極と別に備えることを特徴とする。

このような構成とすることによって、バルク領域に直接電位を印加できるから、低いしきい値を実現し、しきい値のばらつきとリーク電流とを抑制し、低消費電力化ができる。

半導体層の第1の垂直端面にチャネル領域を設け、半導体層の第1の垂直端面と対向する第2の垂直端面に前記バルク領域を設けるようにしてもよい。

このような構成とすることによって、半導体層の幅を任意に定義できるから、フィン型電界効果トランジスタの平面的な面積を小さくすることができる。また、チャネル領域と対向する部分にバルク領域を設けることにより、チャネル領域と同じ面積のバルク領域が対向することになるので、基板バイアスのための電位にむらがない。

ゲート絶縁膜は、第1の垂直端面に設けるようにしてもよい。

このような構成とすることによって、半導体層の垂直方向の高さがチャネル幅とすることができ、垂直方向に制限がなければ半導体層の厚さでドレイン電流を任意に定義することができる。

ゲート電極は、第1の垂直端面に対向して設け、バルク電極は、第2の垂直端面に対向して設けると共に前記バルク領域に直接接続するようにしてもよい。

このような構成とすることによって、第1の垂直端面からはゲート電界を印加でき、第2の垂直端面からはバルク電位を与えることができ、MOSFETとしての電気特性を安定させることができる。

本発明のフィン型電界効果トランジスタは、バルク領域に任意の電位を直接印加できるから、しきい値電圧を任意の値に定めることができ、動作時には低いしきい値に、非動作時には高いしきい値に保つことで、理想的なサブスレッショルドウィングを行うことができるため、低リーク電流を実現できる。

また、この構造のため、基板バイアス効果を利用することができ、フィン型電界効果トランジスタで問題であった、半導体層の寸法ばらつきによるしきい値のばらつきを防ぐことが可能となる。そのため、低消費電力を実現できると共に、半導体層の厚さを完全空乏

層の深さ程度に抑える必要がなくなり、その製造が容易となる。

層の深さ程度に抑える必要がなくなり、その製造が容易となる。

本発明のフィン型電界効果トランジスタは、絶縁膜上に設けられたフィン型電界効果トランジスタのバルク領域に所定の電位を直接印加するためのバルク電極を、ゲート電極と別に備えることで低いしきい値を実現すると共にし、しきい値のばらつきを抑制している。

以下、図面を用いてフィン型電界効果トランジスタを説明する。以下に示す実施形態については、フィン型電界効果トランジスタは、SOI(Silicon−On−Insulator)基板を用いて作成される例で説明する。そして、フィン型電界効果トランジスタの導電型をNチャネル型MOSFET(以下、N型MOSFETと記載する)とする例で説明する。また、説明に必要の無い構成(例えば、最終保護膜やソース電極、ドレイン電極など)は、図面を見やすくするために省略する。

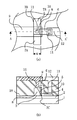

[本発明の第1の実施形態の構成説明:図1]

第1の実施形態のフィン型電界効果トランジスタの全体的な構成を、図1を用いて説明する。図1はフィン型電界効果トランジスタの構造を模式的に示す平面図及び断面図であって、図1(a)に平面図を、図1(b)にその切断線A−A´で切断した断面図を示す。

第1の実施形態のフィン型電界効果トランジスタの全体的な構成を、図1を用いて説明する。図1はフィン型電界効果トランジスタの構造を模式的に示す平面図及び断面図であって、図1(a)に平面図を、図1(b)にその切断線A−A´で切断した断面図を示す。

図1において、1は半導体基板、2は絶縁膜である。3は半導体層、3Aは半導体層3の第1の垂直端面、3Bは半導体層3の第2の垂直端面、3Cは半導体層3の上端面である。4はゲート絶縁膜、5はチャネル領域、6はゲート電極である。7Aはソース領域、7Bはドレイン領域、8はバルク領域、9はバルク電極、10は層間絶縁膜、11はコンタクトホール、12は金属配線である。

第1の実施形態のフィン型電界効果トランジスタは、SOI基板を用いて作成される。半導体基板1は単結晶シリコンよりなる支持基板である。絶縁膜2は埋め込み酸化膜であるシリコン酸化膜である。半導体層3は単結晶シリコンであり、絶縁膜2を介し設けられる。この半導体層3は半導体基板1に対して起立している。

ところで、SOI基板を用いなくてもフィン型電界効果トランジスタを形成できる。例えば、半導体基板1の上部に酸化処理などしてシリコン酸化膜からなる絶縁膜2を形成し、この絶縁膜2上に化学気相成長法(以下、CVD法と記載する)によりアモルファスシ

リコン膜を形成する。その後、熱処理を実施することにより単結晶化させ半導体層3を形成することもできる。この場合、半導体層3は単結晶膜を絶縁膜2上に形成後、エッチング処理することで所定の形状に加工する。

リコン膜を形成する。その後、熱処理を実施することにより単結晶化させ半導体層3を形成することもできる。この場合、半導体層3は単結晶膜を絶縁膜2上に形成後、エッチング処理することで所定の形状に加工する。

半導体層3は、第1の垂直端面3Aと第2の垂直端面3Bとが対向すると共に、平行して位置する形状を有している。N型MOSFETの場合、半導体層3の導電型はP型である。

半導体層3には、ソース領域7Aとドレイン領域7Bとの間にバルク領域8が設けてある。このバルク領域8にチャネル領域5が設けている。この構成は、バルク型MOSFETと同様である。

ゲート絶縁膜4は、半導体層3の表面に設けている。詳しくは、この半導体層3に設ける、ソース領域7Aとドレイン領域7Bとに挟まれるチャネル領域5の第1の垂直端面3Aの表面に設けている。

このゲート絶縁膜4は、既知の手法により、単結晶シリコンである半導体層3を熱酸化することで形成しており、膜厚は、例えば8nmである。

ゲート絶縁膜4は、半導体層3の表面に設けている。詳しくは、この半導体層3に設ける、ソース領域7Aとドレイン領域7Bとに挟まれるチャネル領域5の第1の垂直端面3Aの表面に設けている。

このゲート絶縁膜4は、既知の手法により、単結晶シリコンである半導体層3を熱酸化することで形成しており、膜厚は、例えば8nmである。

ゲート電極6は、ゲート絶縁膜4を覆うようにしてチャネル領域5上に設けている。ゲート電極6は、例えば、CVD法により形成した多結晶シリコンより成る。膜厚は、例えば、350nmである。

ソース領域7Aとドレイン領域7Bとは、上述のように、平面的にバルク領域8を挟むように設けており、バルク領域8の第1の垂直端面3Aにチャネル領域5を設けている。

ソース領域7Aとドレイン領域7Bとは高濃度の不純物層より成り、不純物は、例えば、N型MOSFETの場合、砒素(As)又はリン(P)であり、10E−15atoms/cm2程度のドーズ量(不純物量)でイオン注入されて形成されたものである。

ソース領域7Aとドレイン領域7Bとは高濃度の不純物層より成り、不純物は、例えば、N型MOSFETの場合、砒素(As)又はリン(P)であり、10E−15atoms/cm2程度のドーズ量(不純物量)でイオン注入されて形成されたものである。

バルク電極9は、ゲート電極6とは別に設けるバルク領域8に直接電位を印加する電極であり、半導体層3の上端面3Cの表面に直接接するように設けている。平面的には、ソース領域7Aとドレイン領域7Bとに挟まれるバルク領域8の表面に、ゲート電極6と離間して設けている。

バルク電極9は、例えば、チタンとアルミニウムとの積層膜などが望ましい。半導体層3であるシリコン表面には自然酸化膜が発生しているが、チタンと半導体層3であるシリコンとをシリサイド化させることにより、半導体層3とバルク電極9との間で電気的に良好な接続を得ることができ、電圧制御に適しているためである。

さらに、層間絶縁膜10を全面に設け、層間絶縁膜10にコンタクトホール11を設け、金属配線12がゲート電極6に接続し、バルク電極9がバルク領域8に接続している。

この金属配線12とバルク電極9とは、それぞれ本実施形態において同じ材料、同じプロセスで形成され、図示しない所定の回路素子や端子に接続している。

層間絶縁膜10は、例えば、CVD法により形成したシリコン酸化膜である。金属配線12は、例えば、チタンとアルミニウムの積層膜より成る。

この金属配線12とバルク電極9とは、それぞれ本実施形態において同じ材料、同じプロセスで形成され、図示しない所定の回路素子や端子に接続している。

層間絶縁膜10は、例えば、CVD法により形成したシリコン酸化膜である。金属配線12は、例えば、チタンとアルミニウムの積層膜より成る。

ソース領域7A及びドレイン領域7Bにも電気的な接続を行い、電気信号の授受を行う必要がある。これらの領域と平面的に重なる部分の層間絶縁膜10にコンタクトホール11を設け、金属配線にて電気的な接続を行う。なお、これらの構造についてはすでに説明したとおり、図示を省略している。

ところで、一般的にフィンの幅とは、図1に記号Wで示す、対向する第1の垂直端面3

Aと第2の垂直端面3Bとに挟まれる半導体層3の距離に相当する。

この距離Wが狭いと、すでに説明したように加工精度の影響を受けてしまい、電気特性が安定しなくなり、厚いと低消費電力化のための完全空乏化がしにくくなるのである。

しかし、本発明のフィン型電界効果トランジスタは、バルク電極9を設けており、バルク領域8に直接電圧を印加できるため、バルク領域8の電位を自由に制御できる。このため、距離Wが厚くても、完全空乏化することができる。

Aと第2の垂直端面3Bとに挟まれる半導体層3の距離に相当する。

この距離Wが狭いと、すでに説明したように加工精度の影響を受けてしまい、電気特性が安定しなくなり、厚いと低消費電力化のための完全空乏化がしにくくなるのである。

しかし、本発明のフィン型電界効果トランジスタは、バルク電極9を設けており、バルク領域8に直接電圧を印加できるため、バルク領域8の電位を自由に制御できる。このため、距離Wが厚くても、完全空乏化することができる。

[第1の実施形態の動作の説明]

次に、第1の実施形態のフィン型電界効果トランジスタの構造をまとめ、駆動の様子について説明する。

フィン型電界効果トランジスタは、半導体基板1の上部に設けている絶縁膜2上に起立して半導体層3を設けている。この半導体層3は、フィンを構成する。

半導体層3のバルク領域8の第1の垂直端面3Aの表面にはチャネル領域5を設けており、そのチャネル領域5を覆うようにゲート絶縁膜5を設け、このゲート絶縁膜5を介しゲート電極6を設けている。

そして、半導体層3の上端面3Cと直接接続するようにバルク電極9を備えている。

次に、第1の実施形態のフィン型電界効果トランジスタの構造をまとめ、駆動の様子について説明する。

フィン型電界効果トランジスタは、半導体基板1の上部に設けている絶縁膜2上に起立して半導体層3を設けている。この半導体層3は、フィンを構成する。

半導体層3のバルク領域8の第1の垂直端面3Aの表面にはチャネル領域5を設けており、そのチャネル領域5を覆うようにゲート絶縁膜5を設け、このゲート絶縁膜5を介しゲート電極6を設けている。

そして、半導体層3の上端面3Cと直接接続するようにバルク電極9を備えている。

フィン型電界効果トランジスタを駆動する際は、ゲート電極6にゲート電圧を印加する。 そして、このゲート電極6とは別に設けているバルク電極9からは、バルク領域8に直接電位を印加するためのバルク電圧を印加する。

チャネル領域5は、このゲート電圧による電界により導電型が反転し、この反転した領域を介してソース領域7Aとドレイン領域7Bとが導通する。つまり、半導体層3の第1の垂直端面3A表面部分に沿って電流が流れるのである。

すでに説明したように、本発明のフィン型電界効果トランジスタは、ゲート電圧をゲート電極6からゲート絶縁膜4を介してチャネル領域5に電界として印加し、バルク電極9からは電界ではなくバルク電位をバルク領域8に直接印加できる。電界を与えるのではないから正確にバルク領域8の電位を制御できる。

従来から知られているSOI基板を用いた半導体素子には、半導体基板側から絶縁膜を介して電界を半導体層に与えていた例が提案されていたが、そのような構成とはまったく異なる構成である。

従来から知られているSOI基板を用いた半導体素子には、半導体基板側から絶縁膜を介して電界を半導体層に与えていた例が提案されていたが、そのような構成とはまったく異なる構成である。

ゲート電極6からチャネル領域5に印加する電界と、バルク電極9からバルク領域8に印加される電位との関係を、フィン型電界効果トランジスタに望む電気特性に応じて自由に変更することができる。

例えば、ゲート電極6から印加するゲート電圧とバルク電極9から印加するバルク電圧とを同じにすることができる。

こうすると、このフィン型電界効果トランジスタを、知られているDTMOSFETとして動作させることができる。

こうすると、このフィン型電界効果トランジスタを、知られているDTMOSFETとして動作させることができる。

もちろんこれは一例であって、双方の電圧値を変えてもよい。

例えば、バルク電極9からバルク領域8に所定の電位を与えることにより、バルク領域8の電位を低くすると、バルク領域8とゲート電圧との間の電位差が大きくなるから、フィン型電界効果トランジスタのしきい値電圧を上げることができる。そうすると、リーク電流を削減でき、低消費電力化ができる。

また、反対にバルク領域8の電位を高くすると、バルク領域8とゲート電圧との間の電位差が小さくなるから、しきい値電圧を下げることができる。そうすると、高速動作を実現することができる。

例えば、バルク電極9からバルク領域8に所定の電位を与えることにより、バルク領域8の電位を低くすると、バルク領域8とゲート電圧との間の電位差が大きくなるから、フィン型電界効果トランジスタのしきい値電圧を上げることができる。そうすると、リーク電流を削減でき、低消費電力化ができる。

また、反対にバルク領域8の電位を高くすると、バルク領域8とゲート電圧との間の電位差が小さくなるから、しきい値電圧を下げることができる。そうすると、高速動作を実現することができる。

このように、本発明のフィン型電界効果トランジスタは、バルク領域8に印加する電位をバルク電極9によって自由に変えることができるから、欲する電気特性に応じたフィン型電界効果トランジスタを得ることができる。

また、バルク領域8に電圧を印加することで、しきい値電圧ばらつきを抑制することもできるので、信頼性が高いフィン型電界効果トランジスタを構成することもできる。

また、バルク領域8に電圧を印加することで、しきい値電圧ばらつきを抑制することもできるので、信頼性が高いフィン型電界効果トランジスタを構成することもできる。

[第1の実施形態の応用例の構成説明:図2]

次に、図2を用いて、第1実施形態のフィン型電界効果トランジスタの応用例を説明する。図2はフィン型電界効果トランジスタの応用例の構造を模式的に示す平面図及び断面図であって、図2(a)に平面図を、図2(b)にその切断線B−B´で切断した断面図を示す。

次に、図2を用いて、第1実施形態のフィン型電界効果トランジスタの応用例を説明する。図2はフィン型電界効果トランジスタの応用例の構造を模式的に示す平面図及び断面図であって、図2(a)に平面図を、図2(b)にその切断線B−B´で切断した断面図を示す。

この応用例の特徴は、2つのゲート電極を有する点である。

図2に示すように、第1の側端面3Aにゲート絶縁膜4a及びゲート電極6aを設けており、第1の側端面3Aと対向する第2の側端面3にゲート絶縁膜4b及びゲート電極6bを設けている構造である。

なお、ゲート絶縁膜4a,4b、ゲート電極6a,6bの材質や膜厚については、第2の実施形態と同様であるから説明は省略する。

図2に示すように、第1の側端面3Aにゲート絶縁膜4a及びゲート電極6aを設けており、第1の側端面3Aと対向する第2の側端面3にゲート絶縁膜4b及びゲート電極6bを設けている構造である。

なお、ゲート絶縁膜4a,4b、ゲート電極6a,6bの材質や膜厚については、第2の実施形態と同様であるから説明は省略する。

ソース領域7A及びドレイン領域7Bにも電気的な接続を行い、電気信号の授受を行う必要がある。これらの領域と平面的に重なる部分の層間絶縁膜10にコンタクトホール11を設け、金属配線にて電気的な接続を行う。なお、これらの構造についてはすでに説明したとおり、図面を見やすくするために図示を省略している。そのため、図2(a)ではソース領域7A上にバルク電極9が配線されているが、実際に構成する場合は、ソース電極とバルク電極9とが接触しないように離間して配置する。

[第1の実施形態の応用例の効果の説明]

この応用例は、2つのゲート電極6を有しており、各々独立してゲート電圧を印加できる。このような構造は、いわゆるダブルゲート型MOSFETとしてすでに知られている構成である。図2に示す第1の実施形態の応用例は、知られているダブルゲート型MOSFETの特徴に加え、バルク電極9によりバルク領域8に直接電位を印加できる点にある。

この応用例は、2つのゲート電極6を有しており、各々独立してゲート電圧を印加できる。このような構造は、いわゆるダブルゲート型MOSFETとしてすでに知られている構成である。図2に示す第1の実施形態の応用例は、知られているダブルゲート型MOSFETの特徴に加え、バルク電極9によりバルク領域8に直接電位を印加できる点にある。

このような構成であるから、バルク電位を0V付近に近づけたときのしきい値電圧のばらつきを抑制することができ、消費電力を削減することに加えて、スイッチング特性の向上と、短チャネルによるリーク電流をより抑えやすくすることが可能となる。

その理由は、ゲート電極の数が増加するため、ゲート電極が1つしかないMOSFETと比較して、ゲート電極でチャネル領域の電圧を制御しやすくなるからである。

例えば、バルク電極から電位を印加しバルク領域を0Vに保ったとき、電流が流れるチャネル部分では、ゲート電極から離れるにつれて電位が半導体層(バルク領域)の電位0Vに近づいてしまい、1つのゲート電極によるゲート電圧でチャネル領域の電圧変化の勾配をなだらかにするのは難しくなる。

これに対し、この応用例のような、チャネル領域の左右にゲート電極を設けたダブルゲート構造を有していると、対向するゲート電極が互いのチャネルを引き伸ばすため、双方のチャネル領域の電位はバルク領域に向かうに従って、よりなだらかに0Vへと変化する。

この結果、チャネル領域の電圧のばらつきは小さく抑えることができ、チャネル領域の電圧をゲート電極でより制御しやすくなるのである。

チャネル領域の電圧のばらつきが小さくなると、スイッチング特性を向上させることができ、さらにゲート長が短くてもリーク電流を抑えやすくなる。

また、ゲート電極数が増えると、同じ電位で駆動させた場合、駆動する際の電流量が増える(理想的にはゲート数倍に増加)ため、小さなMOSFETでも大きな電流駆動能力を得るようにすることもできるようになる。

[本発明の第2の実施形態の構成説明:図3]

次に、図3を用いて、フィン型電界効果トランジスタの第2実施形態を説明する。図3はフィン型電界効果トランジスタの構造を模式的に示す平面図及び断面図であって、図3(a)に平面図を、図3(b)にその切断線C−C´で切断した断面図を示す。

次に、図3を用いて、フィン型電界効果トランジスタの第2実施形態を説明する。図3はフィン型電界効果トランジスタの構造を模式的に示す平面図及び断面図であって、図3(a)に平面図を、図3(b)にその切断線C−C´で切断した断面図を示す。

第2の実施形態の特徴は、ゲート電極6とバルク電極9とを半導体層3を挟み対向して設ける点である。

図3に示すように、半導体層3の第1の垂直端面3Aにチャネル領域5を設け、これを覆うようにゲート絶縁膜4を設けている。ゲート電極6は、すでに説明した例と同様に、このゲート絶縁膜4を覆うように設けており、多くの部分が第1の垂直端面3Aに対向して設けている。

バルク電極9は、半導体層3の第2の垂直端面3Bのバルク領域8に直接接して設けている。

バルク電極9は、半導体層3の第2の垂直端面3Bのバルク領域8に直接接して設けている。

[第3の実施形態の効果の説明]

この第3の実施形態は、すでに説明した実施形態と同様の効果を有することに加え、バルク領域8とバルク電極9とを、より低抵抗で接続できるという効果がある。

すなわち、半導体層3上端面(図1でいうところの上端面3c)の狭い領域で、バルク領域8とバルク電極9とを接続するのではなく、より広い半導体層3の垂直端面3Bでバルク電極とバルク領域とが接続できる。

この第3の実施形態は、すでに説明した実施形態と同様の効果を有することに加え、バルク領域8とバルク電極9とを、より低抵抗で接続できるという効果がある。

すなわち、半導体層3上端面(図1でいうところの上端面3c)の狭い領域で、バルク領域8とバルク電極9とを接続するのではなく、より広い半導体層3の垂直端面3Bでバルク電極とバルク領域とが接続できる。

具体的には、半導体層3の半導体基板1側から起立した距離と、半導体層3の第2の垂直端面3Bにおけるバルク電極9の配線幅との分で、双方を接触できるから、より多くの接触面積で、バルク領域8とバルク電極9とを接触させることができる。これにより、より低抵抗で双方を電気的に接続できるという効果を有するのである。

また、半導体層3上端面にバルク電極9とバルク領域8とを接触させるように加工するよりも、加工が簡単に行える場合もあるので、プロセスコストを下げることができる場合もある。

[本発明の第3の実施形態の構成及び効果の説明:図4、図5]

次に、図4、図5を用いて、フィン型電界効果トランジスタの第3実施形態を説明する。図4はフィン型電界効果トランジスタの構造を模式的に示す平面図である。図5は図4に示す構成の断面図を示すものであって、図5(a)には図4に示す切断線D−D´で切断した様子を、図5(b)に図4に示す切断線E−E´で切断した断面図をそれぞれ示す。

次に、図4、図5を用いて、フィン型電界効果トランジスタの第3実施形態を説明する。図4はフィン型電界効果トランジスタの構造を模式的に示す平面図である。図5は図4に示す構成の断面図を示すものであって、図5(a)には図4に示す切断線D−D´で切断した様子を、図5(b)に図4に示す切断線E−E´で切断した断面図をそれぞれ示す。

第2の実施形態の特徴は、ゲート電極6とバルク電極9とを半導体層3を挟み対向して設ける点である。

図4に示すように、バルク領域8はすでに説明した例とは異なり、平面的にソース領域7Aの方向に屈曲している。

半導体層3の第1の垂直端面3Aにチャネル領域5、ゲート絶縁膜4、ゲート電極6を設ける構成はすでに説明した例と同じであるが、屈曲したバルク領域8により、バルク電極9とバルク領域8との接触部分は、ゲート電極6の延長線上にはなく、ソース領域7A方向にシフトしている。この様子は、2つの切断線で切断した様子を表した図5を見れば明らかであろう。

半導体層3の第1の垂直端面3Aにチャネル領域5、ゲート絶縁膜4、ゲート電極6を設ける構成はすでに説明した例と同じであるが、屈曲したバルク領域8により、バルク電極9とバルク領域8との接触部分は、ゲート電極6の延長線上にはなく、ソース領域7A方向にシフトしている。この様子は、2つの切断線で切断した様子を表した図5を見れば明らかであろう。

このような構成にすることで、ゲート電極6とバルク電極9との平面的な配置に自由度を向上させることができる。すでに説明したように、ソース領域7Aやドレイン領域7Bには、それぞれ図示はしないがソース電極とドレイン電極とが接続されている。このように配線が多く存在すると、この第3の実施形態のようにバルク電極9をシフトする構成であれば、配線の引き回しの自由度が増えるのである。

なお、この第3の実施形態でも、第2の実施形態と同様に、バルク領域8とバルク電極9とは、半導体層3の第2の垂直端面3Bにて接触しているから、双方の接触抵抗は低く、バルク領域8を屈曲させた構成でも、まったく影響はない。

[応用例の構成説明:図6]

次に、図6を用いて、すでに説明した実施形態の応用例を、第2の実施形態を例にして説明する。

この応用例は、フィン型電界効果トランジスタであるN型MOSFETとPチャネル型MOSFET(以後、P型MOSFETと記載する)とを並列に並べた構造(コンプリメンタリーMOS、所謂CMOS構造)としたものである。すでに説明した実施形態では、例えば、N型MOSFETを構成する例を説明したが、P型MOSFETと合わせたCMOS構造の例を説明する。

次に、図6を用いて、すでに説明した実施形態の応用例を、第2の実施形態を例にして説明する。

この応用例は、フィン型電界効果トランジスタであるN型MOSFETとPチャネル型MOSFET(以後、P型MOSFETと記載する)とを並列に並べた構造(コンプリメンタリーMOS、所謂CMOS構造)としたものである。すでに説明した実施形態では、例えば、N型MOSFETを構成する例を説明したが、P型MOSFETと合わせたCMOS構造の例を説明する。

図6において、13AはN型MOSFET、13BはP型MOSFET、14は素子間絶縁膜である。素子間絶縁膜14は、既知のCVD法により形成するシリコン酸化膜である。4a,4bはゲート絶縁膜、5a,5bはチャネル領域、6a,6bはゲート電極、8a,8bはバルク領域、12a,12bは金属配線、3Aa,3Abは第1の垂直端面、3Ba,3Bbは第2の垂直端面であり、それぞれ、すでに説明したゲート絶縁膜3、チャネル領域5、ゲート電極6、バルク電極8、金属電極12、第1の垂直端面3A、第2の垂直端面3Bに相当する。

図6に示すように、N型MOSFET13AとP型MOSFET13Bとを、それぞれの第2の垂直端面3Baと第2の垂直端面3Bbとを対向するように隣合わせて配置している。

N型MOSFET13Aのバルク領域8aの第1の垂直端面3Aaにチャネル領域5aを設け、これを覆うようにゲート絶縁膜4aを設けており、さらにゲート電極6aを設けている。

P型MOSFET13Bのバルク領域8bの第1の垂直端面3Abにチャネル領域5bを設け、これを覆うようにゲート絶縁膜4bを設けており、さらにゲート電極6bを設けている。

N型MOSFET13Aのバルク領域8aの第1の垂直端面3Aaにチャネル領域5aを設け、これを覆うようにゲート絶縁膜4aを設けており、さらにゲート電極6aを設けている。

P型MOSFET13Bのバルク領域8bの第1の垂直端面3Abにチャネル領域5bを設け、これを覆うようにゲート絶縁膜4bを設けており、さらにゲート電極6bを設けている。

第2の垂直端面3Baと第2の垂直端面3Bbとに直接接続する共通のバルク電極9を

備えている。このバルク電極9と、ゲート電極6a,6bに接続する金属配線12a,12bとは、この実施形態においても他の実施形態と同様に、同じ材料、同じプロセスで形成され、図示しない所定の回路素子や端子に接続している。

備えている。このバルク電極9と、ゲート電極6a,6bに接続する金属配線12a,12bとは、この実施形態においても他の実施形態と同様に、同じ材料、同じプロセスで形成され、図示しない所定の回路素子や端子に接続している。

素子間絶縁膜14は、N型MOSFET13AとP型MOSFET13Bとを絶縁する役割と、バルク電極9からの電界が半導体基板1側に余剰に及ばないようにする役割、またバルク電極を形成する際の被覆性を向上させる役割がある。このため、ある程度の膜厚が必要であって、印加するバルク電位でもよるが、例えば、0.5μm程度である。

[応用例の効果の説明]

N型MOSFET13AとP型MOSFET13Bとのゲート電極に、それぞれの導電型のMOSFETを駆動するための適正なゲート電圧を印加する。そして、バルク電極9には、所定の電圧を印加する。

例えば、バルク電極9には0.5Vを印加しておき、N型MOSFET13Aを駆動するタイミングでゲート電極6aには+0.8Vを印加する。次に、バルク電極9には−0.5Vを印加しておき、P型MOSFET13Bを駆動するタイミングでゲート電極6bには−0.8Vを印加する。

N型MOSFET13AとP型MOSFET13Bとのゲート電極に、それぞれの導電型のMOSFETを駆動するための適正なゲート電圧を印加する。そして、バルク電極9には、所定の電圧を印加する。

例えば、バルク電極9には0.5Vを印加しておき、N型MOSFET13Aを駆動するタイミングでゲート電極6aには+0.8Vを印加する。次に、バルク電極9には−0.5Vを印加しておき、P型MOSFET13Bを駆動するタイミングでゲート電極6bには−0.8Vを印加する。

そうすると、印加されているバルク電位によって、N型MOSFET13Aがオンするときは、P型MOSFET13Bがオンしにくくなり、逆にP型MOSFET13Bがオンするときは、N型MOSFET13Aがオンしにくくなる。

これは、半導体層に印加される電位の上下が、しきいち電圧を上下させるためである。

これは、半導体層に印加される電位の上下が、しきいち電圧を上下させるためである。

以上説明した本発明のフィン型電界効果トランジスタは、ゲート電極とは別にバルク領域に直接電位を印加するバルク電極を設けているため、しきい値電圧を任意の値に定めることができ、動作時には低いしきい値に、非動作時には高いしきい値に保つことができる。

このような特徴を有していれば、本発明の主旨を逸脱しない範囲で変形が可能である。例えば、半導体層の形状、ゲート電極とバルク電極との位置関係や電極の種類などは任意に定めることができる。

このような特徴を有していれば、本発明の主旨を逸脱しない範囲で変形が可能である。例えば、半導体層の形状、ゲート電極とバルク電極との位置関係や電極の種類などは任意に定めることができる。

本発明は、低しきい値電圧、しきい値電圧ばらつきとリーク電流の抑制、低面積を実施することができる。このため低電圧駆動するLSIに適用できる。特に低消費電力を必要とするLSIに好適である。

1 半導体基板

2 埋め込み絶縁膜

3 半導体層

3A 第1の垂直端面

3B 第2の垂直端面

3C 上端面

4 ゲート絶縁膜

5 チャネル領域

6 ゲート電極

7A ソース領域

7B ドレイン領域

8 バルク領域

9 バルク電極

10 層間絶縁膜

11 コンタクトホール

12 金属配線

13A N型MOSFET

13B P型MOSFET

14 素子間絶縁膜図1

2 埋め込み絶縁膜

3 半導体層

3A 第1の垂直端面

3B 第2の垂直端面

3C 上端面

4 ゲート絶縁膜

5 チャネル領域

6 ゲート電極

7A ソース領域

7B ドレイン領域

8 バルク領域

9 バルク電極

10 層間絶縁膜

11 コンタクトホール

12 金属配線

13A N型MOSFET

13B P型MOSFET

14 素子間絶縁膜図1

Claims (5)

- 半導体基板上に設ける絶縁膜と、

前記絶縁膜上に設ける半導体層と、を備え、

前記半導体層の所定の部分にバルク領域、ソース領域、チャネル領域、ドレイン領域を備え、

前記チャネル領域の前記半導体層表面にゲート絶縁膜を備え、

前記ゲート絶縁膜を介して前記チャネル領域に電界を印加するためのゲート電極を備えるフィン型電界効果トランジスタにおいて、

前記バルク領域に所定の電位を印加するためのバルク電極を、前記ゲート電極と別に備えることを特徴とするフィン型電界効果トランジスタ。 - 前記半導体層の第1の垂直端面に前記チャネル領域を設け、

前記半導体層の前記第1の垂直端面と対向する第2の垂直端面に前記バルク領域を設けることを特徴とする請求項1に記載のフィン型電界効果トランジスタ。 - 前記ゲート絶縁膜は、前記第1の垂直端面に設けることを特徴とする請求項2に記載のフィン型電界効果トランジスタ。

- 前記ゲート電極は、前記第1の垂直端面に対向して設け、

前記バルク電極は、前記第2の垂直端面に対向して設けると共に前記バルク領域に直接接続することを特徴とする請求項2又は3に記載のフィン型電界効果トランジスタ。 - 前記ゲート電極と前記バルク電極とを電気的に接続する接続配線を備えることを特徴とする請求項1から4のいずれか1つに記載のフィン型電界効果トランジスタ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011072295A JP2012209339A (ja) | 2011-03-29 | 2011-03-29 | フィン型電界効果トランジスタ |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011072295A JP2012209339A (ja) | 2011-03-29 | 2011-03-29 | フィン型電界効果トランジスタ |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2012209339A true JP2012209339A (ja) | 2012-10-25 |

Family

ID=47188862

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011072295A Withdrawn JP2012209339A (ja) | 2011-03-29 | 2011-03-29 | フィン型電界効果トランジスタ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2012209339A (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2017505530A (ja) * | 2013-11-27 | 2017-02-16 | クアルコム,インコーポレイテッド | デュアルモードトランジスタ |

| US12495608B2 (en) | 2021-12-14 | 2025-12-09 | United Semiconductor Japan Co., Ltd. | Semiconductor device and method of manufacturing semiconductor device |

-

2011

- 2011-03-29 JP JP2011072295A patent/JP2012209339A/ja not_active Withdrawn

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2017505530A (ja) * | 2013-11-27 | 2017-02-16 | クアルコム,インコーポレイテッド | デュアルモードトランジスタ |

| US12495608B2 (en) | 2021-12-14 | 2025-12-09 | United Semiconductor Japan Co., Ltd. | Semiconductor device and method of manufacturing semiconductor device |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10418480B2 (en) | Semiconductor device capable of high-voltage operation | |

| JP4664631B2 (ja) | 半導体装置及びその製造方法 | |

| TWI309080B (en) | Lateral double-diffused field effect transistor and integrated circuit having same | |

| US7935992B2 (en) | Transistor, display driver integrated circuit including a transistor, and a method of fabricating a transistor | |

| KR101355282B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| JP6316725B2 (ja) | 半導体装置 | |

| JP2010225768A (ja) | 半導体装置 | |

| US8106465B2 (en) | Semiconductor device | |

| WO2009101150A1 (en) | Transistor | |

| US20150295026A1 (en) | Semiconductor device and method for fabricating the same | |

| US20070241400A1 (en) | Semiconductor device | |

| JP4044446B2 (ja) | 半導体装置およびその製造方法 | |

| US10256340B2 (en) | High-voltage semiconductor device and method for manufacturing the same | |

| TWI723379B (zh) | 具有混合的摻雜區域的絕緣層上矽半導體裝置 | |

| US9324786B2 (en) | Semiconductor device and method for fabricating the same | |

| JP2012079992A (ja) | 半導体装置 | |

| JP2012209339A (ja) | フィン型電界効果トランジスタ | |

| TW200826230A (en) | Semiconductor device and method for manufacturing the same | |

| JP2007019200A (ja) | 半導体装置およびその製造方法 | |

| JP2008085117A (ja) | 半導体装置およびその製造方法 | |

| JP2005045080A (ja) | 半導体装置 | |

| JP5718103B2 (ja) | 半導体装置 | |

| JP4577948B2 (ja) | オフセットゲート型電界効果トランジスタ | |

| JP2006147829A (ja) | 半導体装置 | |

| JP2004095567A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A300 | Withdrawal of application because of no request for examination |

Free format text: JAPANESE INTERMEDIATE CODE: A300 Effective date: 20140603 |