JP2012164313A - インターフェースコネクタのデバイス、システムおよび方法 - Google Patents

インターフェースコネクタのデバイス、システムおよび方法 Download PDFInfo

- Publication number

- JP2012164313A JP2012164313A JP2012023564A JP2012023564A JP2012164313A JP 2012164313 A JP2012164313 A JP 2012164313A JP 2012023564 A JP2012023564 A JP 2012023564A JP 2012023564 A JP2012023564 A JP 2012023564A JP 2012164313 A JP2012164313 A JP 2012164313A

- Authority

- JP

- Japan

- Prior art keywords

- circuit board

- connectors

- connector

- interface connector

- electrical path

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01R—ELECTRICALLY-CONDUCTIVE CONNECTIONS; STRUCTURAL ASSOCIATIONS OF A PLURALITY OF MUTUALLY-INSULATED ELECTRICAL CONNECTING ELEMENTS; COUPLING DEVICES; CURRENT COLLECTORS

- H01R12/00—Structural associations of a plurality of mutually-insulated electrical connecting elements, specially adapted for printed circuits, e.g. printed circuit boards [PCB], flat or ribbon cables, or like generally planar structures, e.g. terminal strips, terminal blocks; Coupling devices specially adapted for printed circuits, flat or ribbon cables, or like generally planar structures; Terminals specially adapted for contact with, or insertion into, printed circuits, flat or ribbon cables, or like generally planar structures

- H01R12/50—Fixed connections

- H01R12/51—Fixed connections for rigid printed circuits or like structures

- H01R12/52—Fixed connections for rigid printed circuits or like structures connecting to other rigid printed circuits or like structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01R—ELECTRICALLY-CONDUCTIVE CONNECTIONS; STRUCTURAL ASSOCIATIONS OF A PLURALITY OF MUTUALLY-INSULATED ELECTRICAL CONNECTING ELEMENTS; COUPLING DEVICES; CURRENT COLLECTORS

- H01R12/00—Structural associations of a plurality of mutually-insulated electrical connecting elements, specially adapted for printed circuits, e.g. printed circuit boards [PCB], flat or ribbon cables, or like generally planar structures, e.g. terminal strips, terminal blocks; Coupling devices specially adapted for printed circuits, flat or ribbon cables, or like generally planar structures; Terminals specially adapted for contact with, or insertion into, printed circuits, flat or ribbon cables, or like generally planar structures

- H01R12/70—Coupling devices

- H01R12/71—Coupling devices for rigid printing circuits or like structures

- H01R12/72—Coupling devices for rigid printing circuits or like structures coupling with the edge of the rigid printed circuits or like structures

- H01R12/73—Coupling devices for rigid printing circuits or like structures coupling with the edge of the rigid printed circuits or like structures connecting to other rigid printed circuits or like structures

Abstract

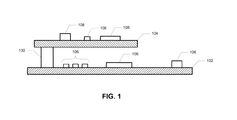

【解決手段】インターフェースコネクタ100を用いて第1の回路基板102および第2の回路基板104を接続するデバイス、方法およびシステムである。ある態様では、ケーシング内で互いに絶縁されている複数の導電性コネクタとを含む、インターフェースコネクタ100が説明される。各コネクタは、第1の端部および第2の端部を有し、第1の端部は第1の回路基板102に接続し、第2の端部は第2の回路基板104に接続する。複数のコネクタは、インターフェースコネクタ100の第1の列および第2の列を形成する。第1の列は偶数番号のコネクタを含み、第2の列は奇数番号のコネクタを含む。

【選択図】図1

Description

102 第1の回路基板

104 第2の回路基板

106 第1の回路基板102上の電子部品

108 第2の回路基板上の電子部品108

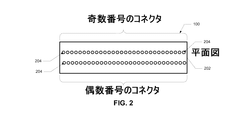

202 ケーシング

204 複数の導電性コネクタ

302 (導電性コネクタ204の)第1の端部

304 (導電性コネクタ204の)第2の端部

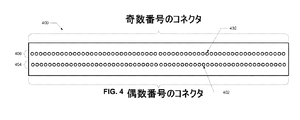

400 インターフェースコネクタ

402 コネクタ

404 インターフェースコネクタの1つの列(偶数番号)

406 インターフェースコネクタの別の列(奇数番号)

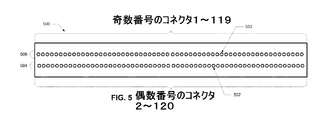

500 インターフェースコネクタ

502 コネクタ

504 インターフェースコネクタ500の1つの列504内のコネクタ502は偶数番号である(2〜120の番号を付けられる)

506 別の列506のコネクタ502は全て奇数番号である(1〜119の番号を付けられる)

Claims (10)

- 2つの回路基板を接続するためのインターフェースコネクタであって、

ケーシング(202)と、

前記ケーシング(202)内で互いに絶縁され、各コネクタ(204)が第1の端部(302)および第2の端部(304)を有する導電性コネクタ(204)とを含み、前記第1の端部(302)が第1の回路基板(102)に接続し、前記第2の端部(304)が第2の回路基板(104)に接続し、前記複数のコネクタ(204)が第1の列(404)および第2の列(406)を形成し、前期第1の列(404)が偶数番号のコネクタ(204)を含み、前記第2の列(406)が奇数番号のコネクタ(204)を含み、前記複数のコネクタ(204)が、

コネクタ1〜4、13〜18、43〜61、68〜71、77、78、79、80、84、86、92および94〜120が、前記第1の回路基板(102)と前記第2の回路基板(104)との間の一般的な回路の接続のための電気的な経路を提供し、

コネクタ41、42、62〜67、72〜75および81が、前記第1の回路基板(102)と前記第2の回路基板(104)との間のホストプロセッサの接続のための電気的な経路を提供し、

コネクタ5〜12、19〜40、76、82、83、85、87〜91および93が、前記第1の回路基板(102)と前記第2の回路基板(104)との間のフィールドプログラマブルゲートアレイ(FPGA)の接続のための電気的な経路を提供する

ように割り当てられる、インターフェースコネクタ。 - コネクタ59、61、79、18、60、80、110、69、71、68、70、77および78が、前記第1の回路基板(102)または前記第2の回路基板(104)の上の電子部品のための電源の接続であり、

コネクタ1〜4が、前記第1の回路基板(102)と前記第2の回路基板(104)との間の複数のkeyphasor(登録商標)信号のための電気的な経路を提供し、

コネクタ63が、前記第1の回路基板(102)と前記第2の回路基板(104)との間のクロック信号のための電気的な経路を提供し、

コネクタ48および56が、前記第1の回路基板(102)と前記第2の回路基板(104)との間のトリップ乗算信号のための電気的な経路を提供し、

コネクタ24〜39が、前記第1の回路基板(102)と前記第2の回路基板(104)との間の管理データバス信号のための電気的な経路を提供する、請求項1記載のインターフェースコネクタ。 - 前記複数のコネクタ(204)の各々の前記第1の端部(302)が、前記第1の回路基板(102)に接続するためのメス型の端部を含み、前記複数のコネクタ(204)の各々の前記第2の端部(304)が、前記第2の回路基板(104)に接続するためのオス型の端部を含む、請求項1記載のインターフェースコネクタ。

- 前記複数のコネクタ(204)の各々の前記第1の端部(302)が、前記第1の回路基板(102)に接続するためのオス型の端部を含み、前記複数のコネクタ(204)の各々の前記第2の端部(304)が、前記第2の回路基板(104)に接続するためのメス型の端部を含む、請求項1記載のインターフェースコネクタ。

- 前記第1の回路基板(102)が、Bently Nevada機械監視システムのための回路基板であり、前記インターフェースコネクタが、前記第2の回路基板(104)を、Bently Nevada機械監視システムのための前記回路基板に電気的に接続するために使用される、請求項1記載のインターフェースコネクタ。

- 2つの回路基板を接続するための方法であって、

インターフェースコネクタ(100)を設けるステップであって、前記インターフェースコネクタ(100)が、ケーシング(202)と、前記ケーシング(202)内で互いに絶縁され、各コネクタ(204)が第1の端部(302)および第2の端部(304)を有する導電性コネクタ(204)とを含み、前記第1の端部(302)が第1の回路基板(102)に接続し、前記第2の端部(304)が第2の回路基板(104)に接続し、前記複数のコネクタ(204)が第1の列(404)および第2の列(406)を形成し、前期第1の列(404)が偶数番号のコネクタ(204)を含み、前記第2の列(406)が奇数番号のコネクタ(204)を含み、前記複数の導電性コネクタ(204)が、少なくとも120個のコネクタを含む、ステップと、

前記複数のコネクタ(204)が、

コネクタ1〜4、13〜18、43〜61、68〜71、77、78、79、80、84、86、92および94〜120が、前記第1の回路基板(102)と前記第2の回路基板(104)との間の一般的な回路の接続のための電気的な経路を提供し、

コネクタ41、42、62〜67、72〜75および81が、前記第1の回路基板(102)と前記第2の回路基板(104)との間のホストプロセッサの接続のための電気的な経路を提供し、

コネクタ5〜12、19〜40、76、82、83、85、87〜91および93が、前記第1の回路基板(102)と前記第2の回路基板(104)との間のフィールドプログラマブルゲートアレイ(FPGA)の接続のための電気的な経路を提供する

ように割り当てられるように、前記インターフェースコネクタ(100)を構成するステップと、

前記構成されたインターフェースコネクタ(100)を用いて、前記第1の回路基板(102)および前記第2の回路基板(104)を接続するステップと

を含む、方法。 - コネクタ1〜4、13〜18、43〜61、68〜71、77、78、79、80、84、86、92および94〜120が、前記第1の回路基板(102)と前記第2の回路基板(104)との間の一般的な回路の接続のための電気的な経路を提供するように、前記インターフェースコネクタ(100)を構成するステップが、コネクタ59、61、79、18、60、80、110、69、71、68、70、77および78を、前記第1の回路基板(102)または前記第2の回路基板(104)の上の電子部品のための電源の接続として構成するステップと、前記第1の回路基板と前記第2の回路基板との間の複数のkeyphasor(登録商標)信号のための電気的な経路を提供するように、コネクタ1〜4を構成するステップと、前記第1の回路基板と前記第2の回路基板との間のトリップ乗算信号のための電気的な経路として、コネクタ48および56を構成するステップとを含み、

前記第1の回路基板(102)または前記第2の回路基板(104)の上の電子部品が、ホストプロセッサおよびFPGAを含み、

コネクタ41、42、62〜67、72〜75および81が、前記第1の回路基板と前記第2の回路基板との間のホストプロセッサの接続のための電気的な経路を提供するように、前記インターフェースコネクタを構成するステップが、前記第1の回路基板と前記第2の回路基板との間のクロック信号のための電気的な経路を提供するようにコネクタ63を構成するステップを含み、

コネクタ5〜12、19〜40、76、82、83、85、87〜91および93が、前記第1の回路基板と前記第2の回路基板との間のフィールドプログラマブルゲートアレイ(FPGA)の接続のための電気的な経路を提供するように、前記インターフェースコネクタを構成するステップが、前記第1の回路基板と前記第2の回路基板との間の管理データバス信号のための電気的な経路として、コネクタ24〜39を構成するステップを含む、請求項6記載の方法。 - 前記構成されたインターフェースコネクタ(100)を用いて前記第1の回路基板(102)および前記第2の回路基板(104)を接続するステップが、前記第2の回路基板(104)を、Bently Nevada機械監視システムのための回路基板に電気的に接続するステップを含む、請求項6記載の方法。

- インターフェースコネクタ(100)と、

第1の回路基板(102)と、

第2の回路基板(104)と

を含むシステムであって、前記インターフェースコネクタ(100)が、前記第1の回路基板(102)を前記第2の回路基板(104)に接続するのに使用され、前記インターフェースコネクタ(100)が、

ケーシング(202)と、

前記ケーシング(202)内で互いに絶縁され、各コネクタ(204)が第1の端部(302)および第2の端部(304)を有する少なくとも120個の導電性コネクタ(204)とを含み、前記第1の端部(302)が前記第1の回路基板(102)に接続し、前記第2の端部(304)が前記第2の回路基板(104)に接続し、前記複数のコネクタ(204)が第1の列(404)および第2の列(406)を形成し、前期第1の列(404)が偶数番号のコネクタ(204)を含み、前記第2の列(406)が奇数番号のコネクタ(204)を含み、前記複数のコネクタ(204)が、

コネクタ1〜4、13〜18、43〜61、68〜71、77、78、79、80、84、86、92および94〜120が、前記第1の回路基板(102)と前記第2の回路基板(104)との間の一般的な回路の接続のための電気的な経路を提供し、コネクタ59、61、79、18、60、80、110、69、71、68、70、77および78が、前記第1の回路基板(102)または前記第2の回路基板(104)の上の電子部品のための電源の接続であり、コネクタ1〜4が、前記第1の回路基板(102)と前記第2の回路基板(104)との間の複数のkeyphasor(登録商標)信号のための電気的な経路を提供し、コネクタ48および56が、前記第1の回路基板(102)と前記第2の回路基板(104)との間のトリップ乗算信号のための電気的な経路を提供し、

コネクタ41、42、62〜67、72〜75および81が、前記第1の回路基板(102)と前記第2の回路基板(104)との間のホストプロセッサの接続のための電気的な経路を提供し、コネクタ63が、前記第1の回路基板(102)と前記第2の回路基板(104)との間のクロック信号のための電気的な経路を提供し、

コネクタ5〜12、19〜40、76、82、83、85、87〜91および93が、前記第1の回路基板(102)と前記第2の回路基板(104)との間のフィールドプログラマブルゲートアレイ(FPGA)の接続のための電気的な経路を提供し、コネクタ24〜39が、前記第1の回路基板(102)と前記第2の回路基板(104)との間の管理データバス信号のための電気的な経路を提供する

ように構成される、システム。 - 前記第1の回路基板(102)が、Bently Nevada機械監視システムのための回路基板であり、前記インターフェースコネクタ(100)が、前記第2の回路基板(104)を、Bently Nevada機械監視システムのための前記回路基板に電気的に接続するために使用される、請求項9記載のシステム。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US13/022,808 US8287290B2 (en) | 2011-02-08 | 2011-02-08 | Device, system and method of an interface connector |

| US13/022,808 | 2011-02-08 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2012164313A true JP2012164313A (ja) | 2012-08-30 |

| JP2012164313A5 JP2012164313A5 (ja) | 2012-11-22 |

Family

ID=46547172

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012023564A Pending JP2012164313A (ja) | 2011-02-08 | 2012-02-07 | インターフェースコネクタのデバイス、システムおよび方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US8287290B2 (ja) |

| JP (1) | JP2012164313A (ja) |

| CN (1) | CN102683930A (ja) |

| DE (1) | DE102012100954A1 (ja) |

| DK (1) | DK177849B1 (ja) |

| IN (1) | IN2012DE00268A (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104347973B (zh) | 2013-08-01 | 2016-09-28 | 富士康(昆山)电脑接插件有限公司 | 连接器组件 |

| US10001459B2 (en) | 2015-02-27 | 2018-06-19 | General Electric Company | System and method for phased array edge card |

| US10028402B1 (en) * | 2017-03-22 | 2018-07-17 | Seagate Technology Llc | Planar expansion card assembly |

| TWI721791B (zh) * | 2020-02-21 | 2021-03-11 | 緯穎科技服務股份有限公司 | 電子裝置 |

Citations (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5621389U (ja) * | 1979-07-27 | 1981-02-25 | ||

| JPH0221305A (ja) * | 1988-07-08 | 1990-01-24 | Omron Tateisi Electron Co | 制御用電子機器 |

| JPH0324279U (ja) * | 1989-07-18 | 1991-03-13 | ||

| JPH0566707U (ja) * | 1992-02-17 | 1993-09-03 | 株式会社キーエンス | 入出力制御装置 |

| JPH06349554A (ja) * | 1993-06-02 | 1994-12-22 | Japan Aviation Electron Ind Ltd | 平行基板用コネクタ及び基板 |

| JPH09146625A (ja) * | 1995-11-24 | 1997-06-06 | Advantest Corp | 調整用ボード対応のタイミング調整装置 |

| JPH09179606A (ja) * | 1995-12-22 | 1997-07-11 | Toei Denki Kk | サーボ制御装置 |

| JP2002135218A (ja) * | 2000-10-25 | 2002-05-10 | Kawamura Electric Inc | ネットワーク環境監視装置 |

| JP2002533047A (ja) * | 1998-12-17 | 2002-10-02 | エス・ピー・ディ、テクノロジーズ、インコーポレーテッド | 電力ノード制御センター |

| JP2005512219A (ja) * | 2001-12-06 | 2005-04-28 | フィッシャー−ローズマウント システムズ, インコーポレイテッド | 固有安全性を備えた現場保守ツール |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5313614A (en) | 1988-12-06 | 1994-05-17 | At&T Bell Laboratories | Method and apparatus for direct conversion of programs in object code form between different hardware architecture computer systems |

| US5539787A (en) | 1992-07-06 | 1996-07-23 | Sharp Kabushiki Kaisha | Converter for connecting modem equipment of dissimilar interface protocol |

| JP3670303B2 (ja) | 1993-09-01 | 2005-07-13 | 富士通株式会社 | データ変換方法及びデータ変換装置 |

| US5732273A (en) | 1995-08-11 | 1998-03-24 | Digital Equipment Corporation | System for monitoring compute system performance |

| US5581558A (en) | 1995-03-29 | 1996-12-03 | Lucent Technologies Inc. | Apparatus for bridging non-compatible network architectures |

| JP3904645B2 (ja) | 1996-12-26 | 2007-04-11 | 株式会社東芝 | ハードウェア/ソフトウェア協調シミュレーション装置 |

| US6151390A (en) | 1997-07-31 | 2000-11-21 | Cisco Technology, Inc. | Protocol conversion using channel associated signaling |

| US6237053B1 (en) | 1998-06-30 | 2001-05-22 | Symbol Technologies, Inc. | Configurable operating system having multiple data conversion applications for I/O connectivity |

| US6493594B1 (en) | 1999-06-04 | 2002-12-10 | Lucent Technologies Inc. | System and method for improved software configuration and control management in multi-module systems |

| US7188171B2 (en) | 2003-01-23 | 2007-03-06 | Hewlett-Packard Development Company, L.P. | Method and apparatus for software and hardware event monitoring and repair |

| TWI282645B (en) * | 2004-04-16 | 2007-06-11 | Hon Hai Prec Ind Co Ltd | Electrical contact |

| CN200941464Y (zh) * | 2006-06-23 | 2007-08-29 | 富士康(昆山)电脑接插件有限公司 | 电连接器 |

| US7341485B2 (en) * | 2006-07-24 | 2008-03-11 | Hon Hai Precision Ind. Co., Ltd. | Land grid array socket |

| US7692281B2 (en) * | 2007-02-16 | 2010-04-06 | Tyco Electronics Corporation | Land grid array module with contact locating features |

| TWM351483U (en) * | 2008-08-04 | 2009-02-21 | Hon Hai Prec Ind Co Ltd | Electrical connector |

-

2011

- 2011-02-08 US US13/022,808 patent/US8287290B2/en active Active

-

2012

- 2012-01-31 IN IN268DE2012 patent/IN2012DE00268A/en unknown

- 2012-02-03 DK DK201270054A patent/DK177849B1/en active

- 2012-02-06 DE DE102012100954A patent/DE102012100954A1/de active Pending

- 2012-02-07 JP JP2012023564A patent/JP2012164313A/ja active Pending

- 2012-02-08 CN CN2012100346532A patent/CN102683930A/zh active Pending

Patent Citations (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5621389U (ja) * | 1979-07-27 | 1981-02-25 | ||

| JPH0221305A (ja) * | 1988-07-08 | 1990-01-24 | Omron Tateisi Electron Co | 制御用電子機器 |

| JPH0324279U (ja) * | 1989-07-18 | 1991-03-13 | ||

| JPH0566707U (ja) * | 1992-02-17 | 1993-09-03 | 株式会社キーエンス | 入出力制御装置 |

| JPH06349554A (ja) * | 1993-06-02 | 1994-12-22 | Japan Aviation Electron Ind Ltd | 平行基板用コネクタ及び基板 |

| JPH09146625A (ja) * | 1995-11-24 | 1997-06-06 | Advantest Corp | 調整用ボード対応のタイミング調整装置 |

| JPH09179606A (ja) * | 1995-12-22 | 1997-07-11 | Toei Denki Kk | サーボ制御装置 |

| JP2002533047A (ja) * | 1998-12-17 | 2002-10-02 | エス・ピー・ディ、テクノロジーズ、インコーポレーテッド | 電力ノード制御センター |

| JP2002135218A (ja) * | 2000-10-25 | 2002-05-10 | Kawamura Electric Inc | ネットワーク環境監視装置 |

| JP2005512219A (ja) * | 2001-12-06 | 2005-04-28 | フィッシャー−ローズマウント システムズ, インコーポレイテッド | 固有安全性を備えた現場保守ツール |

Also Published As

| Publication number | Publication date |

|---|---|

| CN102683930A (zh) | 2012-09-19 |

| US20120202362A1 (en) | 2012-08-09 |

| DE102012100954A1 (de) | 2012-08-09 |

| US8287290B2 (en) | 2012-10-16 |

| DK201270054A (en) | 2012-08-09 |

| IN2012DE00268A (ja) | 2015-07-10 |

| DK177849B1 (en) | 2014-09-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN107444481A (zh) | 旋转检测设备和使用其的电动助力转向设备 | |

| JP2012164313A (ja) | インターフェースコネクタのデバイス、システムおよび方法 | |

| US20040158627A1 (en) | Computer condition detection system | |

| TW201714432A (zh) | 管理方法、服務控制器裝置以及非暫態電腦可讀取媒體 | |

| CN103250107A (zh) | 用于设备故障检测的智能检测系统及检测方法 | |

| CN109522175B (zh) | 一种内存评估的方法及装置 | |

| US20150058482A1 (en) | System insight display | |

| JP5441875B2 (ja) | 計算機システム | |

| TW201621657A (zh) | 電子裝置 | |

| CN108955951A (zh) | 一种温度传感器故障判断方法及装置 | |

| EP2787630B1 (en) | Detecting faults in motors and drives | |

| JP6033913B2 (ja) | ユニバーサルテストプラットフォーム及びそのテスト方法 | |

| JP6069406B2 (ja) | 放熱システム、制御方法、コンピュータ・プログラムおよび情報処理装置 | |

| CN112015689A (zh) | 串口输出路径切换方法、系统及装置和交换机 | |

| EP3068052A1 (en) | Industrial control system with integrated circuit elements partitioned for functional safety and employing watchdog timing circuits | |

| CN113656339A (zh) | Nvme热插拔的处理方法、bmc、装置、设备及介质 | |

| CN106446311B (zh) | Cpu告警电路及告警方法 | |

| CN110083532B (zh) | 基于深度学习框架的融合模式下运行错误定位方法及装置 | |

| JP2012164313A5 (ja) | ||

| US20200110678A1 (en) | Monitoring system and method | |

| US20150365269A1 (en) | Usage of mapping jumper pins or dip switch setting to define node's ip address to identify node's location | |

| US20140281094A1 (en) | External access of internal sas topology in storage server | |

| TWI718807B (zh) | 具振動感測功能的伺服器 | |

| KR101028885B1 (ko) | 계장(계측) 제어장치 | |

| CN102478861B (zh) | 一种用于存储器的风扇控制系统 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121009 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20121009 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20121009 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20121030 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121106 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130131 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130402 |