JP2012109889A - 送信装置、送信方法、受信装置、受信方法、プログラム、および伝送システム - Google Patents

送信装置、送信方法、受信装置、受信方法、プログラム、および伝送システム Download PDFInfo

- Publication number

- JP2012109889A JP2012109889A JP2010258569A JP2010258569A JP2012109889A JP 2012109889 A JP2012109889 A JP 2012109889A JP 2010258569 A JP2010258569 A JP 2010258569A JP 2010258569 A JP2010258569 A JP 2010258569A JP 2012109889 A JP2012109889 A JP 2012109889A

- Authority

- JP

- Japan

- Prior art keywords

- data

- error correction

- correction code

- transmission

- data length

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/0001—Systems modifying transmission characteristics according to link quality, e.g. power backoff

- H04L1/0009—Systems modifying transmission characteristics according to link quality, e.g. power backoff by adapting the channel coding

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/0001—Systems modifying transmission characteristics according to link quality, e.g. power backoff

- H04L1/0023—Systems modifying transmission characteristics according to link quality, e.g. power backoff characterised by the signalling

- H04L1/0025—Transmission of mode-switching indication

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0056—Systems characterized by the type of code used

- H04L1/0071—Use of interleaving

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/12—Arrangements for detecting or preventing errors in the information received by using return channel

- H04L1/16—Arrangements for detecting or preventing errors in the information received by using return channel in which the return channel carries supervisory signals, e.g. repetition request signals

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L2001/0092—Error control systems characterised by the topology of the transmission link

- H04L2001/0094—Bus

Abstract

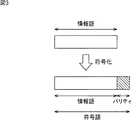

【解決手段】送信側ブロック11と受信側ブロック12は、デジタルカメラ、携帯電話機、パーソナルコンピュータなどの同じ装置内に設けられるブロックであり、1本の伝送路を介して接続される。データの送信時、送信側ブロック11においては、送信対象のデータに基づいて誤り訂正符号の計算が行われ、送信データに付加されることによって誤り訂正符号化が行われる。誤り訂正符号が付加された送信データを受信した受信側ブロック12においては、伝送路上において生じた送信データの誤りが、送信データに付加されている誤り訂正符号を用いて訂正される。本発明は、複数のLSI間でデータの送受信を行う装置に適用することができる。

【選択図】図1

Description

[ブロックの構成]

図1は、本発明の一実施形態に係る伝送システムの第1の構成例を示す図である。

ここで、図1の構成を有する送信側ブロック11と受信側ブロック12の一連の処理について説明する。はじめに、図6のフローチャートを参照して送信側ブロック11の送信処理について説明する。

図9は、伝送システム1の第2の構成例を示す図である。

図10は、伝送システム1の第3の構成例を示す図である。

図11は、伝送システム1の第4の構成例を示す図である。

図12は、伝送システム1の第5の構成例を示す図である。

上述した一連の処理は、ハードウェアにより実行することもできるし、ソフトウェアにより実行することもできる。一連の処理をソフトウェアにより実行する場合には、そのソフトウェアを構成するプログラムが、専用のハードウェアに組み込まれているコンピュータ、または汎用のパーソナルコンピュータなどに、プログラム記録媒体からインストールされる。

Claims (15)

- データ長が可変である誤り訂正符号のデータ長を設定する設定手段と、

送信対象のデータを情報語として、前記設定手段により設定されたデータ長の前記誤り訂正符号を計算する誤り訂正符号計算手段と、

前記誤り訂正符号計算手段による計算によって求められた前記誤り訂正符号を前記送信対象のデータに付加して得られた符号語のデータである符号化データを、同じ装置内にある受信装置に送信する送信手段と

を備える送信装置。 - 前記設定手段は、前記送信装置を構成する回路の入力端子に外部から入力された信号に従って前記誤り訂正符号のデータ長を設定する

請求項1に記載の送信装置。 - 前記設定手段は、外部との通信用のバスを介して外部から入力された信号に従って前記誤り訂正符号のデータ長を設定する

請求項1に記載の送信装置。 - 前記設定手段はプロセッサであり、所定のプログラムに従って前記誤り訂正符号のデータ長を設定する

請求項1に記載の送信装置。 - 前記設定手段はプロセッサであり、前記受信装置のプロセッサから送信されてきた情報に基づいて、前記送信対象のデータの誤り訂正の状況に基づいて前記受信装置のプロセッサにより決定された前記誤り訂正符号のデータ長を設定する

請求項1に記載の送信装置。 - データ長が可変である誤り訂正符号のデータ長を設定し、

送信対象のデータを情報語として、設定したデータ長の前記誤り訂正符号を計算し、

計算によって求めた前記誤り訂正符号を前記送信対象のデータに付加して得られた符号語のデータである符号化データを、同じ装置内にある受信装置に送信する

ステップを含む送信方法。 - データ長が可変である誤り訂正符号のデータ長を設定し、

送信対象のデータを情報語として、設定したデータ長の前記誤り訂正符号を計算し、

計算によって求めた前記誤り訂正符号を前記送信対象のデータに付加して得られた符号語のデータである符号化データを、同じ装置内にある受信装置に送信する

ステップを含む処理をコンピュータに実行させるプログラム。 - データ長が可変である誤り訂正符号のデータ長を設定し、送信対象のデータを情報語として、設定したデータ長の前記誤り訂正符号を計算し、計算によって求めた前記誤り訂正符号を前記送信対象のデータに付加して得られた符号語のデータである符号化データを送信する同じ装置内に設けられる送信装置から送信された前記符号化データを受信する受信手段と、

前記誤り訂正符号のデータ長を設定する設定手段と、

前記符号化データに含まれる、前記設定手段により設定されたデータ長の前記誤り訂正符号に基づいて前記送信対象のデータの誤り訂正を行う誤り訂正手段と、

前記誤り訂正後の前記送信対象のデータの処理を行う処理手段と

を備える受信装置。 - 前記設定手段は、前記受信装置を構成する回路の入力端子に外部から入力された信号に従って前記誤り訂正符号のデータ長を設定する

請求項8に記載の受信装置。 - 前記設定手段は、外部との通信用のバスを介して外部から入力された信号に従って前記誤り訂正符号のデータ長を設定する

請求項8に記載の受信装置。 - 前記設定手段はプロセッサであり、所定のプログラムに従って前記誤り訂正符号のデータ長を設定する

請求項8に記載の受信装置。 - 前記設定手段はプロセッサであり、前記誤り訂正手段による前記誤り訂正の状況に基づいて前記誤り訂正符号のデータ長を決定し、決定したデータ長を表す情報を、前記送信装置において前記誤り訂正符号のデータ長を設定する、前記送信装置のプロセッサに送信する

請求項8に記載の受信装置。 - データ長が可変である誤り訂正符号のデータ長を設定し、送信対象のデータを情報語として、設定したデータ長の前記誤り訂正符号を計算し、計算によって求めた前記誤り訂正符号を前記送信対象のデータに付加して得られた符号語のデータである符号化データを送信する同じ装置内に設けられる送信装置から送信された前記符号化データを受信し、

前記誤り訂正符号のデータ長を設定し、

前記符号化データに含まれる、設定したデータ長の前記誤り訂正符号に基づいて前記送信対象のデータの誤り訂正を行い、

前記誤り訂正後の前記送信対象のデータの処理を行う

ステップを含む受信方法。 - データ長が可変である誤り訂正符号のデータ長を設定し、送信対象のデータを情報語として、設定したデータ長の前記誤り訂正符号を計算し、計算によって求めた前記誤り訂正符号を前記送信対象のデータに付加して得られた符号語のデータである符号化データを送信する同じ装置内に設けられる送信装置から送信された前記符号化データを受信し、

前記誤り訂正符号のデータ長を設定し、

前記符号化データに含まれる、設定したデータ長の前記誤り訂正符号に基づいて前記送信対象のデータの誤り訂正を行い、

前記誤り訂正後の前記送信対象のデータの処理を行う

ステップを含む処理をコンピュータに実行させるプログラム。 - 送信装置と受信装置とを含む伝送システムにおいて、

前記送信装置は、

データ長が可変である誤り訂正符号のデータ長を設定する設定手段と、

送信対象のデータを情報語として、前記設定手段により設定されたデータ長の前記誤り訂正符号を計算する誤り訂正符号計算手段と、

前記誤り訂正符号計算手段による計算によって求められた前記誤り訂正符号を前記送信対象のデータに付加して得られた符号語のデータである符号化データを前記受信装置に送信する送信手段と

を備え、

前記受信装置は、

前記符号化データを受信する受信手段と、

前記誤り訂正符号のデータ長を設定する設定手段と、

前記符号化データに含まれる、前記設定手段により設定されたデータ長の前記誤り訂正符号に基づいて前記送信対象のデータの誤り訂正を行う誤り訂正手段と、

前記誤り訂正後の前記送信対象のデータの処理を行う処理手段と

を備える

伝送システム。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010258569A JP2012109889A (ja) | 2010-11-19 | 2010-11-19 | 送信装置、送信方法、受信装置、受信方法、プログラム、および伝送システム |

| US13/247,161 US20120131422A1 (en) | 2010-11-19 | 2011-09-28 | Transmitting device, transmitting method, receiving device, receiving method, program, and transmission system |

| EP11187646.2A EP2456113A3 (en) | 2010-11-19 | 2011-11-03 | Error correction methods and apparatus |

| CN2011204514684U CN202663412U (zh) | 2010-11-19 | 2011-11-15 | 发送设备、接收设备、以及传输系统 |

| CN2011103612805A CN102480341A (zh) | 2010-11-19 | 2011-11-15 | 发送设备及方法、接收设备及方法、程序、以及传输系统 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010258569A JP2012109889A (ja) | 2010-11-19 | 2010-11-19 | 送信装置、送信方法、受信装置、受信方法、プログラム、および伝送システム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2012109889A true JP2012109889A (ja) | 2012-06-07 |

| JP2012109889A5 JP2012109889A5 (ja) | 2013-12-19 |

Family

ID=44992613

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010258569A Pending JP2012109889A (ja) | 2010-11-19 | 2010-11-19 | 送信装置、送信方法、受信装置、受信方法、プログラム、および伝送システム |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US20120131422A1 (ja) |

| EP (1) | EP2456113A3 (ja) |

| JP (1) | JP2012109889A (ja) |

| CN (2) | CN102480341A (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012109889A (ja) * | 2010-11-19 | 2012-06-07 | Sony Corp | 送信装置、送信方法、受信装置、受信方法、プログラム、および伝送システム |

| US8689049B2 (en) * | 2011-11-03 | 2014-04-01 | Hewlett-Packard Development Company, L.P. | Corrective actions based on probabilities |

| JP2013187606A (ja) | 2012-03-06 | 2013-09-19 | Sony Corp | 撮像装置および画像伝送方法 |

| US9009562B2 (en) | 2013-01-30 | 2015-04-14 | Hewlett-Packard Development Company, L.P. | Providing memory protection using a modified error correction code |

| US9960981B2 (en) * | 2015-10-08 | 2018-05-01 | Sony Corporation | Communication device, communication method, program, and communication system |

| US10366315B1 (en) * | 2018-08-15 | 2019-07-30 | Fmr Llc | Generating a quick response (QR) grid associated with a digital document |

| WO2023080813A1 (en) * | 2021-11-03 | 2023-05-11 | Telefonaktiebolaget Lm Ericsson (Publ) | Congestion level control for data transmission in a neural network |

| CN114167741A (zh) * | 2021-11-29 | 2022-03-11 | 珠海格力电器股份有限公司 | 控制指令的传输方法、装置及存储介质 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05304515A (ja) * | 1992-04-24 | 1993-11-16 | Rohm Co Ltd | デジタルデータ伝送方式 |

| JPH06165143A (ja) * | 1992-11-26 | 1994-06-10 | Sony Corp | 高能率符号化装置および復号化装置 |

| JP2010219869A (ja) * | 2009-03-17 | 2010-09-30 | Sony Corp | 通信装置及び通信方法、コンピューター・プログラム、並びに通信システム |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5636316A (en) * | 1990-12-05 | 1997-06-03 | Hitachi, Ltd. | Picture signal digital processing unit |

| US5907563A (en) * | 1996-03-07 | 1999-05-25 | Kokusai Denshin Denwa Co. Ltd. | Error control method and apparatus for wireless data communication |

| US6477669B1 (en) * | 1997-07-15 | 2002-11-05 | Comsat Corporation | Method and apparatus for adaptive control of forward error correction codes |

| KR100608042B1 (ko) * | 1999-06-12 | 2006-08-02 | 삼성전자주식회사 | 멀티 미디어 데이터의 무선 송수신을 위한 인코딩 방법 및그 장치 |

| US6651213B2 (en) * | 2001-03-19 | 2003-11-18 | International Business Machines Corporation | Programmable multi-level track layout method and system for optimizing ECC redundancy in data storage devices |

| JP2005151299A (ja) * | 2003-11-18 | 2005-06-09 | Sanyo Electric Co Ltd | 無線通信装置、誤り訂正方法、および誤り訂正プログラム |

| WO2006062552A1 (en) * | 2004-12-06 | 2006-06-15 | Thomson Licensing | Multiple flows for incremental forward error corection mechanisms |

| JP4930024B2 (ja) * | 2006-12-08 | 2012-05-09 | 富士通株式会社 | 送信装置及び受信装置並びにデータ伝送方法 |

| US20090282308A1 (en) * | 2008-05-09 | 2009-11-12 | Jan Gutsche | Memory Cell Arrangement and Method for Reading State Information From a Memory Cell Bypassing an Error Detection Circuit |

| US8473815B2 (en) * | 2008-12-22 | 2013-06-25 | Industrial Technology Research Institute | Methods and systems of a flash memory controller and an error correction code (ECC) controller using variable-length segmented ECC data |

| JP5084777B2 (ja) | 2009-04-22 | 2012-11-28 | キヤノン株式会社 | 表示制御装置、撮像装置、表示制御装置の制御方法、及びプログラム |

| US20110286271A1 (en) * | 2010-05-21 | 2011-11-24 | Mediatek Inc. | Memory systems and methods for reading data stored in a memory cell of a memory device |

| JP2012109889A (ja) * | 2010-11-19 | 2012-06-07 | Sony Corp | 送信装置、送信方法、受信装置、受信方法、プログラム、および伝送システム |

-

2010

- 2010-11-19 JP JP2010258569A patent/JP2012109889A/ja active Pending

-

2011

- 2011-09-28 US US13/247,161 patent/US20120131422A1/en not_active Abandoned

- 2011-11-03 EP EP11187646.2A patent/EP2456113A3/en not_active Ceased

- 2011-11-15 CN CN2011103612805A patent/CN102480341A/zh active Pending

- 2011-11-15 CN CN2011204514684U patent/CN202663412U/zh not_active Expired - Lifetime

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05304515A (ja) * | 1992-04-24 | 1993-11-16 | Rohm Co Ltd | デジタルデータ伝送方式 |

| JPH06165143A (ja) * | 1992-11-26 | 1994-06-10 | Sony Corp | 高能率符号化装置および復号化装置 |

| JP2010219869A (ja) * | 2009-03-17 | 2010-09-30 | Sony Corp | 通信装置及び通信方法、コンピューター・プログラム、並びに通信システム |

Non-Patent Citations (3)

| Title |

|---|

| CSNH200900221003; 岡部 聡 Satoshi OKABE: '研究発表3 120GHz帯無線伝送用10Gbps誤り訂正符号化装置' NHK技研R&D NO.116 , 20090715, p.16-21, 日本放送出版協会 * |

| JPN6015004300; DRAFT MIPI Alliance Specification for Camera Serial Interface 2(CSI-2) Draft Version 1.01.00 Revision 0.04, 200904, p.22,23,39,40,46,47,89-91 * |

| JPN6015005879; 岡部 聡 Satoshi OKABE: '研究発表3 120GHz帯無線伝送用10Gbps誤り訂正符号化装置' NHK技研R&D NO.116 , 20090715, p.16-21, 日本放送出版協会 * |

Also Published As

| Publication number | Publication date |

|---|---|

| CN202663412U (zh) | 2013-01-09 |

| US20120131422A1 (en) | 2012-05-24 |

| EP2456113A2 (en) | 2012-05-23 |

| EP2456113A3 (en) | 2015-12-30 |

| CN102480341A (zh) | 2012-05-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2012109889A (ja) | 送信装置、送信方法、受信装置、受信方法、プログラム、および伝送システム | |

| US7734987B2 (en) | Communication method and system using two or more coding schemes | |

| JP5233165B2 (ja) | データ伝送装置 | |

| CN202353700U (zh) | 图像输出装置、图像处理装置和图像拾取装置 | |

| TWI686085B (zh) | 攝像裝置及圖像感測器之資料傳送方法、資訊處理裝置及資訊處理方法以及程式 | |

| US8103942B2 (en) | Data transmission apparatus, data transmission device, data reception device and data transmission system | |

| WO2022078426A1 (zh) | 数据传输方法、系统和计算机可读存储介质 | |

| JP5936030B2 (ja) | 情報処理装置、情報処理方法、及びプログラム | |

| JP2009524335A (ja) | 非圧縮avデータを送受信する装置および方法 | |

| JP5761551B2 (ja) | 送信装置、送信方法、受信装置、受信方法、プログラム、および伝送システム | |

| CN103199954A (zh) | 发送/接收系统和方法 | |

| JP5618143B2 (ja) | 符号化装置、符号化方法、復号装置、復号方法、プログラム、および伝送システム | |

| JP2013141250A (ja) | 階層変調装置及び復調装置とその方法 | |

| US9872035B2 (en) | System and method for transcoding data | |

| WO2011046225A1 (ja) | 復号装置および復号方法、並びに記録媒体 | |

| US20230046212A1 (en) | Information processing device, information processing method, and program | |

| WO2015137854A1 (en) | Method and devices for providing feedback in a communication system | |

| JP2001217727A (ja) | 誤り訂正装置及び方法 | |

| Ohtani et al. | MAC LSI design for wireless MPEG-2 transmission over IEEE802. 11b PHY | |

| JP2012010198A (ja) | Fm多重信号の処理装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131106 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20131106 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140704 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140708 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140822 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150217 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150410 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20150519 |