JP2012108627A - メモリシステム - Google Patents

メモリシステム Download PDFInfo

- Publication number

- JP2012108627A JP2012108627A JP2010255411A JP2010255411A JP2012108627A JP 2012108627 A JP2012108627 A JP 2012108627A JP 2010255411 A JP2010255411 A JP 2010255411A JP 2010255411 A JP2010255411 A JP 2010255411A JP 2012108627 A JP2012108627 A JP 2012108627A

- Authority

- JP

- Japan

- Prior art keywords

- memory

- management information

- difference data

- address

- nonvolatile memory

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/06—Addressing a physical block of locations, e.g. base addressing, module addressing, memory dedication

- G06F12/0638—Combination of memories, e.g. ROM and RAM such as to permit replacement or supplementing of words in one module by words in another module

Abstract

【解決手段】 実施形態に係るメモリシステムは、揮発性メモリを持つ。前記揮発性半導体メモリには、第1の不揮発性メモリが接続される。前記揮発性半導体メモリには、第2の不揮発性メモリが接続される。前記揮発性メモリに最新管理情報を記憶し、前記第1の不揮発性メモリに旧管理情報を記憶し、および前記第2の不揮発性メモリに前記最新管理情報と前記旧管理情報の差分データを記憶するメモリコントローラが設けられる。

【選択図】 図1

Description

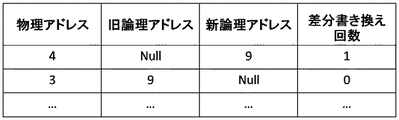

図1は、第1の実施形態に係るメモリシステム1の構成を示すブロック図である。第1の実施形態に係るメモリシステム1は、SATAインターフェース等のインターフェース2を介して、コンピュータ又はCPUコア等のホスト装置3と接続され、ホスト装置の外部メモリとして機能するSSDである。メモリシステム1は、インターフェース2、第1の不揮発性メモリ4としてNAND型フラッシュメモリ、揮発性メモリ5としてDRAM(Dynamic Random Access Memory)、第2の不揮発性メモリ6として比較的小容量であり、かつ高速の不揮発性メモリ、およびメモリコントローラ7を備えている。インターフェース2は、メモリシステム1とコンピュータ等のホスト装置3との通信時における信号の送受信のプロトコルを定めたものであり、例えばSATA(Serial Advanced Technology Attachment)、SAS(Serial Attached SCSI)等のシリアルインターフェースが挙げられる。

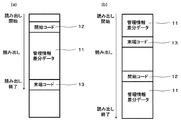

図4は、第2の不揮発性メモリ6上における管理情報差分データ11の保存形式を示す図である。有効な管理情報差分データ11の領域を開始コード12および末端コード13によって識別可能にする。開始コード12および末端コード13は管理情報差分データ11および非書き込み領域のパターンと区別可能なように構成する。例えば、冗長ビットを1bit設けることによって開始コード12および末端コード13を識別することができる。

図5を用いて、管理情報差分データ11の追記方法について説明する。図5(a)に、第2の不揮発性メモリ6上に管理情報差分データ11が書き込まれているアドレス空間を示す。かかる状況において、追記される管理情報差分データ11を末端コード13から上書きする。その後、管理情報差分データ11が全て書き込まれた後、かかるデータの直後のアドレスに新たに末端コード13が書き込まれる。この場合、追加されるデータは管理情報差分データ11および新たな末端コード13のみであるため、第2の不揮発性メモリ6への追記を高速に行うことができる。なお、管理情報差分データ11が書き込まれていない状態においても同様の方法で追記することができる。

図6を用いて、管理情報差分データ11の消去方法について説明する。この消去方法は、例えば、メモリシステム1の正常電源断により第1の不揮発性メモリ4上の管理情報が最新のものに更新され、第2の不揮発性メモリ6上の管理情報差分データ11が不要になる場合に用いられる。図6に第2の不揮発性メモリ6上に管理情報差分データ11が書き込まれているアドレス空間を示す。この状態において、開始コード12に無効なデータ、例えば全て0からなるデータにより上書きし、末端コード13には、新たに開始コード12を上書きし、この新たな開始コード12の直後のアドレスに末端コード13を書き込む。この状態では、開始コード12と末端コード13の間には、管理情報差分データ11が書き込まれていない。これにより、第2の不揮発性メモリ6を読みだしたとき、管理情報差分データ11が存在しないものと認識される。この消去方法は、開始コード12および末端コード13への上書きと、新たな末端コード13の書き込みにより行われるため、差分管理情報データの消去を高速に行うことができる。

図7を用いて、管理情報差分データ11の書き換え方法について説明する。この更新方法は、メモリシステム1の正常電源断により第1の不揮発性メモリ4上の管理情報が最新のものに更新され、第2の不揮発性メモリ6上の管理情報差分データ11が消去されていない状態で新たに差分データを書き込む場合に用いられる。図7に第2の不揮発性メモリ6上に管理情報差分データ11が書き込まれているアドレス空間を示す。この状態において、開始コード12には、無効なデータ、例えば全て0からなるデータにより上書きし、末端コード13には、新たに開始コード12を上書きし、開始コード12の直後のアドレスから管理情報差分データ11を書き込み、その後管理情報差分データ11の末端に、末端コード13を書き込む。この書き換え方法によれば、開始コード12および末端コード13への上書きと管理情報差分データ11の書き込みと、新たな末端コード13の書き込みにより行われるため、差分管理情報データ11の書き換えを高速に行うことができる。

図8に第1の実施形態に係る第2の不揮発性メモリにおいて管理情報差分データ11の読み出し方法を示すフローチャートを示し、図9に開始コード12が末端コード13より前にある場合と後にある場合におけるアドレス空間を示す。以下、図8および図9を用いて、管理情報差分データ11の読み出し方法を説明する。

第2の不揮発性メモリ6の記憶領域が管理情報差分データ11により全て埋まった場合には、以下の動作を行う。まず揮発性メモリ5上の最新管理情報9を第1の不揮発性メモリ4に書き込み、第1の不揮発性メモリ4上の管理情報を最新のものにする。その後、第2の不揮発性メモリ6上の管理情報差分データ11を消去する。これにより、管理情報差分データ11が、第2の不揮発性メモリ6の記憶領域を確保することができる。なお、第2の不揮発性メモリ6の記憶領域が全て埋まった場合において、第2の不揮発性メモリ6に記憶できない管理情報差分データ11を第1の不揮発性メモリ4に追記してもよい。

正常な電源断が行われる場合のメモリシステム1の動作について説明する。正常に電源断を行う際に、揮発性メモリ5上の最新管理情報9を第1の不揮発性メモリ4に書き込み、第1の不揮発性メモリ4上の管理情報を最新のものにする。その後、第2の不揮発性メモリ6上の管理情報差分データ11を消去する。これにより、第2の不揮発性メモリ6の記憶領域に、管理情報差分データ11が全て埋まることを防止することができる。次回のメモリシステム1の起動時には、第1の不揮発性メモリ4に記憶された最新の管理情報を揮発性メモリ5に展開する。

上述の正常な電源断が行われず、異常な電源断が発生した場合において、メモリシステム1におけるデータ復元の動作について説明する。異常な電源断が発生した場合、揮発性メモリ5上の最新管理情報9のデータが失われるため、次回のメモリシステム1の起動時に管理情報のデータ復元が行われる。

本発明の第2の実施形態によるメモリシステム1について図10を用いて説明する。この第2の実施形態の構成について第1の実施形態のメモリシステム1の構成と同一部分は同一符号で示し、その詳細な説明を省略する。この第2の実施形態が、第1の実施形態と異なる点は、図1の第2の不揮発性メモリ6がメモリコントローラ7とは独立して設けられていたものに代えて、メモリコントローラ7のチップ内部に第2の不揮発性メモリ6を組み込み型メモリとして実装する点である。例えば、メモリコントローラ7のチップにFeRAM又はMRAM等の高速の不揮発性メモリを組み込むことができる。

なお、本発明は、上述の実施形態にのみ限定されるものではなく、本発明の要旨を逸脱しない範囲内において種々変更を加え得ることは勿論である。

2…インターフェース

3…ホスト装置

4…第1の不揮発性メモリ

5…揮発性メモリ

6…第2の揮発性メモリ

7…メモリコントローラ

8…ユーザデータ

9…最新管理情報

10…旧管理情報

11…管理情報差分データ

12…開始コード

13…末端コード

Claims (13)

- 揮発性メモリと、

前記揮発性半導体メモリに接続された第1の不揮発性メモリと、

前記揮発性半導体メモリに接続された第2の不揮発性メモリと、

前記揮発性メモリに最新管理情報を記憶し、前記第1の不揮発性メモリに旧管理情報を記憶し、および前記第2の不揮発性メモリに前記最新管理情報と前記旧管理情報の差分データを記憶するメモリコントローラと、

を備えたメモリシステム。 - 前記第2の不揮発性メモリは、前記第1の不揮発性メモリよりレイテンシが小さく、かつ前記揮発性メモリより小容量のものであることを特徴とする請求項1に記載のメモリシステム。

- 前記第2の不揮発性メモリは、前記第1の不揮発性メモリより書き換え可能回数が多いものであることを特徴とする請求項1又は請求項2に記載のメモリシステム。

- 前記第2の不揮発性メモリが、前記メモリコントローラ内に組み込まれたことを特徴とする請求項1乃至請求項3の何れか1項に記載のメモリシステム。

- 前記メモリコントローラは、異常な電源断が発生した場合に、前記旧管理情報と、前記差分データに基づき、前記揮発性メモリ上に前記最新管理情報を復元することを特徴とする請求項1乃至請求項4の何れか1項に記載のメモリシステム。

- 前記メモリコントローラは、正常な電源断を行う場合に、前記最新管理情報を前記第1の不揮発性メモリに書き込み、前記差分データを消去することを特徴とする請求項1乃至請求項5の何れか1項に記載のメモリシステム。

- 前記メモリコントローラは、前記第2の不揮発性メモリにおいて、前記差分データの直前のアドレスに開始コードを記憶し、前記差分データの直後のアドレスに末端コードを記憶することを特徴とする請求項1乃至請求項6の何れか1項に記載のメモリシステム。

- 前記メモリコントローラは、前記差分データを追記する場合に、前記末端コードのアドレスから前記差分データを記憶し、前記差分データの直後のアドレスに新たな末端コードを記憶することを特徴とする請求項7に記載のメモリシステム。

- 前記メモリコントローラは、前記差分データを消去する場合に、前記末端コードのアドレスに新たな開始コードを記憶し、前記新たな開始コードの直後のアドレスに新たな末端コードを記憶することを特徴とする請求項7又は請求項8に記載のメモリシステム。

- 前記メモリコントローラは、前記差分データを書き換える場合に、前記末端コードのアドレスに新たな開始コードを記憶し、前記新たな開始コードの直後のアドレスから前記差分データを記憶し、かつ前記差分データの直後のアドレスに新たな末端コードを記憶することを特徴とする請求項7乃至請求項9の何れか1項に記載のメモリシステム。

- 前記メモリコントローラは、前記差分データを読み出す場合において、前記第2の不揮発性メモリの先端アドレスから順にアドレスをインクリメントして読み出しを実行し、前記末端コードよりも先に前記開始コードを読み出した場合に、前記開始コードの直後のアドレスから前記末端コードの直前のアドレスまでのデータを前記差分データとして読み込むことを特徴とする請求項7乃至請求項10の何れか1項に記載のメモリシステム。

- 前記メモリコントローラは、前記差分データを読み出す場合において、前記第2の不揮発性メモリの先端アドレスから順にアドレスをインクリメントして読み出しを実行し、前記開始コードよりも先に前記末端コードを読み出した場合に、前記先端アドレスから前記末端コードの直前のアドレスまで、および前記開始コードの直後のアドレスから前記第2の不揮発性メモリの末端アドレスまでのデータを管理情報差分データとして読み込むことを特徴とする請求項7乃至請求項11の何れか1項に記載のメモリシステム。

- 前記メモリコントローラは、前記第2の不揮発性メモリが前記差分データで埋まった場合に、前記最新管理情報を前記第1の不揮発性メモリに書き込み、かつ前記差分データを消去することを特徴とする請求項7乃至請求項12の何れか1項に記載のメモリシステム。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010255411A JP2012108627A (ja) | 2010-11-15 | 2010-11-15 | メモリシステム |

| US13/069,963 US20120124275A1 (en) | 2010-11-15 | 2011-03-23 | Memory system and data storage method |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010255411A JP2012108627A (ja) | 2010-11-15 | 2010-11-15 | メモリシステム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2012108627A true JP2012108627A (ja) | 2012-06-07 |

| JP2012108627A5 JP2012108627A5 (ja) | 2013-08-01 |

Family

ID=46048858

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010255411A Pending JP2012108627A (ja) | 2010-11-15 | 2010-11-15 | メモリシステム |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US20120124275A1 (ja) |

| JP (1) | JP2012108627A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9063845B2 (en) | 2012-08-29 | 2015-06-23 | Buffalo Memory Co., Ltd. | Solid-state drive device |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9032264B2 (en) | 2013-03-21 | 2015-05-12 | Kabushiki Kaisha Toshiba | Test method for nonvolatile memory |

| CN110325971A (zh) * | 2017-06-20 | 2019-10-11 | 京瓷办公信息系统株式会社 | 存储器系统及电子设备 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08328821A (ja) * | 1995-05-30 | 1996-12-13 | Kokusai Electric Co Ltd | データ読み出しポイントのサーチ方法 |

| JP2000105694A (ja) * | 1998-09-28 | 2000-04-11 | Nec Ic Microcomput Syst Ltd | フラッシュメモリ、フラッシュメモリを備えたマイクロコンピュータおよびフラッシュメモリへのプログラム格納方法 |

| JP2007156846A (ja) * | 2005-12-05 | 2007-06-21 | Tdk Corp | メモリコントローラ及びフラッシュメモリシステム |

| JP2009009213A (ja) * | 2007-06-26 | 2009-01-15 | Ricoh Co Ltd | データ記憶装置、プログラムおよびデータ記憶方法 |

| JP2009211223A (ja) * | 2008-03-01 | 2009-09-17 | Toshiba Corp | メモリシステム |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3603333B2 (ja) * | 1994-06-22 | 2004-12-22 | カシオ計算機株式会社 | データ処理装置 |

| US5568443A (en) * | 1995-09-08 | 1996-10-22 | Smithills Multimedia Systems, Inc. | Combination dual-port random access memory and multiple first-in-first-out (FIFO) buffer memories |

| US6732223B1 (en) * | 2000-04-03 | 2004-05-04 | Micron Technology, Inc. | Method and apparatus for address FIFO for high-bandwidth command/address busses in digital storage system |

| JP2005115857A (ja) * | 2003-10-10 | 2005-04-28 | Sony Corp | ファイル記憶装置 |

| US20050251617A1 (en) * | 2004-05-07 | 2005-11-10 | Sinclair Alan W | Hybrid non-volatile memory system |

| US8028123B2 (en) * | 2008-04-15 | 2011-09-27 | SMART Modular Technologies (AZ) , Inc. | Circular wear leveling |

| US8843691B2 (en) * | 2008-06-25 | 2014-09-23 | Stec, Inc. | Prioritized erasure of data blocks in a flash storage device |

| JP5317690B2 (ja) * | 2008-12-27 | 2013-10-16 | 株式会社東芝 | メモリシステム |

-

2010

- 2010-11-15 JP JP2010255411A patent/JP2012108627A/ja active Pending

-

2011

- 2011-03-23 US US13/069,963 patent/US20120124275A1/en not_active Abandoned

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08328821A (ja) * | 1995-05-30 | 1996-12-13 | Kokusai Electric Co Ltd | データ読み出しポイントのサーチ方法 |

| JP2000105694A (ja) * | 1998-09-28 | 2000-04-11 | Nec Ic Microcomput Syst Ltd | フラッシュメモリ、フラッシュメモリを備えたマイクロコンピュータおよびフラッシュメモリへのプログラム格納方法 |

| JP2007156846A (ja) * | 2005-12-05 | 2007-06-21 | Tdk Corp | メモリコントローラ及びフラッシュメモリシステム |

| JP2009009213A (ja) * | 2007-06-26 | 2009-01-15 | Ricoh Co Ltd | データ記憶装置、プログラムおよびデータ記憶方法 |

| JP2009211223A (ja) * | 2008-03-01 | 2009-09-17 | Toshiba Corp | メモリシステム |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9063845B2 (en) | 2012-08-29 | 2015-06-23 | Buffalo Memory Co., Ltd. | Solid-state drive device |

| US9632714B2 (en) | 2012-08-29 | 2017-04-25 | Buffalo Memory Co., Ltd. | Solid-state drive device |

Also Published As

| Publication number | Publication date |

|---|---|

| US20120124275A1 (en) | 2012-05-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8862808B2 (en) | Control apparatus and control method | |

| US9400744B2 (en) | Magnetic random access memory journal for multi-level cell flash memory | |

| JP5317690B2 (ja) | メモリシステム | |

| US9026764B2 (en) | Memory system performing wear leveling based on deletion request | |

| JP4871260B2 (ja) | メモリモジュール、メモリコントローラ、不揮発性記憶装置、不揮発性記憶システム、及びメモリの読み書き方法 | |

| US20150331624A1 (en) | Host-controlled flash translation layer snapshot | |

| JP5990430B2 (ja) | Ssd(ソリッドステートドライブ)装置 | |

| CN111752487B (zh) | 一种数据恢复方法、装置及固态硬盘 | |

| JP5983019B2 (ja) | 制御装置、記憶装置、記憶制御方法 | |

| US10838629B2 (en) | Solid state device with fast boot after ungraceful shutdown | |

| TWI662410B (zh) | 資料儲存裝置與記憶體裝置之資料處理方法 | |

| US20190324859A1 (en) | Method and Apparatus for Restoring Data after Power Failure for An Open-Channel Solid State Drive | |

| JP5631938B2 (ja) | 半導体記憶装置 | |

| US9208101B2 (en) | Virtual NAND capacity extension in a hybrid drive | |

| KR20120086239A (ko) | 메모리 시스템 및 그 동작 방법 | |

| JPWO2007119267A1 (ja) | フラッシュメモリ用のメモリコントローラ | |

| US10152280B2 (en) | Storage device and control method | |

| US20180150390A1 (en) | Data Storage Device and Operating Method Therefor | |

| US20170147232A1 (en) | Solid state drive and data programming method thereof | |

| JP2013222435A (ja) | 半導体記憶装置及びその制御方法 | |

| JP5874525B2 (ja) | 制御装置、記憶装置、記憶制御方法 | |

| US8527733B2 (en) | Memory system | |

| US10942811B2 (en) | Data processing method for solid state drive | |

| JP2012108627A (ja) | メモリシステム | |

| JP2006099802A (ja) | 記憶制御装置およびキャッシュメモリの制御方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130614 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20130614 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140115 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140214 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20140704 |