JP2012089564A - 光通信モジュールおよび光通信装置 - Google Patents

光通信モジュールおよび光通信装置 Download PDFInfo

- Publication number

- JP2012089564A JP2012089564A JP2010232590A JP2010232590A JP2012089564A JP 2012089564 A JP2012089564 A JP 2012089564A JP 2010232590 A JP2010232590 A JP 2010232590A JP 2010232590 A JP2010232590 A JP 2010232590A JP 2012089564 A JP2012089564 A JP 2012089564A

- Authority

- JP

- Japan

- Prior art keywords

- wiring

- optical communication

- circuit

- communication module

- laser diode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Semiconductor Lasers (AREA)

Abstract

【課題】光通信モジュールおよびそれを含んだ光通信装置の高速化・小型化を実現する。

【解決手段】例えば、レーザダイオードLDと、LDを電流駆動するレーザダイオードドライバLDDと、LDとLDDを接続する伝送路TLINEから成る光送信系の回路において、LDDが、波形等化機能を有するプリドライバ回路PDRVを含んだドライバ回路DRVと、バイアス回路DC_BIASとを備える。DC_BIASは、内部に終端抵抗を備え、当該終端抵抗を用いてTLINEとLDのインピーダンス不整合に伴う反射を終端すると共に、当該終端抵抗を利用してバイアス電流Ibiasを生成する。DRVは、Ibiasに変調電流Iacを合成した電流によってLDを駆動する。

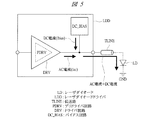

【選択図】図5

【解決手段】例えば、レーザダイオードLDと、LDを電流駆動するレーザダイオードドライバLDDと、LDとLDDを接続する伝送路TLINEから成る光送信系の回路において、LDDが、波形等化機能を有するプリドライバ回路PDRVを含んだドライバ回路DRVと、バイアス回路DC_BIASとを備える。DC_BIASは、内部に終端抵抗を備え、当該終端抵抗を用いてTLINEとLDのインピーダンス不整合に伴う反射を終端すると共に、当該終端抵抗を利用してバイアス電流Ibiasを生成する。DRVは、Ibiasに変調電流Iacを合成した電流によってLDを駆動する。

【選択図】図5

Description

本発明は、光通信モジュール、およびそれを含んだ光通信装置に関し、特に、ルータやサーバ等の光通信装置、およびその部品の一つでありレーザダイオードを用いて光通信を行う光通信モジュールに適用して有効な技術に関する。

例えば、特許文献1には、高速光送信回路の出力インピーダンスを制御するインピーダンス整合装置を設けた光送信回路が記載されている。具体的には、抵抗及びインピーダンス整合用トランジスタから成る終端部と、オペアンプを用いた基準電圧生成回路部から成る構成等が示されている。これによって、レーザダイオードドライバと伝送路とのインピーダンス不整合による波形歪みが補償できる。

近年、通信速度の高速化に伴い、その通信速度は10Gbpsから25Gbps、40Gbps等へと遷移している。このような通信速度の高速化に伴い、例えばルータ装置やサーバ装置として、光ファイバケーブルに対応した光通信装置の適用が進んでいる。光通信装置は、通常、装置間におけるキロメートルオーダーといった長距離伝送を前提としており、この伝送距離に伴う高速性、信頼性の確保が重要となっている。

このような光通信装置の中には、比較的大型のサイズ(例えば数十センチメートルオーダーやメートルオーダー)を持つ装置も多数存在するが、その装置内部では、通常、電気信号を用いた通信が行われている。すなわち、光通信装置は、例えば、外部から入力された光信号を電気信号に変換し、この電気信号によって装置内部での短距離通信(例えばメートルオーダー)を行いながら所定の処理を行い、再び電気信号を光信号に変換して外部に出力している。この短距離通信は、例えば、銅線ケーブル等を用いて行われるが、通信速度の高速化が進むにつれて、銅線ケーブルでは伝送波形品質の著しい低下が生じてしまう。したがって、このような装置内部の短距離通信にも光通信を適用することが求められつつある。この場合、ユーザ側から見ると、銅線ケーブルから光ファイバケーブルへ移行するにあたって、既存の装置において各入出力インターフェース部分が存在する限られた実装面積の範囲内に光通信用の各回路(光通信モジュール)を実装することが望ましい。そのためには、光通信モジュールの小型化が必要となり、その結果、信号線の高密度化等が発生する。

図20は、本発明の前提として検討した光通信モジュールの実装構造の一例を示す斜視図である。図20に示す光通信モジュールは、光通信モジュール内の光素子OP1(例えばレーザダイオードLD)と、それを駆動するレーザダイオードドライバLDDを含んだ光制御チップLSI_OPとが、ボンディングワイヤWBにより電気的に接続された構成となっている。LSI_OPには、コネクタCNTを介して電気信号が入出力され、また必要に応じて、周囲に対する電源雑音の影響を低減するためのバイパス用の容量CAPが接続される。しかし、このような実装方式では、隣接信号間がWB上で容量結合及び誘導結合してしまうため、通信速度の高速化、信号配線の高密度化が進むにつれ、隣接信号間のクロストークの影響により、伝送品質が著しく劣化する恐れがある。

そこで、クロストークの影響を低減し、高密度化による光通信モジュールの小型化を実現する実装方式として、例えば、図3(b)、(c)に示すような実装方式が考えられる。図3(b)では、配線基板(例えば多層セラミック基板)BD_MD上に、光素子OP1(レーザダイオードLD)と光制御チップLSI_OP(レーザダイオードドライバLDDを含む)が実装され、それらが内層配線LN1を介して電気的に接続される。この際に、図3(c)に示すように、各内層配線LN1_CH1、LN1_CH2、LN1_CH3は、上下あるいは左右に配置されたグラウンド用の内層配線LNgndを挟んで配置される。これによって、相互キャパシタンス成分及び、相互インダクタンス成分を効果的に低減し、隣接信号間のクロストークの影響を抑えることが可能となる。

しかしながら、このような実装方式では、光素子OP1(LD)と光制御チップLSI_OP(LDD含む)をグラウンド線(LNgnd)でシールドしながら、内層配線(LN1)で接続しているため、LN1上の容量成分が増加し、高速動作が困難となる恐れがある。更に、LSI_OP(LDD含む)及びOP1(LD)とLN1との間のインピーダンス不整合により、反射が発生し、伝送品質が劣化することが懸念される。特に、LDDとLD間の光送信部は、レーザダイオードLDの抵抗成分が例えば十数Ωのため、反射による影響が顕著である。

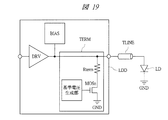

このような光送信部におけるインピーダンス不整合の問題を解決する手段として、例えば、特許文献1では、光送信回路の出力に伝送路とのインピーダンス整合を取るための終端部を設ける方式が用いられている。図19は、本発明の前提として検討した光通信モジュールにおいて、その構成の一例を示す回路ブロック図である。図19に示す光通信モジュールは、LDと、LDとLDD間を接続する伝送路TLINEで構成される。LDDは、DCバイアス電流を供給するバイアス回路BIAS、AC変調電流を供給するドライバ回路DRV、TLINEとのインピーダンス整合を取るための終端部TERMから成る。

図4は、レーザダイオードLDの動作例を示す説明図である。LDから一定の光出力パワーを得るには、LDを駆動するレーザダイオードドライバLDDから、DCバイアス電流IbiasとAC変調電流Imin−Imaxを、LDに供給する必要がある。この結果、平均光出力パワーPmid、振幅Pmax−Pminの光信号が出力される。例えば25Gbpsを超える高速光伝送では、高速動作を可能とする緩和振動周波数の確保のため、LDで必要とされるDCバイアス電流は数十mAといったように大きな値となる。更に高温動作時においては、LDの閾値電流Ithが大きくなるために、常温時と比較し、より大きなDCバイアス電流の供給が必要となる。このため、図19に示したBIASの電流源を構成するトランジスタのサイズが大きくなり、当該トランジスタの寄生成分により、LDDとTLINE間の容量成分が増加し、25Gbpsを超える高速な通信速度の実現が困難となる恐れがある。

本発明は、このようなことを鑑みてなされたものであり、その目的の一つは、光通信モジュール及び光通信装置の高速化または小型化を実現することにある。本発明の前記並びにその他の目的と新規な特徴は、本明細書の記述及び添付図面から明らかになるであろう。

本願において開示される発明のうち、代表的な実施の形態の概要を簡単に説明すれば、次のとおりである。

本実施の形態による光通信モジュールは、レーザダイオードと、伝送路と、バイアス電流回路およびドライバ回路を含んだレーザダイオードドライバとを備え、バイアス電流回路は、可変抵抗と、オペアンプおよびトランジスタ等から構成されるレギュレータとを有するものとなっている。この可変抵抗を伝送路の特性インピーダンスに応じて調整することで、レーザダイオードドライバと伝送路とのインピーダンス整合を取ることが可能である。更に、この方式は、可変抵抗を、インピーダンス整合手段としてのみでなく、DCバイアス電流の供給手段としても用いていることが特徴となっている。レギュレータは、このDCバイアス電流の値を設定する、あるいは、微調整する手段として用いられる。このような構成例を用いると、DCバイアス電流生成用の電流源を構成するためのサイズが大きいトランジスタが不要となり、信号配線上の寄生容量を低減し、光通信モジュールの高速化が実現可能となる。更に、可変抵抗によるインピーダンス整合により、伝送路との間の反射を防ぎ、多層セラミックパッケージを用いた高密度な信号配線の実装が可能となる。その結果、光通信装置の小型化が実現可能となる。

本願において開示される発明のうち、代表的な実施の形態によって得られる効果を簡単に説明すると、通信速度の高速化、または、光通信モジュールおよびそれを含んだ光通信装置の小型化が実現可能になる。

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらは互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。

さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

また、実施の形態の各機能ブロックを構成する回路素子は、特に制限されないが、公知のCMOS(相補型MOSトランジスタ)等の集積回路技術によって、単結晶シリコンのような半導体基板上に形成される。なお、実施の形態では、MISFET(Metal Insulator Semiconductor Field Effect Transistor)の一例としてMOSFET(Metal Oxide Semiconductor Field Effect Transistor)(MOSトランジスタと略す)を用いるが、ゲート絶縁膜として非酸化膜を除外するものではない。図面にはMOSトランジスタの基板電位の接続は特に明記していないが、MOSトランジスタが正常動作可能な範囲であれば、その接続方法は特に限定しない。

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

(実施の形態1)

図1は、本発明の実施の形態1による光通信装置を示すものであり、(a)は、その外形の一例を示す斜視図、(b)は、(a)の内部構造の一例を示す斜視図である。図1(a)に示す光通信装置は、ルータ装置等であり、例えば、幅および奥行きがそれぞれ数十センチ、高さが1〜2m等といった筐体CSEで構成されている。CSEの表面には、多数の通信コネクタCNcが設けられ、CNcのそれぞれは、例えばイーサネット(登録商標)ケーブル端子や、あるいは光ファイバケーブル端子等である。

図1は、本発明の実施の形態1による光通信装置を示すものであり、(a)は、その外形の一例を示す斜視図、(b)は、(a)の内部構造の一例を示す斜視図である。図1(a)に示す光通信装置は、ルータ装置等であり、例えば、幅および奥行きがそれぞれ数十センチ、高さが1〜2m等といった筐体CSEで構成されている。CSEの表面には、多数の通信コネクタCNcが設けられ、CNcのそれぞれは、例えばイーサネット(登録商標)ケーブル端子や、あるいは光ファイバケーブル端子等である。

CSEの内部には、例えば、図1(b)に示すように、複数のインタフェースカードIFC(IFC[1],IFC[2],…)や、スイッチカードSWC等が備わっている。各カードは、バックプレーンBKP等と呼ばれる部品に備わったカードコネクタにそれぞれ接続される。各カードコネクタには、BKPから各カードに電源を供給するためのコネクタや、光通信線路(代表的には光ファイバケーブル)OFを介して各カード間で通信を行うための光コネクタ(光ファイバコネクタ)CNoが含まれている。ここでは、各インタフェースカードIFCがCNoと光通信線路OFを介してスイッチカードSWCに接続され、これによって各IFCが受け持つ通信コネクタCNc間でSWCを介した通信が可能となる。

各IFCには、通信の上位階層で必要となる所定のプロトコル処理を行う論理デバイスLSI_LGiや、このLSI_LGiの入出力となる電気信号を光信号に変換し、光コネクタCNoを介して光通信線路OFとの間の入出力を行う光通信モジュールOMDiが実装されている。同様に、SWCにも、所定のプロトコル処理を行う論理デバイスLSI_LGsや、このLSI_LGsの入出力となる電気信号を光信号に変換し、CNoを介してOFとの間の入出力を行う光通信モジュールOMDsが実装されている。

このような光通信装置において、各光通信線路OFの長さは、例えば数メートルに達する場合がある。この場合、OFの代わりに銅線ケーブル等を用いると、伝送損失により、例えば数十Gbpsレベルの通信に対応できない恐れがある。また、通信速度の高速化(通信帯域の拡大)を図るため、各光通信モジュールOMD(OMDi,OMDs)は、並列に複数本(それぞれ通信チャネルと呼ばれる)の光入出力を行う場合があるが、この通信チャネル数が増加するほど、より高密度実装(小型化)に対応可能な光通信モジュールが求められる。そこで、本実施の形態の光通信モジュールおよび光通信装置を用いることが有益となる。

図2は、図1の光通信装置において、光通信モジュールOMDの概略構成の一例を示すブロック図である。光通信モジュールOMDは、伝送速度変換回路SDC、アナログフロントエンドブロックAFE、光素子ブロックOBKを備えている。光素子ブロックOBKは、送信用の光通信線路OFtxに出力を行うレーザダイオードLDと、受信用の光通信線路OFrxから入力された光信号を電気信号(電流信号)に変換するフォトダイオードPDを備えている。LDおよびPDは、実際には、通信チャネル数に応じてLD,PD共にそれぞれ複数個設けられる。この複数個のLDや複数個のPDは、それぞれ個別の半導体チップで構成したり、あるいは半導体チップ上でアレイ状に纏めて集積することも可能である。

アナログフロントエンドブロックAFEは、LDを駆動するレーザダイオードドライバLDDと、PDからの電流信号を増幅ならびに電圧信号に変換するトランスインピーダンスアンプ回路TIAを備えている。伝送速度変換回路SDCは、SerDes(Serializer/Deserializer)等と呼ばれ、AFE(LDDおよびPD)に対する入出力信号の伝送速度と光通信モジュールOMD外部(すなわちLSI_LG)に対する入出力信号の伝送速度とを変換する。例えば、図1の論理デバイスLSI_LG(LSI_LGi,LSI_LGs)とOMD(OMDi,OMDs)の間では、10Gbps×10本(10チャネル)の電気信号が送受信され、SDCは、この電気信号を25Gbps×4本(4チャネル)に変換してAFEとの間で送受信する。この場合、図1の各カード(IFC,SWC)間の光通信線路OFを介した通信も、光素子25Gbps×4チャネルで行われる。なお、図2の例では、AFEとSDC間の電気入出力の低減による省電力化を図るため、AFEとSDCをCMOSプロセス等の同一半導体プロセスで形成し、それを光制御チップLSI_OPとして一体集積した構成となっている。ただし、AFEとSDCは、それぞれ別の半導体チップとして実装されてもよい。

図3(a)〜(c)は、図2の光通信モジュールOMDにおいて、そのレーザダイオードLDとレーザダイオードドライバLDD関連の概略的な実装構造の一例を示す断面図である。図3(a)は、同一の配線基板(例えば多層セラミックパッケージ基板)BD_MD上に光制御チップLSI_OP(LDD等)と光素子OP1(LD)が実装され、BD_MD内の内層配線LN1を用いてLSI_OPとOP1が電気的に接続された構造となっている。図3(b)は、図3(a)における内層配線LN1周りを拡大した構造例を示す断面図であり、図3(c)は、図3(b)におけるA−A’間の構造例を示す断面図である。

光素子OP1(LD)は、第1面に形成されたバンプBP1を介して配線基板BD_MDの第1面に接続され、光制御チップLSI_OP(LDD等)は、第1面に形成されたバンプBP2を介してBD_MDの第1面に接続される。BP1の一部とBP2の一部は、BD_MD内の内層配線(代表的には銅配線)LN1を介して接続され、これによって、OP1(LD)とLSI_OP(LDD等)が電気的に接続される。また、BD_MDは、第2面に形成されたバンプBP3を介して配線基板BD_CDの第1面に接続される。これにより、BP2の一部は、BD_MD内の内層配線LN2を介してBP3の一部に接続される。BD_CDの第1面には、コネクタCNTが設けられており、BP3の一部がBD_CD内の内層配線LN3を介してCNTに接続される。これにより、LSI_OP(LDD等)とCNTがLN2,LN3を介して電気的に接続される。このCNTには、例えば、図1の論理デバイスLSI_LGからの電気信号が入力される。OP1(LD)は、LDDからの駆動信号に応じてレーザ光を出力し、このレーザ光は、コリメートレンズや集光レンズ等を含んだ光コネクタCNoを介して光通信線路OFtxへと出力される。

ところで、サーバやルータ等の情報処理装置では、高速化や通信容量の拡大が進んでおり、これを実現するために、通信チャネルの拡大と、各通信チャネルにおける伝送速度の高速化が求められる。また、実用上、情報処理装置の大型化は望ましくないため、当該装置のサイズを変えずに(又は小型化しつつ)高速化や通信容量の拡大を図るためには、各通信チャネルの信号配線を狭ピッチ(例えば250μm間隔程度)に配置するといった高密度実装が必要とされる。従来、光通信モジュールでは、光素子OP1(LD)と光制御チップLSI_OP(LDD等)間の容量成分が少なく、高速動作の実現が容易な図20に示すようなワイヤボンディングによる実装方式が主に用いられていた。しかしながら、当該実装方式では、信号配線を狭ピッチ化すると隣接通信チャネル間のクロストークの影響が大きくなり、この影響は、伝送速度が25Gbps、40Gbps等と高速化するにつれて益々増大するため、伝送波形品質の著しい劣化が生じてしまう恐れがある。例えば、クロストークの影響を低減する方法として、各通信チャネル間にグラウンド線を追加し、シールドすることが考えられるが、ワイヤボンディングの実装ばらつき等を考慮すると、十分なシールド効果を得ることは困難である。

一方、図3(a)に示す配線基板BD_MDを用いた実装において、光素子OP1(LD)と光制御チップLSI_OP(LDD等)との間の内層配線LN1は、図3(b)に示すように、その上下の層に絶縁層ISLを挟んでグラウンド用の内層配線LNgndが備わっている。また、LN1は、図2等で述べたように、実際には、OP1(LD)の数に応じて複数本(複数の通信チャネル)存在するが、図3(c)に示すように、各通信チャネルに対応する配線間(例えばLN1_CH1とLN1_CH2間)にもグラウンド用の内層配線LNgndが備わっている。このように、所謂コプレーナ線路などを用いることで、隣接通信チャネル間の相互キャパシタンス成分及び、相互インダクタンス成分等を低減でき、隣接通信チャネル間のクロストークを低減できる。

この図3(b)においては、グラウンドプレーン及びグラウンド配線を用いたシールド構造により、内層配線LN1から見える容量成分が増えるため、伝送路(内層配線LN1)の特性インピーダンスは小さくなり、例えば25〜40Ω程度の値となる。一方、レーザダイオードLDの等価抵抗は例えば十数Ω程度のため、レーザダイオードLDと伝送路とのインピーダンス不整合により、反射が発生し、伝送品質が劣化する。なお、容量成分を更に増加させると特性インピーダンスが低下するが、この場合、容量成分によって高速化が図れなくなる。このため、図3(b)の実装構造を前提とした光通信モジュールを実現するためには、レーザダイオードドライバLDD側で伝送路とのインピーダンス整合を取るための手段を備え、反射を低減することが必要となる。

図4は、図2の光通信モジュールOMDにおいて、レーザダイオードドライバLDDの駆動電流により、レーザダイオードLDから光出力パワーを生成する機構を説明する概略図である。LDを駆動するには、LDDから、DCバイアス電流Ibiasと、最大駆動電流Imaxから最小駆動電流Iminで遷移するAC変調電流の供給を必要とし、その結果、平均光出力パワーPmidを基準として、最大光出力パワーPmaxから最小光出力パワーPminで遷移する光信号が生成できる。

ここで、例えば25Gbpsを超える伝送速度においては、LDの緩和振動周波数を向上させる必要があるが、LDの構造的な改良による周波数向上のみでは伝送速度の高速化に十分対応できない恐れがある。この場合、DCバイアス電流の増加が必要とされ、常温で例えば30mA程度のバイアス電流の供給が必要となる。また、空冷を前提とするサーバやルータ等への光通信モジュールの適用においては、LDのデバイス温度が上昇することでLDの閾値電流Ithが増加するため、例えば60mA以上のバイアス電流の供給が必要とされる。AC電流(AC変調電流)については、最大伝送速度の半分の周波数で高速にLD駆動電流を遷移させる必要があるが、光伝送系の光結合系における損失を考慮し、受信側での負担を考慮すると、電流振幅を大きくし、光出力パワーを増加させることが望ましい。

図5は、図2におけるレーザダイオードドライバLDD等の主要な回路構成例を示すブロック図である。図5に示すレーザダイオードドライバLDDには、ドライバ回路DRVと、バイアス回路DC_BIASとが形成されている。DRVは、場合によっては、プリドライバ回路PDRVを含んでいる。DC_BIASは、DCバイアス電流Ibiasの生成に加えて、詳細は後述するが、反射波形の終端を行うことが特徴となっている。DRVは、図3の伝送速度変換回路SDCを介して入力された信号に応じたAC電流(±Iac)を生成し、Ibiasに加算する。この際に、PDRVは、このAC電流(±Iac)の波形に対して波形等化を行う。

レーザダイオードLDは、伝送路TLINEを介して、(Ibias±Iac)によって駆動される。ここで、電源雑音が大きい状態で、Ibiasを供給すると、DRVからTLINE間の信号線が揺れ、信号品質が劣化するため、DC_BIASには、電源雑音の影響を抑え、安定したバイアス電流の供給が求められる。従来、DC_BIASは、例えばPMOSトランジスタを使用したMOS電流源が用いられていた。この場合、先に述べたように、25Gbpsを超える伝送速度を実現するには、30mA以上のバイアス電流の供給が必要となるため、MOS電流源を形成するトランジスタのサイズが大きくなり、寄生容量によりDRVの出力容量が増加し、高速なAC電流の生成が困難になる恐れがある。

図6は、図5におけるバイアス回路DC_BIASの詳細な回路構成例を示すブロック図である。DC_BIASは、レギュレータ回路VREGと、終端抵抗Rtermを備えている。VREGは、オペアンプ回路AMPrと、PMOSトランジスタMOSpから成る。AMPrの出力はMOSpのゲートに入力され、MOSpは、ソースに電源電圧VDDが供給され、ドレインから電源電圧VDD2を出力する。VDD2は、Rtermの一端に供給されると共にAMPrの2入力の一方に帰還され、AMPrの2入力の他方には制御電圧Vrefが供給される。

このように、DC_BIASでは、LDに供給するDCバイアス電流Ibiasが電源電圧VDDからレギュレータ回路VREGと終端抵抗Rtermを介して供給され、終端抵抗Rtermの値を調整することで伝送路TLINEとのインピーダンス整合が可能となっていることが特徴となっている。すなわち、Vref(=VDD2)の値によってLDに供給するバイアス電流Ibias=(VDD2−Vs)/Rtermの大きさが設定可能であり、更に、Vrefの値を例えばLDの温度変動等に応じて変更することで温度補償等も可能な構成となっている。なお、Vsは、Rtermの他端(DRVの出力ノード)の電圧であり、これはLDの順方向電圧Vfに応じて定まる。

以上のように、図6のような構成例を取ると、終端抵抗Rtermを用いて、LDDとTLINEとのインピーダンス整合を取ることで、反射の影響の低減が可能となる。また、LDに供給するDCバイアス電流を、MOS電流源等で生成するのではなく、終端抵抗を利用してLDに供給するため、信号線上の寄生容量を低減し、AC電流を生成するドライバ回路DRVの高速動作が可能となる。これによって、例えば25Gbpsを超える伝送速度においても、隣接通信チャネル間の低クロストーク化が可能となり、多チャネル化による光通信モジュールの高密度化・小型化に有利な、図3の実装構造の適用が可能となる。また、図1に示すようなルータやサーバ等の情報処理装置に適用した際、通信データ量の大容量化が可能となる。更に、レギュレータ回路VREGを用いて、安定な電源電圧VDD2を生成しているため、電源雑音による影響を抑え、高品質な信号伝送が可能となる。

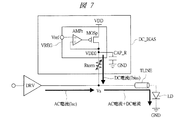

図7は、図6のバイアス回路において、電源変動の影響を抑えるための容量CAP_Rを加えた構成例を示すブロック図である。図7では、図6の構成例に対して、電源電圧VDD2と接地電源電圧GNDの間に容量CAP_Rが付加されている。このように、電源雑音を抑えたい周波数帯域に応じて、容量CAP_Rを搭載することが、電源雑音の低減に関して、より効果的である。ここで、低域の電源雑音成分まで低減する必要がある場合は、CAP_Rのサイズが大きくなり、半導体チップ内の搭載が困難となる可能性があるが、その場合は、CAP_Rを、なるべく半導体チップから近い場所に、半導体チップと別々に実装してもよい。

図12は、図5のレーザダイオードドライバLDDにおいて、ドライバ回路DRVの詳細な構成例を示すものであり、(a)〜(c)は差動型を用いた場合の回路図、(d)はシングルエンド型を用いた場合の回路図となっている。ここでは、プリドライバ回路PDRVを含まない場合の構成例が示されている。図12(a)に示すドライバ回路DRVは、NMOSトランジスタMNd1,MNd2と、電流源INS,IPSによって構成される。MNd1,MNd2は、差動対を構成し、ソースが共通接続され、各ゲートに伝送速度変換回路SDC等からの差動信号(Vinn,Vinp)が入力される。テール電流源となるINSは、MNd1,MNd2の共通ソースノードとGNDの間に接続される。ここで、LDはシングル入力のため、MNd1のドレインノードは、制御電圧VCSで固定し、MNd2のドレインノードは、負荷電流源となるIPSに接続することで、差動信号からシングルエンド信号への変換を行っている。

図12(b)は、より高速化を実現するため、図12(a)に、NMOSトランジスタMNc1,MNc2を追加した構成である。MNc1,MNc2は、ゲートノードに制御電圧VCASが接続されたゲート接地トランジスタとなっており、ソースがMNd1,MNd2のドレインにそれぞれカスコード接続される。これによって、DRVと伝送路TLINE間のトランジスタの寄生容量を低減でき、動作周波数帯域の向上が可能となる。図12(c)は、図12(b)のMNd1,MNd2のドレインノード間を、容量CAP_Dで接続した構成である。これによって、差動信号からシングルエンド信号に変換する際、コモン成分の変動を抑え、より安定した信号の変換が可能となる。

一方、図12(d)に示すドライバ回路DRVは、NMOSトランジスタMNd1,MNc1、電流源IPSによって構成される。MNd1は、ソースがGNDに接続され、ゲートに伝送速度変換回路SDC等からの出力信号が入力される。MNc1は、ゲートノードに制御電圧VCASが接続されたゲート接地トランジスタとなっており、ソースがMNd1のドレインにカスコード接続される。図12(b)と同様に、MNc1は、動作周波数帯域を向上させるために備わっている。

図13(a)、(b)は、図5におけるプリドライバ回路PDRVを含んだドライバ回路DRVのそれぞれ異なる構成例を示す回路ブロック図である。図13(a)のドライバ回路DRVは、例えば、3個の可変増幅回路VAMP1〜VAMP3と、2個のデジタル遅延回路DLY1,DLY2と、加算回路ADD1を備えている。この内、DLY1,DLY2およびVAMP2,VAMP3が波形等化を行うプリドライバ回路PDRVaに該当する。DLY1,DLY2は、それぞれ予め定まった1サイクル分の遅延時間を持つ。DLY1はDRVへの入力信号を遅延させ、DLY2はDLY1の出力信号を遅延させる。VAMP1はDRVへの入力信号を増幅し、VAMP2はDLY1の出力信号を増幅し、VAMP3はDLY2の出力信号を増幅する。ADD1は、VAMP1〜VAMP3の出力信号を加算し、レーザダイオードLDに出力する。ここで、VAMP1〜VAMP3のゲインは、レジスタ回路REGgによって設定可能となっている。

一方、図13(b)のドライバ回路DRVは、図13(a)のデジタル遅延回路DLY1,DLY2がアナログ可変遅延回路VDLY1,VDLY2に置き換わった構成となっている。VDLY1,VDLY2およびVAMP2,VAMP3が波形等化を行うプリドライバ回路PDRVbに該当する。VDLY1,VDLY2は、例えば、複数のインバータ回路等によって実現可能である。VAMP1〜VAMP3のゲインならびにVDLY1,VDLY2の遅延量は、レジスタ回路REGgによって設定可能となっている。波形等化を用いると、時間軸に沿って電流(電圧)波形の形状を細かく調整することができ、例えば、出力波形の立ち上がり・立ち下がりエッジを強調するといったことが可能になる。この際に、図13(a)の構成例では、時間軸に沿って1サイクル単位でしか調整を行えないが、図13(b)の構成例では、時間軸に沿って任意の時間幅で調整を行うことが可能になる。したがって、より波形品質を向上させるためには図13(b)の構成例が好ましいが、回路面積の低減等を図るためには図13(a)の構成例が好ましい。

図14は、図13(a)のドライバ回路の詳細な構成例を示す回路図であり、図15は、図13(b)のドライバ回路の詳細な構成例を示す回路図である。図14において、可変増幅回路VAMP1は、前述した図12(c)とほぼ同様の回路構成であり、差動対となるNMOSトランジスタMNd1,MNd2、カスコード段となるNMOSトランジスタMNc1,MNc2、コモン成分低減用の容量CAP_D1、テール電流源となる電流源INS1、および負荷電流源となる電流源IPSを備えている。ただし、INS1は可変電流源となっており、これによってVAMP1のゲイン(MNd2に流すAC電流Iac)の大きさを制御可能となっている。

一方、プリドライバ回路PDRVaも、VAMP1と同様に、差動対となるNMOSトランジスタMNd3,MNd4、カスコード段となるNMOSトランジスタMNc3,MNc4、コモン成分低減用の容量CAP_D2、テール電流源となる電流源INS2を備え、加えてデジタル遅延回路DLY1を備えている。すなわち、PDRVaは、図13(a)におけるVAMP2とDLY1を備えた構成となっている。このVAMP2の負荷電流源は、VAMP1の電流源IPSと共用化されており、MNc2のドレイン、MNc4のドレイン、およびIPSの一端がDRVの出力ノードに共通接続される。また、MNc1のドレインとMNc3のドレインには、制御電圧VCSが共通に印加される。INS2は可変電流源となっており、これによってVAMP2のゲイン(MNd4に流すAC電流Iac)の大きさを制御可能となっている。

ここで、伝送速度変換回路SDCから入力された差動信号の一方(Vinn)は、VAMP1における差動対の一方(MNd1)に入力されると共に、DLY1を介してVAMP2における差動対の他方(MNd4)に入力される。同様に、SDCから入力された差動信号の他方(Vinp)は、VAMP1における差動対の他方(MNd2)に入力されると共に、DLY1を介してVAMP2における差動対の一方(MNd3)に入力される。したがって、DRVの出力ノードでは、現サイクルに伴うVAMP1による出力電流信号から、一つ前のサイクルに伴うVAMP2による出力電流信号が減算された信号が生成される。例えば、連続する2サイクルのデータが‘H’→‘H’であった場合には、後のサイクルの‘H’レベルが弱められ、‘L’→‘H’であった場合には、後のサイクルの‘H’レベルが強められる。

なお、図14において、前述したVAMP1及びVAMP2のゲインは、レジスタ回路REGgで適宜設定可能となっている。NMc1〜NMc4は、図12(b)と同様に、動作周波数帯域を向上させるために備わっている。また、ここでは、PDRVaとしてVAMP2およびDLY1を備える構成としたが、勿論同様にして、図13(a)のVAMP3およびDLY2を加えることも可能である。一方、図15のドライバ回路DRVでは、図14と比較して、プリドライバ回路PDRVbの構成が異なっており、図14のデジタル遅延回路DLY1の代わりにアナログ可変遅延回路VDLY1を用いた構成となっている。このVDLY1の遅延量は、レジスタ回路REGgで設定可能となっている。

ここで、図3(a)の構成例を参照すると、前述したように、隣接通信チャネル間のクロストークを低減するために、信号線の上下をグラウンドプレーンで挟み、更に、各通信チャネル間にもグラウンド配線を追加したコプレーナ線路を用いることでシールドした構成例となっている。このため、図19のような構成例と異なり、信号線の寄生容量成分の増大に伴い立ち上がり・立ち下がりエッジの鈍化を代表とする波形の歪みが生じる。そこで、図13(a)、(b)に示したような波形等化回路を用いると、この歪みを前もって補正することができ、その結果、各通信チャネル間の相互インダクタンス成分等を低減するための十分なシールド構造が適用可能となる。

以上のように、本実施の形態1の光通信モジュールおよび光通信装置を用いることで、代表的には、通信速度の高速化や、光通信モジュールおよび光通信装置の小型化あるいは低コスト化を実現することが可能となる。

(実施の形態2)

本実施の形態2では、実施の形態1で述べた図6および図7の変形例について説明する。図8は、本発明の実施の形態2による光通信モジュールにおいて、その概略的な構成例を示すブロック図である。図8の構成例は、図6の構成例と比較して、レギュレータ回路が、終端抵抗Rtermに対して直列ではなく並列に接続されている点が異なっている。それ以外の構成に関しては、実施の形態1と同様であるため詳細な説明は省略する。

本実施の形態2では、実施の形態1で述べた図6および図7の変形例について説明する。図8は、本発明の実施の形態2による光通信モジュールにおいて、その概略的な構成例を示すブロック図である。図8の構成例は、図6の構成例と比較して、レギュレータ回路が、終端抵抗Rtermに対して直列ではなく並列に接続されている点が異なっている。それ以外の構成に関しては、実施の形態1と同様であるため詳細な説明は省略する。

図8に示すバイアス回路DC_BIASは、電源電圧VDDとドライバ回路DRVの出力ノードの間に接続された終端抵抗Rtermと、レギュレータ回路IREGを備えている。IREGは、PMOSトランジスタMOSp1,MOSp2、オペアンプ回路AMPr、ダミー回路Dum_cで構成されている。図6の構成例と同様に、Rtermの値は、伝送路TLINEとインピーダンス整合を取るように調整される。MOSp1は、ソースがVDDにドレインがDRVの出力ノードに接続される。Dum_cは、レーザダイオードLDのダミー回路となっており、その入力ノードが、ソースをVDDとするMOSp2のドレインに接続される。

Dum_cの出力ノードは、AMPrの2入力の一方に接続される。AMPrの出力ノードは、MOSp2のゲートに接続され、これによって負帰還ループが形成される。AMPrの出力ノードは、更に、MOSp1のゲートにも接続される。AMPrの2入力の他方には制御電圧Vrefが入力される。これよって、MOSp2とDum_cの関係は、MOSp1とLDの関係のダミーとなる。AMPrの出力ノードには、VDDの変動に依らずDum_cの出力ノード電圧Vs’をVrefに保つと共にDum_cに流れる電流を一定に保つための制御電圧Vconが生成される。このVconは、MOSp1のゲートに印加されるため、MOSp1からはVDDの変動に依らず安定した電流Ib2が生成され、DRVの出力ノード(DRVとTLINE間の信号線)の電圧Vsも安定化する。その結果、電源雑音の影響を受けずにLDへのDCバイアス電流の供給が可能となる。

ここで、LDに供給されるDCバイアス電流は、電源電圧VDDからRtermを介して流れる電流Ib1と、VDDからMOSp1を介して流れる電流Ib2の和となる。この際に、LDDの動作周波数帯域を向上させるにはDRVの出力ノードの寄生容量を低減する必要があるため、MOSp1のゲート幅は小さく設計し、バイアス電流の大半(例えば低温時において必要な電流の70〜80%程度等)がRterm側のIb1から供給される構成とする。一方、電流源として機能するMOSp1は、電流Ib2を介して、残りのバイアス電流を供給すると共に、温度変動を代表とする各種ばらつき変動に伴う補正電流を供給する。

図9は、図8のバイアス回路において、電源変動の影響を抑えるための容量CAP_Rを加えた構成例を示すブロック図である。図9では、図8の構成例に対して、電源電圧VDDとMOSp1のゲートの間に容量CAP_Rが付加されている。CAP_Rのサイズは、低減する電源雑音の周波数帯域に応じて決定し、目標とする周波数帯域までの間の電源変動の影響を低減する。これによって、電圧Vsの変動を低減し、より安定したバイアス電流をLDへ供給することが可能となり、伝送品質をより向上させることが可能となる。ここで、低域の電源雑音成分まで低減する必要がある場合は、CAP_Rのサイズが大きくなり、半導体チップ内の搭載が困難となる可能性があるが、その場合は、CAP_Rを、なるべく半導体チップから近い場所に、半導体チップと別々に実装してもよい。

図10は、図8のバイアス回路DC_BIASにおいて、ダミー回路Dum_cの詳細な回路構成例を示すブロック図である。図10において、Dum_cは、可変抵抗LDeqと、レジスタ回路REGで構成される。LDの簡略的な等価回路は、抵抗とキャパシタを並列に接続したモデルとなるため、LDeqの抵抗値の初期値は、例えばLDの抵抗成分に合わせた数値に設定される。GNDとMOSp2のドレインの間にLDeqを接続することで、LDeqは、LDのダミー回路として機能する。具体的には、LDeqにVrefを印加した際の電流がMOSp2に流れ、MOSp1とMOSp2のサイズ比に応じてMOSp2に流れる電流に比例した電流がMOSp1からIb2としてLDに供給される。ここで、LDeqの抵抗値は、レジスタ回路REGによって初期値から可変設定可能となっている。例えば、LDに製造ばらつきが生じた場合や、あるいは温度に伴う特性変動が生じた場合等で最適なバイアス電流の値も変動し得る。このような場合に、LDeqの抵抗値をREGを介して適宜可変調整することで最適なバイアス電流の値に補正することが可能となる。なお、LDeqについては、可変抵抗に限らず、より高精度なダイオードモデルの等価回路を適用してもよい。

以上、本実施の形態2の光通信モジュールを用いることで、例えば、次のような効果が得られる。終端抵抗(可変抵抗)Rtermを用いて伝送路TLINEとのインピーダンス整合を取ることで、LDDとTLINE間の反射を抑制でき、伝送品質が向上可能になる。LDに供給する必要があるDCバイアス電流の大半を、MOS電流源ではなく、Rtermから供給するため、信号配線上の寄生容量が低減され、高速動作が可能となる。これによって、低クロストーク化が可能な図3に示す実装構造を適用でき、通信チャネルの増加に際して小型化・高密度化が実現可能となる。レギュレータ回路IREGを用いてLDDとTLINE間の電圧Vsを安定化することで、電源雑音の影響が低減され、LDへの安定したDCバイアス電流の供給が可能となる。また、LDの特性がばらついた場合でも、可変抵抗LDeq、Rterm、ならびに制御電圧Vrefを適宜調整することで、ばらつき補償が可能であり、伝送品質を確保できる。

(実施の形態3)

本実施の形態3では、実施の形態2で述べた図10の変形例について説明する。図11は、本発明の実施の形態3による光通信モジュールにおいて、その概略的な構成例を示すブロック図である。図11の構成例は、図10の構成例と異なり、ダミー回路Dum_cが、伝送路TLINEならびにレーザダイオードLD_Dumで構成されたものとなっている。それ以外の構成に関しては、実施の形態2と同様であるため詳細な説明は省略する。図11において、PMOSトランジスタMOSp2のドレインは、TLINEを介してダミー用のレーザダイオードLD_Dumに接続される。ここでは、LDとLD_Dumは、同一チップLD_Array上でアレイ状に集積化されているが、それぞれ別々のチップで実装しても良い。

本実施の形態3では、実施の形態2で述べた図10の変形例について説明する。図11は、本発明の実施の形態3による光通信モジュールにおいて、その概略的な構成例を示すブロック図である。図11の構成例は、図10の構成例と異なり、ダミー回路Dum_cが、伝送路TLINEならびにレーザダイオードLD_Dumで構成されたものとなっている。それ以外の構成に関しては、実施の形態2と同様であるため詳細な説明は省略する。図11において、PMOSトランジスタMOSp2のドレインは、TLINEを介してダミー用のレーザダイオードLD_Dumに接続される。ここでは、LDとLD_Dumは、同一チップLD_Array上でアレイ状に集積化されているが、それぞれ別々のチップで実装しても良い。

LDは、温度変動により、閾値電流及び、緩和振動周波数が変化するため、温度補償を必要とし、温度変化に応じてバイアス電流の値を調整する必要がある。従来の光通信モジュールでは、LDの近くにモニタ用のフォトダイオードを配置し、このフォトダイオードで検出された平均光出力パワーが温度変動によらず常に一定となるようにバイアス電流を負帰還制御することで温度補償を実現していた。しかしながら、このような方法では、モニタ用フォトダイオードの配置により、実装面積を消費してしまうため、光通信モジュールの小型化が困難となり、図1に示したような光通信装置(情報処理装置)への適用が困難となる恐れがある。

そこで、図11の構成例を用いると、LDの近傍にダミー用のLD_Dumを配置し、このLD_Dumの特性をIREGでモニタしながらバイアス電流の制御を行っているため、従来の方式と異なり、モニタ用のフォトダイオードを使用しない温度補償が可能である。これによって、光通信モジュールの小型化が実現可能となる。具体的には、例えば、LD_Dum(LD)の温度が上昇すると、LD_Dumの順方向電圧の低下に伴いMOSp2に流れる電流が増加し、これに比例してMOSp1に流れる電流Ib2が増加する。LDは、一定の光出力パワーを得るためには高温になるほど多くのバイアス電流が必要とされるが、図11の構成例を用いることでこのような温度補償を実現できる。

この際に、特に、LDとLD_Dumを同一チップで形成した場合、LDの製造ばらつきや温度ばらつきに伴う特性変動がLD_Dumにも同様に生じるため、高精度なばらつき補償が行える。また、実施の形態2と同様に、インピーダンス整合による反射の低減と、電源雑音の影響が少ない安定したバイアス電流の供給が可能となり、高速動作の実現と、伝送品質の確保が可能となる。これによって、低クロストーク化が可能な図3に示す実装構造が適用でき、光通信モジュールにおける通信チャネルの増加に際し小型化・高密度化が実現可能となる。

(実施の形態4)

本実施の形態4では、実施の形態1で述べた図6、および実施の形態2で述べた図8の変形例について説明する。図16(a)、(b)は、本発明の実施の形態4による光通信モジュールにおいて、その概略的な構成例を示すそれぞれ異なるブロック図である。図16(a)は、図6の構成例に対してインダクタINDを追加した構成例となっており、図16(b)は、図8の構成例に対してインダクタINDを追加した構成例となっている。図16(a)では、PMOSトランジスタMOSpのドレインと、終端抵抗Rtermの間にINDが接続され、図16(b)では、Rtermと電源電圧VDDの間にINDが接続されている。

本実施の形態4では、実施の形態1で述べた図6、および実施の形態2で述べた図8の変形例について説明する。図16(a)、(b)は、本発明の実施の形態4による光通信モジュールにおいて、その概略的な構成例を示すそれぞれ異なるブロック図である。図16(a)は、図6の構成例に対してインダクタINDを追加した構成例となっており、図16(b)は、図8の構成例に対してインダクタINDを追加した構成例となっている。図16(a)では、PMOSトランジスタMOSpのドレインと、終端抵抗Rtermの間にINDが接続され、図16(b)では、Rtermと電源電圧VDDの間にINDが接続されている。

これらの構成例を用いると、ドライバ回路DRVの出力容量とINDによって形成される並列共振回路により、高周波数帯域におけるゲインにピーキング特性を持たせ、DRVの周波数帯域を延ばすことが可能となる。これによって、光通信モジュールの更なる高速化が図れる。また、実施の形態2と同様に、インピーダンス整合による反射の低減と、電源雑音の影響が少ない安定したバイアス電流の供給が可能となり、高速動作の実現と、伝送品質の確保が可能である。これによって、低クロストーク化が可能な図3に示す構造の光通信モジュールが適用可能となり、多チャネル化による光通信モジュールならびに光通信装置の小型化・高密度化が可能である。

(実施の形態5)

本実施の形態5では、実施の形態1で述べた図6及び、実施の形態2で述べた図8を拡張した構成例について説明する。図17および図18のそれぞれは、本発明の実施の形態5による光通信モジュールにおいて、その概略的な構成例を示すブロック図である。図17は、図6を拡張した構成例を示し、図18は、図8を拡張した構成例を示す。図17および図18の構成例では、レーザダイオードドライバLDDを、多チャネル(CH1〜CHn)化し、バイアス回路DC_BIASを全チャネルで、共有化する構成となっている。各チャネル毎の伝送路TLINEとLDのばらつきに伴うチャネル間のばらつきは、終端抵抗Rt_1〜Rt_nの値を適宜調整することで補償することができる。

本実施の形態5では、実施の形態1で述べた図6及び、実施の形態2で述べた図8を拡張した構成例について説明する。図17および図18のそれぞれは、本発明の実施の形態5による光通信モジュールにおいて、その概略的な構成例を示すブロック図である。図17は、図6を拡張した構成例を示し、図18は、図8を拡張した構成例を示す。図17および図18の構成例では、レーザダイオードドライバLDDを、多チャネル(CH1〜CHn)化し、バイアス回路DC_BIASを全チャネルで、共有化する構成となっている。各チャネル毎の伝送路TLINEとLDのばらつきに伴うチャネル間のばらつきは、終端抵抗Rt_1〜Rt_nの値を適宜調整することで補償することができる。

このように、図17および図18の構成例を用いると、バイアス回路DC_BIASを共有することにより、多チャネル化による通信容量の拡大を小面積で実現可能になる。図示はしないが、特に、図7や図9の構成例のように、DC_BIAS内に電源雑音低減用の比較的サイズが大きい容量CAP_Rを付加する場合には、バイアス回路を共有することが小型化の点で有益となる。また、本実施の形態5においても、実施の形態1、2と同様に、インピーダンス整合による反射の低減と、電源雑音の影響が少ない安定したバイアス電流の供給が可能となり、高速動作の実現と、伝送品質の確保が可能である。これによって、低クロストーク化が可能な図3に示す構造の光通信モジュールが適用可能となり、多チャネル化と併せて光通信モジュールならびに光通信装置の小型化・高密度化が実現できる。

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能である。

例えば、図11等の光通信モジュールで用いるレーザダイオードLDは、特に限定はされないが、端面発光レーザ(Edge Emitting Laser)等を用いることができる。端面発光レーザは、ビクセル(VCSEL:Vertical Cavity Surface Emitting Laser)等を代表とする面発光レーザと比較して、高温時における高速動作の点で有利な場合がある。ただし、この場合、温度変動に伴いバイアス電流を補正することが前提となるが、その手段として、例えば光出力パワー検出用のフォトダイオード等を設けると、十分な小型化が図れない恐れがある。そこで、例えば、図11に示したような方式を用いると、小型な構成で温度補正が実現可能になる。

本実施の形態による光通信モジュールおよび光通信装置は、特に、装置内で光ファイバケーブルを介した通信を行う光通信モジュールおよび光通信装置に適用して有益なものであり、これに限らず、レーザダイオードを用いて光通信を行う製品全般に対して広く適用可能である。

ADD 加算回路

AFE アナログフロントエンドブロック

AMP アンプ回路

BD 配線基板

BIAS,DC_BIAS バイアス回路

BKP バックプレーン

BP バンプ

CAP 容量

CN,CNT コネクタ

CSE 筐体

DLY 遅延回路

DRV ドライバ回路

Dum_c ダミー回路

IFC インタフェースカード

IND インダクタ

IPS,INS 電流源

ISL 絶縁層

LD レーザダイオード

LDD レーザダイオードドライバ

LN 内層配線

LSI_LG 論理デバイス

LSI_OP 光制御チップ

MOSn,MN NMOSトランジスタ

MOSp PMOSトランジスタ

OBK 光素子ブロック

OF 光通信線路

OMD 光通信モジュール

OP 光素子

PD フォトダイオード

PDRV プリドライバ回路

R 抵抗

REG レジスタ回路

SDC 伝送速度変換回路

SWC スイッチカード

TERM 終端部

TIA トランスインピーダンスアンプ回路

TLINE 伝送路

VAMP 可変増幅回路

VDLY 可変遅延回路

VREG,IREG レギュレータ回路

WB ボンディングワイヤ

AFE アナログフロントエンドブロック

AMP アンプ回路

BD 配線基板

BIAS,DC_BIAS バイアス回路

BKP バックプレーン

BP バンプ

CAP 容量

CN,CNT コネクタ

CSE 筐体

DLY 遅延回路

DRV ドライバ回路

Dum_c ダミー回路

IFC インタフェースカード

IND インダクタ

IPS,INS 電流源

ISL 絶縁層

LD レーザダイオード

LDD レーザダイオードドライバ

LN 内層配線

LSI_LG 論理デバイス

LSI_OP 光制御チップ

MOSn,MN NMOSトランジスタ

MOSp PMOSトランジスタ

OBK 光素子ブロック

OF 光通信線路

OMD 光通信モジュール

OP 光素子

PD フォトダイオード

PDRV プリドライバ回路

R 抵抗

REG レジスタ回路

SDC 伝送速度変換回路

SWC スイッチカード

TERM 終端部

TIA トランスインピーダンスアンプ回路

TLINE 伝送路

VAMP 可変増幅回路

VDLY 可変遅延回路

VREG,IREG レギュレータ回路

WB ボンディングワイヤ

Claims (19)

- 第1配線と、

前記第1配線の一端に結合された第1レーザダイオードと、

前記第1配線の他端に結合され、前記第1配線を介して前記第1レーザダイオードに第1バイアス電流を供給すると共に前記第1配線と前記第1レーザダイオードのインピーダンス不整合に伴う反射を終端するバイアス回路と、

前記第1配線の他端に結合され、前記第1バイアス電流に対して第1入力論理レベルに応じた変調電流を合成することで前記第1レーザダイオードを高光出力パワーと低光出力パワーで遷移させながら発光させる第1ドライバ回路とを備え、

前記バイアス回路は、

一端が前記第1配線の他端に結合された第1抵抗と、

第1電源電圧と基準電圧が供給され、前記第1電源電圧を前記基準電圧の大きさに応じて降圧した第2電源電圧を前記第1抵抗の他端に供給するレギュレータ回路とを有することを特徴とする光通信モジュール。 - 請求項1記載の光通信モジュールにおいて、

前記レギュレータ回路は、

前記第1電源電圧と前記第1抵抗の他端の間にソース・ドレイン経路が形成されたMISFETと、

前記基準電圧と前記第1抵抗の他端の電圧が入力され、出力ノードが前記MISFETのゲートに結合された差動アンプ回路とを有することを特徴とする光通信モジュール。 - 請求項1記載の光通信モジュールにおいて、

前記第1レーザダイオードは、第1半導体チップ上に形成され、

前記バイアス回路および前記第1ドライバ回路は、第2半導体チップ上に形成され、

前記第1半導体チップと前記第2半導体チップは、配線層と絶縁層が積層された配線基板上に実装され、

前記第1配線は、前記配線基板における前記配線層によって実現されることを特徴とする光通信モジュール。 - 請求項1記載の光通信モジュールにおいて、

前記第1ドライバ回路は、

入力信号を増幅する第1アンプ回路と、

前記入力信号を遅延される遅延回路と、

前記遅延回路の出力信号を増幅する第2アンプ回路と、

前記第1アンプ回路と前記第2アンプ回路の出力を合成する合成回路と、

前記第1および第2アンプ回路のゲインをそれぞれ設定するレジスタ回路とを有することを特徴とする光通信モジュール。 - 請求項1記載の光通信モジュールにおいて、さらに、

第2配線と、

前記第2配線の一端に結合された第2レーザダイオードと、

前記第2配線の他端に結合された第2ドライバ回路とを備え、

前記バイアス回路は、更に、一端が前記第2配線の他端に結合され、他端に前記第2電源電圧が供給された第2抵抗を備え、前記第2配線を介して前記第2レーザダイオードに第2バイアス電流を供給すると共に前記第2配線と前記第2レーザダイオードのインピーダンス不整合に伴う反射を終端し、

前記第2ドライバ回路は、前記第2バイアス電流に対して第2入力論理レベルに応じた変調電流を合成することで前記第2レーザダイオードを高光出力パワーと低光出力パワーで遷移させながら発光させることを特徴とする光通信モジュール。 - 請求項5記載の光通信モジュールにおいて、

前記第1および第2レーザダイオードは、第1半導体チップ上に形成され、

前記バイアス回路および前記第1および第2ドライバ回路は、第2半導体チップ上に形成され、

前記第1半導体チップと前記第2半導体チップは、配線層と絶縁層が積層された配線基板上に実装され、

前記第1および第2配線は、前記配線基板における前記配線層によって実現されることを特徴とする光通信モジュール。 - 請求項1記載の光通信モジュールにおいて、

前記バイアス回路は、更に、前記第1抵抗の他端と接地電源電圧の間に結合された容量を有することを特徴とする光通信モジュール。 - 請求項1記載の光通信モジュールにおいて、

前記バイアス回路は、更に、第1インダクタを備え、

前記レギュレータ回路は、前記第2電源電圧を前記第1インダクタを介して前記第1抵抗の他端に供給することを特徴とする光通信モジュール。 - 第1配線と、

前記第1配線の一端に結合された第1レーザダイオードと、

前記第1配線の他端に結合され、前記第1配線を介して前記第1レーザダイオードに第1バイアス電流を供給すると共に前記第1配線と前記第1レーザダイオードのインピーダンス不整合に伴う反射を終端するバイアス回路と、

前記第1配線の他端に結合され、前記第1バイアス電流に対して第1入力論理レベルに応じた変調電流を合成することで前記第1レーザダイオードを高光出力パワーと低光出力パワーで遷移させながら発光させる第1ドライバ回路とを備え、

前記バイアス回路は、

前記第1配線の他端と第1電源電圧の間に結合され、前記第1バイアス電流の一部を生成する第1抵抗と、

前記第1配線の他端と前記第1電源電圧の間にソース・ドレイン経路が形成され、前記第1バイアス電流の他の一部を生成する第1MISFETと、

前記第1MISFETのゲート電圧を制御する制御回路とを有することを特徴とする光通信モジュール。 - 請求項9記載の光通信モジュールにおいて、

前記第1レーザダイオードは、第1半導体チップ上に形成され、

前記バイアス回路および前記第1ドライバ回路は、第2半導体チップ上に形成され、

前記第1半導体チップと前記第2半導体チップは、配線層と絶縁層が積層された配線基板上に実装され、

前記第1配線は、前記配線基板における前記配線層によって実現されることを特徴とする光通信モジュール。 - 請求項9記載の光通信モジュールにおいて、

前記制御回路は、

ゲートが前記第1MISFETのゲートと共通に接続され、前記第1MISFETのゲート・ソース間電圧と同一のゲート・ソース間電圧が印加される第2MISFETと、

前記第2MISFETのソース・ドレイン間電流が供給され、当該電流に応じた電圧を生成するダミー回路と、

前記ダミー回路によって生成された電圧と基準電圧が入力され、出力ノードが前記第1および第2MISFETのゲートに結合された差動アンプ回路とを有することを特徴とする光通信モジュール。 - 請求項11記載の光通信モジュールにおいて、

前記ダミー回路は、

前記第2MISFETのソース・ドレイン間電流が供給され、可変抵抗であるダミー用抵抗と、

前記ダミー用抵抗の抵抗値を定める第1レジスタ回路とを有することを特徴とする光通信モジュール。 - 請求項11記載の光通信モジュールにおいて、

前記ダミー回路は、

ダミー用レーザダイオードと、

前記第2MISFETのソース・ドレイン間電流を前記ダミー用レーザダイオードに伝送するダミー用配線とを有することを特徴とする光通信モジュール。 - 請求項13記載の光通信モジュールにおいて、

前記第1レーザダイオードおよび前記ダミー用レーザダイオードは、第1半導体チップ上に形成され、

前記バイアス回路および前記第1ドライバ回路は、第2半導体チップ上に形成され、

前記第1半導体チップと前記第2半導体チップは、配線層と絶縁層が積層された配線基板上に実装され、

前記第1配線および前記ダミー用配線は、前記配線基板における前記配線層によって実現されることを特徴とする光通信モジュール。 - 請求項9記載の光通信モジュールにおいて、さらに、

第2配線と、

前記第2配線の一端に結合された第2レーザダイオードと、

前記第2配線の他端に結合された第2ドライバ回路とを備え、

前記バイアス回路は、更に、前記第2配線の他端と前記第1電源電圧の間に結合された第2抵抗を備え、前記第1MISFETの経路と前記第2抵抗の経路によって生成した第2バイアス電流を前記第2配線を介して前記第2レーザダイオードに供給すると共に前記第2配線と前記第2レーザダイオードのインピーダンス不整合に伴う反射を終端し、

前記第2ドライバ回路は、前記第2バイアス電流に対して第2入力論理レベルに応じた変調電流を合成することで前記第2レーザダイオードを高光出力パワーと低光出力パワーで遷移させながら発光させることを特徴とする光通信モジュール。 - 請求項9記載の光通信モジュールにおいて、

前記バイアス回路は、更に、前記第1電源電圧と前記第1MISFETのゲートの間に結合された容量を有することを特徴とする光通信モジュール。 - 第1A光通信コネクタと、第1光通信モジュールとが搭載された第1配線カードと、

第2A光通信コネクタと、第2光通信モジュールとが搭載された第2配線カードと、

前記第1A光通信コネクタと前記第2A光通信コネクタの間に接続され、数メートル以下の配線長を持つ第1光ファイバケーブルとを備え、

前記第1光通信モジュールは、前記第1A光通信コネクタに第1光信号を送信する第1レーザダイオードが形成された第1A半導体チップと、第1ドライバ回路およびバイアス回路が形成された第1B半導体チップと、前記第1A半導体チップと前記第1B半導体チップが実装され、前記第1A半導体チップと前記第1B半導体チップを接続する第1配線を含んだ配線基板とを備え、

前記第2光通信モジュールは、前記第2A光通信コネクタから受信した前記第1光信号を電流信号に変換する第1フォトダイオードが形成された第2A半導体チップと、当該電流信号を増幅ならびに電圧信号に変換する第1トランスインピーダンスアンプ回路が形成された第2B半導体チップとを備え、

前記第1ドライバ回路は、第1入力論理レベルに応じた変調電流を生成し、第1バイアス電流に対して前記変調電流を合成することで前記第1配線を介して接続された前記第1レーザダイオードを高光出力パワーと低光出力パワーで遷移させながら発光させ、

前記バイアス回路は、前記第1バイアス電流の一部または全てを生成すると共に前記第1配線と前記第1レーザダイオードのインピーダンス不整合に伴う反射を終端する第1抵抗を備えることを特徴とする光通信装置。 - 請求項17記載の光通信装置において、

前記バイアス回路は、前記第1抵抗に加えてレギュレータ回路を備え、

前記第1抵抗は、一端が前記第1配線に結合され、

前記レギュレータ回路は、第1電源電圧と基準電圧が供給され、前記第1電源電圧を前記基準電圧の大きさに応じて降圧した第2電源電圧を前記第1抵抗の他端に供給することを特徴とする光通信装置。 - 請求項17記載の光通信装置において、

前記バイアス回路は、前記第1抵抗に加えて第1MISFETおよび制御回路を備え、

前記第1抵抗は、前記第1配線と第1電源電圧の間に結合され、

前記第1MISFETは、前記第1配線と前記第1電源電圧の間にソース・ドレイン経路が形成され、

前記制御回路は、前記第1MISFETのゲート電圧を制御することを特徴とする光通信装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010232590A JP2012089564A (ja) | 2010-10-15 | 2010-10-15 | 光通信モジュールおよび光通信装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010232590A JP2012089564A (ja) | 2010-10-15 | 2010-10-15 | 光通信モジュールおよび光通信装置 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2012089564A true JP2012089564A (ja) | 2012-05-10 |

Family

ID=46260906

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010232590A Pending JP2012089564A (ja) | 2010-10-15 | 2010-10-15 | 光通信モジュールおよび光通信装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2012089564A (ja) |

Cited By (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014116785A (ja) * | 2012-12-10 | 2014-06-26 | Fujitsu Ltd | 合成回路及びこれを用いた駆動装置 |

| JP2016519436A (ja) * | 2013-04-22 | 2016-06-30 | トリルミナ コーポレーション | 高周波動作のための光電子装置のマルチビームアレイ用マイクロレンズ |

| US9905995B2 (en) * | 2015-09-01 | 2018-02-27 | Integrated Device Technology, Inc. | Adjustable termination circuit for high speed laser driver |

| US10038304B2 (en) | 2009-02-17 | 2018-07-31 | Trilumina Corp. | Laser arrays for variable optical properties |

| US10244181B2 (en) | 2009-02-17 | 2019-03-26 | Trilumina Corp. | Compact multi-zone infrared laser illuminator |

| GB2572604A (en) * | 2018-04-05 | 2019-10-09 | M Squared Lasers Ltd | Laser diode drive system |

| US10615871B2 (en) | 2009-02-17 | 2020-04-07 | Trilumina Corp. | High speed free-space optical communications |

| WO2021065163A1 (ja) * | 2019-09-30 | 2021-04-08 | ソニーセミコンダクタソリューションズ株式会社 | 半導体レーザ駆動装置、電子機器、および、半導体レーザ駆動装置の製造方法 |

| US11095365B2 (en) | 2011-08-26 | 2021-08-17 | Lumentum Operations Llc | Wide-angle illuminator module |

| CN113281853A (zh) * | 2020-02-19 | 2021-08-20 | 青岛海信宽带多媒体技术有限公司 | 一种光模块 |

| CN113835536A (zh) * | 2021-09-26 | 2021-12-24 | 四川写正智能科技有限公司 | 正确读写的坐标标定方法及智能电话手表 |

| CN117452059A (zh) * | 2023-12-25 | 2024-01-26 | 成都光创联科技有限公司 | 光器件多通道背光探测器的测试电路和方法 |

-

2010

- 2010-10-15 JP JP2010232590A patent/JP2012089564A/ja active Pending

Cited By (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11405105B2 (en) | 2009-02-17 | 2022-08-02 | Lumentum Operations Llc | System for optical free-space transmission of a string of binary data |

| US11121770B2 (en) | 2009-02-17 | 2021-09-14 | Lumentum Operations Llc | Optical laser device |

| US10038304B2 (en) | 2009-02-17 | 2018-07-31 | Trilumina Corp. | Laser arrays for variable optical properties |

| US10244181B2 (en) | 2009-02-17 | 2019-03-26 | Trilumina Corp. | Compact multi-zone infrared laser illuminator |

| US10615871B2 (en) | 2009-02-17 | 2020-04-07 | Trilumina Corp. | High speed free-space optical communications |

| US11075695B2 (en) | 2009-02-17 | 2021-07-27 | Lumentum Operations Llc | Eye-safe optical laser system |

| US10938476B2 (en) | 2009-02-17 | 2021-03-02 | Lumentum Operations Llc | System for optical free-space transmission of a string of binary data |

| US11451013B2 (en) | 2011-08-26 | 2022-09-20 | Lumentum Operations Llc | Wide-angle illuminator module |

| US11095365B2 (en) | 2011-08-26 | 2021-08-17 | Lumentum Operations Llc | Wide-angle illuminator module |

| JP2014116785A (ja) * | 2012-12-10 | 2014-06-26 | Fujitsu Ltd | 合成回路及びこれを用いた駆動装置 |

| JP2016519436A (ja) * | 2013-04-22 | 2016-06-30 | トリルミナ コーポレーション | 高周波動作のための光電子装置のマルチビームアレイ用マイクロレンズ |

| US9905995B2 (en) * | 2015-09-01 | 2018-02-27 | Integrated Device Technology, Inc. | Adjustable termination circuit for high speed laser driver |

| GB2572604A (en) * | 2018-04-05 | 2019-10-09 | M Squared Lasers Ltd | Laser diode drive system |

| GB2572604B (en) * | 2018-04-05 | 2020-12-16 | M Squared Lasers Ltd | Laser Diode Driver |

| US11605931B2 (en) | 2018-04-05 | 2023-03-14 | M Squared Lasers Limited | Laser diode drive system |

| WO2021065163A1 (ja) * | 2019-09-30 | 2021-04-08 | ソニーセミコンダクタソリューションズ株式会社 | 半導体レーザ駆動装置、電子機器、および、半導体レーザ駆動装置の製造方法 |

| CN113281853A (zh) * | 2020-02-19 | 2021-08-20 | 青岛海信宽带多媒体技术有限公司 | 一种光模块 |

| CN113835536A (zh) * | 2021-09-26 | 2021-12-24 | 四川写正智能科技有限公司 | 正确读写的坐标标定方法及智能电话手表 |

| CN117452059A (zh) * | 2023-12-25 | 2024-01-26 | 成都光创联科技有限公司 | 光器件多通道背光探测器的测试电路和方法 |

| CN117452059B (zh) * | 2023-12-25 | 2024-02-27 | 成都光创联科技有限公司 | 光器件多通道背光探测器的测试电路和方法 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2012089564A (ja) | 光通信モジュールおよび光通信装置 | |

| JP6334183B2 (ja) | 光伝送回路 | |

| US6941080B2 (en) | Method and apparatus for directly modulating a laser diode using multi-stage driver circuitry | |

| US7734184B2 (en) | Optical transceiver module having an active linear optoelectronic device | |

| US7400791B2 (en) | Semiconductor element mounting board and optical transmission module | |

| KR100396724B1 (ko) | 발광다이오드 구동회로 및 광송신모듈 | |

| US8503888B2 (en) | Optical communication module and optical communication device | |

| US8385752B2 (en) | Laser diode driver with back terminator and optical transmitter providing the same | |

| US7457336B2 (en) | Laser diode drive circuit | |

| US9172473B2 (en) | Active linear amplifier inside transmitter module | |

| US7646988B2 (en) | Linear amplifier for use with laser driver signal | |

| US20080074196A1 (en) | Emi reduction stage in a post-amplifier | |

| JP2016021458A (ja) | 駆動回路及びそれを含む光通信装置 | |

| US11063669B2 (en) | Dual-rate DML device and module having built-in signal calibration circuit, and signal calibration method | |

| US7580434B2 (en) | Dual laser driver architecture in an optical transceiver | |

| US8508396B2 (en) | Signal processing device, signal processing method, reception device, transmission/reception device, communication module, and electronic device | |

| WO2016194091A1 (ja) | 光通信モジュールおよびそれを備える光通信装置 | |

| US9148960B2 (en) | Receiver optical assemblies (ROAs) having photo-detector remotely located from transimpedance amplifier, and related components, circuits, and methods | |

| US8912827B2 (en) | Driver circuit | |

| US20060203863A1 (en) | Optical transmitter with a least pair of semiconductor laser diodes | |

| US7860407B2 (en) | Pre-emphasis circuit | |

| Miao et al. | A 120Gbps VCSEL-Based Parallel Optical Module Design | |

| US20240007069A1 (en) | Hybrid distributed driver | |

| JP2023125053A (ja) | 出力インピーダンス可変ドライバ回路、レーザドライバ回路およびcpoモジュール | |

| JP2010267799A (ja) | 直流結合レーザー駆動回路 |