JP2011524471A - 均一蒸着のための装置及び方法 - Google Patents

均一蒸着のための装置及び方法 Download PDFInfo

- Publication number

- JP2011524471A JP2011524471A JP2011514713A JP2011514713A JP2011524471A JP 2011524471 A JP2011524471 A JP 2011524471A JP 2011514713 A JP2011514713 A JP 2011514713A JP 2011514713 A JP2011514713 A JP 2011514713A JP 2011524471 A JP2011524471 A JP 2011524471A

- Authority

- JP

- Japan

- Prior art keywords

- collimator

- chamber

- substrate support

- aspect ratio

- sputtering target

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C14/00—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material

- C23C14/22—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material characterised by the process of coating

- C23C14/34—Sputtering

- C23C14/35—Sputtering by application of a magnetic field, e.g. magnetron sputtering

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C14/00—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material

- C23C14/04—Coating on selected surface areas, e.g. using masks

- C23C14/046—Coating cavities or hollow spaces, e.g. interior of tubes; Infiltration of porous substrates

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C14/00—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material

- C23C14/22—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material characterised by the process of coating

- C23C14/34—Sputtering

- C23C14/3407—Cathode assembly for sputtering apparatus, e.g. Target

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C14/00—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material

- C23C14/22—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material characterised by the process of coating

- C23C14/50—Substrate holders

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C14/00—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material

- C23C14/22—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material characterised by the process of coating

- C23C14/56—Apparatus specially adapted for continuous coating; Arrangements for maintaining the vacuum, e.g. vacuum locks

- C23C14/564—Means for minimising impurities in the coating chamber such as dust, moisture, residual gases

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/34—Gas-filled discharge tubes operating with cathodic sputtering

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/34—Gas-filled discharge tubes operating with cathodic sputtering

- H01J37/3411—Constructional aspects of the reactor

- H01J37/3447—Collimators, shutters, apertures

Landscapes

- Chemical & Material Sciences (AREA)

- Engineering & Computer Science (AREA)

- Organic Chemistry (AREA)

- Materials Engineering (AREA)

- Mechanical Engineering (AREA)

- Metallurgy (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Physics & Mathematics (AREA)

- Plasma & Fusion (AREA)

- Analytical Chemistry (AREA)

- Physical Vapour Deposition (AREA)

- Electrodes Of Semiconductors (AREA)

- Physical Deposition Of Substances That Are Components Of Semiconductor Devices (AREA)

Abstract

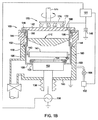

【選択図】図1B

Description

101 システムコントローラ

102 カバーリング

103 リップ

110 コリメータ

111 放射状ブラケット

141 RFコイル

142 ターゲット

143 コイル絶縁体

144 導電性アダプタ

146 誘電絶縁体

148 DC電源

150 チャンバ壁

152 基板支持台

154 基板

156 RF電源

158 蛇腹

160 底部チャンバ壁

162 ガス源

164 質量流コントローラ

170 マグネトロン

172 磁石

174 ベースプレート

176 シャフト

180 下部シールド

182 上部フランジ

184 フランジ

186 上部シールド

188 微小ギャップ

190 先端

196 管状部

198 底部

Claims (15)

- 電気的に接地されたチャンバと、

前記チャンバによって支持されるとともに前記チャンバから電気的に絶縁されたスパッタリングターゲットと、

前記スパッタリングターゲットの下方に位置し、前記スパッタリングターゲットのスパッタ面と実質的に平行な基板支持面を有する基板支持台と、

前記チャンバによって支持されるシールド部材と、

前記シールド部材に機械的及び電気的に結合され、前記スパッタリングターゲットと前記基板支持台との間に位置するコリメータと、

を備え、前記コリメータが、該コリメータを貫いて延びる複数の開口部を有し、中心領域に位置する前記開口部の方が、周辺領域に位置する前記開口部よりも高いアスペクト比を有する、

ことを特徴とする蒸着装置。 - 前記開口部のアスペクト比が、前記中心領域から前記周辺領域にかけて持続的に減少する、

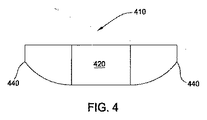

ことを特徴とする請求項1に記載の装置。 - 前記コリメータの厚みが、前記中心領域から前記周辺領域にかけて持続的に減少する、

ことを特徴とする請求項2に記載の装置。 - 前記開口部のアスペクト比が、前記中心領域から前記周辺領域にかけて非直線的に減少する、

ことを特徴とする請求項1に記載の装置。 - 前記コリメータの厚みが、前記中心領域から前記周辺領域にかけて非直線的に減少する、

ことを特徴とする請求項4に記載の装置。 - 前記コリメータが前記シールド部材に、外側にねじ山のある部材と、該外側にねじ山のある部材と係合する内側にねじ山のある部材とを備えたブラケットを介して結合される、

ことを特徴とする請求項1に記載の装置。 - 前記コリメータが前記シールド部材に溶接される、

ことを特徴とする請求項1に記載の装置。 - 前記コリメータが前記シールド部材と一体化される、

ことを特徴とする請求項1に記載の装置。 - 前記コリメータが、アルミニウム、銅及びステンレス鋼から成る群から選択された材料から成る、

ことを特徴とする請求項1に記載の装置。 - 前記コリメータの前記開口部間の壁厚が約0.06インチ〜約0.18インチの間である、

ことを特徴とする請求項1に記載の装置。 - 電気的に接地されたチャンバと、

前記チャンバによって支持され、前記チャンバから電気的に絶縁され、DC電源に電気的に結合されたスパッタリングターゲットと、

前記スパッタリングターゲットの下方に位置し、前記スパッタリングターゲットのスパッタ面に実質的と平行な基板支持面を有する、RF電源に電気的に結合された基板支持台と、

前記チャンバによって支持され、前記チャンバに電気的に結合されたシールド部材と、

前記シールド部材に機械的及び電気的に結合され、前記スパッタリングターゲットと前記基板支持台との間に位置するコリメータと、

を備え、前記コリメータが、該コリメータを貫いて延びる複数の開口部を有し、中心領域に位置する前記開口部の方が、周辺領域に位置する前記開口部よりも高いアスペクト比を有し、

ガス源と、

前記ガス源、DC電源及び前記RF電源を制御するための信号を供給するようにプログラムされるとともに、前記基板支持台に高バイアスを与えるようにプログラムされたコントローラと、

をさらに備えることを特徴とする蒸着装置。 - RFコイルをさらに備え、前記コントローラが、前記基板支持台が高バイアスと低バイアスの間で交互に切り替わるように前記RF電源を制御するための信号を供給するようにプログラムされるとともに、前記RFコイル及び前記ガス源に供給される電力を制御して前記チャンバ内の第2のプラズマを制御するようにプログラムされる、

ことを特徴とする請求項11に記載の装置。 - 前記コリメータの厚みが、前記中心領域から前記周辺領域にかけて持続的に減少する、

ことを特徴とする請求項12に記載の装置。 - 基板上に材料を蒸着させる方法であって、

コリメータを有するチャンバ内のスパッタリングターゲットにDCバイアスを印加するステップを含み、前記コリメータは、前記スパッタリングターゲットと基板支持台との間に位置するとともに、前記コリメータを貫いて延びる複数の開口部を有し、中心領域に位置する前記開口部の方が、周辺領域に位置する前記開口部よりも高いアスペクト比を有し、

前記チャンバ内の前記スパッタリングターゲットに隣接する領域内に加工ガスを供給するステップと、

前記基板支持台にバイアスを印加するステップと、

前記基板支持台に印加した前記バイアスを高バイアスと低バイアスの間でパルスするステップと、

をさらに含むことを特徴とする方法。 - 前記チャンバの内部に位置するRFコイルに電力を印加して前記チャンバの内部に第2のプラズマを供給するステップをさらに含み、前記開口部のアスペクト比が、前記中心領域から前記周辺領域にかけて持続的に減少する、

ことを特徴とする請求項14に記載の方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US7313008P | 2008-06-17 | 2008-06-17 | |

| US61/073,130 | 2008-06-17 | ||

| PCT/US2009/047103 WO2009155208A2 (en) | 2008-06-17 | 2009-06-11 | Apparatus and method for uniform deposition |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011524471A true JP2011524471A (ja) | 2011-09-01 |

| JP2011524471A5 JP2011524471A5 (ja) | 2012-07-26 |

Family

ID=41413769

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011514713A Pending JP2011524471A (ja) | 2008-06-17 | 2009-06-11 | 均一蒸着のための装置及び方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US20090308732A1 (ja) |

| JP (1) | JP2011524471A (ja) |

| KR (8) | KR20160134873A (ja) |

| CN (1) | CN102066603B (ja) |

| WO (1) | WO2009155208A2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20160074666A (ko) * | 2013-10-24 | 2016-06-28 | 어플라이드 머티어리얼스, 인코포레이티드 | 물리 기상 증착 챔버에서 활용되는 바이폴라 콜리메이터 |

Families Citing this family (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101845610B (zh) * | 2010-06-07 | 2011-12-07 | 崔铮 | 一种连续垂直热蒸发的金属镀膜方法 |

| JP5825781B2 (ja) * | 2010-12-17 | 2015-12-02 | キヤノン株式会社 | 反射防止膜形成方法及び反射防止膜形成装置 |

| CN103165375B (zh) * | 2011-12-09 | 2016-06-01 | 中国科学院微电子研究所 | 半导体腔室用压片装置 |

| US9404174B2 (en) | 2011-12-15 | 2016-08-02 | Applied Materials, Inc. | Pinned target design for RF capacitive coupled plasma |

| US8702918B2 (en) | 2011-12-15 | 2014-04-22 | Applied Materials, Inc. | Apparatus for enabling concentricity of plasma dark space |

| US20140061039A1 (en) * | 2012-09-05 | 2014-03-06 | Applied Materials, Inc. | Target cooling for physical vapor deposition (pvd) processing systems |

| US20150122643A1 (en) * | 2013-11-06 | 2015-05-07 | Shenzhen China Star Optoelectronics Technology Co., Ltd. | Supporting member for magnetron sputtering anode bar and magnetron sputtering device including the same |

| CN103602954B (zh) * | 2013-11-06 | 2016-02-24 | 深圳市华星光电技术有限公司 | 用于磁控溅射阳极棒的支撑件及包括其的磁控溅射装置 |

| US9887072B2 (en) * | 2014-01-23 | 2018-02-06 | Taiwan Semiconductor Manufacturing Company, Ltd. | Systems and methods for integrated resputtering in a physical vapor deposition chamber |

| JP2017529239A (ja) * | 2014-07-18 | 2017-10-05 | アプライド マテリアルズ インコーポレイテッドApplied Materials,Incorporated | レーザ及びガス流を用いた付加製造 |

| US9543126B2 (en) * | 2014-11-26 | 2017-01-10 | Applied Materials, Inc. | Collimator for use in substrate processing chambers |

| US9887073B2 (en) | 2015-02-13 | 2018-02-06 | Taiwan Semiconductor Manufacturing Co., Ltd. | Physical vapor deposition system and physical vapor depositing method using the same |

| JP7034912B2 (ja) * | 2015-10-27 | 2022-03-14 | アプライド マテリアルズ インコーポレイテッド | Pvdスパッタチャンバ向けのバイアス可能なフラックスオプティマイザ/コリメータ |

| WO2017155812A1 (en) | 2016-03-05 | 2017-09-14 | Applied Materials, Inc. | Methods and apparatus for controlling ion fraction in physical vapor deposition processes |

| JP6088083B1 (ja) * | 2016-03-14 | 2017-03-01 | 株式会社東芝 | 処理装置及びコリメータ |

| USD859333S1 (en) * | 2018-03-16 | 2019-09-10 | Applied Materials, Inc. | Collimator for a physical vapor deposition chamber |

| USD858468S1 (en) * | 2018-03-16 | 2019-09-03 | Applied Materials, Inc. | Collimator for a physical vapor deposition chamber |

| US11017989B2 (en) | 2018-03-16 | 2021-05-25 | Samsung Electronics Co., Ltd. | Collimator, fabrication apparatus including the same, and method of fabricating a semiconductor device using the same |

| CN110643958A (zh) * | 2019-10-21 | 2020-01-03 | 吴浪生 | 一种利用溅镀实现晶圆的物理镀膜设备 |

| USD937329S1 (en) | 2020-03-23 | 2021-11-30 | Applied Materials, Inc. | Sputter target for a physical vapor deposition chamber |

| USD998575S1 (en) | 2020-04-07 | 2023-09-12 | Applied Materials, Inc. | Collimator for use in a physical vapor deposition (PVD) chamber |

| US20220406583A1 (en) * | 2021-06-18 | 2022-12-22 | Taiwan Semiconductor Manufacturing Co., Ltd. | Deposition system and method |

| USD1009816S1 (en) | 2021-08-29 | 2024-01-02 | Applied Materials, Inc. | Collimator for a physical vapor deposition chamber |

| USD997111S1 (en) | 2021-12-15 | 2023-08-29 | Applied Materials, Inc. | Collimator for use in a physical vapor deposition (PVD) chamber |

| FI20225334A1 (en) * | 2022-04-21 | 2023-10-22 | Biomensio Ltd | Collimator to produce piezoelectric layers having tilted c-axis orientation |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09500690A (ja) * | 1993-07-22 | 1997-01-21 | マティリアルズ リサーチ コーポレイション | 反応スパッタ付着に使用する静止有孔プレート |

| JP2005514777A (ja) * | 2001-12-21 | 2005-05-19 | アプライド マテリアルズ インコーポレイテッド | スパッタリング及び再スパッタリングのための自己イオン化及び誘導性結合プラズマ |

| JP2006500472A (ja) * | 2001-07-25 | 2006-01-05 | アプライド マテリアルズ インコーポレイテッド | 物理的気相堆積システムにおけるアニール方法及び装置 |

| JP2007273490A (ja) * | 2004-03-30 | 2007-10-18 | Renesas Technology Corp | 半導体集積回路装置の製造方法 |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5362372A (en) * | 1993-06-11 | 1994-11-08 | Applied Materials, Inc. | Self cleaning collimator |

| US5380414A (en) * | 1993-06-11 | 1995-01-10 | Applied Materials, Inc. | Shield and collimator pasting deposition chamber with a wafer support periodically used as an acceptor |

| US5431799A (en) * | 1993-10-29 | 1995-07-11 | Applied Materials, Inc. | Collimation hardware with RF bias rings to enhance sputter and/or substrate cavity ion generation efficiency |

| US5650052A (en) * | 1995-10-04 | 1997-07-22 | Edelstein; Sergio | Variable cell size collimator |

| US5985102A (en) * | 1996-01-29 | 1999-11-16 | Micron Technology, Inc. | Kit for electrically isolating collimator of PVD chamber, chamber so modified, and method of using |

| US5658442A (en) * | 1996-03-07 | 1997-08-19 | Applied Materials, Inc. | Target and dark space shield for a physical vapor deposition system |

| JPH10176267A (ja) * | 1996-12-13 | 1998-06-30 | Applied Materials Inc | スパッタ装置 |

| US6692617B1 (en) * | 1997-05-08 | 2004-02-17 | Applied Materials, Inc. | Sustained self-sputtering reactor having an increased density plasma |

| US6482301B1 (en) * | 1998-06-04 | 2002-11-19 | Seagate Technology, Inc. | Target shields for improved magnetic properties of a recording medium |

| US6149776A (en) * | 1998-11-12 | 2000-11-21 | Applied Materials, Inc. | Copper sputtering target |

| KR20000052104A (ko) * | 1999-01-29 | 2000-08-16 | 윤종용 | 스퍼터링 장치의 콜리메이터 구조 및 그 제조방법 |

| US6699375B1 (en) * | 2000-06-29 | 2004-03-02 | Applied Materials, Inc. | Method of extending process kit consumable recycling life |

| US20030015421A1 (en) * | 2001-07-20 | 2003-01-23 | Applied Materials, Inc. | Collimated sputtering of cobalt |

| US7041200B2 (en) * | 2002-04-19 | 2006-05-09 | Applied Materials, Inc. | Reducing particle generation during sputter deposition |

| US7048837B2 (en) * | 2002-09-13 | 2006-05-23 | Applied Materials, Inc. | End point detection for sputtering and resputtering |

| TW200416838A (en) * | 2002-11-20 | 2004-09-01 | Renesas Tech Corp | Method of fabricating semiconductor device |

| US7018515B2 (en) * | 2004-03-24 | 2006-03-28 | Applied Materials, Inc. | Selectable dual position magnetron |

-

2009

- 2009-06-11 KR KR1020167031883A patent/KR20160134873A/ko not_active Application Discontinuation

- 2009-06-11 JP JP2011514713A patent/JP2011524471A/ja active Pending

- 2009-06-11 KR KR1020207021871A patent/KR20200093084A/ko not_active Application Discontinuation

- 2009-06-11 KR KR1020157033650A patent/KR20150137131A/ko not_active Application Discontinuation

- 2009-06-11 WO PCT/US2009/047103 patent/WO2009155208A2/en active Application Filing

- 2009-06-11 US US12/482,713 patent/US20090308732A1/en not_active Abandoned

- 2009-06-11 KR KR1020177023703A patent/KR20170100068A/ko not_active Application Discontinuation

- 2009-06-11 KR KR1020117001222A patent/KR20110020918A/ko not_active Application Discontinuation

- 2009-06-11 CN CN2009801229458A patent/CN102066603B/zh active Active

- 2009-06-11 KR KR1020187004305A patent/KR20180019762A/ko active Search and Examination

- 2009-06-11 KR KR1020197023662A patent/KR20190097315A/ko not_active Application Discontinuation

- 2009-06-11 KR KR1020167034645A patent/KR20160145849A/ko not_active Application Discontinuation

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09500690A (ja) * | 1993-07-22 | 1997-01-21 | マティリアルズ リサーチ コーポレイション | 反応スパッタ付着に使用する静止有孔プレート |

| JP2006500472A (ja) * | 2001-07-25 | 2006-01-05 | アプライド マテリアルズ インコーポレイテッド | 物理的気相堆積システムにおけるアニール方法及び装置 |

| JP2005514777A (ja) * | 2001-12-21 | 2005-05-19 | アプライド マテリアルズ インコーポレイテッド | スパッタリング及び再スパッタリングのための自己イオン化及び誘導性結合プラズマ |

| JP2007273490A (ja) * | 2004-03-30 | 2007-10-18 | Renesas Technology Corp | 半導体集積回路装置の製造方法 |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20160074666A (ko) * | 2013-10-24 | 2016-06-28 | 어플라이드 머티어리얼스, 인코포레이티드 | 물리 기상 증착 챔버에서 활용되는 바이폴라 콜리메이터 |

| JP2016540115A (ja) * | 2013-10-24 | 2016-12-22 | アプライド マテリアルズ インコーポレイテッドApplied Materials,Incorporated | 物理的気相堆積チャンバで利用される双極性コリメータ |

| KR102214958B1 (ko) * | 2013-10-24 | 2021-02-09 | 어플라이드 머티어리얼스, 인코포레이티드 | 물리 기상 증착 챔버에서 활용되는 바이폴라 콜리메이터 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20160145849A (ko) | 2016-12-20 |

| KR20180019762A (ko) | 2018-02-26 |

| KR20110020918A (ko) | 2011-03-03 |

| KR20160134873A (ko) | 2016-11-23 |

| KR20200093084A (ko) | 2020-08-04 |

| CN102066603A (zh) | 2011-05-18 |

| KR20190097315A (ko) | 2019-08-20 |

| KR20170100068A (ko) | 2017-09-01 |

| WO2009155208A2 (en) | 2009-12-23 |

| CN102066603B (zh) | 2013-04-10 |

| US20090308732A1 (en) | 2009-12-17 |

| KR20150137131A (ko) | 2015-12-08 |

| WO2009155208A3 (en) | 2010-03-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2011524471A (ja) | 均一蒸着のための装置及び方法 | |

| TWI761889B (zh) | 用於pvd濺射腔室的可偏壓通量優化器/準直器 | |

| KR102020010B1 (ko) | 웨이퍼 프로세싱 증착 차폐 부품 | |

| US20090308739A1 (en) | Wafer processing deposition shielding components | |

| JP4588212B2 (ja) | 重複端部を有するコイルを備えるスパッタリング装置 | |

| JPH10214799A (ja) | 改良型誘導結合プラズマ源 | |

| CN116752109A (zh) | 物理气相沉积设备、沉积工艺及刻蚀工艺 | |

| JP2021527161A (ja) | 半導体プロセスチャンバ内のマグネトロンアセンブリのための方法および装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120611 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120611 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130823 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130828 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20131128 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20131205 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20140507 |