JP2010142783A - 電圧出力ドライバー - Google Patents

電圧出力ドライバー Download PDFInfo

- Publication number

- JP2010142783A JP2010142783A JP2008325833A JP2008325833A JP2010142783A JP 2010142783 A JP2010142783 A JP 2010142783A JP 2008325833 A JP2008325833 A JP 2008325833A JP 2008325833 A JP2008325833 A JP 2008325833A JP 2010142783 A JP2010142783 A JP 2010142783A

- Authority

- JP

- Japan

- Prior art keywords

- drive

- signal

- power supply

- waveform

- output

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000003990 capacitor Substances 0.000 description 9

- 101710129178 Outer plastidial membrane protein porin Proteins 0.000 description 8

- 102100037820 Voltage-dependent anion-selective channel protein 1 Human genes 0.000 description 8

- 102100031476 Cytochrome P450 1A1 Human genes 0.000 description 3

- 101000941690 Homo sapiens Cytochrome P450 1A1 Proteins 0.000 description 3

- 238000001816 cooling Methods 0.000 description 3

- 239000012530 fluid Substances 0.000 description 3

- 102100026533 Cytochrome P450 1A2 Human genes 0.000 description 2

- 101000855342 Homo sapiens Cytochrome P450 1A2 Proteins 0.000 description 2

- 230000000295 complement effect Effects 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 230000003321 amplification Effects 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 description 1

- 238000003199 nucleic acid amplification method Methods 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

Images

Landscapes

- Reciprocating Pumps (AREA)

- Apparatuses For Generation Of Mechanical Vibrations (AREA)

- General Electrical Machinery Utilizing Piezoelectricity, Electrostriction Or Magnetostriction (AREA)

Abstract

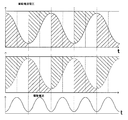

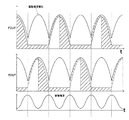

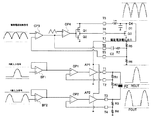

【解決手段】昇圧回路Lvs,Q3,D1は、低電圧の信号電源を昇圧して、圧電素子の駆動制御信号に応じて決定された高電圧の駆動電源を発生する。駆動波発生手段が前記信号電源を電源として、前記駆動制御信号に応じた振幅を有する圧電素子の駆動波形を発生し、アンプAP1、AP2が駆動波形を増幅し、前記駆動制御信号に応じた振幅であって、圧電素子を駆動する駆動信号を得る。駆動波形発生手段において、駆動波形として、サイン波形の一方側に膨らむ部分をカットして他方側に膨らむ部分のみを残した波形(半波波形)を発生し、これをアンプAP1、AP2に入力することで、圧電素子PZを半波駆動する。

【選択図】図15

Description

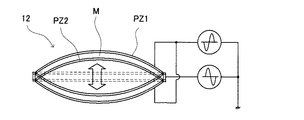

圧電素子を利用したダイヤフラムポンプ(圧電ポンプ)の構成について、図1を用いて説明する。ポンプケーシング10内には、周囲がポンプケーシング10内壁に固定され、中央側が上下動するダイヤフラム12が配置され、このダイヤフラム12の一方側にポンプ室14が形成される。ポンプ室14には、流入通路16に接続される流入口18と、流出通路20に接続される流出口22が設けられ、流入通路16と流入口18の間には流入側の逆止弁24,流出通路20と流出口22の間には流出側の逆止弁26が設けられている。

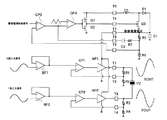

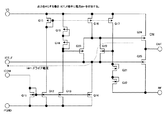

図3には、圧電素子PZへの駆動信号を出力する駆動信号出力回路の構成が示されている。1つの駆動波形(サイン波状の交流波形)であるR側入力信号は、バッファアンプBF1の正入力端に入力される。このバッファアンプBF1は、その出力が負入力端に接続されており、R側入力信号がそのままの波形で出力される。バッファアンプBF1の出力はコンパレータ(エラーアンプ)CP1の正入力端に入力される。このコンパレータCP1の負入力端には、帰還信号が入力されており、両信号の誤差信号がコンパレータCP1の出力に得られる。得られた誤差信号は、高電源電圧で駆動される出力アンプAP1に供給され、この出力アンプAP1の出力が出力端T1に供給される。出力端T1には、圧電素子PZの一方側の電極が接続されているとともに、分圧抵抗R1,R2を介しグランドに接続されている。分圧抵抗R1,R2の中点は、端子T2を介し、コンパレータCP1の負入力端に接続され、出力電圧が分圧された電圧がコンパレータCP1に負帰還される。

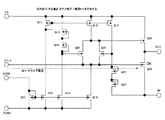

図5、図6には、出力アンプAPの構成例が示されている。ICOMからは定電流が供給され、これがnチャネルトランジスタQ11のドレインおよびゲートに供給される。トランジスタQ11のソースはグランド(PGND)に接続されている。トランジスタQ11のゲートには、ソースがグランド(PGND)に接続されたnチャネルトランジスタQ12,Q13,Q14のゲートが共通接続されている。従って、トランジスタQ11に対し、トランジスタQ12,Q13,Q14がカレントミラーを構成し、これらトランジスタQ11〜Q14に同一の定電流が流れる。

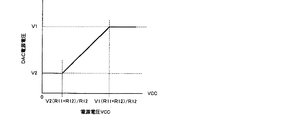

従来の装置において、ファン駆動制御用にファンの駆動を制御する制御電源電圧である電源電圧VCCを出力できる回路がすでに用意されている場合がある。この場合には、この電源電圧VCCに応じて、圧電素子PZを制御する信号を発生することが好適である。

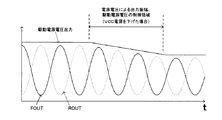

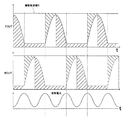

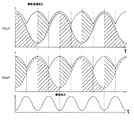

このように、本実施形態では、電源電圧VCCに応じて駆動電源制御信号を発生し、昇圧を制御している。ここで、駆動電源電圧は、駆動信号ROUT、FOUTより大きい必要があるが、一定である必要はない。特に、駆動電源電圧が一定であると、図10に示すように、駆動信号との差が大きいときには、その差分をアンプAP1,AP2の上側トランジスタが受け持つことにあり、ここにおける電力消費が大きくなる等問題がある。図10における右下がり斜線領域が、上側トランジスタが消費する領域である。なお、図における右上がりの斜線で示す領域は、下側トランジスタが受け持つ領域である。

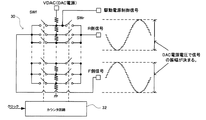

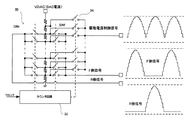

図14には、VCCに連動するA/Dコンバータ30を利用して半波波形のR側信号およびF側信号、およびそれに対応した駆動電源制御信号を形成する構成を示してある。この例では、カウンタ回路32のカウント値に応じて、スイッチSWr,SWfが制御され、カウント値の上昇、下降に応じて、R側信号およびF側信号の山が交互に作成され、一方側信号の山が形成されている場合には、他側信号は最低レベルを維持している。このようなスイッチSWr、SWfの制御によって、図示のような半波のR側信号、F側信号を得られる。

Claims (2)

- 容量性負荷を駆動する電圧出力ドライバーであって、

信号電源に基づいて、容量性負荷の駆動制御信号に応じて決定された電圧の駆動電源を発生する電源回路と、

前記信号電源を電源として、前記駆動制御信号に応じた振幅を有する容量性負荷の駆動波形であって、位相が互いに180度ずれた一対の駆動波形を発生する駆動波形発生手段と、

前記駆動電源を電源として、前記駆動波形を増幅し、前記駆動制御信号に応じた振幅であって、容量性負荷を駆動する駆動信号を得る増幅回路と、

を有し、

前記駆動波形発生手段は、駆動波形として、サイン波形の一方側に膨らむ部分をカットして他方側に膨らむ部分のみを残した波形として発生することを特徴とする電圧出力ドライバー。 - 請求項1に記載の電圧出力ドライバーにおいて、

駆動電源制御信号を一対の駆動波形に対し所定値だけ高い波形として、前記駆動電源電圧を駆動信号に対し所定値高いものに制御することを特徴とする電圧出力ドライバー。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008325833A JP2010142783A (ja) | 2008-12-22 | 2008-12-22 | 電圧出力ドライバー |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008325833A JP2010142783A (ja) | 2008-12-22 | 2008-12-22 | 電圧出力ドライバー |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2010142783A true JP2010142783A (ja) | 2010-07-01 |

Family

ID=42563766

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008325833A Pending JP2010142783A (ja) | 2008-12-22 | 2008-12-22 | 電圧出力ドライバー |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2010142783A (ja) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103987310A (zh) * | 2011-12-09 | 2014-08-13 | 欧姆龙健康医疗事业株式会社 | 电子血压计 |

| JP2017045040A (ja) * | 2015-08-26 | 2017-03-02 | 株式会社リコー | アクチュエータ制御装置、駆動システム、映像機器、画像投影装置およびアクチュエータ制御方法 |

| US9775526B2 (en) | 2012-04-19 | 2017-10-03 | Omron Healthcare Co., Ltd. | Blood pressure meter and pump driving system |

| CN111510018A (zh) * | 2020-05-20 | 2020-08-07 | 矽力杰半导体技术(杭州)有限公司 | 压电驱动电路和压电驱动方法 |

| US12092094B2 (en) | 2017-03-16 | 2024-09-17 | Murata Manufacturing Co., Ltd. | Fluid control device and sphygmomanometer |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS59204737A (ja) * | 1983-05-09 | 1984-11-20 | Kokusai Kikai Shindo Kenkyusho:Kk | 加振方法 |

| WO2005080793A1 (ja) * | 2004-02-23 | 2005-09-01 | Nec Corporation | 圧電ポンプ用駆動回路およびこれを用いた冷却システム |

-

2008

- 2008-12-22 JP JP2008325833A patent/JP2010142783A/ja active Pending

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS59204737A (ja) * | 1983-05-09 | 1984-11-20 | Kokusai Kikai Shindo Kenkyusho:Kk | 加振方法 |

| WO2005080793A1 (ja) * | 2004-02-23 | 2005-09-01 | Nec Corporation | 圧電ポンプ用駆動回路およびこれを用いた冷却システム |

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103987310A (zh) * | 2011-12-09 | 2014-08-13 | 欧姆龙健康医疗事业株式会社 | 电子血压计 |

| CN103987310B (zh) * | 2011-12-09 | 2016-05-11 | 欧姆龙健康医疗事业株式会社 | 电子血压计 |

| US9775526B2 (en) | 2012-04-19 | 2017-10-03 | Omron Healthcare Co., Ltd. | Blood pressure meter and pump driving system |

| JP2017045040A (ja) * | 2015-08-26 | 2017-03-02 | 株式会社リコー | アクチュエータ制御装置、駆動システム、映像機器、画像投影装置およびアクチュエータ制御方法 |

| US12092094B2 (en) | 2017-03-16 | 2024-09-17 | Murata Manufacturing Co., Ltd. | Fluid control device and sphygmomanometer |

| CN111510018A (zh) * | 2020-05-20 | 2020-08-07 | 矽力杰半导体技术(杭州)有限公司 | 压电驱动电路和压电驱动方法 |

| CN111510018B (zh) * | 2020-05-20 | 2022-05-24 | 矽力杰半导体技术(杭州)有限公司 | 压电驱动电路和压电驱动方法 |

| US11985902B2 (en) | 2020-05-20 | 2024-05-14 | Silergy Semiconductor Technology Hangzhou Ltd | Driving circuit and driving method |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100972686B1 (ko) | 모터 구동 장치 및 이것을 이용한 전기 기기 | |

| CN107370340A (zh) | 电流检测电路和包括该电流检测电路的 dcdc 转换器 | |

| JP2010142783A (ja) | 電圧出力ドライバー | |

| JP2013099181A (ja) | 駆動回路 | |

| JP5192359B2 (ja) | 高電圧出力ドライバーおよび圧電ポンプ | |

| JP5408893B2 (ja) | モータ駆動回路 | |

| JP3126735U (ja) | モータ制御回路 | |

| US10637356B2 (en) | Multiple-level buck boost converter control | |

| JP5028400B2 (ja) | 電圧出力ドライバーおよび圧電ポンプ | |

| JP2010081405A (ja) | 高電圧出力ドライバーおよび圧電ポンプ | |

| JP2013247574A (ja) | Pwm信号生成回路および半導体装置 | |

| US9673735B2 (en) | Power converter | |

| JP4454328B2 (ja) | モータ駆動装置、集積回路、モータ駆動方法 | |

| CN101031854A (zh) | 多相三角波振荡电路和使用其的切换调节器 | |

| JP2010136545A (ja) | 高電圧出力ドライバーおよび圧電ポンプ | |

| CN111030653A (zh) | Pwm信号发生电路及锯齿波信号发生电路 | |

| JP4970153B2 (ja) | スイッチング電源装置 | |

| JP2010131539A (ja) | 高電圧出力ドライバーおよび圧電ポンプ | |

| JP2001326567A (ja) | Mosfet駆動回路 | |

| Fathoni et al. | Design of Brushless DC Motor Driver Based on Bootstrap Circuit | |

| JP2010130734A (ja) | 高電圧出力ドライバーおよび圧電ポンプ | |

| JP2011055585A (ja) | 高電圧出力ドライバー | |

| JP2010104131A (ja) | 高電圧出力ドライバー | |

| JP2010130732A (ja) | 出力ドライバー | |

| JP2010104132A (ja) | 高電圧出力ドライバー |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100921 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101021 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120418 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120424 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120828 |