JP2010093989A - 電源回路 - Google Patents

電源回路 Download PDFInfo

- Publication number

- JP2010093989A JP2010093989A JP2008263524A JP2008263524A JP2010093989A JP 2010093989 A JP2010093989 A JP 2010093989A JP 2008263524 A JP2008263524 A JP 2008263524A JP 2008263524 A JP2008263524 A JP 2008263524A JP 2010093989 A JP2010093989 A JP 2010093989A

- Authority

- JP

- Japan

- Prior art keywords

- power supply

- inductor

- circuit

- mosfet

- diode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/0083—Converters characterised by their input or output configuration

- H02M1/0085—Partially controlled bridges

Landscapes

- Rectifiers (AREA)

Abstract

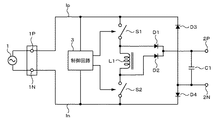

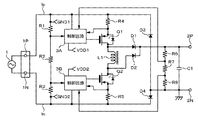

【解決手段】正の半サイクル期間に、Q1が常にオンとされ、Q2がスイッチング動作を行う。負の半サイクル期間において、Q2が常にオンとされ、Q1がスイッチング動作を行う。Q2がオンの期間では、入力端子1PからQ1、インダクタL1、Q2を順に経由して入力端子1Nに電流が流れる。Q2がオフすると、インダクタ電流が瞬時に遮断されるので、昇圧された電圧がD2を介してC1を充電する。負荷からのリターン電流、或いはC1を充電したリターン電流は、D4を介して下側の回路線lnへ流れる。負の半サイクル期間では、Q1が常にオンとされ、Q2がスイッチング動作を行う。

【選択図】図2

Description

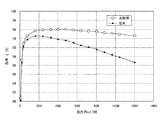

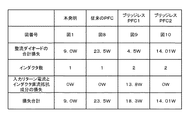

入力交流電圧:85V〜264V(rms:root mean square 二乗平均平方根=実効値)

直流出力電圧:400V 最大出力電力:900W 電源の効率:90%(すなわち、最大入力電力:1000W)

(900W/400V)によって最大直流出力電流が2.25Aとなり、(1000W/85V(rms) )によって最大入力電流が11.76A(rms) となる。

11.76×11.76×0.1=13.8W

Performance Evaluation of Bridgeless PFC Boost RectifiersHuber, Laszlo; Jang, Yungtaek; Jovanovic, Milan M.Applied Power Electronics Conference, APEC 2007 - Twenty Second Annual IEEEVolume , Issue , Feb. 25 2007-March 1 2007 Page(s):165 - 171

1.0×11.76=11.76W

直流電源が出力される第1および第2の出力端子と、

第1および第2の出力端子間に接続される平滑コンデンサと、

インダクタと、

第1の回路線とインダクタの一端との間に接続される第1のスイッチング素子と、

第2の回路線とインダクタの他端との間に接続される第2のスイッチング素子と、

インダクタの一端にアノードが接続され、第1の出力端子にカソードが接続される第1のダイオードと、

インダクタの他端にアノードが接続され、第1の出力端子にカソードが接続される第2のダイオードと、

第1の回路線にカソードが接続され、第2の出力端子にアノードが接続される第3のダイオードと、

第2の回路線にカソードが接続され、第2の出力端子にアノードが接続される第4のダイオードと、

交流電源電圧の一方の半サイクル期間中には、第1のスイッチング素子を常にオン状態とすると共に、第2のスイッチング素子をスイッチング動作させ、交流電源電圧の他方の半サイクル期間中には、第2のスイッチング素子を常にオン状態とすると共に、第1のスイッチング素子をスイッチング動作させる制御回路と

を有する電源回路である。

直流電源が出力される第1および第2の出力端子と、

第1および第2の出力端子間に接続される平滑コンデンサと、

インダクタと、

第1の回路線とインダクタの一端との間に、ドレイン・ソース間が接続される第1のMOSFETと、

第2の回路線とインダクタの他端との間に、ドレイン・ソース間が接続される第2のMOSFETと、

インダクタの一端にアノードが接続され、第1の出力端子にカソードが接続される第1のダイオードと、

インダクタの他端にアノードが接続され、第1の出力端子にカソードが接続される第2のダイオードと、

第1の回路線にカソードが接続され、第2の出力端子にアノードが接続される第3のダイオードと、

第2の回路線にカソードが接続され、第2の出力端子にアノードが接続される第4のダイオードと、

交流電源電圧の一方の半サイクル期間中には、第1のMOSFETを常にオン状態とすると共に、第2のMOSFETをスイッチング動作させ、交流電源電圧の他方の半サイクル期間中には、第2のMOSFETを常にオン状態とすると共に、第1のMOSFETをスイッチング動作させる制御回路と

を有する電源回路である。

1.第1の実施の形態

2.第2の実施の形態

「第1の実施の形態の構成」

図1を参照して第1の実施の形態の構成について説明する。交流電源1と第1の入力端子1Pおよび第2の入力端子1Nが接続される。交流電源の一例は、商用電源である。入力端子1Pおよび入力端子1Nのそれぞれから第1の回路線lpおよび第2の回路線lnが導出される。直流電源が出力される第1の出力端子2Pおよび第2の出力端子2Nに対して負荷(図示せず)が接続される。出力端子2Pおよび出力端子2N間に平滑コンデンサC1が接続される。

正の半サイクル期間において、スイッチング素子S1が常にオンとされ、スイッチング素子S2がスイッチング動作を行う。スイッチング素子S2がオンの期間では、入力端子1Pからスイッチング素子S1、インダクタL1、スイッチング素子S2を順に経由して入力端子1Nに電流が流れる。

「第2の実施の形態の構成」

図2を参照して、この発明の第2の実施の形態の構成について説明する。第2の実施の形態は、第1の実施の形態において、スイッチング素子S1およびスイッチング素子S2として、Nチャネル型MOS(Metal Oxide Semiconductor) FET(Field Effect Transistor) Q1およびMOSFET Q2を使用する構成である。MOSFET Q1およびMOSFET Q2のゲートに対して、別個の制御回路3Aおよび制御回路3Bがドライブパルスをそれぞれ供給する。

Q1およびMOSFET Q2のオン/オフ動作は、制御回路3Aおよび制御回路3Bによってそれぞれ生成されたパルス信号(ドライブパルス)によって制御される。

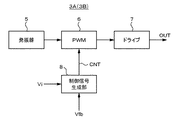

制御回路の構成の一例について説明する。制御回路3Aおよび制御回路3Bは、同一の構成とされている。図3に示すように、制御回路は、発振器5と、パルス幅変調(PWM;Pulse Width Modulation)回路6と、ドライブ回路7とを有する。なお、制御回路には、過電流に対する保護回路が設けられているが、簡単のため省略する。

図4の各部波形図を参照してこの発明の第2の実施の形態の動作について説明する。図4Aは、交流電源1の電圧波形である。T+で示す期間は、入力端子1Pが正極で、入力端子1Nが負極となる正の半サイクル期間である。T−で示す期間は、入力端子1Pが正極で、入力端子1Nが負極となる負の半サイクル期間である。

以上、この発明の実施形態について具体的に説明したが、この発明は、上述の実施形態に限定されるものではなく、この発明の技術的思想に基づく各種の変形が可能である。例えばスイッチング素子としては、MOSFET以外にIGBT(Insulated Gate Bipolar

Transistor:絶縁ゲートバイポーラトランジスタ)を使用しても良い。リレー素子を使用することも可能である。さらに、この発明が適用された電源回路は、電子機器に組み込まれても良いし、AC−DC電源装置単体の構成としても良い。

1P,1N・・・入力端子

2P,2N・・・出力端子

3,3A,3B・・・制御回路

lp,ln・・・回路線

S1,S2・・・スイッチング素子

Q1,Q2・・・MOSFET

L1・・・インダクタ

C1・・・平滑コンデンサ

SW・・・スイッチ回路

D1〜D4・・・ダイオード

Claims (5)

- 交流電源が接続され、第1および第2の回路線が導出される第1および第2の入力端子と、

直流電源が出力される第1および第2の出力端子と、

上記第1および第2の出力端子間に接続される平滑コンデンサと、

インダクタと、

上記第1の回路線と上記インダクタの一端との間に接続される第1のスイッチング素子と、

上記第2の回路線と上記インダクタの他端との間に接続される第2のスイッチング素子と、

上記インダクタの一端にアノードが接続され、上記第1の出力端子にカソードが接続される第1のダイオードと、

上記インダクタの他端にアノードが接続され、上記第1の出力端子にカソードが接続される第2のダイオードと、

上記第1の回路線にカソードが接続され、上記第2の出力端子にアノードが接続される第3のダイオードと、

上記第2の回路線にカソードが接続され、上記第2の出力端子にアノードが接続される第4のダイオードと、

交流電源電圧の一方の半サイクル期間中には、上記第1のスイッチング素子を常にオン状態とすると共に、上記第2のスイッチング素子をスイッチング動作させ、上記交流電源電圧の他方の半サイクル期間中には、上記第2のスイッチング素子を常にオン状態とすると共に、上記第1のスイッチング素子をスイッチング動作させる制御回路と

を有する電源回路。 - 交流電源が接続され、第1および第2の回路線が導出される第1および第2の入力端子と、

直流電源が出力される第1および第2の出力端子と、

上記第1および第2の出力端子間に接続される平滑コンデンサと、

インダクタと、

上記第1の回路線と上記インダクタの一端との間に、ドレイン・ソース間が接続される第1のMOSFETと、

上記第2の回路線と上記インダクタの他端との間に、ドレイン・ソース間が接続される第2のMOSFETと、

上記インダクタの一端にアノードが接続され、上記第1の出力端子にカソードが接続される第1のダイオードと、

上記インダクタの他端にアノードが接続され、上記第1の出力端子にカソードが接続される第2のダイオードと、

上記第1の回路線にカソードが接続され、上記第2の出力端子にアノードが接続される第3のダイオードと、

上記第2の回路線にカソードが接続され、上記第2の出力端子にアノードが接続される第4のダイオードと、

交流電源電圧の一方の半サイクル期間中には、上記第1のMOSFETを常にオン状態とすると共に、上記第2のMOSFETをスイッチング動作させ、上記交流電源電圧の他方の半サイクル期間中には、上記第2のMOSFETを常にオン状態とすると共に、上記第1のMOSFETをスイッチング動作させる制御回路と

を有する電源回路。 - 上記制御回路に対して、上記交流電源と、上記直流電源とが供給され、

上記制御回路が上記交流電源の位相と上記直流電源の電圧に応じてデューティ比が変調されたパルス信号を生成し、

上記パルス信号によって上記第1および第2のMOSFETをスイッチング駆動する請求項2記載の電源回路。 - 上記第1および第2のMOSFETを流れる電流が検出され、検出結果が上記制御回路に供給される請求項3記載の電源回路。

- 上記制御回路が上記第1および第2の制御回路から構成され、

上記第1の制御回路が上記第1のMOSFETを制御し、上記第2の制御回路が上記第2のMOSFETを制御する請求項2記載の電源回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008263524A JP5151889B2 (ja) | 2008-10-10 | 2008-10-10 | 電源回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008263524A JP5151889B2 (ja) | 2008-10-10 | 2008-10-10 | 電源回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010093989A true JP2010093989A (ja) | 2010-04-22 |

| JP5151889B2 JP5151889B2 (ja) | 2013-02-27 |

Family

ID=42256138

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008263524A Expired - Fee Related JP5151889B2 (ja) | 2008-10-10 | 2008-10-10 | 電源回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5151889B2 (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2015033170A (ja) * | 2013-07-31 | 2015-02-16 | ニチコン株式会社 | ブリッジレス電源回路 |

| CN110707947A (zh) * | 2019-10-16 | 2020-01-17 | 福州物联网开放实验室有限公司 | 一种无桥单极pfc电路 |

| CN113985138A (zh) * | 2021-09-26 | 2022-01-28 | 杭州市电力设计院有限公司 | 电动汽车充电机升压电感电流间接测算方法及测压电路 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0833227A (ja) * | 1994-07-13 | 1996-02-02 | Kokusan Denki Co Ltd | 内燃機関用電源装置 |

| JP2004072846A (ja) * | 2002-08-02 | 2004-03-04 | Fuji Electric Holdings Co Ltd | 整流装置 |

| JP2007527687A (ja) * | 2003-10-01 | 2007-09-27 | インターナショナル・レクティファイヤ・コーポレーション | ワンサイクル制御によって制御されるブリッジレスブースト式(blb)力率補正トポロジー |

-

2008

- 2008-10-10 JP JP2008263524A patent/JP5151889B2/ja not_active Expired - Fee Related

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0833227A (ja) * | 1994-07-13 | 1996-02-02 | Kokusan Denki Co Ltd | 内燃機関用電源装置 |

| JP2004072846A (ja) * | 2002-08-02 | 2004-03-04 | Fuji Electric Holdings Co Ltd | 整流装置 |

| JP2007527687A (ja) * | 2003-10-01 | 2007-09-27 | インターナショナル・レクティファイヤ・コーポレーション | ワンサイクル制御によって制御されるブリッジレスブースト式(blb)力率補正トポロジー |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2015033170A (ja) * | 2013-07-31 | 2015-02-16 | ニチコン株式会社 | ブリッジレス電源回路 |

| CN110707947A (zh) * | 2019-10-16 | 2020-01-17 | 福州物联网开放实验室有限公司 | 一种无桥单极pfc电路 |

| CN110707947B (zh) * | 2019-10-16 | 2022-04-05 | 福州物联网开放实验室有限公司 | 一种无桥单极pfc电路 |

| CN113985138A (zh) * | 2021-09-26 | 2022-01-28 | 杭州市电力设计院有限公司 | 电动汽车充电机升压电感电流间接测算方法及测压电路 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5151889B2 (ja) | 2013-02-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6344986B1 (en) | Topology and control method for power factor correction | |

| JP5182375B2 (ja) | Pfcコンバータ | |

| US10193437B1 (en) | Bridgeless AC-DC converter with power factor correction and method therefor | |

| JP5704124B2 (ja) | スイッチング電源装置 | |

| US10819222B2 (en) | Circuitry for power factor correction and methods of operation | |

| US7738266B2 (en) | Forward power converter controllers | |

| US20100259240A1 (en) | Bridgeless PFC converter | |

| US8625311B2 (en) | Switching power supply apparatus including a plurality of switching elements | |

| JP5914989B2 (ja) | スイッチング電源装置 | |

| JP2008312355A (ja) | Ac−dcコンバータ | |

| US9979308B1 (en) | Synchronous rectifier switch control during burst mode operation of an LLC converter | |

| JP2011050135A (ja) | 共振型スイッチング電源装置 | |

| JP2003088114A (ja) | Dc−dcコンバータ | |

| JP5642621B2 (ja) | スイッチング電源装置 | |

| JP2004364433A (ja) | 直流電圧変換回路 | |

| JP2010124567A (ja) | スイッチング電源装置 | |

| JP5151889B2 (ja) | 電源回路 | |

| US7688044B2 (en) | Device for transforming and stabilizing a primary AC voltage for supplying an electric load | |

| JP5927142B2 (ja) | スイッチング電源装置及びその制御方法 | |

| JP2015228760A (ja) | スイッチング電源装置 | |

| JP4764980B2 (ja) | 直流−直流変換装置 | |

| JP2016220342A (ja) | スイッチング電源装置 | |

| Zhang et al. | A new current-source gate driver for a buck voltage regulator | |

| JP2006340590A (ja) | Ac−dcコンバータ | |

| JP7347010B2 (ja) | 昇降圧チョッパ回路及び直流電源装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110912 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121029 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121106 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121119 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151214 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151214 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |