JP2010074176A - Semiconductor device and method for manufacturing the same - Google Patents

Semiconductor device and method for manufacturing the same Download PDFInfo

- Publication number

- JP2010074176A JP2010074176A JP2009260141A JP2009260141A JP2010074176A JP 2010074176 A JP2010074176 A JP 2010074176A JP 2009260141 A JP2009260141 A JP 2009260141A JP 2009260141 A JP2009260141 A JP 2009260141A JP 2010074176 A JP2010074176 A JP 2010074176A

- Authority

- JP

- Japan

- Prior art keywords

- region

- insulating film

- gate insulating

- conductivity type

- gate electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 129

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 55

- 238000000034 method Methods 0.000 title claims abstract description 48

- 239000012535 impurity Substances 0.000 claims abstract description 117

- 239000000758 substrate Substances 0.000 claims abstract description 105

- 238000005468 ion implantation Methods 0.000 claims abstract description 99

- 238000002955 isolation Methods 0.000 claims abstract description 47

- 229910021332 silicide Inorganic materials 0.000 claims abstract description 22

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 claims abstract description 22

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 claims abstract description 20

- 125000006850 spacer group Chemical group 0.000 claims description 87

- 150000002500 ions Chemical class 0.000 claims description 53

- 238000009826 distribution Methods 0.000 claims description 27

- 229910052698 phosphorus Inorganic materials 0.000 claims description 20

- 239000011574 phosphorus Substances 0.000 claims description 20

- 238000005530 etching Methods 0.000 claims description 15

- 238000000151 deposition Methods 0.000 claims description 10

- 230000000149 penetrating effect Effects 0.000 claims description 8

- 239000011810 insulating material Substances 0.000 claims description 4

- 239000012212 insulator Substances 0.000 claims description 4

- 238000011049 filling Methods 0.000 claims description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 abstract description 32

- 229910052710 silicon Inorganic materials 0.000 abstract description 32

- 239000010703 silicon Substances 0.000 abstract description 31

- 230000008569 process Effects 0.000 abstract description 21

- 229910052751 metal Inorganic materials 0.000 abstract description 8

- 239000002184 metal Substances 0.000 abstract description 8

- 230000015572 biosynthetic process Effects 0.000 abstract description 6

- 238000000059 patterning Methods 0.000 abstract description 5

- 239000010410 layer Substances 0.000 description 106

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 41

- 229910052814 silicon oxide Inorganic materials 0.000 description 41

- 230000001133 acceleration Effects 0.000 description 32

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 30

- 230000015556 catabolic process Effects 0.000 description 28

- 238000009792 diffusion process Methods 0.000 description 16

- 230000007423 decrease Effects 0.000 description 13

- 238000004151 rapid thermal annealing Methods 0.000 description 13

- 230000007547 defect Effects 0.000 description 12

- 229920002120 photoresistant polymer Polymers 0.000 description 12

- 229910052581 Si3N4 Inorganic materials 0.000 description 11

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 11

- 230000002159 abnormal effect Effects 0.000 description 9

- 230000000694 effects Effects 0.000 description 9

- 239000011229 interlayer Substances 0.000 description 9

- 238000006243 chemical reaction Methods 0.000 description 8

- 239000013078 crystal Substances 0.000 description 8

- 229920005591 polysilicon Polymers 0.000 description 8

- 238000012545 processing Methods 0.000 description 7

- 239000003990 capacitor Substances 0.000 description 6

- 230000003647 oxidation Effects 0.000 description 6

- 238000007254 oxidation reaction Methods 0.000 description 6

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 5

- 238000002474 experimental method Methods 0.000 description 5

- 238000010438 heat treatment Methods 0.000 description 5

- 238000001020 plasma etching Methods 0.000 description 5

- 238000001994 activation Methods 0.000 description 4

- 230000003247 decreasing effect Effects 0.000 description 4

- 230000006870 function Effects 0.000 description 4

- 238000000206 photolithography Methods 0.000 description 4

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 4

- 238000004088 simulation Methods 0.000 description 4

- 230000004913 activation Effects 0.000 description 3

- 229910021417 amorphous silicon Inorganic materials 0.000 description 3

- 238000013461 design Methods 0.000 description 3

- 239000007943 implant Substances 0.000 description 3

- 238000005498 polishing Methods 0.000 description 3

- 239000000126 substance Substances 0.000 description 3

- XUKUURHRXDUEBC-SXOMAYOGSA-N (3s,5r)-7-[2-(4-fluorophenyl)-3-phenyl-4-(phenylcarbamoyl)-5-propan-2-ylpyrrol-1-yl]-3,5-dihydroxyheptanoic acid Chemical compound C=1C=CC=CC=1C1=C(C=2C=CC(F)=CC=2)N(CC[C@@H](O)C[C@H](O)CC(O)=O)C(C(C)C)=C1C(=O)NC1=CC=CC=C1 XUKUURHRXDUEBC-SXOMAYOGSA-N 0.000 description 2

- 108010063256 HTLV-1 protease Proteins 0.000 description 2

- 101000831940 Homo sapiens Stathmin Proteins 0.000 description 2

- 101000621511 Potato virus M (strain German) RNA silencing suppressor Proteins 0.000 description 2

- 102100024237 Stathmin Human genes 0.000 description 2

- 238000000137 annealing Methods 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 230000012447 hatching Effects 0.000 description 2

- BHEPBYXIRTUNPN-UHFFFAOYSA-N hydridophosphorus(.) (triplet) Chemical compound [PH] BHEPBYXIRTUNPN-UHFFFAOYSA-N 0.000 description 2

- 230000010354 integration Effects 0.000 description 2

- 230000007257 malfunction Effects 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 238000005259 measurement Methods 0.000 description 2

- 230000003071 parasitic effect Effects 0.000 description 2

- 238000010517 secondary reaction Methods 0.000 description 2

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 2

- 238000012546 transfer Methods 0.000 description 2

- 239000011800 void material Substances 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- 241000293849 Cordylanthus Species 0.000 description 1

- 238000004458 analytical method Methods 0.000 description 1

- 230000002547 anomalous effect Effects 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 238000002425 crystallisation Methods 0.000 description 1

- 230000008025 crystallization Effects 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 238000005137 deposition process Methods 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 239000002784 hot electron Substances 0.000 description 1

- 238000002513 implantation Methods 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 239000012299 nitrogen atmosphere Substances 0.000 description 1

- 230000035515 penetration Effects 0.000 description 1

- -1 phosphorus ions Chemical class 0.000 description 1

- 239000011241 protective layer Substances 0.000 description 1

- 239000002994 raw material Substances 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 230000006641 stabilisation Effects 0.000 description 1

- 238000011105 stabilization Methods 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

Images

Landscapes

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

- Semiconductor Integrated Circuits (AREA)

Abstract

Description

本発明は、半導体装置とその製造方法に関し、特に複数の半導体素子、例えば微細化したトランジスタと抵抗、または複数の電圧で動作するトランジスタを含む半導体装置、または耐圧を向上したトランジスタを含む半導体装置とその製造方法に関する。 The present invention relates to a semiconductor device and a method for manufacturing the same, and more particularly, a plurality of semiconductor elements, for example, a semiconductor device including a transistor which operates with a miniaturized transistor and a resistance or a plurality of voltages, or a semiconductor device including a transistor with improved breakdown voltage. It relates to the manufacturing method.

半導体集積回路装置(IC)の集積度の向上と共に、ICの構成要素であるトランジスタは微細化されている。ロジック半導体素子は、性能が著しく向上し、多くの機能を同一チップ上に搭載するようになっている。例えば、高密度スタティックランダムアクセスメモリ(SRAM)、超高速入出力回路がロジック回路と同一チップ上に搭載される。 As the degree of integration of semiconductor integrated circuit devices (ICs) increases, transistors that are components of ICs are miniaturized. Logic semiconductor devices have significantly improved performance and many functions are mounted on the same chip. For example, a high-density static random access memory (SRAM) and an ultrahigh-speed input / output circuit are mounted on the same chip as the logic circuit.

SRAMは、例えば2つのnチャネルドライバトランジスタ、2つのpチャネル負荷トランジスタ、2つのnチャネルトランスファトランジスタの計6トランジスタで1メモリセルを構成する。1トランジスタ、1キャパシタで1メモリセルを構成するダイナミックRAM(DRAM)と比べると、構成素子数は多くなるが、リフレッシュ動作が不要である。 In the SRAM, for example, a total of six transistors including two n-channel driver transistors, two p-channel load transistors, and two n-channel transfer transistors constitute one memory cell. Compared to a dynamic RAM (DRAM) that configures one memory cell with one transistor and one capacitor, the number of constituent elements is increased, but a refresh operation is not required.

高密度SRAM等の多数の半導体素子を高密度に収容する回路の素子分離領域として、シャロートレンチアイソレーション(STI)が広く用いられている。局所酸化(LOCOS)に於けるバーズビークが存在せず、面積利用率を向上できると共に、平坦性のよい表面が得られる。 Shallow trench isolation (STI) is widely used as an element isolation region of a circuit that accommodates a large number of semiconductor elements such as a high-density SRAM. There is no bird's beak in local oxidation (LOCOS), the area utilization rate can be improved, and a surface with good flatness can be obtained.

トランジスタの寄生抵抗を低減するために、ソース/ドレイン領域およびゲート電極の上に自己整合的に金属シリサイド層を形成するサリサイド技術も広く用いられている。

特開2000−198523号は、STIとサリサイド技術を用いたSRAMを開示している。ゲート電極側壁上に第1のサイドウォールスペーサを形成し、ソース/ドレイン領域とゲート電極に対する高濃度イオン注入を行った後、第2のサイドウォールスペーサを形成し、その後基板全面に対してサリサイドを行っている。ソース/ドレイン領域上のシリサイド層のゲート電極側端部を接合から離すことによりリーク電流を低減する。SRAM以外の回路素子については、開示はない。

In order to reduce the parasitic resistance of a transistor, a salicide technique in which a metal silicide layer is formed in a self-aligned manner on the source / drain regions and the gate electrode is also widely used.

Japanese Unexamined Patent Publication No. 2000-198523 discloses an SRAM using STI and salicide technology. A first sidewall spacer is formed on the side wall of the gate electrode, high concentration ion implantation is performed on the source / drain regions and the gate electrode, a second sidewall spacer is formed, and then salicide is applied to the entire surface of the substrate. Is going. Leakage current is reduced by separating the gate electrode side end of the silicide layer on the source / drain region from the junction. There is no disclosure of circuit elements other than SRAM.

トランジスタと他の素子を集積化する場合、各素子を独立に作成すると製造工程は複雑化し、歩留まりは低下する。同一工程を複数の素子に共用させ、製造工程をなるべく簡略化することが望まれる。作成する回路によって、他の素子はキャパシタであったり、抵抗であったりする。抵抗の場合、抵抗値は所望の値であることが望まれ、高すぎても、低すぎても不適当な場合が多い。 In the case of integrating transistors and other elements, if each element is formed independently, the manufacturing process becomes complicated and the yield decreases. It is desired that the same process is shared by a plurality of elements and the manufacturing process is simplified as much as possible. Depending on the circuit to be created, other elements may be capacitors or resistors. In the case of a resistor, it is desired that the resistance value be a desired value, and it is often unsuitable whether it is too high or too low.

特開2000−31295号は、素子分離をSTIで行い、アナログ−デジタル変換回路用アナログ抵抗をシリサイド層付MOSトランジスタと集積化した半導体集積回路装置を開示する。アナログ抵抗をシリコン基板内の拡散層で形成する場合と、素子分離領域上の多結晶シリコンで形成する場合の両者を開示している。 Japanese Patent Application Laid-Open No. 2000-31295 discloses a semiconductor integrated circuit device in which element isolation is performed by STI and an analog resistor for an analog-digital conversion circuit is integrated with a MOS transistor with a silicide layer. Both the case where the analog resistor is formed by a diffusion layer in the silicon substrate and the case where the analog resistor is formed by polycrystalline silicon on the element isolation region are disclosed.

数十Ω/□〜数百Ω/□のアナログ抵抗の抵抗値を最適に設定するため、抵抗部はトランジスタとは別に独立に形成される。サイドウォールスペーサ形成の際、レジストマスクを抵抗部上に形成し、サイドウォールスペーサと同一層のサリサイドブロック層を残す。抵抗部両端の接続部はトランジスタの高濃度領域と同時に高濃度にイオン注入される。その後、全面にサリサイド処理を行なう。トランジスタのソース/ドレイン領域とゲート電極上、抵抗部両端の接続部上にはシリサイド層が形成される。 In order to optimally set the resistance value of the analog resistance of several tens Ω / □ to several hundreds Ω / □, the resistance portion is formed independently of the transistor. When the sidewall spacer is formed, a resist mask is formed on the resistance portion, and the salicide block layer that is the same layer as the sidewall spacer is left. The connection portions at both ends of the resistor portion are ion-implanted at a high concentration simultaneously with the high-concentration region of the transistor. Thereafter, salicide processing is performed on the entire surface. Silicide layers are formed on the source / drain regions of the transistor and the gate electrode, and on the connection portions at both ends of the resistance portion.

特開2002−280459号は、素子分離をLOCOSで行い、トランジスタ、キャパシタ、抵抗を集積化した集積回路装置を開示している。第1の多結晶シリコン層を用いて、トランジスタのゲート電極と同時にキャパシタの下部電極を形成し、キャパシタ用誘電体膜を形成した後、第2の多結晶シリコン層を用いてキャパシタの上部電極と抵抗を形成している。抵抗は別個のイオン注入で所望の不純物濃度にする。サリサイド工程においては、抵抗と入出力用トランジスタ上にサリサイドブロック層を形成し、シリサイド層を形成しないようにする。 Japanese Patent Laid-Open No. 2002-280459 discloses an integrated circuit device in which element isolation is performed by LOCOS and transistors, capacitors, and resistors are integrated. The first polycrystalline silicon layer is used to form the lower electrode of the capacitor simultaneously with the gate electrode of the transistor, the capacitor dielectric film is formed, and then the upper polycrystalline silicon layer is used to form the capacitor upper electrode Forming a resistor. The resistance is brought to the desired impurity concentration by separate ion implantation. In the salicide process, a salicide block layer is formed on the resistor and the input / output transistor, and a silicide layer is not formed.

トランジスタの微細化に伴って、動作電圧は低下し、ゲート絶縁膜は薄く、ゲート長は短くなる。トランジスタのオフ状態でソース/ドレイン間にパンチスルー電流が流れてしまう等の短チャネル効果が生じる。 As the transistor is miniaturized, the operating voltage is decreased, the gate insulating film is thin, and the gate length is shortened. A short channel effect such as a punch-through current flowing between the source and drain occurs when the transistor is off.

短チャネル効果を防止するため、ソース・ドレイン領域をゲート電極の両側の浅いエクステンション領域とゲート電極側壁上のサイドウォールスペーサ両側の高不純物濃度のソース/ドレイン領域で形成し,さらにエクステンション領域を逆導電型のポケット領域で囲む構成が開発されている。ポケット領域は、基板法線から傾いた方向から、エクステンション領域形成用イオン注入より飛程の長いイオン注入を行うことで形成される。 In order to prevent the short channel effect, the source / drain regions are formed with shallow extension regions on both sides of the gate electrode and high impurity concentration source / drain regions on both sides of the side wall spacer on the gate electrode side wall, and the extension regions are reversely conductive. A configuration that surrounds the pocket area of the mold has been developed. The pocket region is formed by performing ion implantation having a longer range than the ion implantation for forming the extension region from the direction inclined from the substrate normal.

システムオンチップにおいては、低電圧動作の論理回路と高電圧動作のフラッシュメモリ制御回路のような異種回路を混載する要請も強い。これを実現するには、低電圧動作の論理回路と高電圧動作のフラッシュメモリ制御回路とを同一半導体基板上に集積化することが必要となる。 In the system-on-chip, there is a strong demand for mounting different types of circuits such as a low-voltage operation logic circuit and a high-voltage operation flash memory control circuit. In order to realize this, it is necessary to integrate a low-voltage operation logic circuit and a high-voltage operation flash memory control circuit on the same semiconductor substrate.

例えば、1.2V動作の論理回路用低電圧トランジスタと、読出時5Vおよび書込/消去時10V弱動作のフラッシュメモリ制御回路用高電圧トランジスタを集積化する。さらに,入出力回路(I/O)用に2.5Vや3.3V動作の中電圧トランジスタを集積化する要請も強い。低電圧トランジスタの動作電圧はさらに低電圧化する傾向にあり、I/O用中電圧トランジスタの動作電圧は、さらに5V、1.8V、1.2V等が加わる可能性がある。但し,特定の顧客の要請においては、中電圧トランジスタの動作電圧は1種類である場合が多い。 For example, a low voltage transistor for a logic circuit that operates at 1.2 V and a high voltage transistor for a flash memory control circuit that operates at a voltage less than 5 V at the time of reading and 10 V at the time of writing / erasing are integrated. Further, there is a strong demand for integrating a medium voltage transistor operating at 2.5 V or 3.3 V for an input / output circuit (I / O). The operating voltage of the low-voltage transistor tends to be further lowered, and the operating voltage of the medium voltage transistor for I / O may be further increased by 5V, 1.8V, 1.2V, and the like. However, there are many cases where the operating voltage of the medium voltage transistor is one type at the request of a specific customer.

高電圧トランジスタは,ホットエレクトロン効果を抑制し、必要な耐圧を備える必要がある。ゲート絶縁膜を厚くし,ゲート長を長くし、ゲート電極両側に不純物濃度の低い低濃度ドレイン(LDD)領域を形成し,ゲート電極側壁上のサイドウォールスペーサ両側に高濃度ソース/ドレイン領域を形成する構成が適している。 The high voltage transistor needs to suppress the hot electron effect and have a necessary breakdown voltage. The gate insulating film is thickened, the gate length is increased, low concentration drain (LDD) regions with low impurity concentration are formed on both sides of the gate electrode, and high concentration source / drain regions are formed on both sides of the side wall spacer on the side wall of the gate electrode. The configuration is suitable.

エクステンション領域をLDD領域と呼ぶ場合も多いが、本明細書においては、浅い接合を形成することを主目的とするものをエクステンション領域と呼び、耐圧を向上することを主目的とするものをLDD領域と呼ぶ。LDD領域は文字通り低不純物濃度であることが望ましいが、エクステンション領域は接合深さが浅ければ低不純物濃度である必要はない。 In many cases, the extension region is referred to as an LDD region. In this specification, a region whose main purpose is to form a shallow junction is called an extension region, and a region whose main purpose is to improve breakdown voltage is an LDD region. Call it. Although it is desirable that the LDD region literally has a low impurity concentration, the extension region need not have a low impurity concentration if the junction depth is shallow.

複数種類のトランジスタを集積化する時、各トランジスタの望ましい特性に合わせてそれぞれ独立に製造プロセスを選択すると、工程数が多くなって製造プロセスは複雑化し、歩留まりが低下し、製造原価が高くなる。複数種類のトランジスタを簡略化したプロセスで製造することが望まれる。 When a plurality of types of transistors are integrated, if a manufacturing process is independently selected in accordance with the desired characteristics of each transistor, the number of steps increases, the manufacturing process becomes complicated, yield decreases, and manufacturing costs increase. It is desirable to manufacture a plurality of types of transistors by a simplified process.

特開2000−68388号は,従来技術として、1.8V動作のCMOSトランジスタと3.3V動作のCMOSトランジスタとを含む半導体集積回路装置の基本的製造方法を開示している。 Japanese Patent Application Laid-Open No. 2000-68388 discloses a basic manufacturing method of a semiconductor integrated circuit device including a 1.8V operation CMOS transistor and a 3.3V operation CMOS transistor as a conventional technique.

図10A−10Dは、この基本的製造方法の要部を示す。シリコン基板101にシャロートレンチアイソレーション102が形成され、nウェル103、pウェル104がイオン注入を用いて形成される。薄いゲート絶縁膜105、厚いゲート絶縁膜106を形成した後,ゲート電極層を堆積し,パターニングすることによりゲート電極107を形成する。

10A-10D show the main parts of this basic manufacturing method. A

図10Aに示すように、1.8V動作のnチャネルMOS(NMOS)トランジスタ領域を開口するマスク112を介して、n型不純物たとえばAs+を比較的高濃度に垂直方

向にイオン注入して、n型エクステンション領域114を形成する。同じマスク112を介して、p型不純物たとえばBF2 +を斜めにイオン注入して、n型エクステンション領域114外側にp型ポケット領域116を形成する。

As shown in FIG. 10A, an n-type impurity such as As + is ion-implanted in a vertical direction at a relatively high concentration through a

図10Bに示すように、1.8V動作のpチャネルMOS(PMOS)トランジスタ領域を開口するマスク118を介して、p型不純物たとえばBF2 +を比較的高濃度に垂直方向にイオン注入して、p型エクステンション領域120を形成する。同じマスク118を介して、n型不純物たとえばAs+を斜めにイオン注入して,p型エクステンション領域

120外側にn型ポケット領域122を形成する。

As shown in FIG. 10B, a p-type impurity, for example, BF 2 + is ion-implanted in a vertical direction at a relatively high concentration through a

図10Cに示すように、3.3V動作のNMOSトランジスタ領域を開口するマスク124を介して、n型不純物たとえばP+を比較的低濃度にイオン注入して、ホットキャリ

アを抑制できるn型LDD領域126を形成する。

As shown in FIG. 10C, an n-type LDD region in which hot carriers can be suppressed by ion-implanting n-type impurities such as P + at a relatively low concentration through a

図10Dに示すように、3.3V動作のPMOSトランジスタ領域を開口するマスク128を介して,p型不純物たとえばBF2 +をイオン注入してリーク電流を抑制できるp型LDD領域130を形成する。

As shown in FIG. 10D, p-type impurities such as BF 2 + are ion-implanted through a

3.3V動作トランジスタはゲート長が長く、短チャネル効果は問題とならない。従って、ポケット領域は不要である。PMOSトランジスタにおいては、ポケット領域を形成すると、かえって接合リーク電流が増加する。 The 3.3V operation transistor has a long gate length, and the short channel effect is not a problem. Therefore, no pocket area is required. In the PMOS transistor, when the pocket region is formed, the junction leakage current increases.

その後,ゲート電極側壁上に酸化シリコン膜で形成されたサイドウォールスペーサを形成し、NMOS領域、PMOS領域にそれぞれn型不純物,p型不純物を高濃度にイオン注入し、高濃度ソース/ドレイン領域を形成する。このようにして、1.8Vおよび3.3V動作の多電源電圧CMOS回路が形成される。 Thereafter, a sidewall spacer formed of a silicon oxide film is formed on the side wall of the gate electrode, and n-type impurities and p-type impurities are ion-implanted at high concentrations in the NMOS region and PMOS region, respectively, and high-concentration source / drain regions are formed. Form. In this way, a multi-supply voltage CMOS circuit operating at 1.8V and 3.3V is formed.

特開2000−164727号は、内部回路用の低電圧動作のCMOSトランジスタと、I/Oブロック用の高い耐圧を有する(上記中電圧に対応)CMOSトランジスタとを製造する簡略化された方法を開示している。 Japanese Laid-Open Patent Publication No. 2000-164727 discloses a simplified method for manufacturing a low-voltage operating CMOS transistor for internal circuits and a CMOS transistor having a high breakdown voltage (corresponding to the above-mentioned medium voltage) for I / O blocks. is doing.

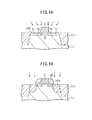

図11A−11Dは、この簡略化された製造方法の要部を示す。p型シリコン基板201に選択的にn型ウェル202が形成され、LOCOS酸化により素子分離領域203が形成される。高電圧動作用の厚さ20nmの厚いゲート絶縁膜205と,低電圧動作用の厚さ7nmの薄いゲート絶縁膜206を形成する。厚さ200nm−300nmのポリシリコン層を堆積し,パターニングすることにより、ゲート長0.2−0.4μmの低電圧用およびゲート長0.5−0.8μmの高電圧用のゲート電極207を形成する。

11A-11D show the main parts of this simplified manufacturing method. An n-

図11Aに示すように、低電圧動作のPMOS領域及び高電圧動作のNMOS領域を覆うレジストマスク208を形成し、低電圧動作のNMOS領域及び高電圧動作のPMOS領域にp型不純物であるボロンを加速エネルギ40keV−60keV、ドーズ量5×1011cm-2−10×1011cm-2の条件で、基板法線から50度−60度の傾きを持たせ、8方向からイオン注入する。p型不純物Bをイオン注された領域209a、209bが

形成される。

As shown in FIG. 11A, a resist

図11Bに示すように、同一マスク208を用い、n型不純物であるP+を、加速エネ

ルギ10keV−30keV、ドーズ量2×1013cm-2−5×1013cm-2の条件でイオン注入する。薄いゲート絶縁膜を有するNMOS領域においては、n型不純物Pがイオン注入され、n型エクステンション領域210aが形成され、厚いゲート絶縁膜205を有するPMOS領域においては、イオン注入されたP+イオンはゲート絶縁膜中に留まり

、シリコン基板に達しないと同公報は断定する。

As shown in FIG. 11B, using the

図11Cに示すように、低電圧NMOS領域及び高電圧PMOS領域を覆うレジストマスク211を形成し、低電圧PMOS領域及び高電圧NMOS領域に対し、n型不純物であるP+イオンを加速エネルギ120keV−170keV、ドーズ量1×1011cm-2

−2×1011cm-2で、基板法線から30度−50度傾いた8方向からイオン注入し、低電圧動作PMOS領域及び高電圧NMOS領域にn型領域212a、212bを形成する。

As shown in FIG. 11C, a resist

Ion implantation is performed at −2 × 10 11 cm −2 from eight directions inclined by 30 ° to 50 ° from the substrate normal, and n-type regions 212a and 212b are formed in the low voltage operation PMOS region and the high voltage NMOS region.

同じマスク211を用い、p型不純物であるB+イオンを加速エネルギ5keV−8k

eV、ドーズ量1−5×1013cm-2でイオン注入し、薄いゲート絶縁膜106を有する低電圧PMOS領域にエクステンション領域214を形成する。この条件においては、高電圧NMOS領域に、イオン注入されたp型不純物B+イオンはゲート絶縁膜中に留まり

、シリコン基板には到達しないと同公報は断定する。

Using the

Ion is implanted at eV and a dose of 1-5 × 10 13 cm −2 to form an

図11Dに示すように、ゲート電極207側壁上にサイドウォールスペーサ215を形成した後、低電圧動作PMOS領域及び高電圧動作PMOS領域を覆うレジストマスク216を形成する。

As shown in FIG. 11D, after a sidewall spacer 215 is formed on the side wall of the

n型不純物であるAs+イオンを、加速エネルギ20keV−40keV、ドーズ量2

.5×1015cm-2でイオン注入し、低電圧動作NMOS領域において高不純物濃度(n+型)ソース/ドレイン領域217a、及び高電圧動作NMOS領域においてn+型ソース/ドレイン領域217bを形成する。

As + ions, which are n-type impurities, are accelerated

. Ion implantation is performed at 5 × 10 15 cm −2 to form a high impurity concentration (n + -type) source / drain region 217a in the low-voltage operation NMOS region and an n + -type source /

同様に、NMOS領域を覆うレジストマスクを形成し、PMOS領域に対してp型不純物をイオン注入し、高不純物濃度のソース/ドレイン領域をイオン注入する。例えば、BF2 +イオンを加速エネルギ30keV−50keV、ドーズ量2×1015cm-2−5×1015cm-2でイオン注入し、高不純物濃度(p+型)ソース/ドレイン領域を形成する。 Similarly, a resist mask covering the NMOS region is formed, p-type impurities are ion-implanted into the PMOS region, and high impurity concentration source / drain regions are ion-implanted. For example, BF 2 + ions are implanted at an acceleration energy of 30 keV-50 keV and a dose of 2 × 10 15 cm −2 −5 × 10 15 cm −2 to form a high impurity concentration (p + -type) source / drain region. .

本発明者等は、特開2000‐164727号公報記載の技術は、後述のように、実施不能であることを見出した。

本発明の目的は、トランジスタと抵抗とを簡略化した工程で作成することのできる半導体装置の製造方法を提供することである。

本発明の他の目的は、複数種類のトランジスタを含む半導体装置の効率的な製造方法を提供することである。

An object of the present invention is to provide a method of manufacturing a semiconductor device in which a transistor and a resistor can be formed by a simplified process.

Another object of the present invention is to provide an efficient method of manufacturing a semiconductor device including a plurality of types of transistors.

本発明のさらに他の目的は、トランジスタとp型不純物をドープした多結晶シリコンの高精度抵抗を簡略化した工程で作製することのできる半導体装置の製造方法を提供することである。 Still another object of the present invention is to provide a method of manufacturing a semiconductor device that can be manufactured in a simplified process of high-precision resistance of a transistor and polycrystalline silicon doped with a p-type impurity.

本発明の他の目的は、短チャネル効果を抑制した低電圧トランジスタと耐圧を向上した高電圧トランジスタとを簡略化した工程で製造する半導体装置の製造方法を提供することである。 Another object of the present invention is to provide a method of manufacturing a semiconductor device in which a low voltage transistor with a suppressed short channel effect and a high voltage transistor with an improved breakdown voltage are manufactured in a simplified process.

本発明の他の目的は、簡略化した工程で作成でき、信頼性高い性能を有するトランジスタと抵抗とを含む半導体装置を提供することである。

本発明の他の目的は、耐圧の優れたトランジスタを含む半導体装置を提供することである。

Another object of the present invention is to provide a semiconductor device including a transistor and a resistor that can be formed by a simplified process and have high reliability.

Another object of the present invention is to provide a semiconductor device including a transistor having an excellent breakdown voltage.

本発明の1観点によれば、

主面を有する半導体基板と、前記半導体基板の主面に形成され、第1、第2の活性領域を画定し、アスペクト比1以上の部分を有する素子分離用溝と、前記素子分離用溝を埋める絶縁体によって形成され、フィールド領域を含む素子分離領域と、前記第1、第2の活性領域表面に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成され、前記第1の活性領域を横断し、高濃度の燐を含む第1のゲート電極と、前記ゲート絶縁膜上に形成され、前記第2の活性領域を横断し、p型不純物を含む第2のゲート電極と、前記フィールド領域上に、前記第2のゲート電極と同じ層で形成された抵抗素子と、前記抵抗素子の表面の一部に形成されたサリサイドブロック層と、前記第1、第2のゲート電極の側壁上に形成されたサイドウォールスペーサと、前記第1の活性領域のサイドウォール外方に形成された高濃度の燐を含む第1のソース/ドレイン領域と、前記第2の活性領域のサイドウォール外方に形成されたp型不純物を含む第2のソース/ドレイン領域と、前記抵抗素子のサリサイドブロック層以外の表面、前記第1、第2のソース/ドレイン領域の少なくとも一部の表面、前記第1、第2のゲート電極の少なくとも一部の表面に形成されたシリサイド層と、を有する半導体装置

が提供される。

According to one aspect of the present invention,

A semiconductor substrate having a main surface, an element isolation groove formed on the main surface of the semiconductor substrate, defining first and second active regions and having a portion with an aspect ratio of 1 or more, and the element isolation groove An isolation region including a field region, a gate insulating film formed on the surfaces of the first and second active regions, and a first active region formed on the gate insulating film. A first gate electrode containing a high concentration of phosphorus, a second gate electrode formed on the gate insulating film, crossing the second active region and containing a p-type impurity, and the field On the region, a resistive element formed of the same layer as the second gate electrode, a salicide block layer formed on a part of the surface of the resistive element, and on the sidewalls of the first and second gate electrodes Side wall space formed on A first source / drain region containing high-concentration phosphorus formed outside the sidewall of the first active region, and a p-type impurity formed outside the sidewall of the second active region A second source / drain region including the surface of the resistive element other than the salicide block layer, at least a part of the surface of the first and second source / drain regions, and the first and second gate electrodes. There is provided a semiconductor device having a silicide layer formed on at least a part of the surface.

本発明の他の観点によれば、

(a)半導体基板に第1導電型の第1、第2の活性領域、および第2導電型の第3、第4の活性領域を形成する工程と、(b)前記第1、第3の活性領域上に第1の厚さのゲート絶縁膜を形成する工程と、(c)前記第2、第4の活性領域上に、第1の厚さより著しく薄い第2の厚さのゲート絶縁膜を形成する工程と、(d)前記第1−第4の活性領域のゲート絶縁膜の上にそれぞれ第1−第4のゲート電極を形成し、前記ゲート絶縁膜は残存させる工程と、(e)前記第1、第4の活性領域に対し、第2の厚さのゲート絶縁膜は貫通し、第1の厚さのゲート絶縁膜は貫通しないように、第1導電型不純物の第1のイオン注入を行う工程と、(f)前記第1、第4の活性領域に対し、ゲート絶縁膜を貫通する第2導電型不純物の第2のイオン注入を行う工程と、(g)前記第2、第3の活性領域に対し、第2の厚さのゲート絶縁膜は貫通し、第1の厚さのゲート絶縁膜は貫通しないように、第2導電型不純物の第3のイオン注入を行う工程と、(h)前記第2、第3の活性領域に対し、ゲート絶縁膜を貫通する第1導電型不純物の第4のイオン注入を行う工程と、(i)半導体基板全面に絶縁層を堆積し、異方性エッチングを行い、ゲート電極側壁上にサイドウォールスペーサを形成すると共に、露出したゲート絶縁膜を除去する工程と、(j)前記第1、第2の活性領域に前記サイドウォールスペーサをマスクとして、第2導電型不純物の第5のイオン注入を行う工程と、(k)前記第3、第4の活性領域に前記サイドウォールスペーサをマスクとして、第1導電型不純物の第6のイオン注入を行う工程と、を有する半導体装置の製造方法

が提供される。

According to another aspect of the invention,

(A) forming a first conductivity type first and second active region and a second conductivity type third and fourth active region on a semiconductor substrate; and (b) the first and third active regions. Forming a gate insulating film having a first thickness on the active region; and (c) a gate insulating film having a second thickness that is significantly thinner than the first thickness on the second and fourth active regions. (D) forming first to fourth gate electrodes on the gate insulating films of the first to fourth active regions, respectively, and leaving the gate insulating film; ) The first conductivity type impurity first electrode is formed so as to penetrate the first and fourth active regions through the second thickness gate insulating film and not through the first thickness gate insulating film. (F) performing a second ion implantation of a second conductivity type impurity penetrating the gate insulating film into the first and fourth active regions. And (g) a second conductivity type so that the second thickness of the gate insulating film penetrates the second and third active regions, and the first thickness of the gate insulating film does not penetrate. A step of performing a third ion implantation of impurities; (h) a step of performing a fourth ion implantation of a first conductivity type impurity penetrating the gate insulating film into the second and third active regions; i) depositing an insulating layer on the entire surface of the semiconductor substrate, performing anisotropic etching, forming a sidewall spacer on the side wall of the gate electrode, and removing the exposed gate insulating film; and (j) the first, Using the sidewall spacer as a mask in the second active region, performing a fifth ion implantation of a second conductivity type impurity; and (k) using the sidewall spacer as a mask in the third and fourth active regions. , Sixth ion of first conductivity type impurity The method of manufacturing a semiconductor device having a step of performing input is provided.

本発明の別の観点によれば、

半導体基板と、前記半導体基板に形成された第1導電型の第1、第2の活性領域と、前記半導体基板に形成された第2導電型の第3、第4の活性領域と、前記第1、第3の活性領域上に形成された第1の厚さのゲート絶縁膜と、前記第2、第4の活性領域上に形成された第1の厚さより著しく薄い第2の厚さのゲート絶縁膜と、前記第1−第4の活性領域のゲート絶縁膜の上にそれぞれ形成された第1−第4のゲート電極と、前記第1−第4のゲート電極側壁上に形成された絶縁材料のサイドウォールスペーサと、前記第1、第2の活性領域の前記サイドウォールスペーサ外方に形成された第2導電型の高不純物濃度の第1、第2のソース/ドレイン領域と、前記第3、第4の活性領域の前記サイドウォールスペーサ外方に形成された第1導電型の高不純物濃度の第3、第4のソース/ドレイン領域と、前記第1の活性領域のサイドウォールスペーサ下方に形成され、前記第1のソース/ドレイン領域に連続する第2導電型のLDD領域と、前記第4の活性領域のサイドウォールスペーサ下方に形成され、前記第4のソース/ドレイン領域に連続する第1導電型のエクステンション領域と、前記第4の活性領域の前記第1導電型のエクステンション領域を取り囲むように形成された第2導電型のポケット領域と、を有し、前記ゲート絶縁膜は前記サイドウォールスペーサ下方まで延在し、前記高不純物濃度のソース/ドレイン領域上方までは延在せず、前記第1のゲート電極側壁のサイドウォールスペーサ下の前記第1の活性領域およびその上の第1の厚さのゲート絶縁膜中の第2導電型不純物濃度分布と、前記第4のゲート電極側壁のサイドウォールスペーサ下の前記第4の活性領域およびその上の第2の厚さのゲート絶縁膜中の第2導電型不純物濃度分布とが実質的に等しい半導体装置

が提供される。

According to another aspect of the invention,

A semiconductor substrate; first and second active regions of a first conductivity type formed on the semiconductor substrate; third and fourth active regions of a second conductivity type formed on the semiconductor substrate; 1. A gate insulating film having a first thickness formed on the third active region, and a second thickness that is significantly smaller than the first thickness formed on the second and fourth active regions. Gate insulating films, first to fourth gate electrodes formed on the gate insulating films of the first to fourth active regions, respectively, and formed on sidewalls of the first to fourth gate electrodes. A sidewall spacer made of an insulating material; and first and second source / drain regions of high conductivity concentration of the second conductivity type formed outside the sidewall spacer of the first and second active regions; The first conductivity type high formed outside the sidewall spacer in the third and fourth active regions. Pure source concentration third and fourth source / drain regions, and a second conductivity type LDD region formed below the side wall spacer of the first active region and continuing to the first source / drain region; A first conductivity type extension region formed under the side wall spacer of the fourth active region and continuing to the fourth source / drain region; and the first conductivity type extension of the fourth active region. A pocket region of a second conductivity type formed so as to surround the region, and the gate insulating film extends below the sidewall spacer and extends above the high impurity concentration source / drain region. Without the second conductive type in the first active region under the side wall spacer on the side wall of the first gate electrode and the first thickness gate insulating film thereon. The material concentration distribution and the second conductivity type impurity concentration distribution in the fourth active region under the side wall spacer on the side wall of the fourth gate electrode and the second thickness gate insulating film thereon are substantially the same. A semiconductor device equal to is provided.

本発明の他の観点によれば、

(a)半導体基板に第1導電型の第1の活性領域を形成する工程と、(b)前記第1の活性領域上に第1のゲート絶縁膜を形成する工程と、(c)前記第1のゲート絶縁膜の上に第1のゲート電極を形成する工程と、(d)前記第1の活性領域に対し、ゲート電極をマスクとして第2導電型の不純物を基板法線から傾いた複数の方向からイオン注入する工程と、(e)前記半導体基板全面に絶縁層を堆積し、異方性エッチングを行い、ゲート電極側壁上にサイドウォールスペーサを形成する工程と、(f)前記第1のゲート電極および前記サイドウォールスペーサをマスクとして、前記第1の活性領域に第2導電型の不純物を高濃度にイオン注入する工程と、を有する半導体装置の製造方法

が提供される。

According to another aspect of the invention,

(A) forming a first conductive type first active region on the semiconductor substrate; (b) forming a first gate insulating film on the first active region; and (c) the first A step of forming a first gate electrode on one gate insulating film; and (d) a plurality of second conductivity type impurities inclined from a substrate normal line with the gate electrode as a mask with respect to the first active region. (E) depositing an insulating layer on the entire surface of the semiconductor substrate, performing anisotropic etching, and forming sidewall spacers on the side walls of the gate electrode; (f) the first And a step of ion-implanting a second conductivity type impurity in the first active region at a high concentration using the gate electrode and the side wall spacer as a mask.

本発明の他の観点によれば、

半導体基板と、前記半導体基板内に画定された第1導電型の活性領域と、前記活性領域上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成されたゲート電極と、前記ゲート電極側壁上に形成された絶縁性サイドウォールスペーサと、前記活性領域の前記ゲート電極端部下方から前記絶縁性サイドウォールスペーサ下方まで延在するように形成され、前記ゲート電極端部下方から前記ゲート電極端下方を越え、前記ゲート電極より外方までの領域で面内方向で第2導電型の不純物濃度が単調増大する濃度勾配を有するLDD領域と、前記サイドウォールスペーサ外方の前記活性領域内に形成され、前記LDD領域に連続する第2導電型の高不純物濃度ソース/ドレイン領域と、を有する半導体装置

が提供される。

According to another aspect of the invention,

A semiconductor substrate, an active region of a first conductivity type defined in the semiconductor substrate, a gate insulating film formed on the active region,

A gate electrode formed on the gate insulating film; an insulating sidewall spacer formed on a side wall of the gate electrode; and extending from below the gate electrode end of the active region to below the insulating sidewall spacer. A concentration gradient in which the impurity concentration of the second conductivity type monotonously increases in an in-plane direction in a region extending from below the gate electrode end to below the gate electrode end and outward from the gate electrode. There is provided a semiconductor device having an LDD region and a second impurity type high impurity concentration source / drain region formed in the active region outside the sidewall spacer and continuing to the LDD region.

本発明者等は、0.13μmルールのホトリソグラフィを用い、SRAMを含む低電圧トランジスタ、フラッシュメモリ、フラッシュメモリ制御用の高電圧トランジスタ、超高速入出力回路用中電圧トランジスタ、アナログ回路用の高精度抵抗素子、ESD保護用の拡散抵抗素子等を同一チップ上に搭載した半導体の開発を行っている。 The present inventors use 0.13 μm rule photolithography, low voltage transistors including SRAM, flash memory, high voltage transistors for flash memory control, medium voltage transistors for ultra high speed input / output circuits, high voltages for analog circuits. We are developing semiconductors that include precision resistance elements, diffused resistance elements for ESD protection, etc. on the same chip.

まず、本発明者らの行なった特開2000−164727号公報開示の技術の解析を説明する。

特開2000‐164727号公報は、厚さ20nmのゲート絶縁膜に対し、燐(P+

)イオンを加速エネルギ10keV−30keV、ドーズ量2×1013cm-2−5×1013cm-2でイオン注入しても、イオン注入されたP+イオンはシリコン基板に到達しない

と断定している。

First, analysis of the technique disclosed in Japanese Patent Laid-Open No. 2000-164727 performed by the present inventors will be described.

Japanese Unexamined Patent Publication No. 2000-164727 discloses phosphorous (P +) for a gate insulating film having a thickness of 20 nm.

) Even if ions are implanted at an acceleration energy of 10 keV-30 keV and a dose of 2 × 10 13 cm −2 −5 × 10 13 cm −2 , it is determined that the ion-implanted P + ions do not reach the silicon substrate. Yes.

図12は、イオン注入直後の不純物濃度分布を示すグラフである。曲線Pは、加速エネルギ10keV,ドーズ量2×1013cm-2の条件でイオン注入したPの不純物分布をシミュレーションした結果である。厚いゲート酸化膜の領域をOXで示す。同図から明らかなように、イオン注入された不純物Pは、シリコン基板中にも高濃度で分布する。 FIG. 12 is a graph showing the impurity concentration distribution immediately after ion implantation. A curve P is a result of simulating an impurity distribution of P ion-implanted under conditions of an acceleration energy of 10 keV and a dose of 2 × 10 13 cm −2 . A thick gate oxide region is indicated by OX. As is apparent from the figure, the ion-implanted impurity P is also distributed at a high concentration in the silicon substrate.

なお、同一領域に対し、B+イオンを、加速エネルギ40keV−60keV、ドーズ

量5×1011cm-2−10×1011cm-2、イオン注入角度50°−60°で8回イオン注入している。このイオン注入によるB分布も合わせてシミュレーションした。

In the same region, B + ions are implanted eight times at an acceleration energy of 40 keV-60 keV, a dose of 5 × 10 11 cm −2 -10 × 10 11 cm −2 , and an ion implantation angle of 50 ° -60 °. ing. The B distribution by this ion implantation was also simulated.

図12において、Bを加速エネルギ60keV、ドーズ量8×1012cm-2でイオン注入した場合、及びBを加速エネルギ40keV、ドーズ量8×1012cm-2でイオン注入した場合のB分布を合わせて示す。 In FIG. 12, the distribution of B when B is ion-implanted with an acceleration energy of 60 keV and a dose of 8 × 10 12 cm −2 , and when B is ion-implanted with an acceleration energy of 40 keV and a dose of 8 × 10 12 cm −2. Shown together.

図から明らかなように、Bイオン注入は、シリコン基板中にp型不純物濃度分布を形成するが、その表面部分には、Pイオンのイオン注入により、ほぼ2桁高濃度のn型不純物濃度領域が形成されている。このように、イオン注入された燐イオンは、低耐圧のNMOS領域では基板に注入されるが、高耐圧のPMOS領域では厚いゲート酸化膜中に留まり、シリコン基板に到達しないとの記載は根拠のないものであることが分る。 As is apparent from the figure, the B ion implantation forms a p-type impurity concentration distribution in the silicon substrate, but an n-type impurity concentration region approximately two orders of magnitude higher on the surface portion by ion implantation of P ions. Is formed. As described above, it is stated that phosphorus ions implanted into the substrate are implanted in the substrate in the low breakdown voltage NMOS region, but remain in the thick gate oxide film in the high breakdown voltage PMOS region and do not reach the silicon substrate. It turns out that it is not.

図11Dの工程においては、ゲート絶縁膜を介してAsイオンを注入し、高濃度ソース/ドレイン領域217a、217bを形成している。このイオン注入の加速エネルギは、厚いゲート絶縁膜を介しても高濃度ソース/ドレイン領域217bが形成されるように高く選択する必要がある。すると、薄いゲート絶縁膜を有する低電圧NMOSトランジスタ領域においては、ソース/ドレイン領域217aがより深く形成されることになる。深いソース/ドレイン領域間には短チャネル効果が発生し易くなる。

In the step of FIG. 11D, As ions are implanted through a gate insulating film to form high concentration source /

特開2000−164727号公報は、トランジスタのオフリーク(短チャネル効果)の増加を抑え、ホットキャリア耐圧の向上を達成することを目的としているが、この目的がどのように達成されるかは何ら説明していない。 Japanese Patent Application Laid-Open No. 2000-164727 aims to suppress an increase in off-leakage (short channel effect) of a transistor and achieve an improvement in hot carrier breakdown voltage. How can this object be achieved? Not done.

結晶シリコンの抵抗値は温度と共に低下し、温度変化する環境も高精度を維持する抵抗を形成することは難しい。p型多結晶シリコンの抵抗値は、最も温度変化が少ない。高精度の抵抗はp型多結晶シリコンで形成することが好ましい。 The resistance value of crystalline silicon decreases with temperature, and it is difficult to form a resistor that maintains high accuracy even in a temperature changing environment. The resistance value of p-type polycrystalline silicon has the least temperature change. The high-precision resistor is preferably formed of p-type polycrystalline silicon.

論理回路、SRAM等に用いる低電圧トランジスタは、なるべく高集積度で形成することが望まれる。素子間距離縮小の観点から素子分離領域幅の狭い素子分離用溝を形成し、シャロートレンチアイソレーションで素子分離領域を形成することが好ましい。 Low voltage transistors used in logic circuits, SRAMs, etc. are desired to be formed as highly integrated as possible. From the viewpoint of reducing the inter-element distance, it is preferable to form an element isolation trench having a narrow element isolation region width and to form the element isolation region by shallow trench isolation.

0.13μm以下のルールを用いた半導体素子では、STI用溝のアスペクト比が1以上となることを許容することが望まれる。アスペクト比が1以上の部分が生じると、熱TEOS−CVDで堆積した酸化シリコン膜では溝がうまく埋め込めず、ボイドが生じてしまう。アスペクト比が1以上の溝を埋め込むためには、現在の技術では、高密度プラズマ(HDP)CVDによる酸化シリコン膜を用いることができる。 In a semiconductor device using a rule of 0.13 μm or less, it is desirable to allow the aspect ratio of the STI trench to be 1 or more. When a portion having an aspect ratio of 1 or more is generated, the groove cannot be filled well in the silicon oxide film deposited by thermal TEOS-CVD, and a void is generated. In order to fill a groove having an aspect ratio of 1 or more, a silicon oxide film formed by high-density plasma (HDP) CVD can be used in the current technology.

トランジスタの寄生抵抗を低減するためには、サリサイド構造を用いることが好ましい。また、低電圧動作とするために、低い閾値Vtを有するトランジスタを形成することが好ましく、NMOSトランジスタのゲート電極はn型多結晶シリコン、PMOSトランジスタのゲート電極は、p型多結晶シリコンで構成するデュアルゲート構造を採用する。 In order to reduce the parasitic resistance of the transistor, a salicide structure is preferably used. In order to operate at a low voltage, it is preferable to form a transistor having a low threshold Vt. The gate electrode of the NMOS transistor is composed of n-type polycrystalline silicon, and the gate electrode of the PMOS transistor is composed of p-type polycrystalline silicon. Adopt dual gate structure.

次に本発明の基礎となる予備実験について説明する。

図1Aは、SRAMの等価回路を示す。2つのドライバトランジスタTdは、nチャネルMOSトランジスタであり、2つのpチャネル負荷トランジスタTlと直列にインバータ接続されている。2つのインバータ接続の相互接続点は、nチャネルトランスファMOSトランジスタTtを介して出力される。又、各インバータ接続の出力電圧は、対向するインバータ接続のゲート電極にクロス配線されている。

Next, a preliminary experiment as the basis of the present invention will be described.

FIG. 1A shows an equivalent circuit of an SRAM. The two driver transistors Td are n-channel MOS transistors, and are inverter-connected in series with the two p-channel load transistors Tl. The interconnection point between the two inverters is output via the n-channel transfer MOS transistor Tt. The output voltage of each inverter connection is cross-wired to the gate electrode of the opposite inverter connection.

図1Bは、作成したSRAMセルのユニットセルの平面図を示す。各トランジスタTにおいて、活性領域の上に右下がりのハッチングを付して示したゲート電極(ワード線)が配置され、その上方で、左下がりのハッチングを付して示した金属配線が相互接続を形成している。活性領域間の素子分離領域は、STIによって形成した。 FIG. 1B shows a plan view of a unit cell of the created SRAM cell. In each transistor T, a gate electrode (word line) shown with a right-down hatching is arranged on the active region, and above that, a metal wiring shown with a left-down hatching is interconnected. Forming. The element isolation region between the active regions was formed by STI.

STI用溝は、アスペクト比が1以上の部分を有し、HDP−CVDで形成した酸化シリコン層によって埋め込んだ。ゲート電極作成後、サイドウォールスペーサを形成し、nチャネルトランジスタ、pチャネルトランジスタの各高濃度ソース/ドレイン形成用イオン注入を行なった。nチャネルMOSトランジスタの高濃度ソース/ドレイン領域には、Asをイオン注入した。その後、基板表面にサリサイド処理を行なった。 The STI trench had a portion with an aspect ratio of 1 or more and was filled with a silicon oxide layer formed by HDP-CVD. After forming the gate electrode, sidewall spacers were formed, and ion implantation for forming high-concentration source / drain of the n-channel transistor and p-channel transistor was performed. As ions were implanted into the high concentration source / drain regions of the n-channel MOS transistor. Thereafter, salicide treatment was performed on the substrate surface.

図1Cは、低電圧で動作させたSRAMの歩留りを示すグラフである。ソース/ドレイン領域をAsイオン注入で形成し、その後の活性化を950℃のラピッドサーマルアニール(RTA)で行なったサンプル(As−SD 950C RTA)は、歩留りが極端に悪かった。

FIG. 1C is a graph showing the yield of SRAM operated at a low voltage. The sample (As-

欠陥を生じたサンプルを観察すると、図1Aの等価回路図において太線で示した部分にディスロケーション等の結晶欠陥が見出された。nチャネルトランジスタに欠陥が生じており、pチャネルトランジスタには欠陥が生じていない。 When the sample in which the defect was generated was observed, crystal defects such as dislocation were found in a portion indicated by a thick line in the equivalent circuit diagram of FIG. 1A. The n-channel transistor has a defect, and the p-channel transistor has no defect.

活性化アニールを940℃のRTAとしたサンプル(As−SD 940C

RTA)は、歩留りがかなり回復したが、絶対値は依然としてかなり低く、不満足な結果である。さらに、アニール温度を低下させれば、歩留りを向上することが期待できるが、処理に長時間を必要とすることになる。

Sample (As-

RTA) is an unsatisfactory result, although the yield has recovered considerably but the absolute value is still quite low. Furthermore, if the annealing temperature is lowered, the yield can be expected to be improved, but a long time is required for the treatment.

サンプル(P−SD)は、Asの代りにPを用いて高濃度ソース/ドレイン領域を形成した。他の条件はサンプル(As−SD 950C RTA)と同一とした。この場合(P−SD)、歩留りが大幅に改善し、絶対値も満足できるものとなった。

In the sample (P-SD), high-concentration source / drain regions were formed using P instead of As. Other conditions were the same as the sample (As-

このように、HDP‐CVDによる酸化シリコン層でSTI用溝を埋め込み、活性領域内に微細化したnチャネルMOSトランジスタを形成する場合、高濃度ソース/ドレイン領域はAsでドープすると歩留りが非常に低いが、Pでドープすると、Asでドープした時と比べ、歩留りが大幅に改善されることが分った。 Thus, when the STI trench is filled with a silicon oxide layer formed by HDP-CVD and a miniaturized n-channel MOS transistor is formed in the active region, the yield is very low when the high concentration source / drain region is doped with As. However, when doped with P, it was found that the yield was significantly improved compared to when doped with As.

この結果は、以下のように考えることができるであろう。HDP‐CVD酸化シリコン層は、強いストレスを与えることが知られている。シリコン結晶にAsをイオン注入すると、原子半径の大きなAsは、シリコン結晶をアモルファス化させる。活性化処理においてアモルファス化された結晶が回復しようとする。AsとSiとは原子半径が異なるため、結晶欠陥が生じ易い。 This result can be considered as follows. The HDP-CVD silicon oxide layer is known to give a strong stress. When As is ion-implanted into a silicon crystal, As having a large atomic radius makes the silicon crystal amorphous. Crystals made amorphous in the activation process tend to recover. Since As and Si have different atomic radii, crystal defects are likely to occur.

特に強いストレスを受けているシリコン中においては、Si原子の位置がずれ易い。又、強いストレスを受けている状態において欠陥が多数生じると、格子間シリコン原子は容易に移動し、欠陥が成長し易くなる。欠陥がディスロケーション等に成長すると、リークパスが発生し、リーク電流が流れる。 In silicon that is particularly stressed, the position of Si atoms tends to shift. In addition, when a large number of defects are generated in a state of being subjected to strong stress, the interstitial silicon atoms easily move and the defects are likely to grow. When a defect grows in a dislocation or the like, a leak path occurs and a leak current flows.

ドライバトランジスタTdと負荷トランジスタTlとの相互接続点がハイの状態において、ドライバトランジスタTdにリーク電流が流れると、相互接続点の電位をハイからローに引き下げようとする。負荷トランジスタTlが相互接続点の電位を高く維持できれば誤動作とはならないが、低電圧動作のPMOSトランジスタは駆動能力が弱く、ハイ状態からロー状態への変換を許容してしまう。 When a leakage current flows through the driver transistor Td in a state where the interconnection point between the driver transistor Td and the load transistor Tl is high, the potential at the interconnection point is lowered from high to low. If the load transistor Tl can keep the potential at the interconnection point high, no malfunction occurs, but the low-voltage operation PMOS transistor has a weak driving capability and allows the conversion from the high state to the low state.

高濃度ソース/ドレイン領域をPドープで作成した場合、歩留りが大幅に改善したことは、原子半径の小さなPを用いると、上述のような結晶欠陥の発生、ディスロケーションの成長などを防止することが可能となるためであろう。 When the high-concentration source / drain region is formed by P doping, the yield is greatly improved. When P having a small atomic radius is used, the generation of crystal defects and the growth of dislocation as described above are prevented. This will be possible.

そこで、nチャネルMOSトランジスタの高濃度ソース/ドレイン領域は、Pドープで形成することとし、アナログ抵抗をp型多結晶シリコン層で形成することとした。

図2Aは、作成したサンプルの構成を概略的に示す。シリコン基板にHDP−CVDでSTIを形成し、必要なウェルを形成した。厚さの異なるゲート絶縁膜を形成し、その上に多結晶シリコン層を堆積した。多結晶シリコン層をパターニングして、ゲート電極G、抵抗素子Rを形成した。

Therefore, the high-concentration source / drain region of the n-channel MOS transistor is formed by P doping, and the analog resistance is formed by a p-type polycrystalline silicon layer.

FIG. 2A schematically shows the structure of the created sample. STI was formed on the silicon substrate by HDP-CVD, and necessary wells were formed. Gate insulating films having different thicknesses were formed, and a polycrystalline silicon layer was deposited thereon. The polycrystalline silicon layer was patterned to form a gate electrode G and a resistance element R.

2.5V動作トランジスタN−MVは、ゲート絶縁膜上にn型多結晶シリコンで形成されたゲート電極G、ゲート電極側壁上にサイドウォールスペーサSWを有し、ソース/ドレイン領域は浅い接合のエクステンション領域EXと高濃度領域HDDで構成されている。ソース/ドレイン領域の一方には、部分的にサリサイドブロック層SB1が形成されている。 The 2.5-V operation transistor N-MV has a gate electrode G formed of n-type polycrystalline silicon on a gate insulating film, a sidewall spacer SW on the side wall of the gate electrode, and a source / drain region having a shallow junction extension. The area EX and the high density area HDD are configured. A salicide block layer SB1 is partially formed in one of the source / drain regions.

1.2V動作トランジタN−LVは、薄いゲート絶縁膜上に、2.5Vトランジスタのゲート電極と同一の多結晶シリコン層で形成されたゲート電極G、サイドウォールスペーサSWと、浅い接合を有するn型エクステンション領域EXとその周囲に形成されたp型ポケット領域PKと高濃度領域HDDで形成される。なお、N−MV、N−LVとも、種々のゲート長のサンプルを作成した。 The 1.2V operation transistor N-LV has a shallow junction with a gate electrode G formed of the same polycrystalline silicon layer as the gate electrode of the 2.5V transistor, a side wall spacer SW, and a thin gate insulating film. A type extension region EX, a p-type pocket region PK formed therearound, and a high concentration region HDD are formed. Samples with various gate lengths were prepared for both N-MV and N-LV.

素子分離領域STI上には、p型多結晶シリコンで形成された抵抗Rが形成される。抵抗Rの抵抗部上には、サリサイドブロック層SB1と同一絶縁層で形成された、シリサイド反応を防止するサリサイドブロック層SB2が形成されている。サリサイドブロック層は、TEOSを主原料ガスとする熱CVDにより、基板温度620℃で、数10分〜100分程度で、厚さ50nmに成長した。 A resistor R made of p-type polycrystalline silicon is formed on the element isolation region STI. A salicide block layer SB2 that is formed of the same insulating layer as the salicide block layer SB1 and prevents a silicide reaction is formed on the resistance portion of the resistor R. The salicide block layer was grown to a thickness of 50 nm at a substrate temperature of 620 ° C. for several tens of minutes to 100 minutes by thermal CVD using TEOS as a main raw material gas.

サリサイドブロック層SB1、SB2外に露出しているシリコン表面上には、540℃、30秒の1次反応RTA、840℃、30秒の2次反応RTAを用いて、コバルトシリサイド層SLが形成され、低抵抗化を行なっている。なお、サリサイドブロック層SBを形成せず、サリサイド処理を行なったサンプルも作成した。 A cobalt silicide layer SL is formed on the silicon surface exposed outside the salicide block layers SB1 and SB2 using a primary reaction RTA at 540 ° C. for 30 seconds and a secondary reaction RTA at 840 ° C. for 30 seconds. The resistance is reduced. In addition, the sample which did not form salicide block layer SB but performed salicide processing was also created.

図2Bは、作成したNMOSトランジスタの閾値Vtのゲート長に対する依存性を示すグラフである。白抜きの測定スポットを結ぶ曲線p1、p2は、サリサイドブロック層を形成しなかったサンプルを示し、中実の測定スポットを結ぶ曲線x1、x2はサリサイドブロック層を形成したサンプルを示す。2.5Vトランジスタp1、x1においては、閾値調整用イオン注入条件に若干の差があり、ゲート長1μm以上では、プロットの差は有意義な差を意味しない。しかし、サリサイドブロック層を形成した時、0.25〜0.3μm以下で閾値の急激な低下が顕著となった。しかし、その差はそれほど大きくはない。 FIG. 2B is a graph showing the dependence of the threshold value Vt of the created NMOS transistor on the gate length. Curves p1 and p2 connecting the white measurement spots indicate samples in which the salicide block layer is not formed, and curves x1 and x2 connecting the solid measurement spots indicate samples in which the salicide block layer is formed. In the 2.5V transistors p1 and x1, there is a slight difference in the threshold adjustment ion implantation conditions. When the gate length is 1 μm or more, the difference in plots does not mean a significant difference. However, when the salicide block layer was formed, the threshold was drastically lowered at 0.25 to 0.3 μm or less. However, the difference is not so great.

サリサイドブロック層を形成しない1.2Vトランジスタの特性p2は、予測されるものであった。サリサイドブロック層を形成したサンプルのスポットx2は、サンプルp2と比較して、ゲート長が1μm以上の領域でも、ゲート長が短くなるにつれ、閾値が減少し、ゲート長の減少と共に閾値の減少率も大きくなっている。ゲート長0.2μm以下では、トランジスタとして機能しない。

The characteristic p2 of the 1.2V transistor that does not form the salicide block layer was expected. The sample spot x2 in which the salicide block layer is formed has a threshold value that decreases as the gate length becomes shorter even in the region where the gate length is 1 μm or more compared to the sample p2, and the reduction rate of the threshold value decreases as the gate length decreases. It is getting bigger. When the gate length is 0.2 μm or less, it does not function as a transistor.

ポケット領域を形成しない2.5Vトランジスタにおいては閾値低下を生じないゲート長(0.35〜1μm)においても、ポケット領域を形成し、シリサイド化した1.2Vトランジスタは閾値低下を示している。サリサイドブロック層を形成することにより、予期せざる障害が発生したことになる。 In a 2.5V transistor that does not form a pocket region, even when the gate length (0.35 to 1 μm) does not cause a decrease in threshold, a silicided 1.2V transistor that exhibits a decrease in threshold shows a decrease in threshold. By forming the salicide block layer, an unexpected failure has occurred.

IEEE TRANSACTIONS ONELECTRON DEVICES, Vol. 49, NO. 11, November 2002, pp 2031は、濃度7×1020cm-3にドープしたPは、異常拡散を示すことを報告している。

サリサイドブロック層は620℃、数十分〜100分程度のCVDで作成している。CVDの加熱工程により、Pが異常拡散し、短チャネルトランジスタにおいて閾値を低下させてしまったことが考えられる。そこで、サリサイドブロック層のCVD温度を、600℃のTEOSを用いたCVDから400℃のプラズマCVDに変更し、温度を低下させたところ、閾値の急激な低下は発生しなかった。

IEEE TRANSACTIONS ONELECTRON DEVICES, Vol. 49, NO. 11, November 2002, pp 2031 reports that P doped to a concentration of 7 × 10 20 cm −3 exhibits anomalous diffusion.

The salicide block layer is formed by CVD at 620 ° C. for several tens of minutes to 100 minutes. It is conceivable that P is abnormally diffused by the CVD heating process and the threshold value is lowered in the short channel transistor. Therefore, when the CVD temperature of the salicide block layer was changed from CVD using TEOS at 600 ° C. to plasma CVD at 400 ° C. and the temperature was lowered, the threshold value did not drop sharply.

Pの異常拡散を低減し、閾値変動を防止するためには、Pドープの高濃度ソース/ドレイン領域を形成した後、ある程度以上の時間を必要とする熱処理の温度は低く選択して、拡散を抑えることが有効であろう。 In order to reduce the abnormal diffusion of P and prevent threshold fluctuation, the temperature of the heat treatment that requires a certain amount of time after the P-doped high-concentration source / drain regions is formed is selected to be low. It would be effective to suppress it.

620℃は、非晶質シリコンが結晶化する温度より高い。このような温度では異常拡散が発生すると考えられる。結晶化温度よりも十分に低い500℃以下の温度であれば、異常拡散を防止できるであろう。 620 ° C. is higher than the temperature at which amorphous silicon crystallizes. It is considered that abnormal diffusion occurs at such temperatures. If the temperature is below 500 ° C., which is sufficiently lower than the crystallization temperature, abnormal diffusion will be prevented.

本実験においては、サリサイド処理の2次反応は840℃のRTAで行なっている。しかし、その処理時間は30秒と十分に短く、不純物の拡散は大きくない。絶縁膜を成長するCVDにおいては、そのような短時間処理は困難である。ウエハの温度安定化、成膜、ガス排気等を含めて、数十〜100分程度の処理時間を要する。不純物活性化のためのRTAは、さらに高温である。しかし、その処理時間は数秒以下とさらに短く、不純物の拡散は大きくない。こうしてサリサイドブロック層成長の温度が最も重要な要因となる。 In this experiment, the secondary reaction of the salicide treatment is performed at 840 ° C. RTA. However, the processing time is sufficiently short as 30 seconds, and the diffusion of impurities is not large. In CVD for growing an insulating film, such a short-time treatment is difficult. A processing time of about several tens to 100 minutes is required including temperature stabilization of the wafer, film formation, gas exhaust, and the like. RTA for impurity activation is at a higher temperature. However, the processing time is even shorter, a few seconds or less, and the diffusion of impurities is not large. Thus, the temperature of salicide block layer growth is the most important factor.

なお、このような異常拡散は、不純物としてAsを用いた場合には非常に小さく、不純物としてBを用いた場合には全く問題とならないこともトランジスタの特性から実験的に確認した。 It has been experimentally confirmed from the transistor characteristics that such abnormal diffusion is very small when As is used as an impurity and does not cause any problem when B is used as an impurity.

以上の実験結果から、n型MOSトランジスタのソース/ドレイン領域に不純物として燐(P)を用いることで、ストレスの大きなSTIを用いて微細化しても、SRAMの低電圧不良という非公知の問題を解決できることが判った。 From the above experimental results, by using phosphorus (P) as an impurity in the source / drain region of the n-type MOS transistor, even when miniaturization is performed using STI having a large stress, an unknown problem of low voltage failure of the SRAM is obtained. It turns out that it can be solved.

抵抗を形成するためにサリサイドブロック層を用いることにより、工程増加を最小にして抵抗素子を形成することできる。サリサイドブロック層を500℃以下の低温で形成することにより、ソース/ドレイン領域のPの異常拡散を抑制し、0.2μm以下のゲート長を有するNMOSトランジスタの短チャネル効果急増という非公知の問題を解決できることも判った。 By using the salicide block layer to form the resistance, the resistance element can be formed with a minimum increase in the number of steps. By forming the salicide block layer at a low temperature of 500 ° C. or lower, an abnormal diffusion of P in the source / drain region is suppressed, and the short channel effect of the NMOS transistor having a gate length of 0.2 μm or less is rapidly increased. I also found that it could be solved.

以下、これらの発見に基づく実施例を説明する。

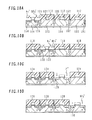

図3Aに示すように、シリコン基板11の表面上に、厚さ15nmの酸化膜、厚さ110nmの窒化膜の積層等によるハードマスク層HMをCVDにより堆積し、その表面上に素子分離用溝を画定するホトレジストマスクPR1を形成する。ホトレジストマスクPR1をマスクとし、ハードマスク層HMをエッチングし、続いてシリコン基板11をエッチングする。エッチされる溝は、例えば最小幅0.18μm、深さ0.3μmであり、アスペクト比が1を大きく越える部分を有する。その後ホトレジストマスクPR1は除去する。

Hereinafter, examples based on these findings will be described.

As shown in FIG. 3A, a hard mask layer HM is deposited by CVD on the surface of the

図3Bに示すように、形成した溝の表面を例えば1100℃で熱酸化し、厚さ40nmの酸化膜を形成した後、ソースガスとしてHe/SiH4/O2を用いた高密度プラズマ(HDP)CVDにより酸化シリコン膜を厚さ550nm(0.55μm)堆積する。酸化シリコン膜12は、ボイドを発生することなく溝を埋め込む。その後、化学機械研磨(CMP)により、ハードマスクHMより上の酸化シリコン層12を研磨して除去する。その後ハードマスク層HMも除去する。

As shown in FIG. 3B, the surface of the formed groove is thermally oxidized at 1100 ° C., for example, to form an oxide film having a thickness of 40 nm, and then high density plasma (HDP) using He / SiH 4 / O 2 as a source gas. ) A silicon oxide film having a thickness of 550 nm (0.55 μm) is deposited by CVD. The

図3Cに示すように、酸化シリコン層を埋め込んだSTI12により、活性領域が画定される。活性領域表面上に、スルー酸化膜13を形成し、レジストマスクを用いたイオン注入を行ない、p型ウェルWp(nチャネル領域)、n型ウェルWn(pチャネル領域)を形成する。その後、スルー酸化膜13は除去し、新たにゲート酸化膜を成長する。動作電圧の異なるトランジスタを形成する場合は、動作電圧に応じて厚さの異なるゲート絶縁膜を形成する。

As shown in FIG. 3C, the active region is defined by the

以下の説明においては、1.2V動作のトランジスタを例として説明する。入出力回路用に高精度抵抗を形成し、ESD保護抵抗を備えたトランジスタも形成する。

図3Dに示すように、1.2V動作のトランジスタを形成する各活性領域表面には、例えば850℃の熱酸化により、厚さ2.2nmのゲート酸化膜43が形成される。基板表面にノンドープの多結晶シリコン層を厚さ約180nmCVDにより堆積し、ホトレジストパターンを用いてパターニングする。各活性領域上にゲート電極Gn、Gpが形成され、素子分離領域STI上に抵抗Rpが形成される。

In the following description, a transistor operating at 1.2 V will be described as an example. A high-precision resistor is formed for the input / output circuit, and a transistor having an ESD protection resistor is also formed.

As shown in FIG. 3D, a

図3Eに示すように、pチャネル領域及び抵抗を覆うホトレジストマスクPR2を形成し、nチャネル領域にエクステンション領域形成用のAs+のイオン注入及びポケット領

域形成用のBF2 +の斜めイオン注入を行なう。n型エクステンション領域EXn及びそれを取り囲むp型ポケット領域PKpが形成される。Asを用いてもドーズ量が低いため、ディスロケーションの発生によってトランジスタを不良とする可能性は低い。その後、レジストマスクPR2は除去する。

As shown in FIG. 3E, a photoresist mask PR2 that covers the p-channel region and the resistor is formed, and As + ion implantation for extension region formation and BF 2 + oblique ion implantation for pocket region formation are performed in the n-channel region. . An n-type extension region EXn and a p-type pocket region PKp surrounding it are formed. Even when As is used, since the dose is low, there is a low possibility that a transistor will be defective due to the occurrence of dislocation. Thereafter, the resist mask PR2 is removed.

図3Fに示すように、nチャネル領域及び抵抗を覆うレジストマスクPR3を形成し、pチャネル領域に対してエクステンション領域形成用のB+のイオン注入、ポケット領域

形成用のAs+の斜めイオン注入を行なう。p型エクステンション領域EXp及びそれを

取り囲むn型ポケット領域PKnが形成される。その後レジストマスクPR3は除去する。

As shown in FIG. 3F, a resist mask PR3 covering the n channel region and the resistor is formed, and B + ion implantation for extension region formation and As + oblique ion implantation for pocket region formation are performed on the p channel region. Do. A p-type extension region EXp and an n-type pocket region PKn surrounding it are formed. Thereafter, the resist mask PR3 is removed.

図3Gに示すように、基板全面に酸化シリコン膜を、例えば基板温度620℃の減圧TEOS‐CVDで、厚さ130nm堆積し、全面リアクティブイオンエッチング(RIE)で異方性エッチして、ゲート電極及び抵抗の側壁上にサイドウォールスペーサSWを形成する。 As shown in FIG. 3G, a silicon oxide film is deposited on the entire surface of the substrate with a thickness of 130 nm by, for example, reduced pressure TEOS-CVD at a substrate temperature of 620 ° C., and anisotropic etching is performed by reactive ion etching (RIE) on the entire surface. Sidewall spacers SW are formed on the electrode and resistor sidewalls.

酸化膜堆積工程における基板温度620℃は、それまでに注入されたn型不純物がAsであるので異常拡散を生じることはない。又、例えPをn型不純物として用いても、低濃度であるため異常拡散は生じない。620℃の温度により、電荷トラップ等も比較的減少でき、ホットキャリア耐性を確保することができ、絶縁耐圧等の不具合も生じない。 A substrate temperature of 620 ° C. in the oxide film deposition process does not cause abnormal diffusion because the n-type impurity implanted so far is As. Even if P is used as an n-type impurity, abnormal diffusion does not occur because of its low concentration. With a temperature of 620 ° C., charge traps and the like can be relatively reduced, hot carrier resistance can be ensured, and problems such as withstand voltage do not occur.

図3Hに示すように、抵抗及びpチャネル領域を覆うホトレジストマスクPR4を形成し、nチャネル領域に対してP+イオンを加速エネルギ11keV、ドーズ量6.0×1

015cm-2で高濃度にイオン注入する。このイオン注入により、サイドウォールスペーサSW外方に、高濃度のn型ソース/ドレイン領域HDDnが形成される。高濃度であるが、Pであるため、STIのストレスが増加してもシリコンの結晶欠陥が多発し、SRAMの低電圧動作歩留りが低下する等の不都合は生じない。その後、レジストマスクPR4は除去する。

As shown in FIG. 3H, a photoresist mask PR4 covering the resistor and the p-channel region is formed, and P + ions are accelerated to the ke channel with an acceleration energy of 11 keV and a dose amount of 6.0 × 1.

Ion implantation is performed at a high concentration at 0 15 cm −2 . By this ion implantation, a high concentration n-type source / drain region HDDn is formed outside the sidewall spacer SW. Although it is a high concentration, since it is P, there is no inconvenience such as frequent occurrence of silicon crystal defects even if the stress of STI increases and the low voltage operation yield of the SRAM is lowered. Thereafter, the resist mask PR4 is removed.

図3Iに示すように、nチャネル領域を覆うホトレジストマスクPR5を形成し、抵抗Rp及びpチャネル領域にB+イオンを加速エネルギ5keV、ドーズ量4.0×1015

cm-2で高濃度にイオン注入する。pチャネル領域においては、サイドウォールスペーサSWの外方に、高濃度p型ソース/ドレイン領域HDDpが形成される。抵抗Rpにおいても、高濃度のp型不純物が注入され、p型多結晶シリコンとなる。p型多結晶シリコンは、シリコン抵抗の中で最も温度係数が低い高精度の抵抗に適した材料である。

As shown in FIG. 3I, a photoresist mask PR5 covering the n-channel region is formed, B + ions are accelerated

High concentration ion implantation is performed at cm −2 . In the p channel region, a high concentration p-type source / drain region HDDp is formed outside the sidewall spacer SW. Also in the resistor Rp, a high-concentration p-type impurity is implanted to become p-type polycrystalline silicon. P-type polycrystalline silicon is a material suitable for a high-precision resistor having the lowest temperature coefficient among silicon resistors.

その後、レジストマスクPR5は除去する。1025℃、N2雰囲気、3秒間のラピッ

ドサーマルアニールを行ない。イオン注入した不純物を活性化する。

図3Jに示すように、基板全面にプラズマCVDにより、TEOSを原料ガスとし、基板温度350℃でシリコン酸化膜を厚さ50nm堆積する。このCVDは、500℃よりも十分に低い350℃で行なわれるため、高濃度の燐(P)拡散領域が存在しても、燐の異常拡散は生じない。形成するシリコン酸化膜は、サリサイドブロックとしての機能を果たせればよく、緻密性等の条件は要しないため、低温で形成してもよい。

Thereafter, the resist mask PR5 is removed. Rapid thermal annealing is performed at 1025 ° C. in an N 2 atmosphere for 3 seconds. The ion-implanted impurity is activated.

As shown in FIG. 3J, a silicon oxide film having a thickness of 50 nm is deposited on the entire surface of the substrate by plasma CVD using TEOS as a source gas and a substrate temperature of 350 ° C. Since this CVD is performed at 350 ° C., which is sufficiently lower than 500 ° C., abnormal diffusion of phosphorus does not occur even if a high concentration phosphorus (P) diffusion region exists. The silicon oxide film to be formed only needs to function as a salicide block, and does not require conditions such as denseness. Therefore, the silicon oxide film may be formed at a low temperature.

堆積したシリコン酸化膜上にサリサイドブロック層を形成するためのホトレジストマスクPR6を形成し、異方性エッチングを行なってシリコン酸化膜をパターニングする。その後、レジストマスクPR6は除去する。図の構成においては、左端に示す抵抗Rpの中央部上にサリサイドブロック層SBが形成される他、左側のnチャネルトランジスタの一方のソース/ドレイン領域上及び右側のpチャネルトランジスタの一方のソース/ドレイン領域上にサリサイドブロック層SBが形成されている。 A photoresist mask PR6 for forming a salicide block layer is formed on the deposited silicon oxide film, and anisotropic etching is performed to pattern the silicon oxide film. Thereafter, the resist mask PR6 is removed. In the configuration shown in the figure, the salicide block layer SB is formed on the center of the resistor Rp shown at the left end, and on one source / drain region of the left n-channel transistor and one source / drain of the right p-channel transistor. A salicide block layer SB is formed on the drain region.

図3Kに示すように、例えばCo膜を厚さ8nmスパッタリングで形成し、540℃のRTA30秒で1次シリサイド反応を生じさせ、続いて未反応Co膜を除去する。その後、840℃のRTA30秒で2次シリサイド反応を生じさせ、低抵抗のシリサイド層SLを形成する。サリサイドブロック層SB下の多結晶シリコン抵抗Rp表面はシリサイド化されず、所望の抵抗値を保って高精度抵抗を形成する。トランジスタのソース/ドレイン領域においては、サリサイドブロック層SB下の領域がソース/ドレイン領域と一体化したESD保護抵抗を形成する。

As shown in FIG. 3K, for example, a Co film is formed by sputtering with a thickness of 8 nm, a primary silicide reaction is caused in RTA at 540 ° C. for 30 seconds, and then an unreacted Co film is removed. Thereafter, a secondary silicide reaction is caused in

図3Lに示すように、500℃以下の基板温度で、基板表面上にプラズマCVDによりシリコン窒化膜4を厚さ50nm堆積し、その上にHDP‐CVDにより酸化シリコン膜5を厚さ900nm堆積する。CMPにより表面を平坦化した後、コンタクトホールを開口する。コンタクトホールにWを埋め込み、CMPで不要部を除去してコンタクトホール内にWプラグ6を形成する。

As shown in FIG. 3L, a

さらに基板全面上に窒化シリコン膜7、酸化シリコン膜8を堆積し、ダマシン法によりCu配線9を形成する。必要に応じ、配線層を積層し、多層配線構造を形成する。

上述の実施例によれば、STIのアスペクト比が1を越える部分を有し、高密度集積化が可能となる。STIのアスペクト比が1を越えても、HDP酸化シリコン膜により素子分離溝を埋め込むことにより、ボイドを発生することなく素子分離領域を形成することができる。

Further, a silicon nitride film 7 and a silicon oxide film 8 are deposited on the entire surface of the substrate, and a Cu wiring 9 is formed by a damascene method. If necessary, wiring layers are laminated to form a multilayer wiring structure.

According to the above-described embodiment, the STI has an aspect ratio exceeding 1, and high-density integration is possible. Even if the aspect ratio of STI exceeds 1, the element isolation region can be formed without generating a void by embedding the element isolation groove with the HDP silicon oxide film.

HDP酸化シリコン膜によるSTIは、強いストレスを発生するが、高濃度n型ソース/ドレイン領域を燐(P)を用いて形成することにより、結晶欠陥に基づく不良の多発を防止することができる。 STI caused by the HDP silicon oxide film generates a strong stress. However, by forming the high-concentration n-type source / drain regions using phosphorus (P), frequent occurrence of defects due to crystal defects can be prevented.

サリサイドブロック層を用い、ポリシリコン抵抗、拡散層抵抗形成のための不純物イオン注入と、トランジスタのソース/ドレイン領域形成のためのイオン注入とを兼用することにより、最小の工程数増加で抵抗を作成することができる。サリサイドブロック層を堆積する工程を、500℃以下の低温とすることにより、高濃度の燐をドープしたソース/ドレイン領域を用いても異常拡散を防止し、短チャネルn型トランジスタの特性を維持することができる。高精度のアナログ抵抗が、p型多結晶シリコンを用いた抵抗により形成される。ESD保護抵抗は、トランジスタと同一の活性領域内にサリサイドブロック層を用いることにより簡略に作成できる。 Using a salicide block layer, both resistance ion implantation for forming polysilicon resistance and diffusion layer resistance and ion implantation for forming a source / drain region of a transistor are combined to create resistance with a minimum number of steps. can do. By depositing the salicide block layer at a low temperature of 500 ° C. or lower, abnormal diffusion is prevented even when a source / drain region doped with a high concentration of phosphorus is used, and the characteristics of the short-channel n-type transistor are maintained. be able to. A highly accurate analog resistor is formed by a resistor using p-type polycrystalline silicon. The ESD protection resistor can be simply created by using a salicide block layer in the same active region as the transistor.

上述の実施例の説明においては、nチャネルトランジスタ、pチャネルトランジスタとも1種類であった。実際の半導体装置においては、低電圧動作の論理回路、SRAM回路、中電圧の入出力回路の他不揮発メモリのフラッシュメモリ等を混載する要請も強い。フラッシュメモリの制御回路は読出時5V、書込/消去時10V弱の電圧を扱う。又、高速動作する低閾値トランジスタと、オフ時のリーク電流の低い高閾値トランジスタとの両者が要求される場合もある。 In the description of the above embodiment, there is only one type of n-channel transistor and p-channel transistor. In an actual semiconductor device, there is a strong demand for mounting a low-voltage operation logic circuit, an SRAM circuit, a medium-voltage input / output circuit, a non-volatile memory flash memory, and the like. The control circuit of the flash memory handles a voltage of less than 5V at the time of reading and less than 10V at the time of writing / erasing. Further, there are cases where both a low threshold transistor that operates at high speed and a high threshold transistor that has a low leakage current when turned off are required.

以下、多種トランジスタを形成する実施例を説明する。同時にアナログ/デジタル変換回路に用いる高精度抵抗、ESD保護抵抗も形成するが、抵抗の形成工程に関しては前述の実施例同様であるので図示は省略する。 Hereinafter, an embodiment for forming a multi-type transistor will be described. At the same time, a high-precision resistor and an ESD protection resistor used for the analog / digital conversion circuit are also formed.

図4は、半導体装置に集積化される11種類のトランジスタを列挙したものである。トランジスタFMは、フラッシュメモリセルを表わす。高電圧、低閾値トランジスタN−HV−LVtは、高耐圧で低い閾値を有するnチャネルMOSトランジスタである。高電圧、高閾値トランジスタN−HV−HVtは、高耐圧、高閾値のnチャネルMOSトランジスタである。高電圧、低閾値トランジスタP−HV−LVtは高耐圧、低閾値のpチャネルMOSトランジスタである。高電圧、高閾値トランジスタP−HV−HVtは、高耐圧、高閾値のpチャネルMOSトランジスタである。高電圧は例えば5V動作である。 FIG. 4 lists eleven types of transistors integrated in a semiconductor device. Transistor FM represents a flash memory cell. The high voltage, low threshold transistor N-HV-LVt is an n-channel MOS transistor having a high breakdown voltage and a low threshold. The high voltage, high threshold transistor N-HV-HVt is a high breakdown voltage, high threshold n-channel MOS transistor. The high voltage, low threshold transistor P-HV-LVt is a high breakdown voltage, low threshold p-channel MOS transistor. The high voltage, high threshold transistor P-HV-HVt is a high breakdown voltage, high threshold p-channel MOS transistor. The high voltage is, for example, 5V operation.

中電圧トランジスタN−MVは、入出力インターフェイスに用いられる例えば2.5V動作のnチャネルMOSトランジスタである。中電圧トランジスタP−MVは、入出力インターフェイスに用いられる例えば2.5V動作のpチャネルMOSトランジスタである。中電圧は、2.5Vに限らず、3.3Vや5V、1.8V,1.2Vの可能性もある。入出力回路には、高精度アナログ抵抗も形成する。 The intermediate voltage transistor N-MV is, for example, an n-channel MOS transistor that operates at 2.5 V and is used for an input / output interface. The medium voltage transistor P-MV is, for example, a 2.5-V operation p-channel MOS transistor used for an input / output interface. The medium voltage is not limited to 2.5V, but may be 3.3V, 5V, 1.8V, and 1.2V. A high-precision analog resistor is also formed in the input / output circuit.

低電圧、高閾値トランジスタN‐LV−HVtは、低耐圧、高閾値のnチャネルMOSトランジスタである。低電圧、低閾値トランジスタN−LV−LVtは、低耐圧、低閾値のnチャネルMOSトランジスタである。低電圧、高閾値トランジスタP‐LV‐HVtは、低耐圧、高閾値のpチャネルMOSトランジスタである。低電圧、低閾値トランジスタP−LV−LVtは、低耐圧、低閾値のpチャネルMOSトランジスタである。低電圧は、例えば1.2V動作である。 The low voltage, high threshold transistor N-LV-HVt is a low breakdown voltage, high threshold n-channel MOS transistor. The low voltage, low threshold transistor N-LV-LVt is a low breakdown voltage, low threshold n-channel MOS transistor. The low voltage, high threshold transistor P-LV-HVt is a low breakdown voltage, high threshold p-channel MOS transistor. The low voltage, low threshold transistor P-LV-LVt is a low breakdown voltage, low threshold p-channel MOS transistor. The low voltage is, for example, 1.2V operation.

電源電圧、入力信号の供給端子に接続されたトランジスタには必要に応じてESD保護抵抗を接続する。ESD保護抵抗は上述の実施例で説明した様に、ソース/ドレイン領域の一部にシリサイド層を形成しないことによってトランジスタと一体に形成できる。 An ESD protection resistor is connected to the transistor connected to the supply terminal of the power supply voltage and the input signal as necessary. As described in the above embodiments, the ESD protection resistor can be formed integrally with the transistor by not forming a silicide layer in a part of the source / drain region.

nチャネル高電圧トランジスタ及びフラッシュメモリセルは、n型ウェル19内のp型ウェル14内に形成される。nチャネルトランジスタはp型ウェル14内に形成され、pチャネルMOSトランジスタはn型ウェル24内に形成される。高耐圧、低閾値pチャネルMOSトランジスタP−HV−LVt以外のトランジスタには、チャネルストップ領域15、25が形成されている。

The n-channel high voltage transistor and flash memory cell are formed in the p-type well 14 in the n-

低電圧、高閾値トランジスタN−LV−HVt、P−LV−HVtには、閾値調整用イオン注入16、26が形成されている。中電圧トランジスタN‐MV、P‐MVには、閾値調整用イオン注入37、38が形成されている。フラッシュメモリFMには、閾値調整用イオン注入36が形成されている。閾値調整用イオン注入とチャネルストップ領域とが協働してトランジスタの閾値を調整している。

Threshold

以下、図4に示す半導体装置を製造する製造工程について説明する。

図5Aに示すように、半導体基板11にアスペクト比1以上の部分を有する素子分離溝を形成し、高密度プラズマ(HDP)酸化シリコン膜で埋め込み、CMPを行って、シャロートレンチアイソレーション(STI)12を形成する。次いでシリコン基板表面を熱酸化し、例えば厚さ10nmの酸化シリコン膜13を形成する。

A manufacturing process for manufacturing the semiconductor device shown in FIG. 4 will be described below.

As shown in FIG. 5A, an element isolation trench having a portion with an aspect ratio of 1 or more is formed in a

図5Bに示すように、フラッシュメモリセルFM及び高電圧nチャネルMOSトランジスタN−HV領域を露出するホトレジストマスクPR14を形成し、n型ウェル19形成用のP+イオンを加速エネルギ2MeV、ドーズ量2×1013cm-2でイオン注入する。

その後レジストマスクPR14は除去する。

As shown in FIG. 5B, a photoresist mask PR14 that exposes the flash memory cell FM and the high-voltage n-channel MOS transistor N-HV region is formed, and P + ions for forming the n-type well 19 are accelerated

Thereafter, the resist mask PR14 is removed.

図5Cに示すように、フラッシュメモリFM及びnチャネルMOSトランジスタ領域を露出する開口を有するホトレジストマスクPR11を形成し、p型ウェル14形成用のB+イオンを加速エネルギ400keV、ドーズ量1.5×1013cm-2でイオン注入し、

さらにチャネルストップ領域15形成用のB+イオンを加速エネルギ100keV、ドー

ズ量2×1012cm-2でイオン注入する。その後レジストマスクPR11は除去する。このようにして、p型ウェル14及びチャネルストップ領域15が形成される。

As shown in FIG. 5C, a photoresist mask PR11 having an opening exposing the flash memory FM and the n-channel MOS transistor region is formed, and B + ions for forming the p-type well 14 are accelerated energy of 400 keV and a dose of 1.5 ×. Ion implantation at 10 13 cm -2

Further, B + ions for forming the

図5Dに示すように、フラッシュメモリFM及び高電圧、低閾値nチャネルトランジスタN−HV−LVtを除くnチャネルMOSトランジスタを露出するレジストマスクPR12を形成し、チャネルストップ領域形成用のB+イオンを加速エネルギ100keV、

ドーズ量6×1012で追加的にイオン注入する。追加イオン注入をされたチャネルストップ領域15xが形成される。その後レジストマスクPR12は除去する。

As shown in FIG. 5D, a resist mask PR12 exposing the n-channel MOS transistors excluding the flash memory FM and the high-voltage, low-threshold n-channel transistors N-HV-LVt is formed, and B + ions for forming a channel stop region are formed.

Additional ion implantation is performed with a dose amount of 6 × 10 12 . A

図5Eに示すように、pチャネルMOSトランジスタを露出するレジストマスクPR21を形成し、n型ウェル24形成用のP+イオンを加速エネルギ600keV、ドーズ量

1.5×1013cm-2でイオン注入する。その後レジストマスクPR21は除去する。

As shown in FIG. 5E, a resist mask PR21 exposing the p-channel MOS transistor is formed, and P + ions for forming the n-type well 24 are ion-implanted with an acceleration energy of 600 keV and a dose of 1.5 × 10 13 cm −2. To do. Thereafter, the resist mask PR21 is removed.

図5Fに示すように、高電圧、低閾値トランジスタを除くpチャネルMOSトランジスタを露出するレジストマスクPR22を形成し、チャネルストップ領域25形成用のP+

イオンを加速エネルギ240keV、ドーズ量4.5×1012cm-2でイオン注入する。その後レジストマスクPR22は除去する。

As shown in FIG. 5F, a resist mask PR22 that exposes the p-channel MOS transistor excluding the high-voltage, low-threshold transistor is formed, and P + for forming the

Ions are implanted with an acceleration energy of 240 keV and a dose of 4.5 × 10 12 cm −2 . Thereafter, the resist mask PR22 is removed.

図5Gに示すように、フラッシュメモリセルFMを露出するレジストマスクPR31を形成し、閾値調整用領域36を形成するB+イオンを加速エネルギ40keV、ドーズ

量6×1013cm-2でイオン注入する。その後レジストマスクPR31は除去する。さらに、半導体基板表面の酸化シリコン膜13をHF溶液により除去する。活性領域のシリコン表面が露出する。

As shown in FIG. 5G, a resist mask PR31 exposing the flash memory cell FM is formed, and B + ions forming the

図5Hに示すように、半導体基板表面を熱酸化し、厚さ約10nmのトンネル酸化膜を成長する。トンネル酸化膜上に、厚さ約90nmの燐(P)をドープしたアモルファスシリコン膜をCVDにより堆積し、フローティングゲート31の形状にパターニングする。なお、アモルファスシリコン膜は、その後の熱処理によりポリシリコン膜に変換される。