JP2010056554A - 半導体素子の漏洩電流予測方法 - Google Patents

半導体素子の漏洩電流予測方法 Download PDFInfo

- Publication number

- JP2010056554A JP2010056554A JP2009197032A JP2009197032A JP2010056554A JP 2010056554 A JP2010056554 A JP 2010056554A JP 2009197032 A JP2009197032 A JP 2009197032A JP 2009197032 A JP2009197032 A JP 2009197032A JP 2010056554 A JP2010056554 A JP 2010056554A

- Authority

- JP

- Japan

- Prior art keywords

- leakage

- characteristic function

- leakage current

- variable

- chip

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F30/00—Computer-aided design [CAD]

- G06F30/30—Circuit design

-

- H10P74/00—

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F30/00—Computer-aided design [CAD]

- G06F30/30—Circuit design

- G06F30/36—Circuit design at the analogue level

- G06F30/367—Design verification, e.g. using simulation, simulation program with integrated circuit emphasis [SPICE], direct methods or relaxation methods

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F30/00—Computer-aided design [CAD]

- G06F30/30—Circuit design

- G06F30/39—Circuit design at the physical level

- G06F30/398—Design verification or optimisation, e.g. using design rule check [DRC], layout versus schematics [LVS] or finite element methods [FEM]

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Evolutionary Computation (AREA)

- Geometry (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

Abstract

【課題】 半導体素子の漏洩電流予測方法を提供する。

【解決手段】 半導体素子の漏洩電流予測方法において、多数のセルを有するチップを多数の分割領域に区分して、各セルで漏洩電流を引き起こす工程変数相互間の空間相関を決める。多数の漏洩成分に関する実際漏洩特性関数を算術的に合算して、上記多数の漏洩成分と物理的に等価の仮想セル漏洩特性関数を生成する。分割領域内の各セルに対する仮想セル漏洩特性関数を算術的に合算して、上記分割領域で発生する漏洩電流に関する特性関数の領域漏洩特性関数を生成する。領域漏洩特性関数を統計的に合算して、全チップで発生する漏洩電流に関する特性関数の全チップ漏洩特性関数を生成する。これにより、全チップ漏洩特性関数を獲得するためのウィルキンソンアルゴリズムの複雑度を減らすことができる。

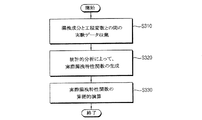

【選択図】図1

Description

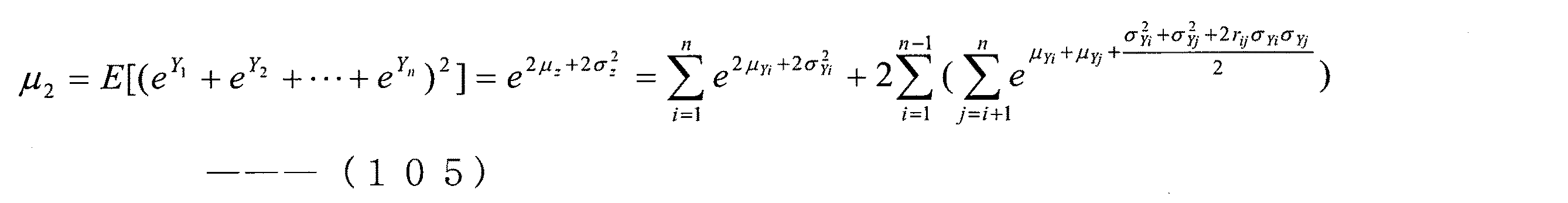

前記仮想セル漏洩特性関数を合算する段階は、ログノーマル分布の合成のためのウィルキンソン方法の第2次モーメントに関する等価条件を適用して指数多項式を獲得する段階と、前記指数多項式を第1次テイラー級数で展開する段階と、前記テイラー級数を任意のログノーマル分布に関する確立変数に関する恒等式で整列する段階と、を含むことを特徴とする半導体素子の漏洩電流予測方法である。解決手段12では、前記領域漏洩特性関数は、サブ閾値漏洩電流(sub−threshold leakage current)またはゲート漏洩電流(gate leakage current)のうちの何れかの1つを含むことを特徴とする半導体素子の漏洩電流予測方法である。

図1は、本発明の一実施形態による全チップ漏洩評価方法を示すフローチャートである。図2は、ウエハーに形成されたチップを本発明の位置に沿って、多数の分割領域に区分したグリッドモデルの一部を示す平面図である。

Claims (20)

- 集積回路を構成する単位素子が配置される多数のセルを有するチップを多数の分割領域に区分する段階と、

前記各セルで漏洩電流を引き起こす工程変数相互間の空間相関を決定する段階と、

前記セルから発生する多数の漏洩成分に関する実際漏洩特性関数を算術的に演算して、前記多数の実際漏洩特性関数と物理的に等価である仮想セル漏洩特性関数を生成する段階と、

前記分割領域内のセルに対する前記仮想セル漏洩特性関数を算術的に合算して前記分割領域から発生する漏洩電流に関する特性関数である領域漏洩特性関数を生成する段階と、

前記分割領域ごとの前記領域漏洩特性関数を演算し、統計的に合算して全チップから発生する漏洩電流に関する特性関数である全チップ漏洩特性関数を生成する段階と、

を含むことを特徴とする半導体素子の漏洩電流決定方法。 - 前記実際漏洩特性関数及び前記仮想セル漏洩特性関数は、前記工程変数の指数多項式で表現されることを特徴とする請求項1に記載の半導体素子の漏洩電流予測方法。

- 前記全域工程変数は、チップ単位で、漏洩電流に影響を及ぼすチップ変数及びチップ内部で漏洩成分相互間に空間相関を有するチップ内部変数を含み、

前記地域工程変数は、漏洩成分相互間に空間相関を有しない全ての工程変数を含むことを特徴とする請求項4に記載の半導体素子の漏洩電流予測方法。 - 前記第1及び第2漏洩電流は、サブ閾値漏洩電流またはゲート漏洩電流のうちの何れかの1つを含むことを特徴とする請求項3に記載の半導体素子の漏洩電流予測方法。

- 前記領域漏洩特性関数は、指数多項式を含むログノーマル分布を有することを特徴とする請求項9に記載の半導体素子の漏洩電流決定方法。

- 前記仮想セル漏洩特性関数を合算する段階は、

ログノーマル分布の合成のためのウィルキンソン方法の第2次モーメントに関する等価条件を適用して指数多項式を獲得する段階と、

前記指数多項式を第1次テイラー級数で展開する段階と、

前記テイラー級数を任意のログノーマル分布に関する確率変数に関する恒等式で整列する段階と、

を含むことを特徴とする請求項10に記載の半導体素子の漏洩電流予測方法。 - 前記領域漏洩特性関数は、サブ閾値漏洩電流またはゲート漏洩電流の内の何れかの1つを含むことを特徴とする請求項9に記載の半導体素子の漏洩電流予測方法。

- 前記全チップ漏洩特性関数を生成する段階は、前記多数の領域漏洩特性関数に対する第1次及び第2次モーメントを利用して平均及び分散を獲得する段階を含むことを特徴とする請求項1に記載の半導体素子の漏洩電流予測方法。

- 前記実際漏洩特性関数は、前記多数の漏洩成分と工程変数との間のデータを分析して獲得することを特徴とする請求項1に記載の半導体素子の漏洩電流予測方法。

- 前記実際漏洩特性関数を決定する段階は、前記工程変数と前記漏洩成分との間の確率的関係を獲得するための回帰分析法を遂行する段階を含むことを特徴とする請求項14に記載の半導体素子の漏洩電流予測方法。

- 前記工程変数は、前記チップ単位で前記漏洩成分に影響を及ぼすチップ単位変数、前記チップ内部で漏洩成分相互間に空間相関を有するチップ内部変数を含む全域変数、及び、前記漏洩成分相互間に空間相関を有しない全ての工程変数を含む地域変数を具備することを特徴とする請求項14に記載の半導体素子の漏洩電流予測方法。

- 前記工程変数は、工程遂行の中に、外部環境によって任意的に発生する任意変異に関する変数である任意変数、及び、前記工程遂行のための物理的設備によって発生する構造型変異に関する変数である構造型変数を含むことを特徴とする請求項16に記載の半導体素子の漏洩電流予測方法。

- 前記任意変異は、前記任意変数を確率変数にした確率分布で表示され、

前記構造型変異は、前記空間相関性行列で表示されることを特徴とする請求項17に記載の半導体素子の漏洩電流決定方法。 - 前記工程変数は、薄膜を形成するための蒸着工程の工程温度、蒸着膜の厚さ、パターンの線幅、ゲート電圧の大きさを含むことを特徴とする請求項17に記載の半導体素子の漏洩電流予測方法。

- 前記仮想セル漏洩特性関数と前記セルから発生する他の追加漏洩成分に関する追加実際漏洩特性関数とを算術的に演算し、前記セルに対する追加漏洩成分による影響を分析する変化量分析を遂行する段階をさらに含むことを特徴とする請求項1に記載の半導体素子の漏洩電流予測方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020080084718A KR101504594B1 (ko) | 2008-08-28 | 2008-08-28 | 반도체 소자의 누설전류 예측 방법 |

| KR10-2008-0084718 | 2008-08-28 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010056554A true JP2010056554A (ja) | 2010-03-11 |

| JP2010056554A5 JP2010056554A5 (ja) | 2012-09-13 |

| JP5558758B2 JP5558758B2 (ja) | 2014-07-23 |

Family

ID=41202919

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009197032A Active JP5558758B2 (ja) | 2008-08-28 | 2009-08-27 | 半導体素子の漏洩電流予測方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US8156460B2 (ja) |

| JP (1) | JP5558758B2 (ja) |

| KR (1) | KR101504594B1 (ja) |

| CN (1) | CN101661525B (ja) |

| DE (1) | DE102009038844A1 (ja) |

| GB (1) | GB2462936B (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2011111796A1 (ja) | 2010-03-12 | 2011-09-15 | 旭硝子株式会社 | 硬化性組成物 |

| JP2013092901A (ja) * | 2011-10-25 | 2013-05-16 | Fujitsu Ltd | 解析プログラム、解析方法、および解析装置 |

| CN103698680A (zh) * | 2013-12-06 | 2014-04-02 | 上海卫星工程研究所 | 一种元器件抗总剂量生存能力预估方法 |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN105021871B (zh) * | 2014-04-17 | 2017-04-05 | 国家电网公司 | 一种不完全信息下电缆线路泄露电流确定方法 |

| US10521538B2 (en) * | 2016-04-27 | 2019-12-31 | Taiwan Semiconductor Manufacturing Co., Ltd | Method and system for integrated circuit design with on-chip variation and spatial correlation |

| CN107506511B (zh) * | 2017-06-21 | 2020-05-08 | 太原理工大学 | 基于有限元的矿用xlpe电缆泄漏电流动态分析方法 |

| KR102426729B1 (ko) * | 2017-08-11 | 2022-07-29 | 삼성전자주식회사 | 불휘발성 메모리 장치 및 불휘발성 메모리 장치의 동작 방법 |

| KR102089083B1 (ko) * | 2018-11-14 | 2020-03-16 | 주식회사 바움 | 회로 설계의 누설 전력을 조기에 추정하기 위한 시스템 및 방법 |

| KR102023096B1 (ko) * | 2019-02-13 | 2019-09-19 | 울산과학기술원 | 양산되는 집적 회로의 성능 지표를 통합적으로 확률 해석하는 방법 |

| US10839129B2 (en) * | 2019-02-13 | 2020-11-17 | International Business Machines Corporation | Characterization of spatial correlation in integrated circuit development |

| CN112072609B (zh) * | 2020-09-28 | 2022-06-24 | 国网山东省电力公司莱芜供电公司 | 一种漏电保护器动作电流的调整方法 |

| KR102750126B1 (ko) | 2022-09-05 | 2025-01-03 | 주식회사 유진테크 | 기판 처리 장치 및 기판 처리 방법 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002270478A (ja) * | 2000-12-21 | 2002-09-20 | Toshiba Corp | 電子回路設計シミュレータ |

| JP2005071360A (ja) * | 2003-08-22 | 2005-03-17 | Internatl Business Mach Corp <Ibm> | リーク電流感度(leakagecurrentsensitivity)を求め、それを用いて集積回路の設計を最適化する方法 |

| JP2006186150A (ja) * | 2004-12-28 | 2006-07-13 | Hitachi Ltd | 半導体記憶装置の製造方法及び半導体設計装置 |

| WO2007052334A1 (ja) * | 2005-11-01 | 2007-05-10 | Fujitsu Limited | 論理セルの構成処理方法、及び、プログラム |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6842714B1 (en) | 2003-08-22 | 2005-01-11 | International Business Machines Corporation | Method for determining the leakage power for an integrated circuit |

| US7328126B2 (en) | 2003-09-12 | 2008-02-05 | Tokyo Electron Limited | Method and system of diagnosing a processing system using adaptive multivariate analysis |

| KR100630755B1 (ko) * | 2005-07-18 | 2006-10-02 | 삼성전자주식회사 | 포텐샬 쇼트를 검출하기 위한 집적회로 패키지의 테스트방법 |

| JP2008153415A (ja) * | 2006-12-18 | 2008-07-03 | Renesas Technology Corp | 半導体集積回路およびその製造方法 |

| KR20080084718A (ko) | 2007-03-16 | 2008-09-19 | 박근수 | 숯불구이장치 |

| CN201038831Y (zh) * | 2007-05-24 | 2008-03-19 | 饶学进 | 一种监控对地泄漏电流信号的装置 |

| JP5056478B2 (ja) * | 2008-02-28 | 2012-10-24 | 富士通株式会社 | リーク電流解析プログラム、該プログラムを記録した記録媒体、リーク電流解析装置、およびリーク電流解析方法 |

-

2008

- 2008-08-28 KR KR1020080084718A patent/KR101504594B1/ko active Active

-

2009

- 2009-08-26 US US12/547,729 patent/US8156460B2/en active Active

- 2009-08-26 DE DE102009038844A patent/DE102009038844A1/de not_active Withdrawn

- 2009-08-27 JP JP2009197032A patent/JP5558758B2/ja active Active

- 2009-08-28 GB GB0915132.5A patent/GB2462936B/en active Active

- 2009-08-28 CN CN200910170609.2A patent/CN101661525B/zh active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002270478A (ja) * | 2000-12-21 | 2002-09-20 | Toshiba Corp | 電子回路設計シミュレータ |

| JP2005071360A (ja) * | 2003-08-22 | 2005-03-17 | Internatl Business Mach Corp <Ibm> | リーク電流感度(leakagecurrentsensitivity)を求め、それを用いて集積回路の設計を最適化する方法 |

| JP2006186150A (ja) * | 2004-12-28 | 2006-07-13 | Hitachi Ltd | 半導体記憶装置の製造方法及び半導体設計装置 |

| WO2007052334A1 (ja) * | 2005-11-01 | 2007-05-10 | Fujitsu Limited | 論理セルの構成処理方法、及び、プログラム |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2011111796A1 (ja) | 2010-03-12 | 2011-09-15 | 旭硝子株式会社 | 硬化性組成物 |

| JP2013092901A (ja) * | 2011-10-25 | 2013-05-16 | Fujitsu Ltd | 解析プログラム、解析方法、および解析装置 |

| CN103698680A (zh) * | 2013-12-06 | 2014-04-02 | 上海卫星工程研究所 | 一种元器件抗总剂量生存能力预估方法 |

| CN103698680B (zh) * | 2013-12-06 | 2016-08-17 | 上海卫星工程研究所 | 一种元器件抗总剂量生存能力预估方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN101661525B (zh) | 2014-10-08 |

| KR101504594B1 (ko) | 2015-03-23 |

| JP5558758B2 (ja) | 2014-07-23 |

| DE102009038844A1 (de) | 2010-03-25 |

| GB0915132D0 (en) | 2009-10-07 |

| CN101661525A (zh) | 2010-03-03 |

| GB2462936A (en) | 2010-03-03 |

| GB2462936B (en) | 2013-05-22 |

| KR20100025951A (ko) | 2010-03-10 |

| US8156460B2 (en) | 2012-04-10 |

| US20100058258A1 (en) | 2010-03-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5558758B2 (ja) | 半導体素子の漏洩電流予測方法 | |

| US10902173B2 (en) | System for designing integrated circuit using extracted model parameter and method of manufacturing integrated circuit using the same | |

| US10025894B2 (en) | System and method to emulate finite element model based prediction of in-plane distortions due to semiconductor wafer chucking | |

| US7503020B2 (en) | IC layout optimization to improve yield | |

| US8429576B2 (en) | Methods and system for analysis and management of parametric yield | |

| US20140033159A1 (en) | Method of Optimizing Design for Manufacturing (DFM) | |

| US20120239178A1 (en) | Device performance parmeter tuning method and system | |

| WO2011078930A1 (en) | Methods and systems for high sigma yield estimation | |

| US20240143893A1 (en) | Modeling method and modeling system for optical proximity correction model, and optical proximity correction method | |

| CN106599336B (zh) | 半导体工艺模拟装置及方法以及计算装置 | |

| KR20220051903A (ko) | 회로 모델을 생성하는 방법 및 이를 이용한 집적 회로의 제조 방법 | |

| EP4075211B1 (en) | Prediction method and system for multivariate time series data in manufacturing systems | |

| US20110289472A1 (en) | Layout quality evaluation | |

| US8555224B2 (en) | Circuit simulation method and semiconductor integrated circuit | |

| Panigrahy et al. | Integration of artificial neural network and finite element simulation for package warpage prediction | |

| US10830800B1 (en) | Subcircuit physical level power monitoring technology for real-time hardware systems and simulators | |

| TWI392886B (zh) | Non-performing rate prediction method, defect rate prediction program, management method of semiconductor manufacturing apparatus, and manufacturing method of semiconductor device | |

| Juan et al. | Statistical thermal evaluation and mitigation techniques for 3D chip-multiprocessors in the presence of process variations | |

| Krishnan et al. | Stochastic behavioral modeling of analog/mixed-signal circuits by maximizing entropy | |

| CN109425815B (zh) | 用于预测半导体装置的特性的设备和方法 | |

| US20140215419A1 (en) | Analytical model for predicting current mismatch in metal oxide semiconductor arrays | |

| US20200327207A1 (en) | Transient Sensitivity Analysis | |

| US20230066516A1 (en) | Virtual cross metrology-based modeling of semiconductor fabrication processes | |

| US7024645B2 (en) | Method for predicting performance of integrated circuit and method for designing the circuit | |

| CN119416720B (zh) | 双极型运算放大器的可靠性预计模型的构建方法和装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120726 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120726 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131203 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20140303 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20140306 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140331 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140515 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140605 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5558758 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |