JP2010045657A - フレームスイッチング装置、通信システム、コンピュータプログラム及びアドレス学習方法 - Google Patents

フレームスイッチング装置、通信システム、コンピュータプログラム及びアドレス学習方法 Download PDFInfo

- Publication number

- JP2010045657A JP2010045657A JP2008208935A JP2008208935A JP2010045657A JP 2010045657 A JP2010045657 A JP 2010045657A JP 2008208935 A JP2008208935 A JP 2008208935A JP 2008208935 A JP2008208935 A JP 2008208935A JP 2010045657 A JP2010045657 A JP 2010045657A

- Authority

- JP

- Japan

- Prior art keywords

- address

- frame

- mac

- flooding

- frame switching

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L45/00—Routing or path finding of packets in data switching networks

- H04L45/54—Organization of routing tables

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L45/00—Routing or path finding of packets in data switching networks

- H04L45/02—Topology update or discovery

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L45/00—Routing or path finding of packets in data switching networks

- H04L45/32—Flooding

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L61/00—Network arrangements, protocols or services for addressing or naming

- H04L61/09—Mapping addresses

- H04L61/10—Mapping addresses of different types

- H04L61/103—Mapping addresses of different types across network layers, e.g. resolution of network layer into physical layer addresses or address resolution protocol [ARP]

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Data Exchanges In Wide-Area Networks (AREA)

- Small-Scale Networks (AREA)

Abstract

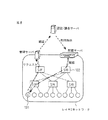

【解決手段】スイッチング装置1は、あるアドレスに対するフラッディングの発生が所定条件を満たすか否かを判定するフラッディング判定部31と、上記条件を満たすアドレスと同じアドレスのアドレスエントリを記憶している他のスイッチから送信される所定の通知を受信する通知受信部33と、上記条件を満たすアドレスと上記通知を受信したポートとを対応付けるアドレスエントリを登録するアドレスエントリ登録部35を備える。

【選択図】図12

Description

広域LANサービスは、上位プロトコルであるレイヤ3のプロトコルを選ばないネットワーク、すなわちL3トポロジーフリーなネットワークであり、顧客が自由にIPネットワークを設計及び運用することができる。

顧客は、例えば、RIP/OSPF(Routing Information Protocol/Open Shortest Path First)等のダイナミックルーティングプロトコルを用いて、動的な経路制御を行うことが可能である一方、スタティックルートを用いてシンプルな経路設定を行うことも可能である。

図1の(A)及び図1の(B)は従来のMAC学習法の説明図である。図1の(A)に示すレイヤ2スイッチSW1は、送信先MACアドレスb及び送信元MACアドレスaを有するMACフレームFR1を受信する。

図1の(B)に示す例においてレイヤ2スイッチSW1は、受信MACフレームFR1を受信したポートp1に、受信MACフレームFR1の送信元MACアドレスaを持ったノードが接続されていることを学習し、MACアドレスaとポートp1との間の対応関係をMACテーブルMT1に登録する。

レイヤ2スイッチSW1が有するMACテーブルMT1には、受信したMACフレームFR2の送信先MACアドレスcが登録されていない。このためレイヤ2スイッチSW1は、図2の(B)に示すように、受信ポートp1以外の他の全てのポートp2及びp3からMACフレームFR2を出力する。

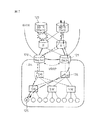

本社内LANは、ネットワークアドレスA/24を有しており、レイヤ2スイッチSW4に接続されたルータR−aを介して広域LANに接続されている。ルータR−aのMACアドレスはaである。

xx出張所内LANは、ネットワークアドレスC/24を有しており、レイヤ2スイッチSW2に接続されたルータR−cを介して広域LANに接続されている。ルータR−cのMACアドレスはcである。

ww支店内LANは、ネットワークアドレスD/24を有しており、レイヤ2スイッチSW1に接続されたルータR−dを介して広域LANに接続されている。ルータR−dのMACアドレスはdである。

データセンタ内LANに接続されたレイヤ2スイッチSW3のポートp1は、ルータR−bに接続されており、レイヤ2スイッチSW3のポートp2は隣接するレイヤ2スイッチSW4に接続されており、レイヤ2スイッチSW3のポートp3は隣接するレイヤ2スイッチSW2に接続されている。

ww支店内LANに接続されたレイヤ2スイッチSW1のポートp1は、ルータR−dに接続されており、レイヤ2スイッチSW1のポートp2は、隣接するレイヤ2スイッチSW2に接続されている。

ルーティングテーブルRT1〜RT4は、各ルータR−d〜R−aがパケットのルーティングに使用するルーティングテーブルである。ルーティングテーブルRT1〜RT4は、I/Pフィールドとネクストホップフィールドとを有する。簡単のため添付する図面においてネクストホップを「N.H.」と示す。

例えばルーティングテーブルRT4は、ネットワークアドレスB/24へ送信するパケットの次に転送先のルータがR−bであることを示し、ネットワークアドレスC/24へ送信するパケットの次に転送先のルータがR−cであることを示し、ネットワークアドレスD/24へ送信するパケットの次に転送先のルータがR−dであることを示している。

また例えばルーティングテーブルRT3は、ネットワークアドレスA/24へ送信するパケットの次に転送先のルータがR−aであることを示し、ネットワークアドレスC/24へ送信するパケットの次に転送先のルータがR−cであることを示し、ネットワークアドレスD/24へ送信するパケットの次に転送先のルータがR−dであることを示している。

そして本社のルータR−aが、xx出張所及びww支店からトラフィックを分配している。このようなネットワーク構成は、ルータの追加及び削除の度に行うスタティックルートの再設定を省略できるという利点がある。

しかし、データセンタからww支店へ送信されるMACヘッダの送信元MACアドレスはデータセンタ内LANのルータR−bのアドレスbであり、データセンタとww支店とのトラフィックにおいてMACアドレスaを送信元アドレスとするフレームが送信されることはない。このためMACテーブルのエ−ジング処理によって、MACアドレスaに関するエントリがレイヤ2スイッチSW1及びSW2のMACテーブルMT1及びMT2から消去される。

RT1a〜RT1cは、ルータR−dで使用されるルーティングテーブル及びARPテーブルを示し、添字a〜cは、時系列に沿って変化するルーティングテーブル及びARPテーブルのそれぞれの時点のデータ内容を示す。

RT4a及びRT4bは、ルータR−aで使用されるルーティングテーブル及びARPテーブルを示し、添字a及びbは、時系列に沿って変化するルーティングテーブル及びARPテーブルのそれぞれの時点のデータ内容を示す。

MT2a及びMT2bは、レイヤ2スイッチSW2で使用されるMACテーブルを示し、添字a及びbは、時系列に沿って変化するMACテーブルのそれぞれの時点のデータ内容を示す。

MT4a及びMT4bは、レイヤ2スイッチSW4で使用されるMACテーブルを示し、添字a及びbは、時系列に沿って変化するMACテーブルのそれぞれの時点のデータ内容を示す。

本社内LANのルータR−aで中継されるフレーム103は、ルータR−aのMACアドレスaを送信先MACアドレス、ルータR−dのMACアドレスdを送信元MACアドレスに有する。この時点では、転送経路上にあるレイヤ2スイッチSW2はMACアドレスaを学習しているためフラッディングは生じない。

この状況は、本来不要なフラッディングを発生させて続けてしまうだけでなく、回線容量が小さい箇所では、帯域圧迫によりほとんど通信が出来ないといった状況が発生してしまう。

端末110は、有線ネットワーク用及び無線ネットワーク用の2つのネットワークインタフェースを有しており、有線ネットワーク用インタフェースはMACアドレスaを有し無線ネットワーク用インタフェースはMACアドレスbを有している。

そして、上りフレームは無線アクセスポイント111及びレイヤ2スイッチ112を経由してルータ113へ転送され、下りフレームはレイヤ2スイッチ114を経由して端末110へ転送される。

このようなネットワーク構成では、レイヤ2スイッチ114において、図3に示すネットワークと同様に端末110の有線ネットワーク用のMACアドレスaの学習漏れが発生するため、レイヤ2スイッチ114にてフラッディングが発生する。

第1フレームスイッチング装置のポートを第1ポートとし、第1フレームスイッチング装置のアドレスエントリ記憶部を第1アドレスエントリ記憶部と示すとき、第2フレームスイッチング装置は、フレームスイッチングネットワーク内の他のフレームスイッチング装置に接続されてフレームを送受信する複数の第2ポートと、アドレスとこのアドレスを送信元アドレスとして含んだフレームを受信した第2ポートとの間の対応関係を示すアドレスエントリが記憶される第2アドレスエントリ記憶部と、を備える。

第2フレームスイッチング装置から送信される、第1フレームスイッチング装置のフラッディング判定部によりフラッディングの発生が所定の条件を満たすと判定されたアドレスと同じアドレスに関するアドレスエントリを第2フレームスイッチング装置がその第2アドレスエントリ記憶部に記憶していることを知らせる所定の通知が、第1フレームスイッチング装置の通知受信部により受信される。

上記コンピュータプログラムが実行されるフレームスイッチング装置は、フレームスイッチングネットワーク内の他のフレームスイッチング装置に接続されてフレームを送受信する複数のポートと、アドレスとこのアドレスを送信元アドレスとして含んだフレームを受信したポートとの間の対応関係を示すアドレスエントリが記憶されるアドレスエントリ記憶部と、送信フレームの送信先アドレスに関するアドレスエントリがアドレスエントリ記憶部に記憶されていないとき、該送信フレームのフラッディング処理を行うフラッディング処理部と、を備える。

上記コンピュータプログラムは、上記処理ユニットに、あるアドレスに対して生じるフラッディングの発生が所定の条件を満たすか否かを判定するフラッディング判定処理と、フラッディング判定処理によりフラッディングの発生が所定の条件を満たすと判定されたアドレスと同じアドレスに関するアドレスエントリを、フレームスイッチングネットワーク内の他のフレームスイッチング装置がそのアドレスエントリ記憶部に記憶していることを知らせる、該他のフレームスイッチング装置から送信される所定の通知を受信する通知受信処理と、フラッディング判定処理によりフラッディングの発生が所定の条件を満たすと判定されたアドレスと所定の通知を受信したポートとを対応付けるアドレスエントリをアドレスエントリ記憶部に登録するアドレスエントリ登録処理と、を実行させる。

上記アドレス学習方法が実行されるフレームスイッチング装置は、フレームスイッチングネットワーク内の他のフレームスイッチング装置に接続されてフレームを送受信する複数のポートと、アドレスとこのアドレスを送信元アドレスとして含んだフレームを受信したポートとの間の対応関係を示すアドレスエントリが記憶されるアドレスエントリ記憶部と、送信フレームの送信先アドレスに関するアドレスエントリがアドレスエントリ記憶部に記憶されていないとき、該送信フレームのフラッディング処理を行うフラッディング処理部とを備える。

上記のアドレス学習方法は、あるアドレスに対して生じるフラッディングの発生が所定の条件を満たすか否かを判定し、フラッディングの発生が所定の条件を満たすと判定されたアドレスと同じアドレスに関するアドレスエントリを、フレームスイッチングネットワーク内の他のフレームスイッチング装置がそのアドレスエントリ記憶部に記憶していることを知らせる、該他のフレームスイッチング装置から送信される所定の通知を受信し、フラッディングの発生が所定の条件を満たすと判定されたアドレスと所定の通知を受信したポートとを対応付けるアドレスエントリをアドレスエントリ記憶部に登録する。

開示のフレームスイッチング装置は、アドレスとこのアドレスを送信先とするフレームを出力する出力ポートとの対応関係を示すアドレスエントリを記憶するとともに、アドレスエントリが記憶されていないアドレスを送信先とするフレームのフラッディング処理を行うスイッチング装置に、広く使用することができる。

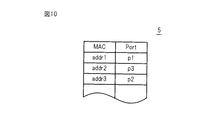

図10は、MACテーブル7のデータ構成例を示す図である。MACテーブル5は、転送すべきMACフレームの送信先MACアドレスを格納するMACフィールドと、転送すべきMACフレームの送信に使用するポートの識別子を格納するPORTフィールドとを少なくとも備え、各送信先MACアドレスを有するフレームを送信するポートを関連付けるテーブルである。

MACテーブル5に記憶される、一対の送信先MACアドレスと出力先ポートの対を有するデータの組み合わせ、すなわちMACテーブル5の各レコードに記憶されるデータの組み合わせをMACエントリと示す。MACエントリは、特許請求の範囲に記載されるアドレスエントリに相当する。

ROM13には、CPU11により実行され、以下に説明する各処理をCPU11に実行させる制御プログラム17を記憶されている。制御プログラム17は、特許請求の範囲に記載されるコンピュータプログラムに相当する。

なお本実施例では、制御プログラム17は、スパニングツリー処理もCPU11に実行させるが、これは開示のコンピュータプログラムの必須の処理ではない。

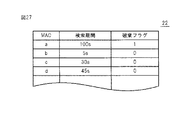

不揮発性メモリ14には、ポート設定テーブル20、学習漏れフラグテーブル21及び破棄アドレステーブル22が記憶される。

なお以下の説明において、LANに接続されているポート、すなわち端末やルータ等が接続されているポートを「LAN側のポート」と示すことがあり、またレイヤ2ネットワークを構成するポートを「WAN側のポート」と示すことがある。

学習漏れフラグテーブル21及び破棄アドレステーブル22のデータ構成については後述する。

なお、本実施例では、図9に示される制御部10をCPU11によるソフトウエア処理により実現する。しかし、制御部10は専用のハードウエア回路によって実現されてもよく、図12を参照して以下に説明される各機能部ブロック31〜35、40及び41は、それぞれ専用のハードウエア回路によって実現されてもよい。

また、MACエントリ検索/通知フレーム送信部32は特許請求の範囲に記載されるアドレスエントリ照会部及び通知送信部に相当し、MAC補完判定部40は特許請求の範囲に記載される登録可否判定部に相当する。

MACエントリ検索フレームは、フラッディングの発生が所定の条件を満たすとフラッディング監視部31に判定されたMACアドレスについて、このMACアドレスと同じMACアドレスに関するMACエントリをMACテーブル5に記憶しているか否かについて、他のレイヤ2スイッチに照会する制御フレームである。

末尾1桁の”x”は、制御フレームが使用される処理の種類に応じて異なる値であり、本明細書によって以下に開示される処理のために専用に割り当てられた値である。

Ether_typeフィールドには、フレームが、本明細書によって以下に開示される処理に使用される制御フレームであることを識別する2バイトのコードが格納される。

Typeフィールドには、フレームがMACエントリ検索フレーム及びMACエントリ通知フレームの何れであるかを示す種別情報が格納される。本実施例ではMACエントリ検索フレームのTypeフィールドには「Req」が格納され、MACエントリ通知フレームのTypeフィールドには「Reply」が格納される。

MACエントリ通知フレームのMACエントリフィールドには、当該のレイヤ2スイッチがMACテーブル5に記憶しているMACアドレスが格納される。

後述するMACエントリ検索/通知フレーム受信部33によって受信されたMACエントリ検索フレームによって照会されたMACアドレスに関するMACエントリを、後述するMACエントリ検索部34がMACテーブル5内で発見したとき、MACエントリ検索/通知フレーム送信部32は、照会されたMACアドレスをMACテーブル5に記憶していることを知らせるMACエントリ通知フレームを作成し、MACエントリ検索フレームを受信したポートから送信する。

MACエントリ検索部34は、MACエントリ検索/通知フレーム受信部33によって受信されたMACエントリ検索フレームによって照会されたMACアドレスに関するMACエントリを、MACテーブル5内で検索する。

MACエントリ登録部35は、MACエントリ検索/通知フレーム受信部33によって受信されたMACエントリ通知フレームによって通知されたMACアドレスが、フラッディング監視部31によりフラッディングの発生が所定の条件を満たすと判定されていたとき、MACエントリ通知フレームを受信したポートとこのMACアドレスとの対を含むMACエントリをMACテーブル5に登録する。

フレーム破棄部41は、MACエントリ登録部35により登録できなかったMACアドレスを送信先MACアドレスとして有するフレームを破棄するように指示する、指示信号をフレーム交換部4へ出力する。

以下の説明では、図3に示すネットワーク構成のレイヤ2スイッチSW1〜SW4として図9に示すレイヤ2スイッチ1を使用した場合のレイヤ2スイッチ1の動作を説明する。しかし、開示のレイヤ2スイッチ1は、他の構成を有するネットワーク構成、例えば図6〜図8を参照して説明した各ネットワーク構成に使用しても、以下に説明する機能を実行することができ、かつ以下に説明する効果を奏する。図21に示す例についても同様である。

RT1、RT3及びRT4は、それぞれルータR−d、R−b及びR−aで使用されるルーティングテーブル及びARPテーブルを示す。

MT1及びMT4は、それぞれレイヤ2スイッチSW1及びSW4で使用されるMACテーブルを示す。

MT2a及びMT2bは、レイヤ2スイッチSW2で使用されるMACテーブルを示し、添字a及びbは、時系列に沿って変化するMACテーブルのそれぞれの時点のデータ内容を示す。

MT3a及びMT3bは、レイヤ2スイッチSW3で使用されるMACテーブルを示し、添字a及びbは、時系列に沿って変化するMACテーブルのそれぞれの時点のデータ内容を示す。

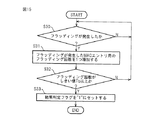

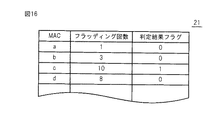

図15は、フラッディングの発生が所定の条件を満たすか否かを判定する処理の第1例を示すフローチャートである。この例では、フラッディングの発生回数が所定のしきい値Tc以上となったときフラッディングの発生が所定の条件を満たす。

ステップS30においてフラッディング監視部31は、図12のフラッディング処理部6がフラッディング処理を行ったか否かを検出する。フラッディング処理が行われなかった場合にはステップS30を繰り返す。

ステップS32における判定においてフラッディング回数が所定のしきい値Tc以上であるときは、ステップS33においてフラッディング監視部31は、ステップS30でフラッディングが検出されたMACアドレスについて学習漏れフラグテーブル21に記憶された結果判定フラグの値を「1」にセットする。

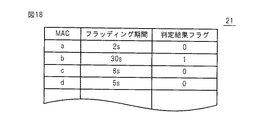

ステップS40においてフラッディング監視部31は、フラッディング処理部6がフラッディング処理を行ったか否かを検出する。フラッディング処理が行われなかった場合にはステップS40を繰り返す。

計測が開始されていない場合には、ステップS42においてフラッディング監視部31は、ステップS40でフラッディングを検出したMACアドレスに対して上記タイマ手段を作動させ、処理をステップS40に戻す。

ステップS43の判定において経過時間がしきい値時間Tt未満であるとき、ステップS44においてフラッディング監視部31は、ステップS40でフラッディングが検出されたMACアドレスについて学習漏れフラグテーブル21に記憶された結果判定フラグの値を「1」にセットする。

レイヤ2スイッチSW2からMACエントリ検索フレーム141を受信できるスイッチの範囲を、照会元のレイヤ2スイッチSW2に隣接するスイッチSW3及びSW4に限定してもよい。この場合には、スイッチSW3及びSW4は、隣接スイッチSW2から受信したMACエントリ検索フレーム141を転送しない。

ステップS51においてMACエントリ検索/通知フレーム送信部32は、学習漏れフラグテーブル21の結果判定フラグを参照して、各MACアドレスについて生じたフラッディングの発生が所定の条件を満たすか否かを判定する。

ステップS52においてMACエントリ検索/通知フレーム送信部32は、フラッディングの発生が所定の条件を満たしたMACアドレスを照会する、MACエントリ検索フレーム141を作成する。

ステップS53においてMACエントリ検索/通知フレーム送信部32は、ポート設定テーブル20によりWAN側のポートであると指定されたポートから、MACエントリ検索フレーム141を送信する。

このためレイヤ2スイッチSW3は、ステップS24において、MACエントリ検索フレーム141を受信したポートp3から、MACテーブルMT3bにMACアドレスaに関するMACエントリが記憶されていることを知らせるMACエントリ通知フレーム142を送信する。

ステップS61においてMACエントリ検索/通知フレーム受信部33は、Typeフィールドの値を参照することによって、受信したフレームがMACエントリ検索フレームであるかMACエントリ通知フレームであるかを判定する。またMACエントリ検索/通知フレーム受信部33は、いずれのポートでこのフレームを受信したかをMACエントリ検索/通知フレーム送信部32に通知する。

ステップS64において、MACエントリ検索/通知フレーム送信部32は、MACエントリ検索フレーム141を受信したポートからMACエントリ通知フレーム142を送信する。

なお、あるレイヤ2スイッチXから送信されたMACエントリ検索フレーム141を受信できるレイヤ2スイッチYの範囲を、スイッチXに隣接するスイッチに制限する場合には、MACエントリ検索フレーム141を転送するステップS65を省略する。

MACアドレスaについて生じたフラッディングの発生が所定の要件を満たしていると判定されていたときは、MACエントリ登録部35は、MACアドレスaとMACエントリ通知フレーム142を受信したポートp2との対を含むMACエントリをMACテーブルMT2bに登録する。

ステップS60においてMACエントリ検索/通知フレーム受信部33は、MACエントリ検索フレーム又はMACエントリ通知フレームの何れかを受信する。

ステップS61においてMACエントリ検索/通知フレーム受信部33は、受信したフレームがMACエントリ検索フレームであるかMACエントリ通知フレームであるかを判定する。またMACエントリ検索/通知フレーム受信部33は、いずれのポートでこのフレームを受信したかをMACエントリ検索/通知フレーム送信部32に通知する。

結果判定フラグの値が”1”であるとき、すなわちMACエントリ通知フレーム141で通知されたMACアドレスについて生じたフラッディングが所定の条件を満たすと判定された場合には、ステップS67においてMACエントリ登録部35は、MACエントリ通知フレームで通知されたMACアドレスとMACエントリ通知フレーム1を受信したポートとの対を含むMACエントリをMACテーブル5に登録する。

なお、あるレイヤ2スイッチXから送信されたMACエントリ検索フレーム141を受信できるレイヤ2スイッチYの範囲が、スイッチXに隣接するスイッチに制限された場合には、MACエントリ通知フレーム142を転送するステップS68を省略する。

ステップS71においてレイヤ2スイッチSW2のフラッディング監視部31は、MACアドレスaについて生じるフラッディングの発生が所定の要件を満たすと判定すると、MACアドレスaについて学習漏れフラグテーブル21に記憶されている結果判定フラグの値を”1”にセットする。ステップS71におけるフラッディング監視部31の処理は、図15〜図18を参照して説明した処理と同じである。

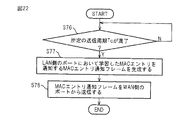

MACエントリ通知フレーム151は、発信元のレイヤ2スイッチSW4のMACアドレステーブル5に記憶されている、スイッチSW4がLAN側のポートにて学習したMACアドレスa、a1、a2…を、レイヤ2スイッチSW4が属しているレイヤ2ネットワーク内の他のレイヤ2スイッチSW1、SW2及びSW3に通知するフレームである。

MACエントリ検索/通知フレーム送信部32は、収集した送信元MACアドレスをMACエントリフィールドに格納したMACエントリ通知フレーム151を生成する。

ステップS78においてMACエントリ検索/通知フレーム送信部32は、ポート設定テーブル20によりWAN側のポートであると指定された全てのポートから、MACエントリ通知フレーム151を送信する。

レイヤ2スイッチSW3は、受信したMACエントリ通知フレーム151の送信元MACアドレスをレイヤ2スイッチSW3のMACアドレスyに変更し、変更したMACエントリ通知フレーム152をステップS74においてレイヤ2スイッチSW2に転送する。

本実施例では、レイヤ2スイッチSW3のMACテーブルMT3aにはMACアドレスaが既に登録されているため、MACエントリ通知フレーム151にて通知されたMACアドレスaについて結果判定フラグの値が”1”でなく、またその他のMACアドレスa1、a2…についても結果判定フラグの値が”1”でないものとする。したがってレイヤ2スイッチSW3のMACエントリ登録部35は、MACテーブルMT3bに新たなMACエントリを追加しない。

上記の通り、レイヤ2スイッチSW2の学習漏れフラグテーブル21に記憶されているMACアドレスaの結果判定フラグの値は”1”である。このためレイヤ2スイッチSW2のMACエントリ登録部35は、MACテーブルMT2bに示すように、MACアドレスaについての新たなMACエントリを追加する。追加されたMACエントリは、MACアドレスaとMACエントリ通知フレーム152を受信したポートp2の対を含む。

MACエントリ検索/通知フレーム送信部32は、MACエントリ通知フレームを、ステップS80で受信したポート以外の全てのWAN側のポートから送信する。

ステップS90において図12に示すフラッディング処理部6がフラッディングの発生を検出すると、ステップS91においてフラッディング監視部31が、学習漏れフラグテーブル21の内容を更新する。ステップS91によるフラッディング監視部31の処理は、図15〜図18を参照して説明した処理と同じである。

破棄アドレステーブル22と学習漏れフラグテーブル21とを1つのテーブルで実現してもよい。

ステップS96においてMAC補完判定部40は、ステップS95においてMACエントリ検索フレームが送信されたMACアドレスについて、破棄アドレステーブル22に記憶された送信回数の値を1つ増加する。

フレーム破棄指示部41は、破棄フラグの値が”1”であるMACアドレスが送信先アドレスであるMACフレームを破棄することを指示する指示信号をフレーム交換部4へ出力する。

本実施例により、MACエントリ検索フレームを所定の回数Tc2以上送信しても他のスイッチから応答が得られないとき、このような送信先MACアドレスを有するフレームはフラッディングされずに破棄される。このためネットワーク中に存在しないMACアドレスを宛先とするフレームの拡散を防止することができる。

ステップS100においてフラッディング処理部6がフラッディングの発生を検出すると、ステップS101においてフラッディング監視部31が、学習漏れフラグテーブル21の内容を更新する。ステップS101によるフラッディング監視部31の処理は、図15〜図18を参照して説明した処理と同じである。

MAC補完判定部40は、ステップS102の判定においてMACエントリ検索フレームを送信していないと判定されたMACアドレスについて、MACエントリ検索フレームが送信され始めてから現在までの経過時間を計測するタイマ手段を作動させ、処理をステップS105へ移す。

破棄アドレステーブル22は、学習漏れフラグテーブル21に記憶されているMACアドレスが格納されるMACフィールドと、各MACアドレスについてMACエントリ検索フレームを送信し始めてから現在までの経過時間すなわち検索時間が格納される検索時間フィールドと、各MACアドレスについての検索時間がしきい値Tt2以上となった否かを示す破棄フラグを格納する破棄フラグフィールドを有する。

破棄アドレステーブル22と学習漏れフラグテーブル21とを1つのテーブルで実現してもよい。

ステップS105及びS106においてMACエントリ検索/通知フレーム送信部32は、図19に示すステップS52及びS53と同様にして、MACエントリ検索フレームを生成及び送信する。

ステップS107においてMAC補完判定部40は、ステップS104の判定において検索時間がしきい値Tt2以上でないと判定されたMACアドレスについて、破棄アドレステーブル22に記憶された破棄フラグの値を”1”にセットする。

フレーム破棄指示部41は、破棄フラグの値が”1”であるMACアドレスが送信先アドレスであるMACフレームを破棄することを指示する指示信号をフレーム交換部4へ出力する。

フレームスイッチングネットワークにおいてフレームの交換を行うフレームスイッチング装置であって、

前記フレームスイッチングネットワーク内の他の前記フレームスイッチング装置に接続されてフレームを送受信する複数のポートと、

アドレスと、このアドレスを送信元アドレスとして含んだフレームを受信した前記ポートと、の間の対応関係を示すアドレスエントリが記憶されるアドレスエントリ記憶部と、

送信フレームの送信先アドレスに関する前記アドレスエントリが前記アドレスエントリ記憶部に記憶されていないとき、該送信フレームのフラッディング処理を行うフラッディング処理部と、

あるアドレスに対して生じるフラッディングの発生が所定の条件を満たすか否かを判定するフラッディング判定部と、

前記フラッディング判定部によりフラッディングの発生が前記所定の条件を満たすと判定されたアドレスと同じアドレスに関するアドレスエントリを、前記フレームスイッチングネットワーク内の他の前記フレームスイッチング装置がそのアドレスエントリ記憶部に記憶していることを知らせる、該他の前記フレームスイッチング装置から送信される所定の通知を受信する通知受信部と、

前記フラッディング判定部によりフラッディングの発生が前記所定の条件を満たすと判定されたアドレスと前記所定の通知を受信したポートとを対応付けるアドレスエントリを前記アドレスエントリ記憶部に登録するアドレスエントリ登録部と、

を備えるフレームスイッチング装置。

前記フラッディング判定部は、あるアドレスに対して生じたフラッディングの回数が所定回数を超えたとき、該アドレスに対して生じるフラッディングの発生が所定の条件を満たすと判定する、付記1に記載のフレームスイッチング装置。

前記フラッディング判定部は、あるアドレスに対して一定時間経過以上にわたってフラッディングが生じたとき、該アドレスに対して生じるフラッディングの発生が所定の条件を満たすと判定する、付記1に記載のフレームスイッチング装置。

前記フラッディング判定部によりフラッディングの発生が前記所定の条件を満たすと判定されたアドレスについて、このアドレスと同じアドレスに関するアドレスエントリを前記アドレスエントリ記憶部に記憶しているか否かを、前記フレームスイッチングネットワーク内の他の前記フレームスイッチング装置に照会するアドレスエントリ照会部を、さらに備える付記1〜3のいずれか一項に記載のフレームスイッチング装置。

前記フレームスイッチングネットワーク内の他の前記フレームスイッチング装置から照会されたアドレスと同一のアドレスに関するアドレスエントリを前記アドレスエントリ記憶部に記憶しているとき、前記照会を受信したポートから前記所定の通知を送信する通知送信部を、さらに備える付記1〜4のいずれか一項に記載のフレームスイッチング装置。

前記所定の通知は、前記他のフレームスイッチング装置の前記アドレスエントリ記憶部にアドレスエントリが記憶されているアドレスに関するアドレス情報を含み、

前記アドレスエントリ登録部は、前記フレームスイッチングネットワーク内の他の前記フレームスイッチング装置から一定周期で送信された前記所定の通知に、前記フラッディング判定部によりフラッディングの発生が前記所定の条件を満たすと判定されたアドレスに関する前記アドレス情報が含まれるとき、該アドレスに関するアドレスエントリを登録する付記1〜3のいずれか一項に記載のフレームスイッチング装置。

前記アドレスエントリ記憶部にアドレスエントリが記憶されているアドレスに関するアドレス情報を含んだ前記所定の通知を、前記フレームスイッチングネットワーク内の他の前記フレームスイッチング装置に一定周期で送信する通知送信部を、さらに備える付記1〜3及び6のいずれか一項に記載のフレームスイッチング装置。

前記フラッディング判定部によりフラッディングの発生が前記所定の条件を満たすと判定されたアドレスに関するアドレスエントリを、前記アドレスエントリ登録部が登録できるか否かを判定する登録可否判定部と、

前記アドレスエントリ登録部により登録できないアドレスを送信先アドレスに有するフレームを破棄するフレーム破棄部と、

さらに備える付記1〜7のいずれか一項に記載のフレームスイッチング装置。

付記1に記載のフレームスイッチング装置としての第1フレームスイッチング装置と、前記フレームスイッチングネットワーク内のフレームスイッチング装置としての第2フレームスイッチング装置と、を前記フレームスイッチングネットワークにおいてフレームの交換を行うフレームスイッチング装置として少なくとも含む通信システムであって、

前記第1フレームスイッチング装置の前記ポートを第1ポートとし、前記第1フレームスイッチング装置の前記アドレスエントリ記憶部を第1アドレスエントリ記憶部とするとき、前記第2フレームスイッチング装置は、

前記フレームスイッチングネットワーク内の他の前記フレームスイッチング装置に接続されてフレームを送受信する複数の第2ポートと、

アドレスと、このアドレスを送信元アドレスとして含んだフレームを受信した前記第2ポートと、の間の対応関係を示すアドレスエントリが記憶される第2アドレスエントリ記憶部と、を備え、

前記第2フレームスイッチング装置から送信される、前記第1フレームスイッチング装置の前記フラッディング判定部によりフラッディングの発生が前記所定の条件を満たすと判定されたアドレスと同じアドレスに関するアドレスエントリを前記第2フレームスイッチング装置がその前記第2アドレスエントリ記憶部に記憶していることを知らせる前記所定の通知が、前記第1フレームスイッチング装置の前記通知受信部により受信される通信システム。

前記第1フレームスイッチング装置は、前記フラッディング判定部によりフラッディングの発生が前記所定の条件を満たすと判定されたアドレスについて、このアドレスと同じアドレスに関するアドレスエントリを前記第2アドレスエントリ記憶部に記憶しているか否かを、前記第2フレームスイッチング装置に照会するアドレスエントリ照会部を、さらに備え、

前記第2フレームスイッチング装置は、前記第1フレームスイッチング装置から照会されたアドレスと同一のアドレスに関するアドレスエントリが前記第2アドレスエントリ記憶部に記憶されているとき、前記照会を受信したポートから前記所定の通知を送信する通知送信部を、さらに備える、

付記9に記載の通信システム。

前記第2フレームスイッチング装置は、前記第2アドレスエントリ記憶部にアドレスエントリが記憶されているアドレスに関するアドレス情報を含んだ前記所定の通知を一定周期で送信する通知送信部を、さらに備え、

前記第1フレームスイッチング装置の前記アドレスエントリ登録部は、前記第2フレームスイッチング装置から送信された前記所定の通知に、前記フラッディング判定部によりフラッディングの発生が前記所定の条件を満たすと判定されたアドレスに関する前記アドレス情報が含まれるとき、該アドレスに関するアドレスエントリを登録する、

付記9に記載の通信システム。

フレームスイッチングネットワークにおいてフレームの交換を行うフレームスイッチング装置内に設けられた処理ユニットにより実行されるコンピュータプログラムであって、前記フレームスイッチング装置は、

前記フレームスイッチングネットワーク内の他の前記フレームスイッチング装置に接続されてフレームを送受信する複数のポートと、

アドレスと、このアドレスを送信元アドレスとして含んだフレームを受信した前記ポートと、の間の対応関係を示すアドレスエントリが記憶されるアドレスエントリ記憶部と、

送信フレームの送信先アドレスに関する前記アドレスエントリが前記アドレスエントリ記憶部に記憶されていないとき、該送信フレームのフラッディング処理を行うフラッディング処理部と、を備え、

前記コンピュータプログラムは、

あるアドレスに対して生じるフラッディングの発生が所定の条件を満たすか否かを判定するフラッディング判定処理と、

前記フラッディング判定処理によりフラッディングの発生が前記所定の条件を満たすと判定されたアドレスと同じアドレスに関するアドレスエントリを、前記フレームスイッチングネットワーク内の他の前記フレームスイッチング装置がそのアドレスエントリ記憶部に記憶していることを知らせる、該他の前記フレームスイッチング装置から送信される所定の通知を受信する通知受信処理と、

前記フラッディング判定処理によりフラッディングの発生が前記所定の条件を満たすと判定されたアドレスと前記所定の通知を受信したポートとを対応付けるアドレスエントリを前記アドレスエントリ記憶部に登録するアドレスエントリ登録処理と、

を前記処理ユニットに実行させる、コンピュータプログラム。

前記フラッディング判定処理によりフラッディングの発生が前記所定の条件を満たすと判定されたアドレスについて、このアドレスと同じアドレスに関するアドレスエントリを前記アドレスエントリ記憶部に記憶しているか否かを、前記フレームスイッチングネットワーク内の他の前記フレームスイッチング装置に照会するアドレスエントリ照会処理を、さらに前記処理ユニットに実行させる、付記12に記載のコンピュータプログラム。

前記所定の通知は、前記他のフレームスイッチング装置の前記アドレスエントリ記憶部にアドレスエントリが記憶されているアドレスに関するアドレス情報を含み、

前記アドレスエントリ登録処理は、前記フレームスイッチングネットワーク内の他の前記フレームスイッチング装置から一定周期で送信された前記所定の通知に、前記フラッディング判定部によりフラッディングの発生が前記所定の条件を満たすと判定されたアドレスに関する前記アドレス情報が含まれるとき、該アドレスに関するアドレスエントリを登録する、付記12に記載のコンピュータプログラム。

前記フラッディング判定処理によりフラッディングの発生が前記所定の条件を満たすと判定されたアドレスに関するアドレスエントリを、前記アドレスエントリ登録処理により登録できるか否かを判定する登録可否判定処理と、

前記アドレスエントリ登録処理により登録できないアドレスを送信先アドレスに有するフレームを破棄することを決定するフレーム破棄処理と、

を前記処理ユニットに実行させる、付記12〜14のいずれか一項に記載のコンピュータプログラム。

フレームスイッチングネットワークにおいてフレームの交換を行うフレームスイッチング装置において実行されるアドレス学習方法であって、

前記フレームスイッチング装置は、

前記フレームスイッチングネットワーク内の他の前記フレームスイッチング装置に接続されてフレームを送受信する複数のポートと、

アドレスと、このアドレスを送信元アドレスとして含んだフレームを受信した前記ポートと、の間の対応関係を示すアドレスエントリが記憶されるアドレスエントリ記憶部と、

送信フレームの送信先アドレスに関する前記アドレスエントリが前記アドレスエントリ記憶部に記憶されていないとき、該送信フレームのフラッディング処理を行うフラッディング処理部と、を備え、

前記アドレス学習方法は、

あるアドレスに対して生じるフラッディングの発生が所定の条件を満たすか否かを判定し、

フラッディングの発生が前記所定の条件を満たすと判定された前記アドレスと同じアドレスに関するアドレスエントリを、前記フレームスイッチングネットワーク内の他の前記フレームスイッチング装置がそのアドレスエントリ記憶部に記憶していることを知らせる、該他の前記フレームスイッチング装置から送信される所定の通知を受信し、

フラッディングの発生が前記所定の条件を満たすと判定された前記アドレスと前記所定の通知を受信したポートとを対応付けるアドレスエントリを前記アドレスエントリ記憶部に登録する、

アドレス学習方法。

フラッディングの発生が前記所定の条件を満たすと判定された前記アドレスについて、このアドレスと同じアドレスに関するアドレスエントリを前記アドレスエントリ記憶部に記憶しているか否かを、前記フレームスイッチングネットワーク内の他の前記フレームスイッチング装置に照会する、付記16に記載のアドレス学習方法。

前記所定の通知は、前記他のフレームスイッチング装置の前記アドレスエントリ記憶部にアドレスエントリが記憶されているアドレスに関するアドレス情報を含み、

前記フレームスイッチングネットワーク内の他の前記フレームスイッチング装置から一定周期で送信された前記所定の通知に、前記フラッディング判定部によりフラッディングの発生が前記所定の条件を満たすと判定されたアドレスに関する前記アドレス情報が含まれるとき、該アドレスに関するアドレスエントリを登録する、付記16に記載のアドレス学習方法。

フラッディングの発生が前記所定の条件を満たすと判定された前記アドレスについて、他の前記フレームスイッチング装置から前記所定の通知を受信しないとき、該アドレスを送信先アドレスに有するフレームを破棄する、付記16〜18のいずれか一項に記載のアドレス学習方法。

10 制御部

31 フラッディング監視部

32 MACエントリ検索/通知フレーム送信部

33 MACエントリ検索/通知フレーム受信部

34 MACエントリ検索部

35 MACエントリ登録部

Claims (9)

- フレームスイッチングネットワークにおいてフレームの交換を行うフレームスイッチング装置であって、

前記フレームスイッチングネットワーク内の他の前記フレームスイッチング装置に接続されてフレームを送受信する複数のポートと、

アドレスと、このアドレスを送信元アドレスとして含んだフレームを受信した前記ポートと、の間の対応関係を示すアドレスエントリが記憶されるアドレスエントリ記憶部と、

送信フレームの送信先アドレスに関する前記アドレスエントリが前記アドレスエントリ記憶部に記憶されていないとき、該送信フレームのフラッディング処理を行うフラッディング処理部と、

あるアドレスに対して生じるフラッディングの発生が所定の条件を満たすか否かを判定するフラッディング判定部と、

前記フラッディング判定部によりフラッディングの発生が前記所定の条件を満たすと判定されたアドレスと同じアドレスに関するアドレスエントリを、前記フレームスイッチングネットワーク内の他の前記フレームスイッチング装置がそのアドレスエントリ記憶部に記憶していることを知らせる、該他の前記フレームスイッチング装置から送信される所定の通知を受信する通知受信部と、

前記フラッディング判定部によりフラッディングの発生が前記所定の条件を満たすと判定されたアドレスと前記所定の通知を受信したポートとを対応付けるアドレスエントリを前記アドレスエントリ記憶部に登録するアドレスエントリ登録部と、

を備えるフレームスイッチング装置。 - 前記フラッディング判定部によりフラッディングの発生が前記所定の条件を満たすと判定されたアドレスについて、このアドレスと同じアドレスに関するアドレスエントリを前記アドレスエントリ記憶部に記憶しているか否かを、前記フレームスイッチングネットワーク内の他の前記フレームスイッチング装置に照会するアドレスエントリ照会部を、さらに備える請求項1に記載のフレームスイッチング装置。

- 前記所定の通知は、前記他のフレームスイッチング装置の前記アドレスエントリ記憶部にアドレスエントリが記憶されているアドレスに関するアドレス情報を含み、

前記アドレスエントリ登録部は、前記フレームスイッチングネットワーク内の他の前記フレームスイッチング装置から一定周期で送信された前記所定の通知に、前記フラッディング判定部によりフラッディングの発生が前記所定の条件を満たすと判定されたアドレスに関する前記アドレス情報が含まれるとき、該アドレスに関するアドレスエントリを登録する請求項1に記載のフレームスイッチング装置。 - 前記フラッディング判定部によりフラッディングの発生が前記所定の条件を満たすと判定されたアドレスに関するアドレスエントリを、前記アドレスエントリ登録部が登録できるか否かを判定する登録可否判定部と、

前記アドレスエントリ登録部により登録できないアドレスを送信先アドレスに有するフレームを破棄するフレーム破棄部と、

さらに備える請求項1〜3のいずれか一項に記載のフレームスイッチング装置。 - 請求項1に記載のフレームスイッチング装置としての第1フレームスイッチング装置と、前記フレームスイッチングネットワーク内のフレームスイッチング装置としての第2フレームスイッチング装置と、を前記フレームスイッチングネットワークにおいてフレームの交換を行うフレームスイッチング装置として少なくとも含む通信システムであって、

前記第1フレームスイッチング装置の前記ポートを第1ポートとし、前記第1フレームスイッチング装置の前記アドレスエントリ記憶部を第1アドレスエントリ記憶部とするとき、前記第2フレームスイッチング装置は、

前記フレームスイッチングネットワーク内の他の前記フレームスイッチング装置に接続されてフレームを送受信する複数の第2ポートと、

アドレスと、このアドレスを送信元アドレスとして含んだフレームを受信した前記第2ポートと、の間の対応関係を示すアドレスエントリが記憶される第2アドレスエントリ記憶部と、を備え、

前記第2フレームスイッチング装置から送信される、前記第1フレームスイッチング装置の前記フラッディング判定部によりフラッディングの発生が前記所定の条件を満たすと判定されたアドレスと同じアドレスに関するアドレスエントリを前記第2フレームスイッチング装置がその前記第2アドレスエントリ記憶部に記憶していることを知らせる前記所定の通知が、前記第1フレームスイッチング装置の前記通知受信部により受信される通信システム。 - 前記第1フレームスイッチング装置は、前記フラッディング判定部によりフラッディングの発生が前記所定の条件を満たすと判定されたアドレスについて、このアドレスと同じアドレスに関するアドレスエントリを前記第2アドレスエントリ記憶部に記憶しているか否かを、前記第2フレームスイッチング装置に照会するアドレスエントリ照会部を、さらに備え、

前記第2フレームスイッチング装置は、前記第1フレームスイッチング装置から照会されたアドレスと同一のアドレスに関するアドレスエントリが前記第2アドレスエントリ記憶部に記憶されているとき、前記照会を受信したポートから前記所定の通知を送信する通知送信部を、さらに備える、

請求項5に記載の通信システム。 - 前記第2フレームスイッチング装置は、前記第2アドレスエントリ記憶部にアドレスエントリが記憶されているアドレスに関するアドレス情報を含んだ前記所定の通知を一定周期で送信する通知送信部を、さらに備え、

前記第1フレームスイッチング装置の前記アドレスエントリ登録部は、前記第2フレームスイッチング装置から送信された前記所定の通知に、前記フラッディング判定部によりフラッディングの発生が前記所定の条件を満たすと判定されたアドレスに関する前記アドレス情報が含まれるとき、該アドレスに関するアドレスエントリを登録する、

請求項5に記載の通信システム。 - フレームスイッチングネットワークにおいてフレームの交換を行うフレームスイッチング装置内に設けられた処理ユニットにより実行されるコンピュータプログラムであって、前記フレームスイッチング装置は、

前記フレームスイッチングネットワーク内の他の前記フレームスイッチング装置に接続されてフレームを送受信する複数のポートと、

アドレスと、このアドレスを送信元アドレスとして含んだフレームを受信した前記ポートと、の間の対応関係を示すアドレスエントリが記憶されるアドレスエントリ記憶部と、

送信フレームの送信先アドレスに関する前記アドレスエントリが前記アドレスエントリ記憶部に記憶されていないとき、該送信フレームのフラッディング処理を行うフラッディング処理部と、を備え、

前記コンピュータプログラムは、

あるアドレスに対して生じるフラッディングの発生が所定の条件を満たすか否かを判定するフラッディング判定処理と、

前記フラッディング判定処理によりフラッディングの発生が前記所定の条件を満たすと判定されたアドレスと同じアドレスに関するアドレスエントリを、前記フレームスイッチングネットワーク内の他の前記フレームスイッチング装置がそのアドレスエントリ記憶部に記憶していることを知らせる、該他の前記フレームスイッチング装置から送信される所定の通知を受信する通知受信処理と、

前記フラッディング判定処理によりフラッディングの発生が前記所定の条件を満たすと判定されたアドレスと前記所定の通知を受信したポートとを対応付けるアドレスエントリを前記アドレスエントリ記憶部に登録するアドレスエントリ登録処理と、

を前記処理ユニットに実行させる、コンピュータプログラム。 - フレームスイッチングネットワークにおいてフレームの交換を行うフレームスイッチング装置において実行されるアドレス学習方法であって、

前記フレームスイッチング装置は、

前記フレームスイッチングネットワーク内の他の前記フレームスイッチング装置に接続されてフレームを送受信する複数のポートと、

アドレスと、このアドレスを送信元アドレスとして含んだフレームを受信した前記ポートと、の間の対応関係を示すアドレスエントリが記憶されるアドレスエントリ記憶部と、

送信フレームの送信先アドレスに関する前記アドレスエントリが前記アドレスエントリ記憶部に記憶されていないとき、該送信フレームのフラッディング処理を行うフラッディング処理部と、を備え、

前記アドレス学習方法は、

あるアドレスに対して生じるフラッディングの発生が所定の条件を満たすか否かを判定し、

フラッディングの発生が前記所定の条件を満たすと判定された前記アドレスと同じアドレスに関するアドレスエントリを、前記フレームスイッチングネットワーク内の他の前記フレームスイッチング装置がそのアドレスエントリ記憶部に記憶していることを知らせる、該他の前記フレームスイッチング装置から送信される所定の通知を受信し、

フラッディングの発生が前記所定の条件を満たすと判定された前記アドレスと前記所定の通知を受信したポートとを対応付けるアドレスエントリを前記アドレスエントリ記憶部に登録する、

アドレス学習方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008208935A JP4717909B2 (ja) | 2008-08-14 | 2008-08-14 | フレームスイッチング装置、通信システム、コンピュータプログラム及びアドレス学習方法 |

| US12/536,678 US8243741B2 (en) | 2008-08-14 | 2009-08-06 | Frame switching device and address learning method |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008208935A JP4717909B2 (ja) | 2008-08-14 | 2008-08-14 | フレームスイッチング装置、通信システム、コンピュータプログラム及びアドレス学習方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010045657A true JP2010045657A (ja) | 2010-02-25 |

| JP4717909B2 JP4717909B2 (ja) | 2011-07-06 |

Family

ID=41681243

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008208935A Expired - Fee Related JP4717909B2 (ja) | 2008-08-14 | 2008-08-14 | フレームスイッチング装置、通信システム、コンピュータプログラム及びアドレス学習方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8243741B2 (ja) |

| JP (1) | JP4717909B2 (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012015679A (ja) * | 2010-06-30 | 2012-01-19 | Fujitsu Ltd | 伝送システム、伝送装置、宛先管理装置、制御ユニット、伝送制御プログラム及び同プログラムを記録したコンピュータ読み取り可能な記録媒体 |

| JP2014086841A (ja) * | 2012-10-23 | 2014-05-12 | Nec Commun Syst Ltd | 端末および方法 |

| JP2016220138A (ja) * | 2015-05-25 | 2016-12-22 | 日本電気通信システム株式会社 | 通信装置、中継方法、および有効性確認応答方法、並びにコンピュータ・プログラム |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9264342B2 (en) * | 2009-12-24 | 2016-02-16 | Samsung Electronics Co., Ltd. | Terminal device based on content name, and method for routing based on content name |

| AU2011101297B4 (en) * | 2011-08-15 | 2012-06-14 | Uniloc Usa, Inc. | Remote recognition of an association between remote devices |

| US9363225B2 (en) * | 2012-01-12 | 2016-06-07 | Cisco Technology, Inc. | Connecting layer-2 domains over layer-3 networks |

| US9973378B2 (en) * | 2013-01-23 | 2018-05-15 | Hewlett Packard Enterprise Development Lp | Implementing gateway redundancy in a network |

| US10306467B2 (en) * | 2013-04-11 | 2019-05-28 | Uniloc 2017 Llc | Shared state among multiple devices |

| US9762436B2 (en) * | 2014-02-25 | 2017-09-12 | Red Hat, Inc. | Unified and persistent network configuration |

| CN107005476B (zh) * | 2014-11-26 | 2021-08-31 | 瑞典爱立信有限公司 | 用于管理交换网络中的数据帧的方法和第一设备 |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004193821A (ja) * | 2002-12-10 | 2004-07-08 | Fujitsu Ltd | ブリッジ装置およびブリッジ装置のアドレス学習方法 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6990316B2 (en) * | 2001-06-26 | 2006-01-24 | Nokia Corporation | Short range RF network configuration |

| JP4020753B2 (ja) | 2002-10-25 | 2007-12-12 | 富士通株式会社 | リング切替方法 |

| JP2006279820A (ja) | 2005-03-30 | 2006-10-12 | Fujitsu Ltd | ブロードキャスト抑制機能を有するネットワークシステム |

| KR100800810B1 (ko) * | 2006-06-30 | 2008-02-01 | 삼성전자주식회사 | 브리지형 휴대 인터넷 시스템 및 그 신호 처리 방법 |

-

2008

- 2008-08-14 JP JP2008208935A patent/JP4717909B2/ja not_active Expired - Fee Related

-

2009

- 2009-08-06 US US12/536,678 patent/US8243741B2/en not_active Expired - Fee Related

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004193821A (ja) * | 2002-12-10 | 2004-07-08 | Fujitsu Ltd | ブリッジ装置およびブリッジ装置のアドレス学習方法 |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012015679A (ja) * | 2010-06-30 | 2012-01-19 | Fujitsu Ltd | 伝送システム、伝送装置、宛先管理装置、制御ユニット、伝送制御プログラム及び同プログラムを記録したコンピュータ読み取り可能な記録媒体 |

| US8934494B2 (en) | 2010-06-30 | 2015-01-13 | Fujitsu Limited | Transmission system, transmission apparatus, destination management apparatus |

| JP2014086841A (ja) * | 2012-10-23 | 2014-05-12 | Nec Commun Syst Ltd | 端末および方法 |

| JP2016220138A (ja) * | 2015-05-25 | 2016-12-22 | 日本電気通信システム株式会社 | 通信装置、中継方法、および有効性確認応答方法、並びにコンピュータ・プログラム |

Also Published As

| Publication number | Publication date |

|---|---|

| US20100040072A1 (en) | 2010-02-18 |

| JP4717909B2 (ja) | 2011-07-06 |

| US8243741B2 (en) | 2012-08-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4717909B2 (ja) | フレームスイッチング装置、通信システム、コンピュータプログラム及びアドレス学習方法 | |

| US11811511B2 (en) | Method, apparatus, and system for communication between controllers in TSN | |

| US7586894B2 (en) | Communication system capable of selecting optimum gateway for terminals | |

| US7619987B2 (en) | Node device | |

| EP2074752B1 (en) | Resiliency schemes in connection oriented communications networks | |

| JP3286584B2 (ja) | 多重化ルータ装置 | |

| KR100656488B1 (ko) | 라우팅 시스템 및 그 라우팅 시스템의 포워딩 정보관리방법 | |

| JP5404938B2 (ja) | 通信装置、通信システムおよび通信方法 | |

| US9094330B2 (en) | Data transport system and control method of data transport system | |

| US20080019265A1 (en) | Systems and methods for configuring a network to include redundant upstream connections using an upstream control protocol | |

| CN102055665A (zh) | 广播上或nbma上的ospf点到多点模式 | |

| JP4890239B2 (ja) | Rprの送信経路指定方法及び装置 | |

| JP4822905B2 (ja) | ブリッジ装置、ブリッジ装置における制御方法、及び制御プログラム | |

| US20080304480A1 (en) | Method for Determining the Forwarding Direction of Ethernet Frames | |

| US20110317681A1 (en) | Network communication system, communication device, network linkage method and program thereof | |

| US7969988B2 (en) | Method and independent communications subnet for determining label-switched routes a communications subnet of this type | |

| JP2000278264A (ja) | データネットワーク監視方法 | |

| US20080037419A1 (en) | System for improving igp convergence in an aps environment by using multi-hop adjacency | |

| JP2022074129A (ja) | BIERv6パケットを送信するための方法および第1のネットワークデバイス | |

| WO2006040796A1 (ja) | 通信システムおよび中継装置 | |

| JP2006279402A (ja) | 通信経路の切替装置、通信経路の切替方法、及び、通信システム | |

| JP4751817B2 (ja) | パケット転送装置およびネットワークシステム | |

| JP3887301B2 (ja) | フレーム転送ネットワーク | |

| JPH057224A (ja) | パケツト交換網 | |

| KR20160137413A (ko) | 소프트웨어 정의 네트워크 토폴리지 내 네트워크 장치 간의 거리 검출 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100423 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100511 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100705 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100928 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101125 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110322 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110330 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140408 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |